# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CURSO DE ENGENHARIA DE COMPUTAÇÃO

#### ALESSANDRA LEONHARDT

# **Compact Modelling and Parameter Extraction of Nanoscale FinFETs**

Work presented in partial fulfillment of the requirements for the degree of Bachelor in Computer Engeneering

Advisor: Prof. Dr. Sergio Bampi

Coadvisor: Prof. Dr. Luiz Fernando Ferreira

Porto Alegre December 2014

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Graduação: Prof. Sérgio Roberto Kieling

Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb

Coordenador do Curso de Engenharia de Computação: Prof. Marcelo Götz Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

Esse trabalho não seria possível sem a ajuda e a o apoio de diversas pessoas a organizações. Primeiramente, gostaria de agradecer ao meu orientador Prof. Dr. Sergio Bampi pela competência na orientação do trabalho e também pelo vasto conhecimento me passado durante as reuniões de acompanhamento. Agradeço também pelo incentivo de buscar além e de fazer o melhor trabalho possível. Sou grata ao meu coorientador Prof. Dr. Luiz Fernando Ferreira por acreditar no sucesso desse trabalho e pelas discussões teóricas e práticas, e também pela ajuda oferecida. Sem suas medidas experimentais esse trabalho sequer existiria.

Ao Centro Nacional de Tecnologia Eletrônica Avançada – CEITEC S.A. – agradeço por ter me dado a oportunidade de experienciar como estagiária os desafios de uma empresa de semicondutores e ainda mais por ter me fornecido a infraestrutura essencial para a conclusão desse trabalho. Em especial gostaria de agradecer ao Dr. Cristiano Krug pela oportunidade. Gostaria de agradecer também ao Dr. Cleber Biasotto pelas importantes discussões e indicações recebidas.

Agradeço à Coordenação de Aperfeiçoamento de Pessoal de Nivel Superior – CAPES – e ao Governo Federal, que através do programa Ciência sem Fronteiras me ofereceram a oportunidade de estudar em uma universidade de importância internacional, onde comecei a me envolver com a pesquisa de dispositivos semicondutores. Também agradeço ao Prof. Dr. Renato Perez Ribas, Prof. Dr. Iain Thayne, e Prof. Dr. Nikolaj Gadegaard que tiveram importância fundamental ao despertar meu interesse por MOSFETs e outros dispositivos.

Agradeço à Universidade Federal do Rio Grande do Sul – UFRGS – por ter me acolhido durante esses anos e me provido com educação de ótima qualidade gratuitamente. Estendo esse agradecimento à toda a sociedade, que possibilita que universidades federais gratuitas sejam referências em termos de educação superior.

Gostaria de agradecer aos meus amigos Jeckson Dellagostin Souza, Luis Henrique Reinicke e Gennaro Rodrigues pelo apoio e descontração nesses anos todos. Em especial agradeço à minha namorada Flávia Filippin pela paciência e apoio incondicional em todas as etapas desse trabalho, e que sempre foi um grande incentivo para continuar indo além. Mais importante, agradeço à minha família, que sempre esteve ao meu lado. Especialmente meu pai Carlos Henrique e minha mãe Solange que me apoiaram em todos os momentos e me deram a possibilidade de crescer. E também à minha irmã Mariana com quem sempre compartilhei ótimas experiências e está sempre presente, e à minha irmã Cristina que foi uma inspiração e uma conselheira nos momentos mais importantes.

## **CONTENTS**

| LIST                                                            | OF FIGURES                                                                                                                                                                                                                                                                            | 8                                            |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| LIST                                                            | OF TABLES                                                                                                                                                                                                                                                                             | 13                                           |

| LIST                                                            | OF PUBLICATIONS                                                                                                                                                                                                                                                                       | 14                                           |

| ABS                                                             | TRACT                                                                                                                                                                                                                                                                                 | 15                                           |

| 1 IN                                                            | ITRODUCTION                                                                                                                                                                                                                                                                           | 16                                           |

| <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul>                   | CALING OF FETS BELOW 100-NM                                                                                                                                                                                                                                                           | 18<br>18<br>20<br>25                         |

|                                                                 | OMPACT DEVICE MODELS                                                                                                                                                                                                                                                                  | 28                                           |

| 3.1                                                             | EKV Double-gate                                                                                                                                                                                                                                                                       | 28                                           |

| 3.2                                                             | BSIM-CMG                                                                                                                                                                                                                                                                              | 30                                           |

| 3.3                                                             | PSP-DGFET                                                                                                                                                                                                                                                                             | 33                                           |

| 4 P                                                             | ARAMETER EXTRACTION                                                                                                                                                                                                                                                                   | 35                                           |

| 4.1                                                             | Threshold Voltage and Subthreshold Slope                                                                                                                                                                                                                                              | 35                                           |

| 4.2                                                             | Series Resistance and Effective Length                                                                                                                                                                                                                                                | 37                                           |

|                                                                 |                                                                                                                                                                                                                                                                                       |                                              |

| 4.2.1                                                           | Suciu-Johnston                                                                                                                                                                                                                                                                        | 38                                           |

| 4.2.1<br>4.2.2                                                  | Suciu-Johnston                                                                                                                                                                                                                                                                        | 38<br>39                                     |

|                                                                 |                                                                                                                                                                                                                                                                                       |                                              |

| 4.2.2                                                           | Campbell et al                                                                                                                                                                                                                                                                        | 39                                           |

| 4.2.2<br>4.2.3                                                  | Campbell et al                                                                                                                                                                                                                                                                        | 39<br>39                                     |

| 4.2.2<br>4.2.3<br><b>4.3</b>                                    | Campbell et al                                                                                                                                                                                                                                                                        | 39<br>39<br>40                               |

| 4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5                             | Campbell et al                                                                                                                                                                                                                                                                        | 39<br>39<br>40<br>42                         |

| 4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5                             | Campbell et al  Torres-Torres  EKV Double-Gate Parameter Extraction Methodology  BSIM-CMG Parameter Extraction Methodology  PSP-DGFET Parameter Extraction Methodology  ESULTS                                                                                                        | 39<br>39<br>40<br>42<br>48                   |

| 4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5                             | Campbell et al                                                                                                                                                                                                                                                                        | 39<br>40<br>42<br>48                         |

| 4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5<br>5 R<br>5.1               | Campbell et al Torres-Torres  EKV Double-Gate Parameter Extraction Methodology  BSIM-CMG Parameter Extraction Methodology  PSP-DGFET Parameter Extraction Methodology  ESULTS  Experimental Devices  Subthreshold Slope and Threshold Voltage Extraction                              | 39<br>39<br>40<br>42<br>48<br>50<br>50<br>51 |

| 4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5<br>5 R<br>5.1<br>5.2        | Campbell et al Torres-Torres  EKV Double-Gate Parameter Extraction Methodology  BSIM-CMG Parameter Extraction Methodology  PSP-DGFET Parameter Extraction Methodology  ESULTS  Experimental Devices  Subthreshold Slope and Threshold Voltage Extraction  Extrinsic Device Parameters | 39<br>39<br>40<br>42<br>48<br>50<br>51<br>53 |

| 4.2.2<br>4.2.3<br>4.3<br>4.4<br>4.5<br>5 R<br>5.1<br>5.2<br>5.3 | Campbell et al Torres-Torres  EKV Double-Gate Parameter Extraction Methodology  BSIM-CMG Parameter Extraction Methodology  PSP-DGFET Parameter Extraction Methodology  ESULTS  Experimental Devices  Subthreshold Slope and Threshold Voltage Extraction                              | 39<br>39<br>40<br>42<br>48<br>50<br>50<br>51 |

| 5.5.1 BSIM-CMG Extracted Parameters   | 68 |

|---------------------------------------|----|

| 5.6 Discussions                       | 72 |

| 6 CONCLUSIONS AND FUTURE WORK         | 74 |

| REFERENCES                            | 76 |

| APPENDIX A BSIM-CMG MODEL CARDS       | 83 |

| APPENDIX B PARAMETER EXTRACTION PLOTS | 86 |

| B.1 Suciu-Johnston Method             | 86 |

| B.2 Torres-Torres Method              | 86 |

| APPENDIX C BSIM-CMG DEVICE MODELLING  | 89 |

| C.1 10nm FinFETs                      | 89 |

| C.2 15nm FinFETs                      | 93 |

| C.3 20nm FinFETs                      | 96 |

## **LIST OF FIGURES**

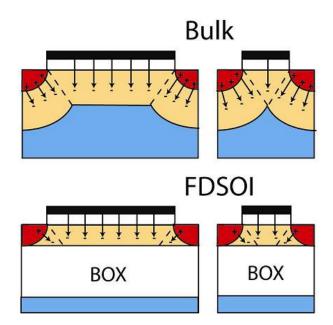

| 2.1  | Charge distribution in long and short channel bulk and SOI MOSFETs (THOMAS, 2011)      | 19 |

|------|----------------------------------------------------------------------------------------|----|

| 2.2  | Cross section of a fully depleted double-gate MOSFET, showing the elec-                | 1) |

|      | tric field and depletion charges from both gates and source and drain(THOMA            | S, |

|      | 2011)                                                                                  | 20 |

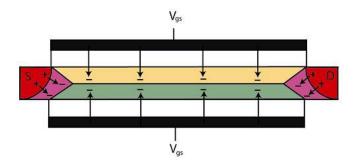

| 2.3  | FinFET device with multiple fins                                                       | 21 |

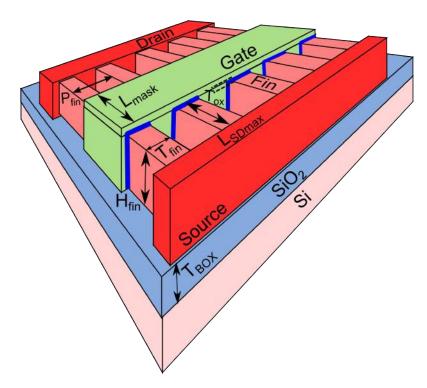

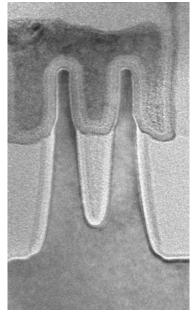

| 2.4  | Scanning Electron Miscroscope image of a FinFET with multiple fins                     | 21 |

| 2.5  | Comparison between Intel aspect ratio and fin pitch of Tri-gate transistors            |    |

|      | from different technology nodes                                                        | 23 |

| 2.6  | Images removed from (NOWAK et al., 2004)                                               | 24 |

| 2.7  | Images extracted from (SUBRAMANIAN et al., 2006)                                       | 25 |

| 2.8  | Aspect ratios and geometries used in (CHENG; LI, 2010)                                 | 25 |

| 2.9  | From the work presented in (CHENG; LI, 2010)                                           | 26 |

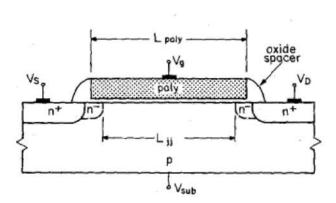

| 2.10 | Schematic cross section of a LDD planar MOSFET device, as presented in                 |    |

|      | (HU; CHANG; CHIA, 1987)                                                                | 26 |

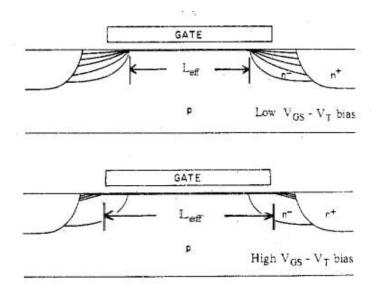

| 2.11 | Current flow patterns in a LDD MOSFET. The top picture shows the opera-                |    |

|      | tion in low $V_{GS}$ bias, while the bottom is in high $V_{GS}$ bias. The variation of |    |

|      | $L_{eff}$ is clearly seen in the different biases, as a result of the gate modulation  |    |

|      | of the n <sup>-</sup> region. (SHEU et al., 1984)                                      | 27 |

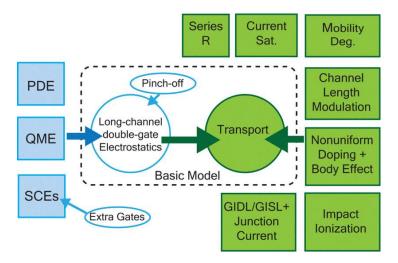

| 3.1  | Simplified structure of the BSIM-CMG model, from (PAYDAVOSI et al.,                    |    |

|      | 2013)                                                                                  | 31 |

| 3.2  | Schematic of the PSP model structure (GILDENBLAT et al., 2006)                         | 33 |

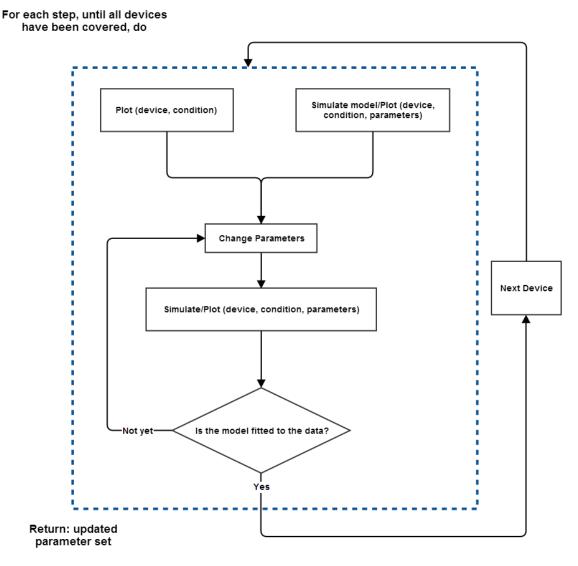

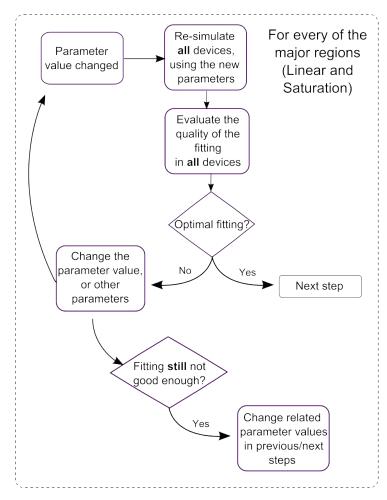

| 4.1  | Flowchart for each step of a general device model parameter extraction                 |    |

|      | procedure                                                                              | 36 |

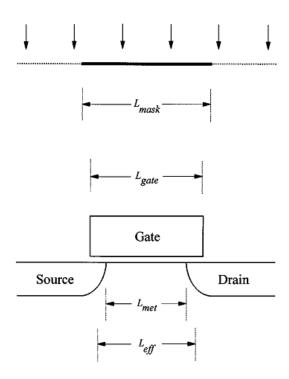

| 4.2  | Schematic of the relationship between the different terms for the channel              |    |

|      | length, in a planar MOSFET (TAUR, 2000)                                                | 37 |

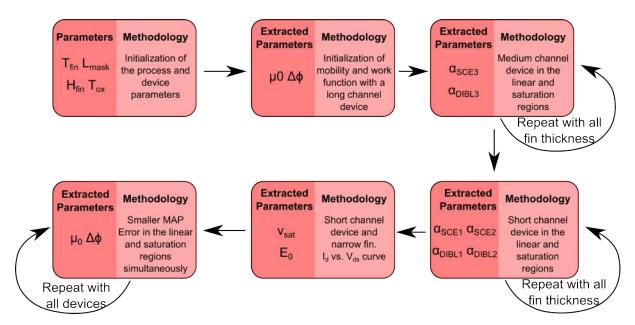

| 4.3  | Simplified flow of the parameter extraction procedure for the EKV Double-              |    |

|      | Gate model                                                                             | 41 |

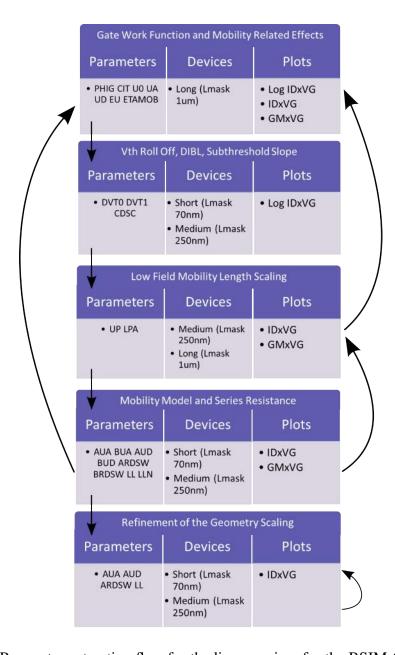

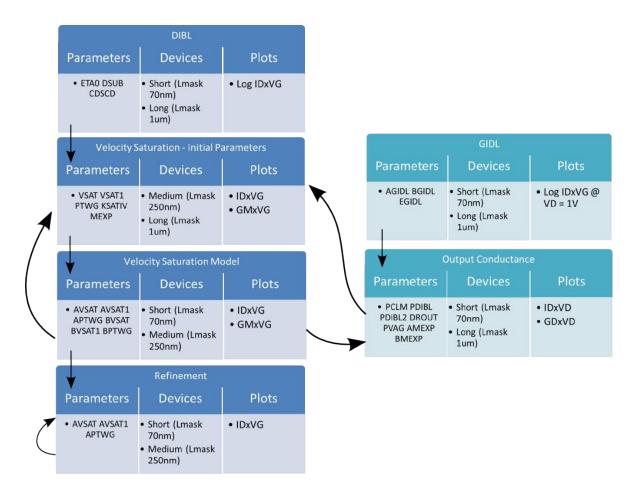

| 4.4  | Simplified flow of the parameter extraction procedure for the BSIM-CMG                 |    |

|      | model                                                                                  | 44 |

| 4.5  | Parameter extraction flow for the linear region, for the BSIM-CMG model.               | 45 |

| 4.6  | Parameter extraction flow for the saturation region and other effects, for the         |    |

|      | BSIM-CMG model                                                                         | 46 |

| 4.7  | Schematic of the proposed changes to the reference BSIM-CMG extraction procedure                                                                                                                                                  | 47 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

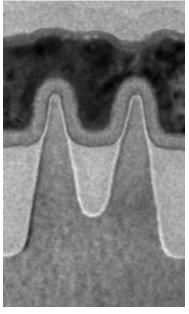

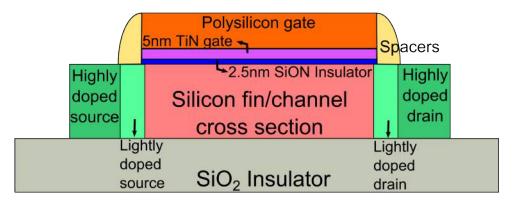

| 5.1  | Schematic of the fabricated devices, showing the cross section of a single fin. Note the lightly doped region below the gate spacers, a characteristic of the LDD structure                                                       | 50 |

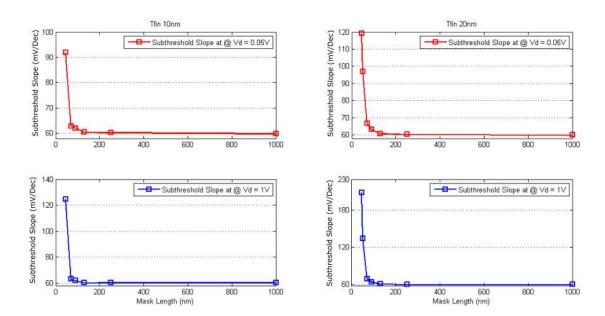

| 5.2  | Comparison of extracted subthreshold slope from devices with different fin thickness. Narrow fins provide better control of the subthreshold region and thus lower subthreshold slope.                                            | 51 |

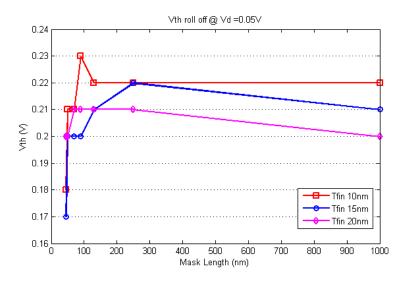

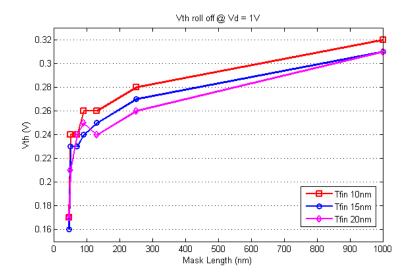

| 5.3  | Threshold voltage extraction for all device in the linear region                                                                                                                                                                  | 52 |

| 5.4  | Threshold voltage extraction for all device in the saturation region                                                                                                                                                              | 52 |

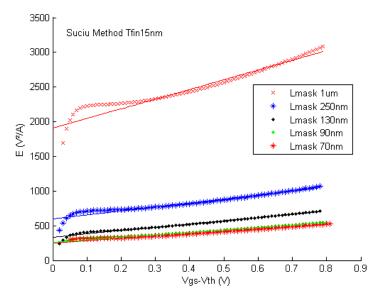

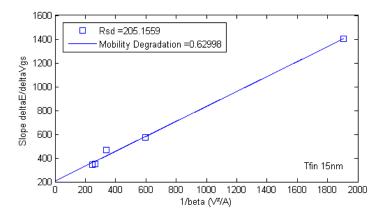

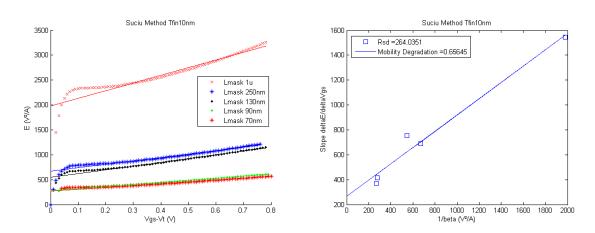

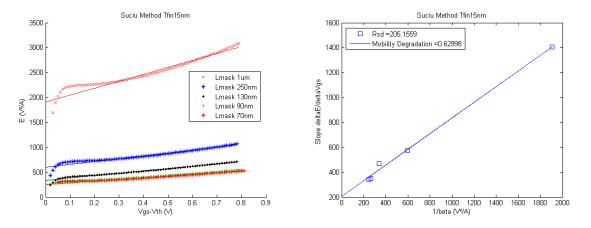

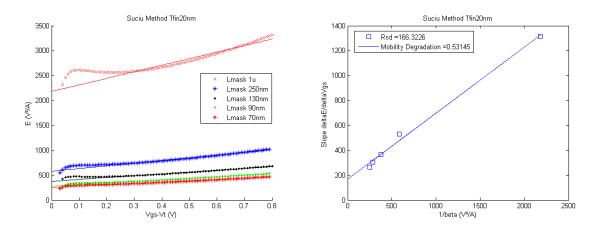

| 5.5  | First step of Suciu-Johnston method, plotting $E$ against the gate overdrive .                                                                                                                                                    | 53 |

| 5.6  | Suciu-Johnston method final results                                                                                                                                                                                               | 54 |

| 5.7  | Campbell et al. method with extrapolation of the curves to yield a single                                                                                                                                                         |    |

|      | value for the series resistance $R_{SD}$                                                                                                                                                                                          | 54 |

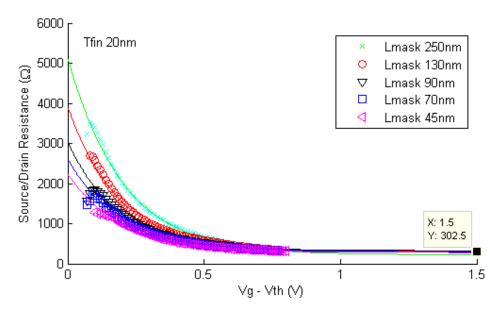

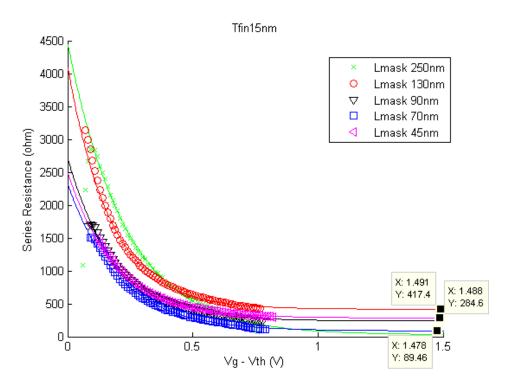

| 5.8  | Campbell et al. method applied to the FinFETs with fin thickness of 15nm.                                                                                                                                                         | 55 |

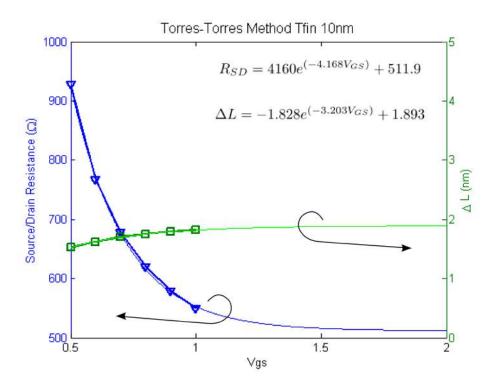

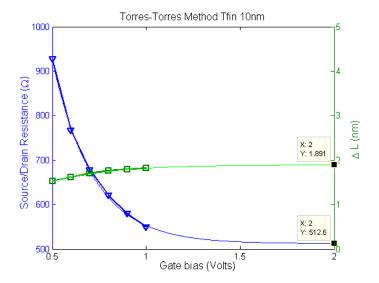

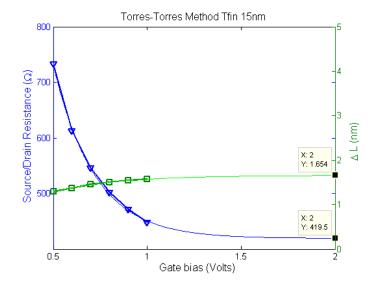

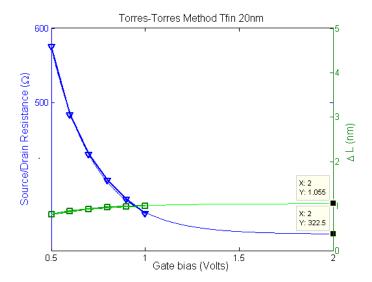

| 5.9  | Torres-Torres method results, presenting the extracted $R_{SD}$ and $\Delta L$ , along                                                                                                                                            |    |

|      | with their dependence on $V_{GS}$                                                                                                                                                                                                 | 56 |

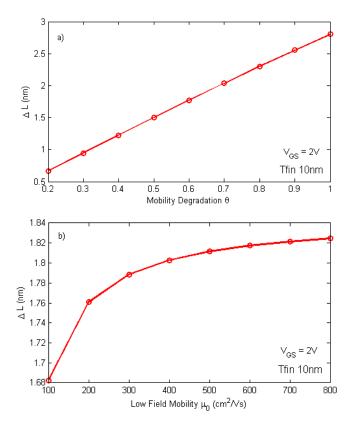

| 5.10 | a) $\Delta L$ sensitivity on the mobility degradation $\theta$ and b) a low field mobility                                                                                                                                        |    |

|      | $\mu_0$ , in the Torres-Torres method                                                                                                                                                                                             | 57 |

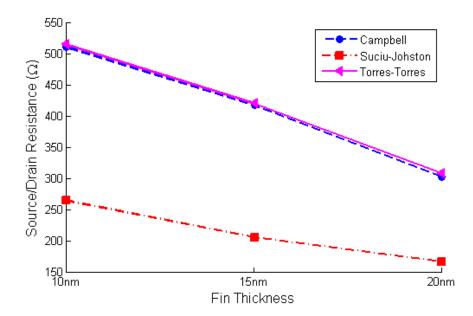

| 5.11 | Source and drain resistance relationship with fin thickness for the explored                                                                                                                                                      |    |

|      | methods                                                                                                                                                                                                                           | 58 |

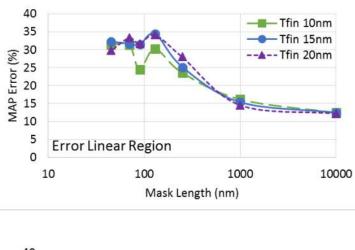

| 5.12 | Mean Absolute Percentage Error between EKV Double-Gate model and measurements, for all devices in the linear and saturation regions. Mask                                                                                         |    |

|      | length is shown in logarithmic scale for better visualization                                                                                                                                                                     | 60 |

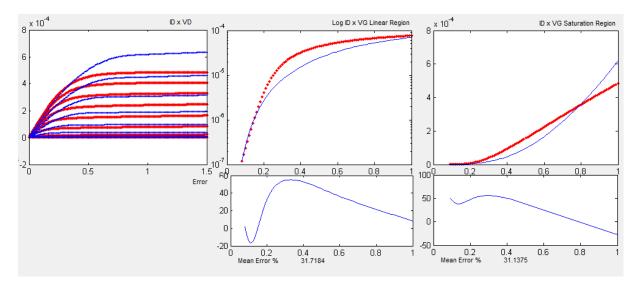

| 5.13 | Fitting of the EKV - DG model to the data measured from a FinFET with                                                                                                                                                             |    |

|      | fin thickness of 20nm and mask gate length of 70nm                                                                                                                                                                                | 61 |

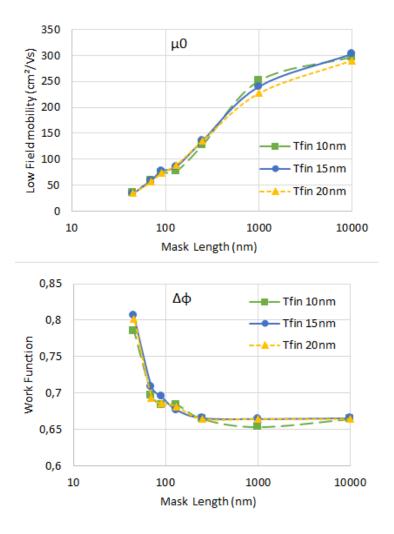

| 5.14 | Extracted low field mobility and $\Delta\phi$ for the EKV Double-Gate model using                                                                                                                                                 |    |

|      | devices with fin thickness from 10nm to 20nm                                                                                                                                                                                      | 62 |

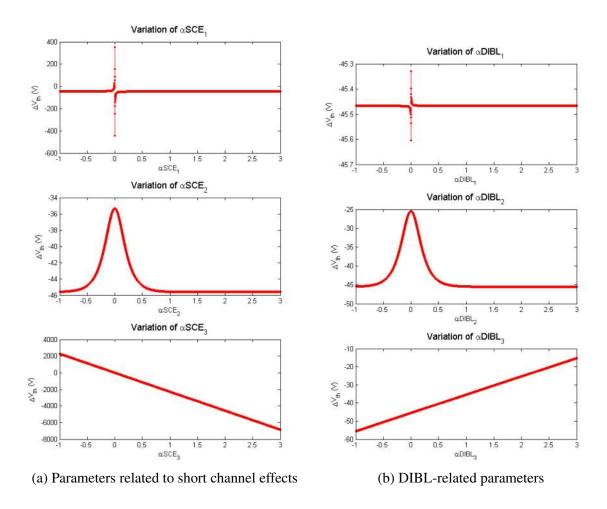

| 5.15 | Sensitivity of the threshold voltage reduction $\Delta v_{th}$ to the parameters related                                                                                                                                          |    |

|      | to short channel effects and DIBL                                                                                                                                                                                                 | 63 |

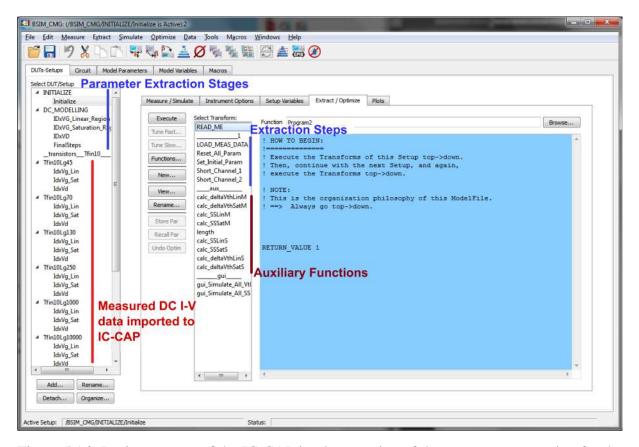

| 5.16 | Basic structure of the IC-CAP implementation of the parameter extraction for the BSIM-CMG model                                                                                                                                   | 64 |

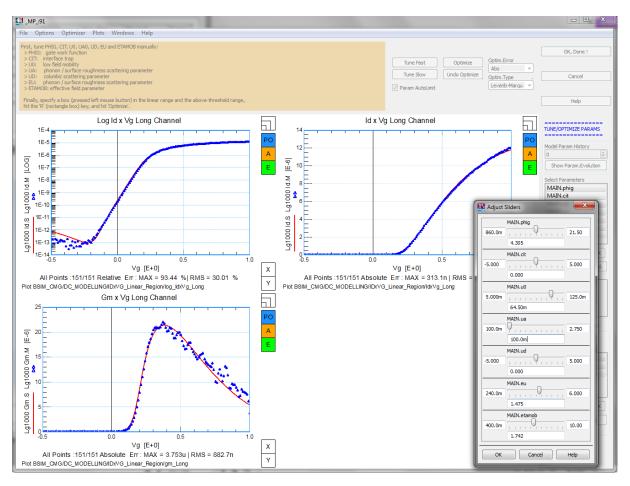

| 5.17 | Example extraction graphic interface implemented in IC-CAP, showing the sliders that change the value of the parameters being extracted. Every time a slider is moved, the program simulates the all setups again and refresh the |    |

|      | plots                                                                                                                                                                                                                             | 65 |

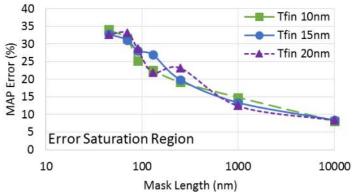

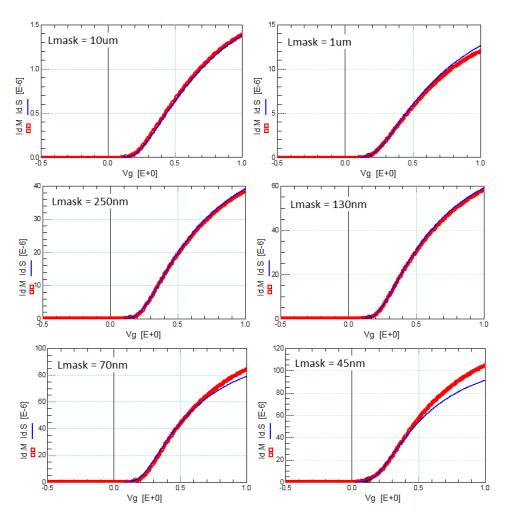

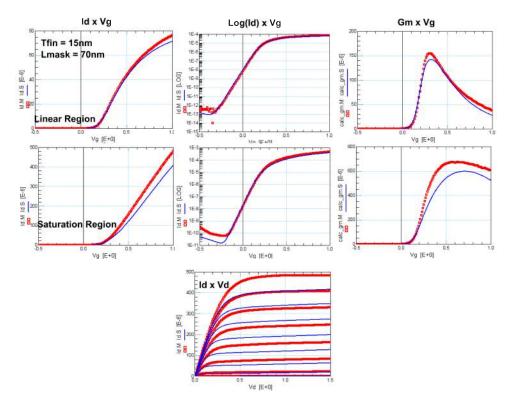

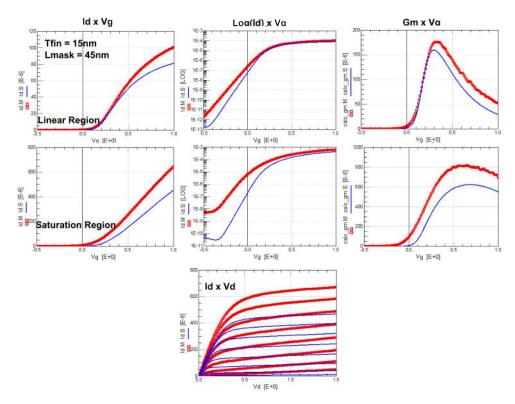

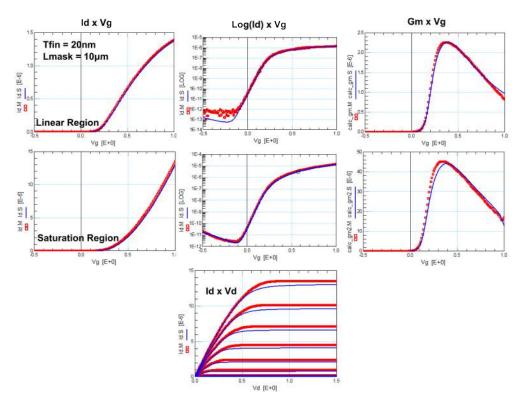

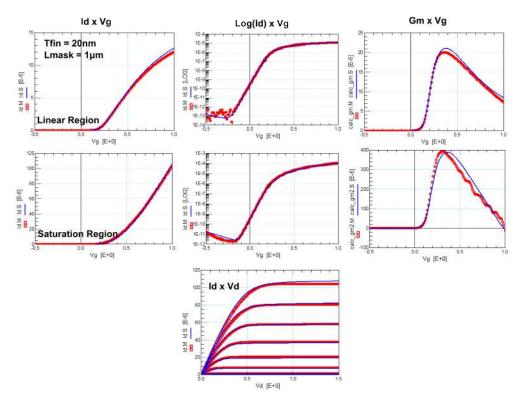

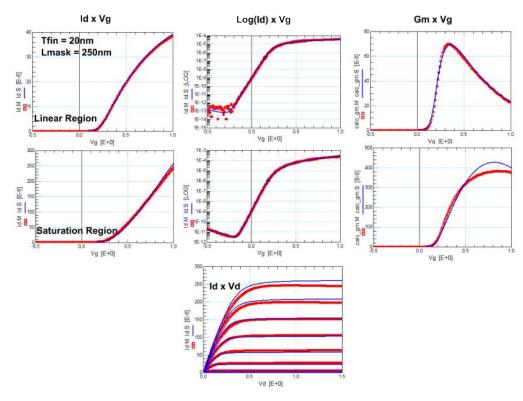

| 5.18 | Resulting plots for devices with 20nm of fin thickness                                                                                                                                                                            | 66 |

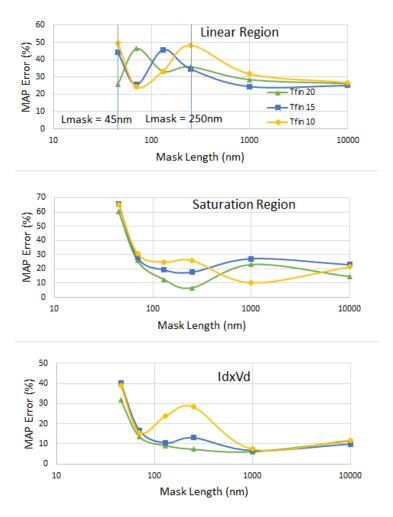

| 5.19 | Mean Absolute Percentage Error for all devices in each of the operation regions. Mask length is shown in logarithmic scale for better visualization. | 67 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

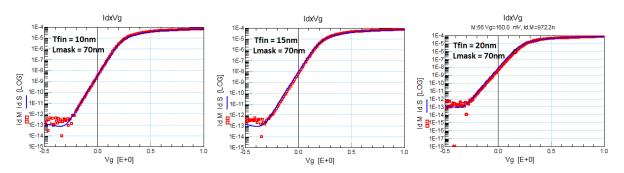

| 5.20 | Modelling of devices with 70nm of mask gate length, with fin thickness of                                                                            | 07 |

| 3.20 | 10nm, 15nm and 20nm, operating in the linear region. The subthreshold                                                                                |    |

|      | region is very well fitted, showing accuracy in the formulation of SCE and                                                                           |    |

|      | DIBL                                                                                                                                                 | 68 |

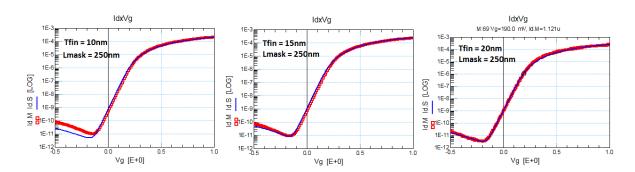

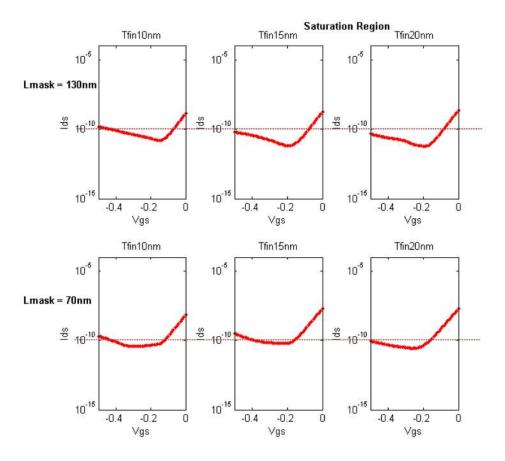

| 5.21 | Modelling of devices with 250nm of mask gate length, with fin thickness                                                                              |    |

|      | of 10nm, 15nm and 20nm, operating in the saturation region. The both                                                                                 |    |

|      | the accumulation and subthreshold regions are very well fitted, showing                                                                              |    |

|      | how GIDL was properly modelled in the BSIM-CMG. This effect is not                                                                                   |    |

|      | accounted for in other double-gate compact models                                                                                                    | 68 |

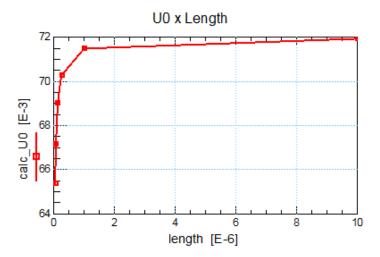

| 5.22 | Low field mobility $\mu_0$ scaling with mask length, for devices with 20nm of                                                                        |    |

|      | fin thickness                                                                                                                                        | 69 |

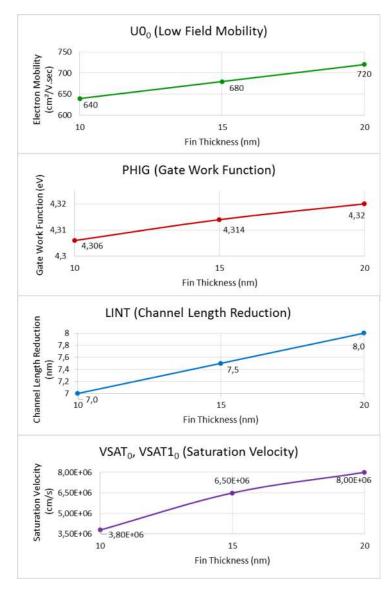

| 5.23 | Comparison of physically relevant parameters extracted for devices with                                                                              |    |

|      | different fin thickness                                                                                                                              | 70 |

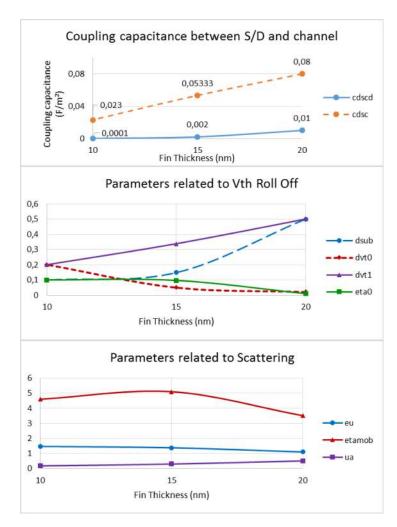

| 5.24 | Comparison of short channel effect related parameters, extracted for de-                                                                             |    |

|      | vices with different fin thickness                                                                                                                   | 71 |

| 5.25 | Leakage current in the saturation region due to GIDL for devices with the                                                                            |    |

|      | same mask length, but different fin thickness                                                                                                        | 72 |

| B.1  | Extraction of the series resistance for FinFETs with 10nm of fin thickness                                                                           |    |

|      | using the Suciu-Johnston method                                                                                                                      | 86 |

| B.2  | Extraction of the series resistance for FinFETs with 15nm of fin thickness                                                                           |    |

|      | using the Suciu-Johnston method                                                                                                                      | 86 |

| B.3  | Extraction of the series resistance for FinFETs with 20nm of fin thickness                                                                           |    |

|      | using the Suciu-Johnston method                                                                                                                      | 87 |

| B.4  | Extraction of the series resistance for FinFETs with 10nm of fin thickness                                                                           |    |

|      | using the Torres-Torres method, including the variation with gate bias and                                                                           |    |

|      | the extrapolation to higher overdrives                                                                                                               | 87 |

| B.5  | Extraction of the series resistance for FinFETs with 15nm of fin thickness                                                                           |    |

|      | using the Torres-Torres method, including the variation with gate bias and                                                                           |    |

|      | the extrapolation to higher overdrives                                                                                                               | 88 |

| B.6  | Extraction of the series resistance for FinFETs with 20nm of fin thickness                                                                           |    |

|      | using the Torres-Torres method, including the variation with gate bias and                                                                           |    |

|      | the extrapolation to higher overdrives                                                                                                               | 88 |

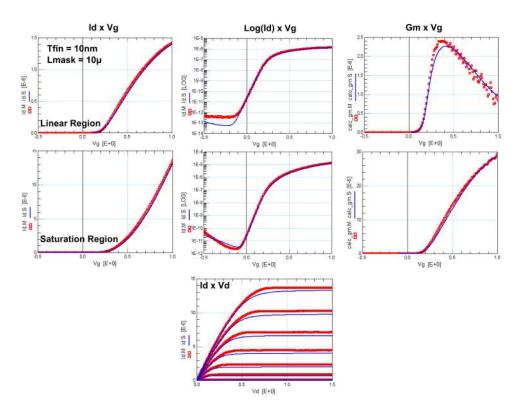

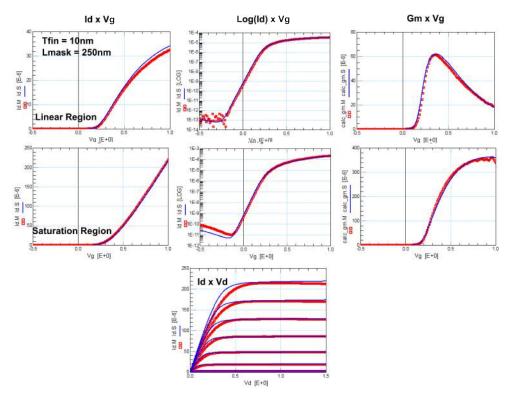

| C.1  | Modelling of a FinFET with $T_{fin}$ = 10nm and $L_{mask}$ = 10 $\mu$ m in all operation                                                             |    |

|      | regions. Measured points are the small red squares and simulated data is                                                                             |    |

|      | the solid blue line                                                                                                                                  | 89 |

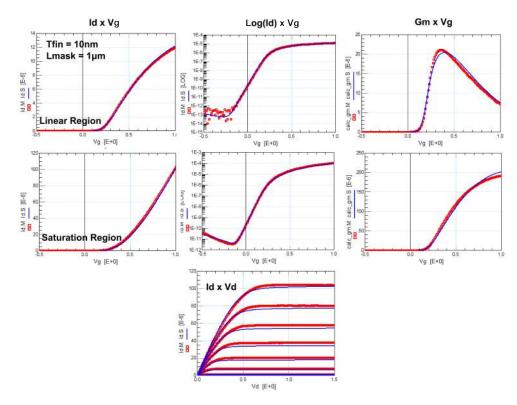

| C.2  | Modelling of a FinFET with $T_{fin}$ = 10nm and $L_{mask}$ = 1 $\mu$ m in all operation                                                                     |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | regions. Measured points are the small red squares and simulated data is                                                                                    | 00  |

| C.3  | the solid blue line                                                                                                                                         | 90  |

| C.3  | Modelling of a FinFET with $T_{fin} = 10$ nm and $L_{mask} = 250$ nm in all opera-                                                                          |     |

|      | tion regions. Measured points are the small red squares and simulated data is the solid blue line                                                           | 90  |

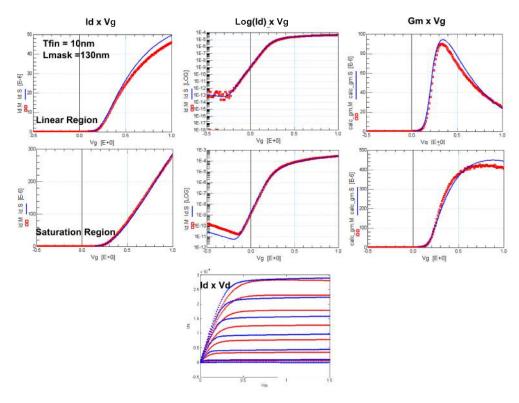

| C.4  |                                                                                                                                                             | 90  |

| C.4  | Modelling of a FinFET with $T_{fin} = 10$ nm and $L_{mask} = 130$ nm in all operation regions. Measured points are the small red squares and simulated data |     |

|      | is the solid blue line                                                                                                                                      | 91  |

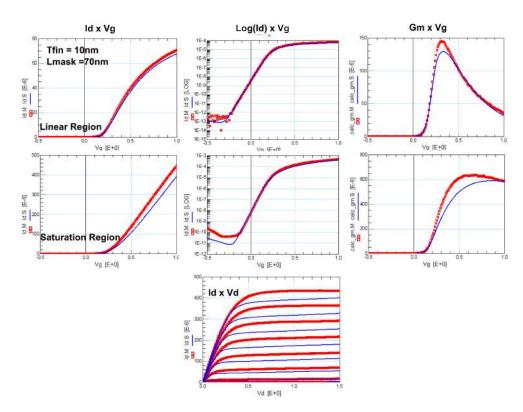

| C.5  | Modelling of a FinFET with $T_{fin}$ = 10nm and $L_{mask}$ = 70nm in all operation                                                                          | 71  |

| C.3  | regions. Measured points are the small red squares and simulated data is                                                                                    |     |

|      | the solid blue line                                                                                                                                         | 91  |

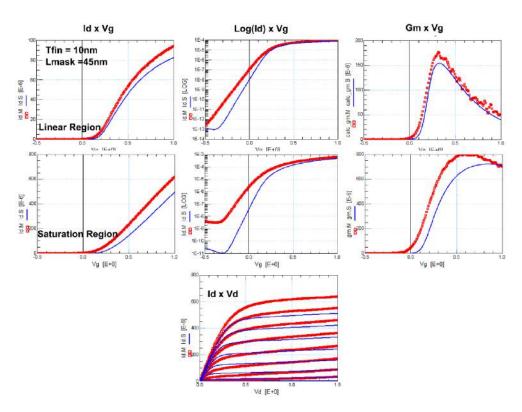

| C.6  | Modelling of a FinFET with $T_{fin}$ = 10nm and $L_{mask}$ = 45nm in all operation                                                                          | 71  |

| C.0  | regions. Measured points are the small red squares and simulated data is                                                                                    |     |

|      | the solid blue line                                                                                                                                         | 92  |

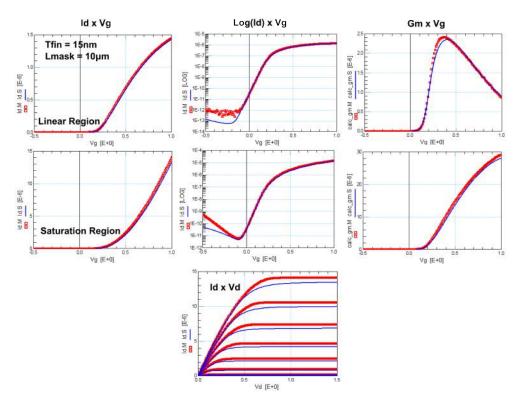

| C.7  | Modelling of a FinFET with $T_{fin}$ = 15nm and $L_{mask}$ = 10 $\mu$ m in all operation                                                                    | 72  |

| C.7  | regions. Measured points are the small red squares and simulated data is                                                                                    |     |

|      | the solid blue line                                                                                                                                         | 93  |

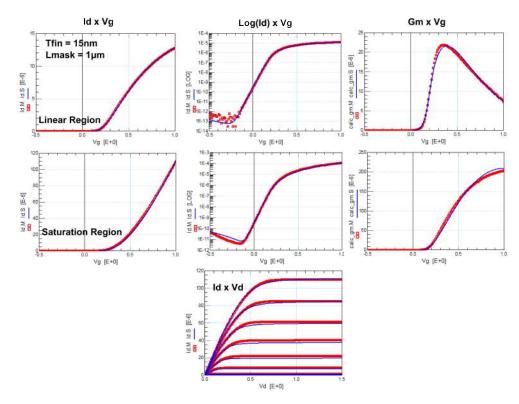

| C.8  | Modelling of a FinFET with $T_{fin}$ = 15nm and $L_{mask}$ = 1 $\mu$ m in all operation                                                                     | , , |

|      | regions. Measured points are the small red squares and simulated data is                                                                                    |     |

|      | the solid blue line                                                                                                                                         | 93  |

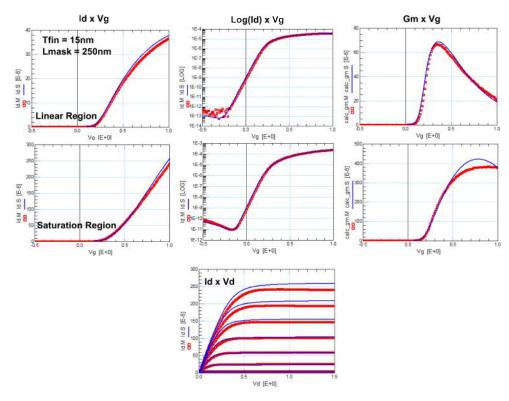

| C.9  | Modelling of a FinFET with $T_{fin}$ = 15nm and $L_{mask}$ = 250nm in all opera-                                                                            |     |

|      | tion regions. Measured points are the small red squares and simulated data                                                                                  |     |

|      | is the solid blue line                                                                                                                                      | 94  |

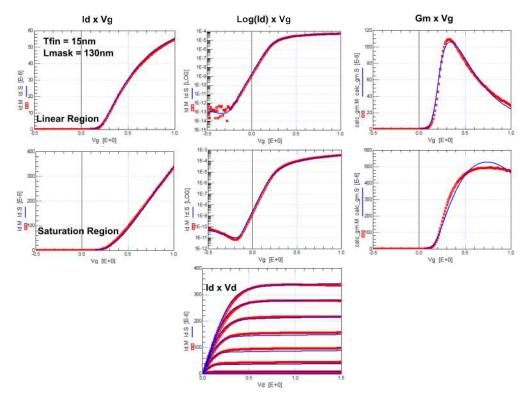

| C.10 | Modelling of a FinFET with $T_{fin}$ = 15nm and $L_{mask}$ = 130nm in all opera-                                                                            |     |

|      | tion regions. Measured points are the small red squares and simulated data                                                                                  |     |

|      | is the solid blue line                                                                                                                                      | 94  |

| C.11 | Modelling of a FinFET with $T_{fin} = 15$ nm and $L_{mask} = 70$ nm in all operation                                                                        |     |

|      | regions. Measured points are the small red squares and simulated data is                                                                                    |     |

|      | the solid blue line.                                                                                                                                        | 95  |

| C.12 | Modelling of a FinFET with $T_{fin}$ = 15nm and $L_{mask}$ = 45nm in all operation                                                                          |     |

|      | regions. Measured points are the small red squares and simulated data is                                                                                    |     |

|      | the solid blue line                                                                                                                                         | 95  |

| C.13 | Modelling of a FinFET with $T_{fin}$ = 20nm and $L_{mask}$ = 10 $\mu$ m in all operation                                                                    |     |

|      | regions. Measured points are the small red squares and simulated data is                                                                                    |     |

|      | the solid blue line                                                                                                                                         | 96  |

| C.14 | Modelling of a FinFET with $T_{fin}$ = 20nm and $L_{mask}$ = 1 $\mu$ m in all operation                                                                     |     |

|      | regions. Measured points are the small red squares and simulated data is                                                                                    |     |

|      | the solid blue line                                                                                                                                         | 96  |

| C.15 | Modelling of a FinFET with $T_{fin} = 20$ nm and $L_{mask} = 250$ nm in all opera- |    |

|------|------------------------------------------------------------------------------------|----|

|      | tion regions. Measured points are the small red squares and simulated data         |    |

|      | is the solid blue line                                                             | 97 |

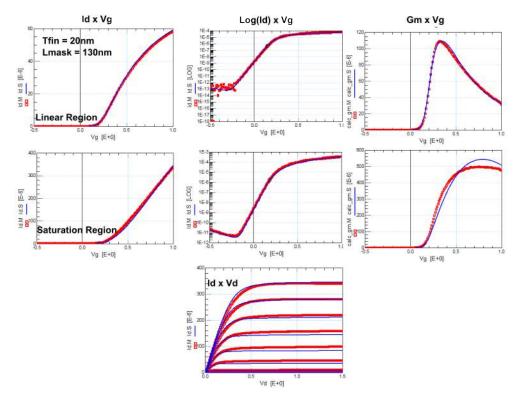

| C.16 | Modelling of a FinFET with $T_{fin}$ = 20nm and $L_{mask}$ = 130nm in all opera-   |    |

|      | tion regions. Measured points are the small red squares and simulated data         |    |

|      | is the solid blue line                                                             | 97 |

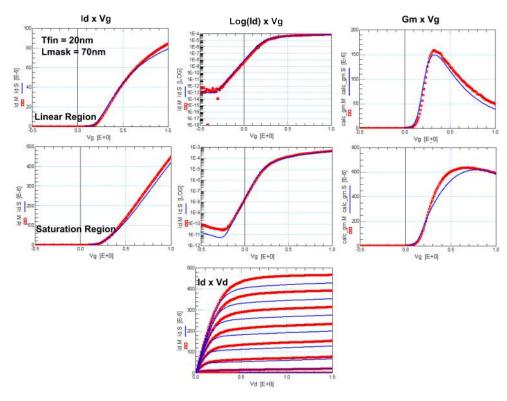

| C.17 | Modelling of a FinFET with $T_{fin}$ = 20nm and $L_{mask}$ = 70nm in all operation |    |

|      | regions. Measured points are the small red squares and simulated data is           |    |

|      | the solid blue line.                                                               | 98 |

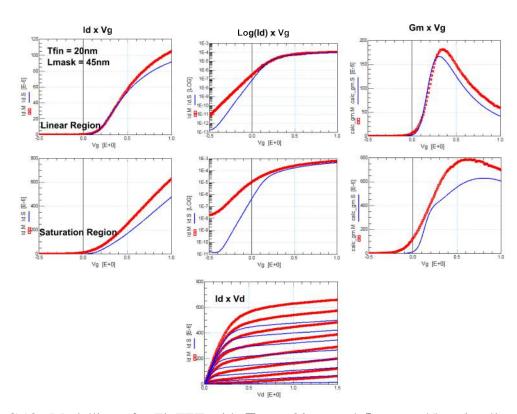

| C.18 | Modelling of a FinFET with $T_{fin}$ = 20nm and $L_{mask}$ = 45nm in all operation |    |

|      | regions. Measured points are the small red squares and simulated data is           |    |

|      | the solid blue line.                                                               | 98 |

# **LIST OF TABLES**

| 5.1 | Available mask gate lengths for the Reference Process FinFETs with 10nm |    |

|-----|-------------------------------------------------------------------------|----|

|     | to 20nm of fin thickness                                                | 51 |

| 5.2 | Extracted values of series resistance and channel length reduction. The |    |

|     | following values were used as initial parameters for the models         | 58 |

| 5.3 | Added effects to the MATLAB implementation of the long channel core     |    |

|     | model of the EKV Double-Gate                                            | 59 |

| 5.4 | Extracted values of series resistance and channel length reduction. The |    |

|     | following values were used as initial parameters for the models         | 61 |

| A.1 | Tfin 20nm BSIM-CMG Model Card                                           | 83 |

| A.2 | Tfin 15nm BSIM-CMG Model Card                                           | 84 |

| A.3 | Tfin 10nm BSIM-CMG Model Card                                           | 85 |

#### LIST OF PUBLICATIONS

ALESSANDRA LEONHARDT AND SERGIO BAMPI, Analytical Compact Models for Long Channel Double Gate MOSFETs: A Review. **XXIX South Symposium on Microelectronics** - **SIM**, 2014.

ALESSANDRA LEONHARDT, LUIZ FERNANDO FERREIRA AND SERGIO BAMPI, Effective Device Electrical Parameter Extraction on sub-22nm FinFETs. **IEEE International Symposium on Circuits and Systems - ISCAS**, 2015. (Submitted to publication)

ALESSANDRA LEONHARDT, LUIZ FERNANDO FERREIRA AND SERGIO BAMPI, Nanoscale FinFET Global Parameter Extraction for the BSIM-CMG Model. **VI Latin American Symposium on Circuits & Systems - LASCAS**, 2015. (Accepted)

#### **ABSTRACT**

This graduation work presents a study of FinFETs, compact models and their parameter extraction procedures, and also the results of parameter extractions of measured FinFET devices for different compact models, as well as other electrical parameters extracted from the transistors.

The first part of this report will explain in detail the existing challenges to further scale the dimensions of the MOSFET device, such as short channel and parasitic effects, as well as large statistical device variations, that have become proeminent and assume a higher influence in the device behaviour. The FinFET architecture promises a better electrical behaviour in sub-22nm lengths, and will be discussed in detail. A large set of FinFET devices has been manufactured in the IMEC Institute, Belgium, and characterised in the PhD thesis of (FERREIRA, 2012) and is used throughout this work. The FinFET devices range from 10µm to 45nm of mask length, with fin thickness of 10nm, 15nm and 20nm.

A compact model uses assumptions and simplifications to predict the electrical output characteristics of a device, while being computationally efficient. In this work, the EKV Double-Gate model, the BSIM-CMG and the PSP-DGFET will be studied, along with their parameter extraction procedures. Changes are proposed to the BSIM-CMG global parameter extraction in order to ensure that the parameters are consistent with the whole set of devices.

The results obtained for the implemented parameter extractions are presented and discussed. Electrical parameters, such as series resistance and effective length have been extracted using different methodologies available in the literature. The extracted series resistance ranges from  $500\Omega$  to  $300\Omega$ , and the channel length reduction varies between 14nm and 16nm. The EKV Double-Gate model and parameter extraction has been implemented in MATLAB and the results show weaknesses in the model. The BSIM-CMG parameter extraction procedure was implemented in IC-CAP and shows an accurate fitting over a wide range of channel lengths using a single set of parameters, with error mean absolute around 20% in all operation regimes. Subjective analysis are also used to compare and demonstrate issues that the models and extraction procedures present.

**Keywords:** FinFETs. Compact Models. Parameter Extraction. MOSFET. BSIM-CMG. EKV-DG. Effective Channel Length.

#### 1 INTRODUCTION

The MOSFET technology has been driving the semiconductor industry to its current power for the last five decades. The dimensions of the transistors have been shrinking consistently from channel lengths of several micrometers to the current technology of tenths of nanometers. Several challenges are faced, however, in order to push forward this reduction in length, such as threshold voltage roll off, drain induced barrier lowering (DIBL), gate leakage, subthreshold slope degradation, gate induced drain leakage (GIDL), and also higher statistical variability. The FinFET architecture promises a better electrical behaviour in dimensions of few nanometers, and is regarded as the best alternative to further scale the transistor without a fundamental change in substrate material or fabrication flow. A large set of silicon on insulator FinFET devices has been manufactured by the IMEC Institute, Belgium, and characterised in the PhD thesis of (FERREIRA, 2012) and is used throughout this work. The measured FinFET devices range from 10µm to 45nm of mask length, with fin thickness of 10nm, 15nm and 20nm. In order to integrate the FinFET technology in modern circuit design, an accurate electrical modelling is essential, since compact device models are important tools for circuit designers.

The parameter extraction was performed in two different ways, although related: first, using extraction methodologies to assess electrical parameters such as series resistance, effective channel length, threshold voltage and subthreshold slope. These extractions were made using the methodologies presented in (SUCIU; JOHNSTON, 1980; CAMPBELL et al., 2011; TORRES-TORRES; MURPHY-ARTEAGA, 2002; WONG et al., 1987). The second part of the parameter extraction was performed for different compact models, adopting the proposed methodologies, in order to obtain a set of parameters to correctly simulate the FinFETs, using a certain device model.

A compact model uses assumptions and simplifications to predict the electrical output characteristics of a device, while being computationally efficient. In this work, the EKV Double-Gate model, the BSIM-CMG and the PSP-DGFET will be studied, along with their parameter extraction procedures. The EVK model for double-gate semiconductor devices (SALLESE et al., 2005; PRÉGALDINY et al., 2006; TANG et al., 2009; CHEVILLON et al., 2009; YESAYAN et al., 2011) is an academic and simple charge based model, with its long channel core model available in VHDL in (PRÉGALDINY et al., 2006). The BSIM-CMG was formulated in (DUNGA et al., 2007; DUNGA, 2008; DUNGA et al., 2008) and afterwards expanded in (LU et al., 2010; LU, 2011; CHAUHAN et al., 2011). It is an already solidified analytical model for multi gate devices, already implemented in commercial simulators such as the Cadence SPECTRE Circuit Simulator (CADENCE DESIGN SYSTEMS, 2013), used for the model simulations in this report. Finally, the PSP compact model for FinFETs (SMIT et al., 2006; SMIT et al., 2007; DESSAI et al., 2009) derived from the PSP surface potential model. It has no accessible implementation, however.

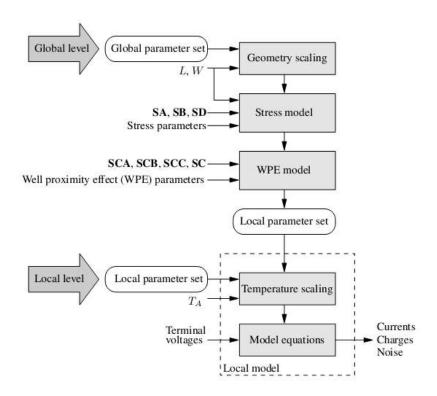

In order to correctly describe a given technology, a compact model needs a set of physi-

cal and fitting parameters, which is obtained from measured data using a parameter extraction procedure. A parameter extraction can be either global, to extract a single set of parameters to model a wide range of devices, or local, that accurately model transistors with small variations in channel length and width. The parameter extraction procedures of the studied models are explained and detailed in this report. The parameter extraction for the EKV Double-Gate model is adjusted to improve the model fitting. Changes are proposed to the BSIM-CMG global parameter extraction in order to ensure that the parameters are consistent with the whole set of devices.

Finally, the results obtained for the implemented parameter extractions are presented and discussed. Electrical parameters, such as series resistance and effective length have been extracted using different methodologies available in the literature. The EKV Double-Gate model and parameter extraction has been implemented in MATLAB and the results examined. The SPECTRE implementation of the BSIM-CMG was used and the parameter extraction procedure implemented in the Keysight IC-CAP Device Modeling Software. The quality of the extraction and modelling is assessed using the mean absolute percentage error (MAP Error) methodology. Subjective analysis are also used to compare and demonstrate issues that the models and extraction procedures present.

This work is organized as follows: in chapter 2 the MOSFET technology is reviewed, and the FinFET architecture detailed, along with comparisons. Chapter 3 explains in detail the models studied, with their equations, assumptions and issues. The effective device parameter extraction is addressed in chapter 4. The extraction procedures for the studied models are detailed, comprehensibly. In this chapter, the changes proposed in this work for the extraction procedures are presented, alongside their motivation. In chapter 5, the results of the mentioned parameter extractions are shown and discussed. Finally, chapter 6 summarizes the conclusions this work has reached, and points future lines of research that appeared as a direct or indirect result.

#### 2 SCALING OF FETS BELOW 100-NM

#### 2.1 CMOS Scaling Challenges

The CMOS transistor can be considered the greatest invention of the 20th century and has revolutionized the field of electronic devices and systems. For the last five decades the transistor has become steadily smaller and the integrated circuit density has increased, which in turn has made it cheaper, more powerful and more efficient. Scaling has doubled the device density in integrated circuits with each generation, as described by Moore's observation (MOORE, 1965).

The length scaling in MOS transistors allows for improvements in both electrical performance and packing density, where a reduction by a factor  $\alpha$  provides a scaling in area equivalent to  $\alpha^2$  (SZE, 1998). Transistor scaling generally followed simple rules: either to maintain the electric field constant or to allow it to increase, but to conserve the shape of the potential profile in the scaled device (LIU; CHANG, 2009). The saturation of the carrier velocities and non scaling of the subtheshold slope and the OFF current forced for more generalized scaling rules (FRANK et al., 2001). Fundamental physical limits, however, have imposed challenges to the scaling trend of MOSFETs (KIM, 2010; ZEITZOFF, 2004).

The parameter non-scaling mentioned above present another difficulty, which slows the voltage reduction trend from one technology node to the next, since the ON/OFF current ration has to be high enough to allow for efficient circuits. Voltage reduction is not attractive for high performance circuits, where the switching time of the CMOS is fundamental. However, if the drain bias remains roughly constant while the other dimensions are scaled, however, the direct and transverse electric fields rise such as to degrade the effective carrier mobility (CHAUDHRY, 2013). A fine balance has to be achieved, thus, where the applied voltages are not low enough in order to still have a adequate ratio of ON/OFF current, but not high enough to cause mobility scattering and hot electron emissions.

The physical dimensions are limited by quantum mechanical tunnelling currents that pass through the various barriers in the transistor when they are sufficiently thin, deteriorating the electrical behaviour of the MOSFET. Tunnelling current through the gate insulator is one of the most restraining limits to scaling. The most commonly used gate insulator, SiO<sub>2</sub>, presents high gate current leakage with thickness of approximately 2nm. If the oxide is kept at this thickness, while the rest of the device scales, the gate capacitance becomes insufficient to properly control the channel region as it shrinks and the source and drain get closer. This in turn increases the effect of DIBL, as the drain bias has increased control over the channel. The solution for the oxide tunnelling issue was to use insulators with higher dielectric constant, which provide the same gate capacitance while increasing the physical insulator thickness. Significant leakage current reductions could be achieved, yet sacrificing interface quality between the dielectric and the body or gate of the device. The surface scattering arising from the use of high-k dielectrics can be then reduced by the use of a mid-gap metal gate such as TiN (CHAU et al., 2004). This

combination of metal gate and high-k dielectric improves the mobility in the channel, compared to using only the dielectric and a conventional poly-Si gate. The association of metal gates and high-k dielectrics are nowadays integrated in several mainstream semiconductor foundries, being an important reason for the scaling of planar CMOS to the current geometries.

To minimize short channel effects in bulk MOSFETs, very high doping concentrations are necessary, in order to reduce the gate-controlled depletion width in the channel. This high doping profile, however, has an effect in raising the value of the threshold voltage  $V_{th}$ , which can be avoided by employing retrograde channel doping (TAUR et al., 1997). The technique of nonuniform doping is difficult to accurately control and very sensible to statistical variability, specially in very small channel lengths. Device-to-device variations arising from the statistical variability of the doping process – known as Random Dopant Fluctuation – cause reliability issues for the integrated circuit (TANG; DE; MEINDL, 1997; ASENOV, 1998; ASENOV, 2007). A very high doping concentration in the MOSFET channel also result in degraded carrier mobilities due to Coulombic scattering, and phonon scattering due to high effective transverse field (LIU; CHANG, 2009).

Figure 2.1: Charge distribution in long and short channel bulk and SOI MOSFETs (THOMAS, 2011).

The need for precisely controlled vertical channel and source/drain doping profiles to suppress SCE can be avoided by physically limiting the thickness of the semiconductor body. The thin body structure decreases the drain/source coupling with the channel and thus improves electrostatic control of the gate over the channel. Silicon-on-insulator wafers are commonly used for this purpose, with body thickness of 10nm or less. A high precision in the physical silicon thickness is necessary, however, in order to achieve controlled electrical characteristics.

Figure 2.2: Cross section of a fully depleted double-gate MOSFET, showing the electric field and depletion charges from both gates and source and drain(THOMAS, 2011).

This ultra thin film is challenging to fabricate and is prone to self heating (SU et al., 1994). The use of a second gate, opposite from the first further improves the gate coupling over the channel, and relaxes the body thinness requirement, so that quantum confinement effects and mobility degradation due to surface scattering can be mitigated. The double-gate structure, first proposed in (Sekigawa; Hayashi, 1984), reduces short channel effects such as DIBL and subthreshold slope due to its better control of the longitudinal electric field generated by the drain (COLINGE, 2008). Fig. 2.1 presents a schematic comparison of the gate control over the channel for long and short channel bulk and SOI MOSFETs. In the short channel bulk device, it can be noted how the source and drain diffusions have a greater influence over the channel, which is mitigated in the fully depleted SOI (FDSOI) counterpart. Fig. 2.2 illustrates how a double-gate transistor has an even improved performance, regarding gate electrostatic control and the influence of the transversal drain electric field over the channel, allowing further scaling.

The main challenge, however, for the adoption of the double gate technology is the fabrication of both gates self-aligned to the source and drain. The gates also have to be perfectly aligned and of the same size, so as to provide high drive current while reducing the parasitic capacitances. Lastly, the two gates have to be connected with a low-resistance path (NOWAK et al., 2004). The final challenge for the adoption of the double gate MOSFET structure is to be compatible with the current fabrication process flow.

#### 2.2 FinFETs

A FinFET (HISAMOTO et al., 1998; HUANG et al., 1999) is a tri- or double-gate semiconductor device with self-aligned source and drain regions and gates aligned to each other. Figure 2.3 shows a schematic of a tri-gate FinFET device with multiple fins, with most relevant lengths and thickness indicated. It is important to note that in a tri-gate FinFET, the channel width is given by  $2H_{fin} + T_{fin}$  for each fin. Typical FinFET devices have several parallel fins. This geometry creates the possibility of increasing the channel width, and thus the current drive, by increasing the silicon film thickness, which controls the  $H_{fin}$ , producing a wider channel in the

Figure 2.3: FinFET device with multiple fins

same device area.

The first FinFET device was fabricated in Berkeley in 1998 (HISAMOTO et al., 1998) called folded-channel MOSFET. The device was later named FinFET (HUANG et al., 1999) due to the fin-like structure of the silicon channel. Ten years before,though, a very similar device, called DELTA had been fabricated (HISAMOTO et al., 1989), only without the hard mask on top of the fin, as proposed by the Berkeley group. Yet, any device with a fin-like body for the channel may be called FinFET. A scanning electron microscope image of a fabricated FinFET is shown in Fig 2.4.

Figure 2.4: Scanning Electron Miscroscope image of a FinFET with multiple fins.

The fabrication of FinFET devices is very similar to the fabrication of conventional planar MOSFETs and holds even greater similarities with SOI devices (XIONG, 2008). The fins are patterned though steps photolithography and etch, the gate dielectric is deposited and the gate electrode is deposited on top of the fins and patterned to assume its correct dimensions. After that the source and drain regions are implanted in a carefully selected angle and the spacers are formed, similarly to planar MOSFETs. Selective epitaxial growth is performed on the fin extensions to reduce the series resistance. Metal via formation and routing follows the same steps as in traditional circuit fabrication. This compatibility with existing CMOS processing is an important reason for the adoption of this layout by the mainstream semiconductor industry and academic community. The most challenging step of the fabrication is the fin etch, which involves patterning through photolithography and etch. A perfectly smooth and uniform sidewall is desired for the fins, to reduce interface traps that degrade mobility and also decrease the variability of the metal gate work function, a factor which has a great influence in the threshold voltage of the device and thus are responsible for performance degradations (HWANG; LI; HAN, 2010; WANG et al., 2011; BELLO et al., 2013; ZIMPECK; MEINHARDT; REIS, 2014). This dependence of the threshold voltage upon the metal gate work function of the FinFET device is caused by the fact that the superior control the gate has upon the channel enables the use of undoped or lightly doped channels. As previously mentioned, lower doping concentrations are desired for better device uniformity and current drive. The threshold voltage is thus controlled essentially by the work function of the metal gate.

Intel has been the first chip maker to adopt the FinFET technology, calling it the Tri-gate Transistor. The first generation of devices is presented in Fig. 2.5a, from the work of (AUTH et al., 2012; AUTH, 2012). The fin width is 8 nm and the fin height is 34 nm, for the 22 nm gate length technology. The rounded fin are likely to reduce corner effects on the electric field, and improve reliability, but also can be due to the difficulty associated to the fin etching process. The tilted sidewalls offer higher mobility for the PMOS device, acording to (AUTH, 2012). Intel has also adopted the technology of bulk FinFET devices, rather than SOI FinFETs, probably because of price constraints. The next technological node, with 14nm gate length transistors is presented in 2.5b, extracted from a presentation of the technology (INTEL, 2014a). The fins have become taller and thinner, with 42nm of fin height, compared to 34nm. The fin pitch also lowered from 60nm to 42nm. The rounded edges is maintained, but the more vertical aspect ratio is clearly seen, which improves the performance and short channel effects control.

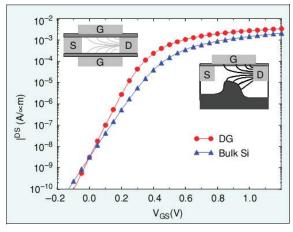

The review presented in (NOWAK et al., 2004), traces a brief comparison between planar bulk devices and double-gate FETs. The devices were simulated in the Taurus MEDICI simulator. Fig. 2.6a compares the  $I_DxV_G$  characteristics for two devices designed to have the same subthreshold current density at  $V_{GS} = 0$ . The slope is clearly steeper in the double-gate device, indicating a better control over short channel effects, and also rendering higher drive currents at lower voltages. A lower  $V_{DD}$  power-supply voltage is possible in such devices. Fig. 2.6b presents both DIBL and subthreshold swing (also referred as subthreshold slope in other parts

(a) TEM image of an 22nm In- (b) TEM image of an 14nm Intel Tri-gate Transistor (AUTH tel Tri-gate Transistor (INTEL, et al., 2012; AUTH, 2012; IN- 2014a) TEL, 2014a)

Figure 2.5: Comparison between Intel aspect ratio and fin pitch of Tri-gate transistors from different technology nodes.

of this work) for bulk single-gate and double-gate devices, for different channel lengths. Both characteristics are improved by the use of a second gate, as clearly shown in the plot. It is important to note the greater increase for DIBL and sub-threshold swing in small geometries single-gate devices. This exponential increase in undesired effects deeply limits the scaling of planar bulk devices beyond existing gate lengths. The simulation results presented in Fig. 2.6b, however, are very optimistic, showing nearly perfect subthreshold swing for FinFETs down to 20nm of effective gate length.

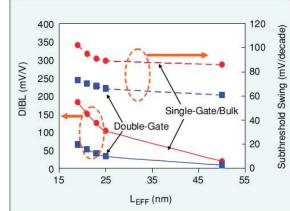

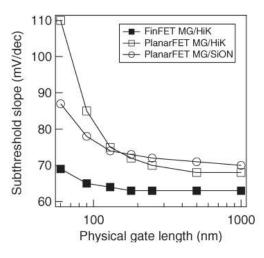

The IMEC Institute created experimental comparisons between planar bulk MOSFETs and SOI FinFETs for electric characteristics and performance in the works of (SUBRAMANIAN et al., 2005) and (SUBRAMANIAN et al., 2006). The FinFETs under study were fabricated on SOI wafers with 145 nm buried oxide thickness. The undoped fin height is 60nm with 25nm of fin thickness. A high-k insulator and TiN metal gate were used. The planar bulk MOSFETs were fabricated with either high-k insulator ("HiK") or SiON and TiN metal gate. Fig. 2.7a illustrates, experimentally, the already mentioned fact that the FinFET devices have superior subthreshold slope, compared to planar bulk devices. The subthreshold slope is nearly the optimal 60 mV/dec in FinFET devices with gate length greater than 100 nm, slightly rising for smaller devices. On the other hand, the planar devices present high sub-hreshold slope even for greater channel lengths, increasing exponentially for gate lengths below 100 nm.

(a)  $I_D x V_G$  curves of double-gate and single-gate devices designed to have equal sub-threshold current density at  $V_{GS} = 0$ .

(b) DIBL and sub-threshold swing for double-gate and bulk planar devices. The double-gate device is designed with undoped body and near mid-gap gate metal.

Figure 2.6: Images removed from (NOWAK et al., 2004)

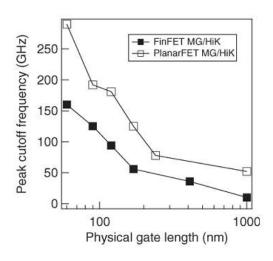

The study also points that the maximum intrinsic cutoff frequency of planar MOSFETs is greater than that of FinFETs, as seen in Fig 2.7b. The cuttof frequency is given by the peak transconductance  $G_{m,max}/2\pi C_{GS}$ , with  $C_{GS}$  the gate-to-source capacitance. Since FinFETs have high series resistance because of the reduced source/drain contact areas, the transconductance is lower than that of planar MOSFETs. The series resistance also increases with decreasing fin width (DIXIT et al., 2005). However, the series resistance issue can be further reduced by selective epitaxial growth of source and drain regions, as shown in (DIXIT et al., 2005; NICOLETTI, 2009).

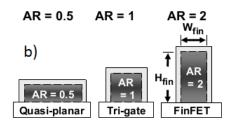

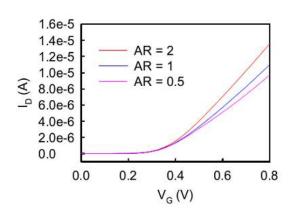

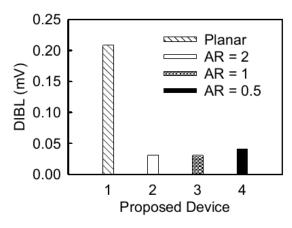

The work presented in (CHENG; LI, 2010) simulates multiple-gate devices with different fin aspect ratios, as explained in Fig. 2.8, and compares its DC and dynamic characteristics. The simulations were performed for 16 nm gate length devices. The height and thickness (mentioned as  $W_{fin}$ ) of the fin for each device are also explained in Fig. 2.8. The drive current of the FinFET device is larger, as illustrated in Fig. 2.9a, mainly because the FinFET presents a larger channel width (=  $2xH_{fin}+W_{fin}$ ), of 80 nm, compared to the 67.8 nm width of the Tri-gate and 64 nm channel width of the Quasi-planar simulated devices. Fig. 2.9b compares the devices regarding the DIBL each of them presents. As previously discussed, DIBL is reduced in multigate devices due to the superior control over the channel. FinFET devices present even smaller DIBL, because the complete volume inversion of the fin improves even further the control over the channel.

A large component of the off-state leakage current is gate-induced drain leakage current – GIDL – a quantum mechanical tunnelling between gate and drain in the drain region underneath the gate, due to high field effect in the drain junction (ROY; MAHMOODI-MEIMAND; MUKHOPADHYAY, 2003). In the accumulation region, the leakage current in mostly due to

- (a) Sub-threshold slope for bulk MOSFETs and FinFETs

- (b) Peak cutoff frequency at  $V_{DS} = 1.2V$

Figure 2.7: Images extracted from (SUBRAMANIAN et al., 2006)

| a)               |     |      |      |

|------------------|-----|------|------|

|                  | AR2 | AR1  | AR05 |

| Lg               | 16  | 16   | 16   |

| H <sub>fin</sub> | 32  | 22.6 | 16   |

| W <sub>fin</sub> | 16  | 22.6 | 32   |

Figure 2.8: Aspect ratios and geometries used in (CHENG; LI, 2010)

GILD. The advantage of thin body and double-gate architectures in reducing GIDL is investigated in (CHOI et al., 2003). It states that double-gate transistors have a better control over GIDL, in comparison to bulk and ultra thin body SOI devices. GIDL also decreases with a thinner silicon body – or fin, in the case of FinFETs – attributed to the lower transversal electric field and increase in tunnelling effective mass.

#### 2.3 LDD Structure

The lightly doped drain (LDD) structure, proposed in (OGURA et al., 1980), is characterized by a lightly doped region n<sup>-</sup> between the channel and the highly doped n<sup>+</sup> source and drain. The LDD device is fabricated using a first step of light doping concentration implant, after the gate stack formation, to create the self-aligned source and drain. The gate spacers are then formed and the source and drain are again implanted, this time with high doping concentrations. The schematic cross section of a LDD device is presented in Fig. 2.10, with n<sup>-</sup> and n<sup>+</sup> regions shown.

- (a) IDxVG curves of FinFET devices with different aspect ratio

- (b) Comparison of DIBL present in planar and FinFET devices with different aspect ratio

Figure 2.9: From the work presented in (CHENG; LI, 2010)

Figure 2.10: Schematic cross section of a LDD planar MOSFET device, as presented in (HU; CHANG; CHIA, 1987)

In a conventional MOSFET, the electric field has its peak near the metallurgical junction of drain and channel, and drops abruptly in the n<sup>+</sup> region. In a LDD device, however, the electric field spreads along the lightly doped region n<sup>-</sup> before becoming zero at the drain, creating a "buffer zone". The magnitude of the peak field is thus lower in the LDD MOSFET, which allows for higher device operation biases, while reducing hot electron emissions and impact ionization. Hot electrons in turn, break molecular bonds and generate interface traps, that are responsible for device degradation and reduction in its lifetime (HU et al., 1985). Thus, LDD structures, when properly designed, can increase device lifetime.

It must be noted, however, that the  $n^-$  region increases the series resistance in the device. Also, part of the lightly doped region is modulated by the gate bias, and thus the series resistance and  $\Delta L$  change as a function of the gate voltage overdrive, as presented in Fig. 2.11 (SHEU et al., 1984; LIANG; DEEN, 1993; HU; CHANG; CHIA, 1987). This creates difficulties in the extraction of those parameters, which will be addressed in Chapter 4.

FinFET devices can be fabricated with LDD structures also, as is the case in (MAGNONE

Figure 2.11: Current flow patterns in a LDD MOSFET. The top picture shows the operation in low  $V_{GS}$  bias, while the bottom is in high  $V_{GS}$  bias. The variation of  $L_{eff}$  is clearly seen in the different biases, as a result of the gate modulation of the  $n^-$  region. (SHEU et al., 1984)

et al., 2008) and the ones fabricated in the IMEC Institute and used in the PhD thesis of (FER-REIRA, 2012) that will be studied in this work. The fabrication of FinFET LDD devices follows the same steps as in planar MOSFETs, with a lightly doping followed by spacers formation and a second implantation, with higher dopant concentration. In FinFETs, however, the implantation angle has to be carefully selected such as to prevent shadowing on the fins. This is extensively discussed in (FERREIRA, 2012).

#### 3 COMPACT DEVICE MODELS

A device model is the interface between the fabrication process and the circuit design. All integrated circuits are designed and verified first in a circuit simulator such as SPICE, HSPICE and SPECTRE, and just then sent to actual fabrication. This simulation is performed using a compact model to describe the behaviour of a given technology. Their accuracy is essential, specially for the design of analog circuits, but also for performance and timing improvements in digital circuits. Compact models have a simplified analytical formulation to determinate the I-V or C-V characteristics of transistor, using a specific set of parameters. They avoid numerical solutions for the device properties by making assumptions that simplify the derivations of an analytical solution. Compact models also have a fine balance between their physical accuracy and their compactness, which is, their simplicity and computational efficiency. Some applications and project phases might use more simple and computationally efficient models, while others might require a higher accuracy in the predicted electrical behaviour.

This work focusses on compact models for double-gate devices, more specifically FinFETs, expanding the work presented in the XXIX South Symposium on Microelectronics. Among the large number of proposed models, the EKV Double-Gate, the BSIM-CMG and the PSP-DGFET were chosen for having planar counterparts already established as default models for different circuit applications. The BSIM-CMG has already been released and is currently integrated in commercial circuit simulators, while the other models are still academic, with some work published, but no official release. In this chapter the features of the models will be briefly reviewed and discussed, and their parameter extraction detailed in the next.

#### 3.1 EKV Double-gate

The EKV related model for double-gate devices (SALLESE et al., 2005; PRÉGALDINY et al., 2006; DIAGNE et al., 2008; CHEVILLON et al., 2009; TANG et al., 2009; YESAYAN et al., 2011) is proposed as a simplified, design-based compact model. It is a charge-based formulation, following the same form of equations as the planar EKV (ENZ; KRUMMENACHER; VITTOZ, 1995). The long channel core model is implemented in VHDL-AMS code in (PRÉGALDINY et al., 2006) and in this work ported to MATLAB and expanded to short channel devices according to the formulation presented in the articles cited above.

The long channel I-V equations are given in normalized forms, in order to simplify the model. The normalized drain current  $i=I/I_S$  is given by:

$$i = -q_m^2 + 2q_m + 2\frac{C_{si}}{C_{ox}} \ln\left(1 - q_m \cdot \frac{C_{ox}}{2C_{si}}\right) \Big|_{q_m S}^{q_{mS}}$$

(3.1)

where the current normalizing factor is

$$I_s = 4C_{ox}U_T^2 \frac{W}{L} \tag{3.2}$$

having

$$W = n_{fin} \left( 2H_{fin} \right) \tag{3.3}$$

with the normalized charge  $q_m = \frac{Q_m}{Q_0}$ , the charge normalizing factor  $Q_0 = 4C_{ox}U_T$  and the mobile charge given by  $Q_m = 2Q_G$ .  $C_{si}$  is the silicon fin capacitance,  $C_{ox}$  the gate dielectric capacitance and  $U_T = \frac{k_B T}{q}$  the thermal voltage, with  $k_B$  the Boltzmann constant, T the temperature in Kelvin and q the electronic charge. The most important point to note regarding the EKV double-gate model is the similarity between this proposal and the planar MOSFET model regarding the normalizing factors (SALLESE et al., 2003). Both  $Q_0$  and  $I_s$  are expressed, in the planar model, as half the value of the double-gate model counterparts. This implies that the formulations of equations for the EKV model assumes that a FinFET device acts essentially as two independent planar devices.

The short channel effects are expressed through the subthreshold slope degradation factor n and the threshold voltage roll off  $\Delta V_{th}$ . The subthreshold slope degradation factor n is given by

$$n = \frac{dv_g}{d\varphi C_{min}} = 1 / \left[ 1 - 2\sinh\left(\alpha_n \cdot \frac{L}{l}\right) / \sinh\left(\frac{L}{l}\right) \right]$$

(3.4)

with

$$l = \sqrt{\frac{\varepsilon_{si} W_{si} t_{OX}}{2\varepsilon_{OX}} \left( 1 + \frac{\varepsilon_{OX} W_{si}}{4\varepsilon_{si} t_{OX}} \right)}$$

(3.5)

where l is the natural length, that controls the subthreshold behaviour for small geometry structures and  $\alpha_n$  is the location of the minimum potential across the channel, and is fixed as 0.6 based on comparisons with 3-D simulations.  $W_{si}$  is the fin thickness, referred in this work as  $T_{fin}$ , which was kept in this style to maintain the original formulation as in (TANG et al., 2009).  $\varepsilon_{si}$  and  $\varepsilon_{OX}$  are the silicon and dielectric relative permittivity, respectively.

The threshold voltage roll off is modelled based on SCE and DIBL parameters as

$$\Delta v_{th} = 2\gamma_{SCE} \left( v_{bi} - \phi_f - v_{to} \right) + \gamma_{DIBL} v_{ds} \tag{3.6}$$

where  $v_{bi}$  is the built in potential between the source and the silicon body,  $\phi_f$  is the normalized Fermi potential,  $v_{to}$  is the normalized threshold potential for the long channel device, and  $v_{ds}$  the normalized voltage between drain and source. The generic relationship for  $\gamma$  is valid for both SCE and DIBL  $\alpha$  parameters, as

$$\gamma_i = \frac{1}{\alpha_{i1} \cosh\left(\frac{\alpha_{i2}L}{l}\right)} + \alpha_{i3} \left\{ 1 - 0.00055 \left[ (L - 100) + \sqrt{(L - 100)^2} \right] \right\}$$

(3.7)

for i = SCE or DIBL.

The threshold voltage roll off is integrated into the calculation of the normalized drain current by changing the charge calculation function to

$$qm_0 = f(v_{qs}, v_{d,s}) \text{ and } qm = f(v_{qs} - \Delta v_{th}, v_{d,s})$$

(3.8)

and the subthreshold slope degradation n is used to define

$$v = \frac{v_{gs} - v_{to}}{n} - v_{d,s} \tag{3.9}$$

which is in turn used to calculate the normalized charge, as defined in (PRÉGALDINY et al., 2006). In strong inversion, which is expressed by the quadratic charge term of the drain current, the value of n is set to 1 to prevent errors.

The new relationship for the drain current is thus given by

$$i = -q_{m0}^{2}(v_{gs}, v_{ch}) + 2(v_{gs} + \Delta v_{th}, v_{ch}) + 2\frac{C_{si}}{C_{ox}} \ln\left(1 - q_{m}(v_{gs} + \Delta v_{th}, v_{ch}) \cdot \frac{C_{ox}}{2C_{si}}\right)\Big|_{q_{mD}}^{q_{mS}}$$

(3.10)

where  $v_{ch} = v_d$  for  $q_{mD}$  and  $v_{ch} = v_s$  for  $q_{mS}$ .

The model assumes that the mobility is kept constant, which cannot be proven for real devices with narrow fins, specially when several scattering parameters act simultaneously (GÁMIZ; GODOY, 2008). The simplistic modelling is more focused on designer accessibility than on physical correctness, even though the group calls it a *physics-based model* (YESAYAN et al., 2011).

#### 3.2 BSIM-CMG

The BSIM-CMG was formulated in (DUNGA et al., 2007; DUNGA, 2008; DUNGA et al., 2008) and afterwards expanded in (LU et al., 2010; LU, 2011; CHAUHAN et al., 2011). As a surface potential-based model, the currents, charges and capacitances are obtained after the surface potentials at the source and drain are calculated. Its structure is illustrated in Fig. 3.1, presented in (PAYDAVOSI et al., 2013). The core model is formulated for a long channel double-gate device. Gate poly depletion (PDE), quantum mechanical (QME) and short channel effects (SCE) are introduced in this core model, while the other real device effects are used in the carrier transport equations. In order to correctly model the devices behaviour and the mentioned effects, the BSIM-CMG has over 150 parameters, divided in device and process parameters, model controllers, physical parameters such as velocity saturation and DIBL, scaling parameters for the correct modelling of the length dependent quantities, and fitting or smoothing parameters. With all the effects considered, the BSIM-CMG qualifies less as a compact model

and more as a semi-empiric model, with a large parameter set to describe currents and charges.

Figure 3.1: Simplified structure of the BSIM-CMG model, from (PAYDAVOSI et al., 2013)

The model is based on surface potential calculations to obtain the device behaviour. This is an important change of formulation from the early planar models of the BSIM family, that were based on the threshold voltage and employed smoothing functions (SHEU et al., 1987). This design decision is done in order to have continuous and smooth equations for all the operation regions.

The I-V model of the BSIM-CMG, after derivation of the Poisson's equation is given by

$$I_d = \mu \frac{W_{eff}}{L} [f(\psi_{s,s}) - f(\psi_{s,d})]$$

(3.11)

where the terms  $f(\psi_{s,s})$  and  $f(\psi_{s,d})$  are expressed as