UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

JEFERSON SANTIAGO DA SILVA

Architectural Exploration of Digital Systems Design for FPGAs Using C/C++/SystemC Specification Languages

> Thesis presented in partial fulfillment of the requirements for the degree of Master in Computer Science

Prof. Dr. Sergio Bampi Advisor

Porto Alegre, January 2015

da Silva, Jeferson Santiago

Architectural Exploration of Digital Systems Design for FP-GAs Using C/C++/SystemC Specification Languages / Jeferson Santiago da Silva. – Porto Alegre: PPGC da UFRGS, 2015.

83 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2015. Advisor: Sergio Bampi.

1. High-level Synthesis. 2. FPGA. 3. Design Space Exploration. 4. Digital Design. 5. Optimization Techniques. I. Bampi, Sergio. II. Architectural Exploration of Digital Systems Design for FPGAs Using C/C++/SystemC Specification Languages.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento Diretor do Instituto de Informática: Prof. Luís da Cunha Lamb Coordenador do PPGC: Prof. Luigi Carro Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"Best remain silent and be thought a fool, than open your mouth and remove all doubt." — ABRAHAM LINCOLN

## ACKNOWLEDGMENTS

I would like to thank all my family, specially to my wife Clara. I want to thank Prof. Bampi, my advisor in this work. My thanks also go to all staff of PPGC, including professors and administrative personnel.

### ABSTRACT

The increasing demand for high computational performance and massive data processing has driven the development of systems-on-chip. One implementation target for complex digital systems are FPGA (Field-programmable Gate Array) devices, heavily used for prototyping systems or complex and fast time-to-market electronic products development. Certain inefficient aspects of FPGA devices relate to performance and power degradation with respect to custom hardware design.

In this context, this master thesis proposes a survey on FPGA optimization techniques. This work presents a literature review on methods of power and area reduction applied to FPGA designs. Techniques for performance increasing and design speedup enhancing will be presented based on classic and state-of-the-art academic works. The main focus of this work is to discuss high-level design techniques and to present the results obtained in synthesis examples we developed, comparing with hand-coded HDL (Hardware Description Language) designs.

In this work we present our methodology for fast digital design development using High-Level Synthesis (HLS) environments. Our methods include efficient high-level code partitioning for proper synthesis directives exploration in HLS tools. However, a non-guided HLS flow showed poor synthesis results when compared to hand-coded HDL designs. To fill this gap, we developed an iterative design space exploration method aiming at improving the area results. Our method is described in a high-level script language and it is compatible with the Xilinx Vivado<sup>TM</sup> HLS compiler. Our method is capable of detecting optimization checkpoints, automatic synthesis directives insertion, and check the results aiming at reducing area consumption.

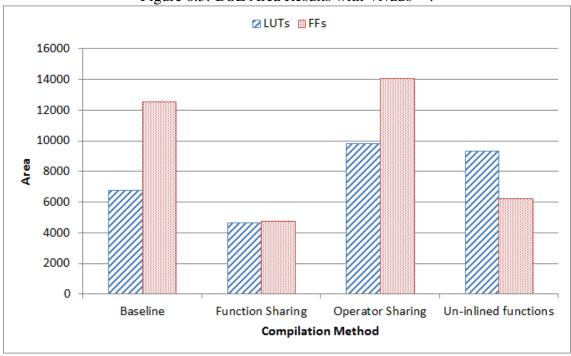

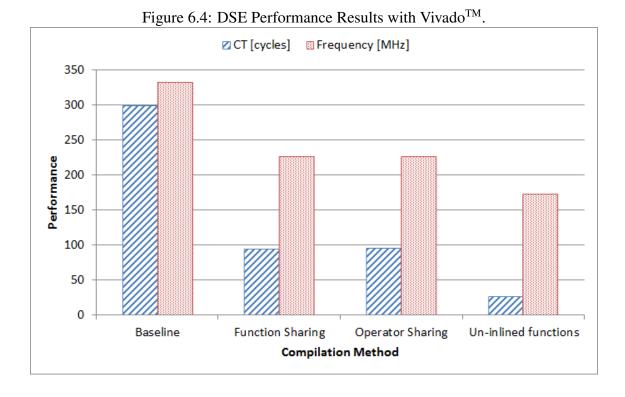

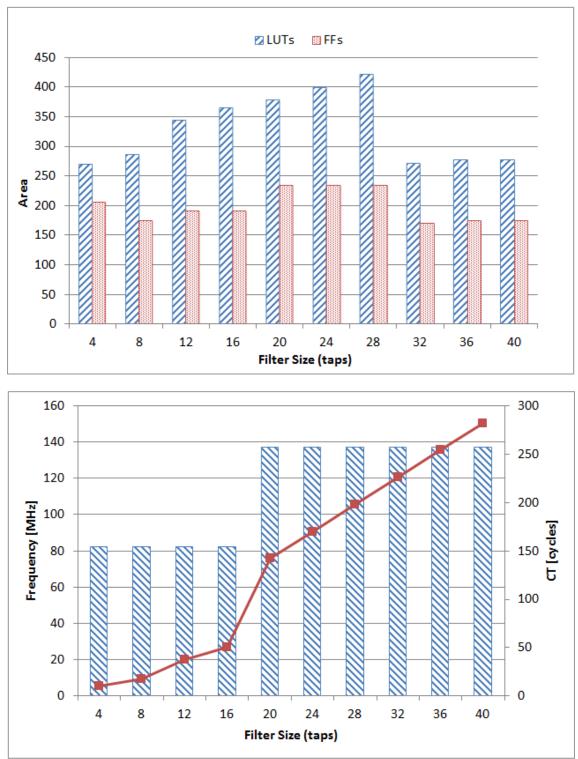

Our Design Space Exploration (DSE) experimental results proved to be more efficient than non-guided HLS design flow by at least 50% for a VLIW (Very Long Instruction Word) processor and 62% for a 12<sup>th</sup>-order FIR (Finite Impulse Response) filter implementation. Our area results in terms of flip-flops were up to 4X lower compared to a non-guided HLS flow, while the performance overhead was around 38%, for the VLIW processor compilation. In the FIR filter example, the flip-flops reduction were up to 3X, with no relevant LUTs and performance overhead.

**Keywords:** High-level Synthesis, FPGA, Design Space Exploration, Digital Design, Optimization Techniques.

#### Exploração Arquitetural no Projeto de Sistemas Digitais para FPGAs Utilizando Linguagens de Especificação C/C++/SystemC

### RESUMO

A crescente demanda por alto desempenho computacional e massivo processamento de dados tem impulsionado o desenvolvimento de sistemas-on-chip. Um dos alvos de implementação para sistemas digitais complexos são os dispositivos FPGA (*Field-programmable Gate Array*), muito utilizados para prototipação de sistemas e rápido desenvolvimento de produtos eletrônicos complexos. Certos aspectos ineficientes relacionados aos dispositivos FPGA estão relacionadas com degradação no desempenho e na potência consumida em relação ao projeto de hardware customizado.

Neste contexto, esta dissertação de mestrado propõe um estudo sobre técnicas de otimização em FPGAs. Este trabalho apresenta uma revisão da literatura sobre os métodos de redução de potência e área aplicados ao projeto de FPGA. Técnicas para aumento de desempenho e aceleração do tempo de desenvolvimento de projetos são apresentadas com base em referencias clássicas e do estado-da-arte. O principal foco deste trabalho é discutir sobre as técnicas de alto nível e apresentar os resultados obtidos nesta área, comparando com os projetos HDL (*Hardware Description Language*) codificados a mão.

Neste trabalho, é apresentado uma metodologia para o desenvolvimento rápido projetos digitais utilizando ambientes HLS (*High-Level Synthesis*. Estes métodos incluem eficiente particionamento de código de alto nível, para a correta exploração de diretivas de síntese em ferramentas HLS. Porém, o fluxo HLS não guiado apresentou pobres resultados de síntese quando comparado com modelos HDL codificado a mão. Para preencher essa lacuna, foi desenvolvido um método iterativo para exploração de espaço de projeto com o objetivo de melhorar os resultados de área. Nosso método é descrito em uma linguagem de script de alto nível e é compatível com o Vivado<sup>TM</sup> HLS Compiler. O método proposto é capaz de detectar pontos chave para otimização, inserção automatica de diretivas síntese e verificação dos resultados com objetivo de reduzir o consumo de área.

Os resultados experimentais utlizando o método de DSE (*Design Space Exploration*) provaram ser mais eficazes que o fluxo HLS não guiado, em ao menos 50% para um processador VLIW e em 43% para um filtro FIR (*Finite Impulse Response* de 12<sup>a</sup> ordem. Os resultados em área, em termos de flip-flops, foram até 4X menores em comparação com o fluxo HLS não guiado, enquanto redução no desempenho ficou em cerca de 38%, no caso do processador VLIW. No exemplo do filtro FIR, a redução no número flip-flops chegou a 3X, sem relevante aumento no número de LUTs e redução no desempenho.

**Palavras-chave:** Síntese de Alto Nível, FPGA, Exploração de Espaço de Projeto, Sistemas Digitais, Técnicas de Otimização.

## LIST OF ABBREVIATIONS AND ACRONYMS

| ABEL | Advanced Boolean Expression Language              |  |

|------|---------------------------------------------------|--|

| ABL  | A Block diagram Language                          |  |

| ALU  | Arithmetic and Logic Unit                         |  |

| ANSI | American National Standards Institute             |  |

| APL  | A Programming Language                            |  |

| ASIC | Application-Specific Integrated Circuit           |  |

| CE   | Clock Enable                                      |  |

| CMOS | Complementary Metal-Oxide-Semiconductor           |  |

| СТ   | Compute Time                                      |  |

| CPU  | Central Processing Unit                           |  |

| CUDA | Compute Unified Device Architecture               |  |

| DSE  | Design Space Exploration                          |  |

| DDDG | Dynamic Data Dependence Graphs                    |  |

| DSP  | Digital Signal Processing                         |  |

| EDA  | Electronic Design Automation                      |  |

| FF   | Flip-flop                                         |  |

| FIR  | Finite Impulse Response                           |  |

| FPGA | Field-Programmable Gate Array                     |  |

| FSM  | Finite State Machine                              |  |

| GIMP | GNU Image Manipulation Program                    |  |

| GPU  | Graphic Processing Unit                           |  |

| HDL  | Hardware Description Language                     |  |

| HLS  | High-Level Synthesis                              |  |

| HW   | Hardware                                          |  |

| IC   | Integrated Circuit                                |  |

| IEEE | Institute of Electrical and Electronics Engineers |  |

| ISP    | Instruction Set Processing                         |  |

|--------|----------------------------------------------------|--|

| JPEG   | Joint Photographic Experts Group                   |  |

| LDMC   | Logic Delay Measurement Circuit                    |  |

| KARL   | Kaiserslautern RTL                                 |  |

| LE     | Logic Element                                      |  |

| LUT    | Look-up Table                                      |  |

| MAC    | Multiply and Accumulate                            |  |

| MIPS   | Microprocessor without Interlocked Pipeline Stages |  |

| MPEG   | Moving Picture Experts Group                       |  |

| OpenCL | Open Computing Language                            |  |

| PLL    | Phase-locked loop                                  |  |

| QoR    | Quality of Results                                 |  |

| RAM    | Random Access Memory                               |  |

| RISC   | Reduced Instruction Set Computer                   |  |

| RTL    | Register-Transfer Level                            |  |

| SDK    | Software Development Kit                           |  |

| SRAM   | Static RAM                                         |  |

| SW     | Software                                           |  |

| TCL    | Tool Command Language                              |  |

| Vex    | VLIW Example                                       |  |

| VLIW   | Very Long Instruction Word                         |  |

| VHDL   | VHSIC HDL                                          |  |

| VHSIC  | Very-High-Speed IC                                 |  |

|        |                                                    |  |

## LIST OF SYMBOLS

- $\alpha$  Switching Rate

- C Capacitance

- f Operation Frequency

- V<sub>dd</sub> Power-Supply Voltage

- $\tau_{DN}$  Wire Delay

- L Wire Length

- c Capacitance of a Wire per Unit Area

- r Sheet Resistance of a Wire ( $\Omega$ /square)

- $\rho$ -Vex Reconfigurable Vex Processor

# **LIST OF FIGURES**

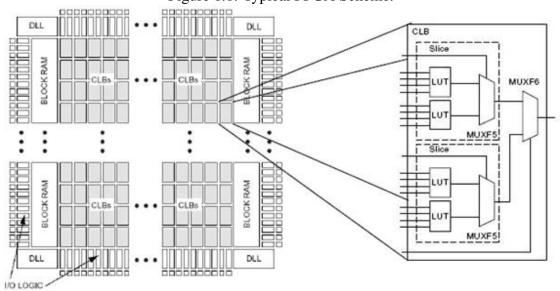

| Typical FPGA Scheme.                                                | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

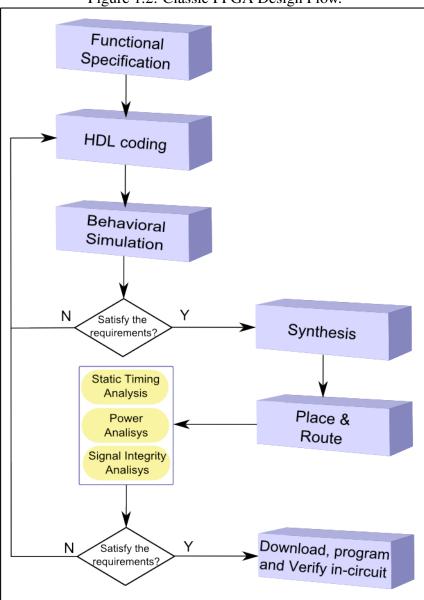

| Classic FPGA Design Flow                                            | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

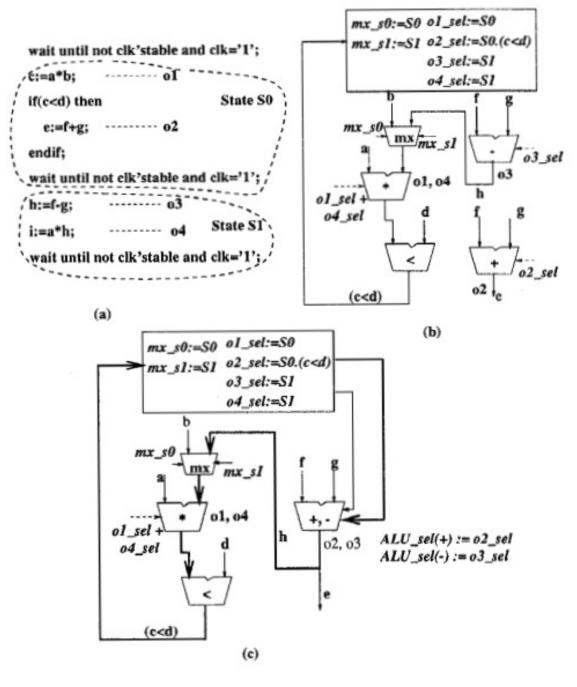

| Resource Sharing. a) Behavioural description. b) Data and Control   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| , i C                                                               | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

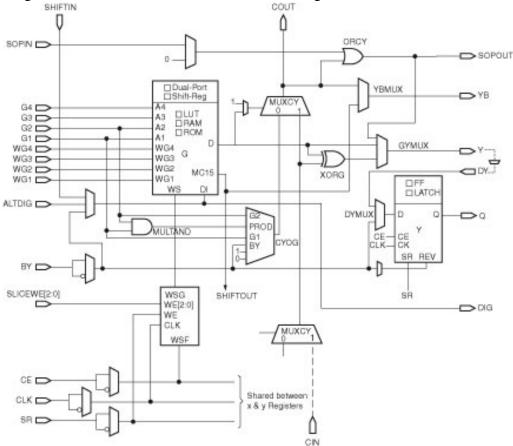

| -                                                                   | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Gated Clock Circuits: a) Falling edge. b) Rising edge               | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LDCM scheme proposed in (CHOW et al., 2005)                         | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Four issue VLIW scheme.                                             | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Fan-out Reduction Circuit (N = 2)                                   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Verilog Implementation for a D-FF.                                  | 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VHDL Implementation for a D-FF.                                     | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SystemC Implementation for a D-FF.                                  | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

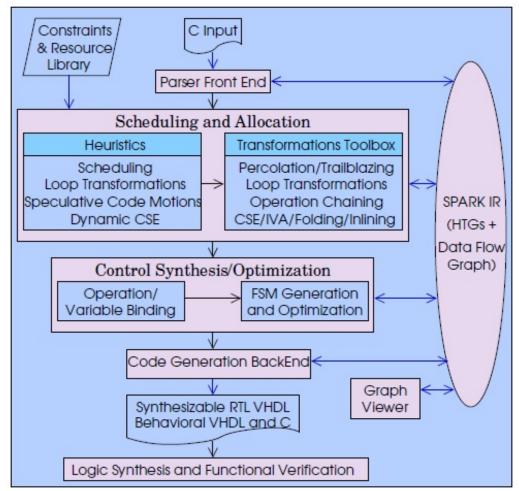

| SPARK Design Flow.                                                  | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

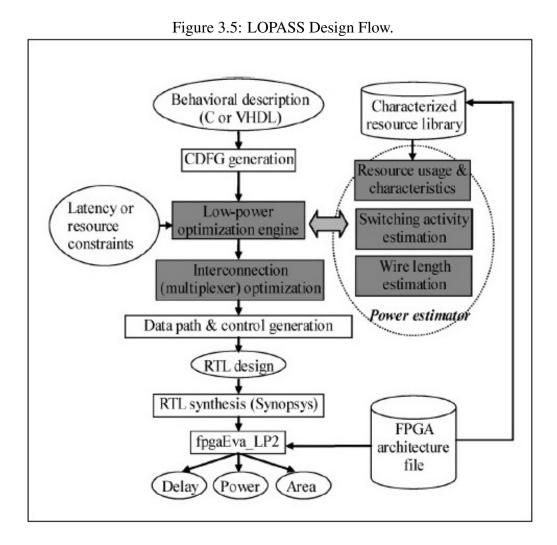

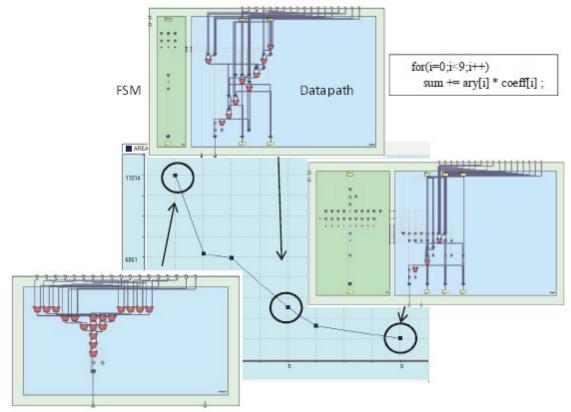

|                                                                     | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

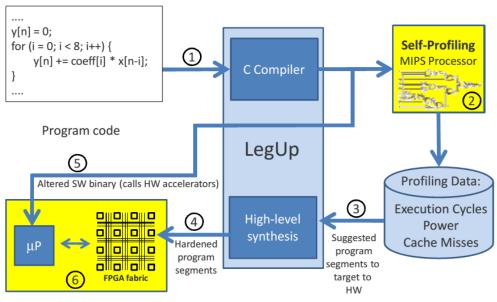

|                                                                     | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

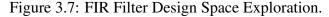

|                                                                     | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                     | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

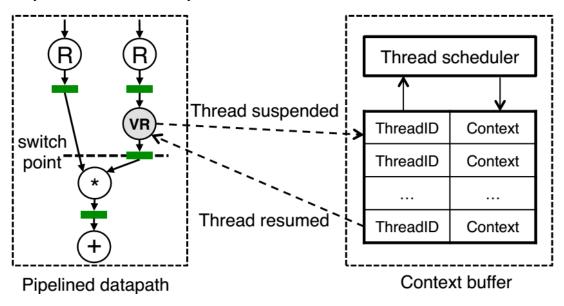

| an variable latency for an external memory access                   | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

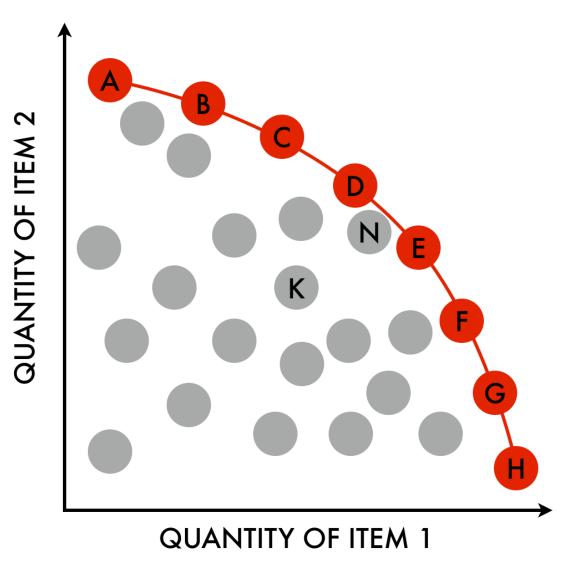

| Pareto Curve.                                                       | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

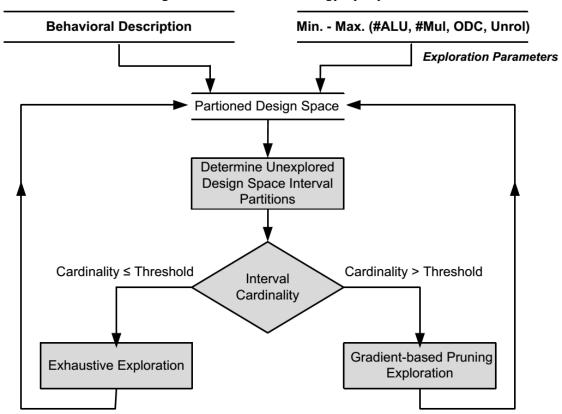

|                                                                     | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

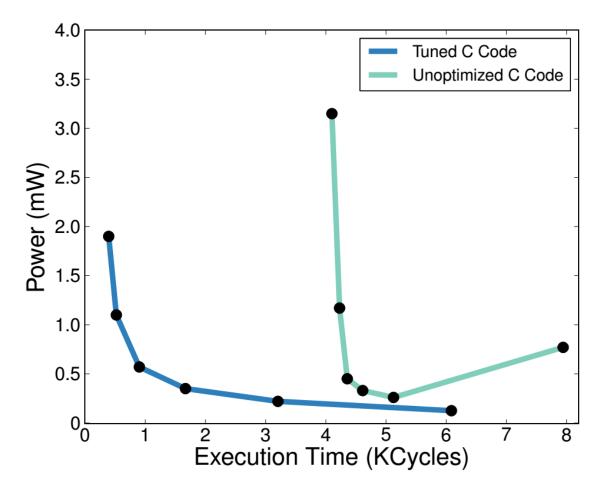

| Tuned and Untuned C code comparison.                                | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Code transformation example: Original code, on left. On right, code |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                     | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

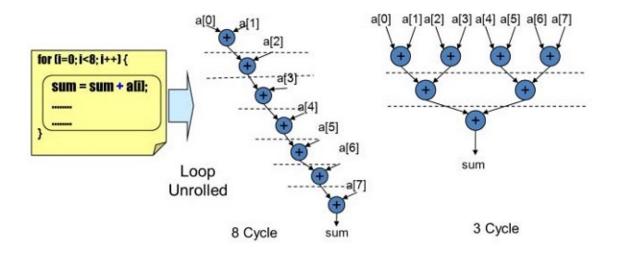

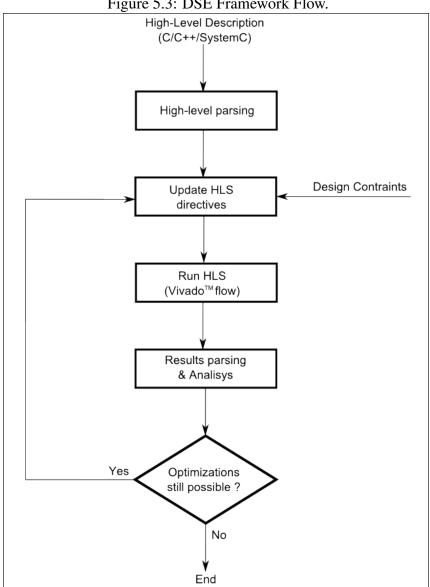

|                                                                     | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Example Code for ALU operation.                                     | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Square Root Algorithm Pseudo-code.                                  | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1 6                                                                 | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| formance Versus Filter Size Curve.                                  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                     | Classic FPGA Design Flow.<br>Resource Sharing. a) Behavioural description. b) Data and Control<br>Path. c) Data and Control Path with Sum/Sub Operations Merged .<br>Internal Architecture of a FPGA Logic Element inside Virtex <sup>TM</sup> 5.<br>Gated Clock Circuits: a) Falling edge. b) Rising edge.<br>LDCM scheme proposed in (CHOW et al., 2005).<br>Four issue VLIW scheme.<br>Fan-out Reduction Circuit (N = 2).<br>Verilog Implementation for a D-FF.<br>SystemC Implementation.<br>LoPASS Design Flow.<br>LegUp Design Flow.<br>FIR Filter Design Space Exploration.<br>Loop Unrolling. a) Loop Pseudo-code. b) Unrolled Data Flow. c)<br>Tree Reduction Structure.<br>Kernel Graph. R represents a memory reading while VR represents<br>an variable latency for an external memory access.<br>Pareto Curve.<br>DSE methodology by Xydis.<br>Tuned and Untuned C code comparison.<br>Code transformation example: Original code, on left. On right, code<br>partitioned.<br>Code Snippet Example of a VLIW Implementaion.<br>DSE Framework Flow.<br>Example Code for ALU operation.<br>Square Root Algorithm Pseudo-code.<br>FIR Filter Pseudo-code.<br>DSE Area Results with Vivado <sup>TM</sup> .<br>DSE Performance Results with Vivado <sup>TM</sup> .<br>Multiple Size FIR Filters. a) Area Versus Filter Size Curve. b) Per- |

# LIST OF TABLES

| 3.1 | Hardware Design Domains and Abstraction Levels                                    | 28 |

|-----|-----------------------------------------------------------------------------------|----|

| 3.2 | Differences between C/C++ and SystemC.                                            | 30 |

| 6.1 | MIPS Implementation Comparison.                                                   | 47 |

| 6.2 | Square Root Algorithm Implementation Comparison.                                  | 48 |

| 6.3 | $\rho$ -Vex Synthesis Results Using LegUp Compiler                                | 49 |

| 6.4 | $\rho$ -Vex Synthesis Results Using Vivado <sup>TM</sup> HLS                      | 49 |

| 6.5 | Synthesis Results for FIR Filter Example: Target Altera Cyclone <sup>TM</sup> IV. | 50 |

| 6.6 | Synthesis Results for FIR Filter Example: Target Xilinx Spartan <sup>TM</sup> 6   |    |

|     | and Xilinx Virtex <sup>TM</sup> II.                                               | 51 |

| 6.7 | DSE Framework Results: VLIW processor.                                            | 54 |

| 6.8 | DSE Framework Results: FIR Filter.                                                | 55 |

| 6.9 | Synthesis Results for Multiple Order FIR Filter Example                           | 55 |

# CONTENTS

| 1     | INTRODUCTION                                                          | 14 |

|-------|-----------------------------------------------------------------------|----|

| 1.1   | Motivation                                                            | 15 |

| 1.2   | Contributions                                                         | 16 |

| 1.3   | Thesis Organization                                                   | 16 |

| 2     | HARDWARE DESIGN OPTIMIZATION TECHNIQUES                               | 18 |

| 2.1   | Area Saving Methods                                                   | 18 |

| 2.2   | Power Saving Methods                                                  | 18 |

| 2.3   | Performance Enhancing Methods                                         | 21 |

| 2.4   | Hardware Optimization Methods Summary                                 | 23 |

| 3     | METHODS TO REDUCE DESIGN TIME                                         | 25 |

| 3.1   | Evolution of Hardware Description Languages                           | 25 |

| 3.2   | High-Level Synthesis Tools                                            | 28 |

| 3.3   | High-level Optimization Techniques                                    | 32 |

| 3.4   | HLS tools and Methods Summary                                         | 34 |

| 4     | DESIGN SPACE EXPLORATION IN HARDWARE SYSTEMS                          | 36 |

| 4.1   | Introduction                                                          | 36 |

| 4.2   | Architectural Exploration                                             | 36 |

| 4.3   | Conclusions                                                           | 39 |

| 5     | METHODOLOGY PROPOSED FOR ARCHITECTURAL EXPLORATION                    | 40 |

| 5.1   | High-Level Code Tuning                                                | 40 |

| 5.2   | Iterative Design Space Exploration Method with High-level Synthesis . | 42 |

| 5.2.  | 1 High-level Design Entry                                             | 42 |

| 5.2.2 | 0                                                                     | 42 |

| 5.2.  |                                                                       | 44 |

| 5.2.4 | <u>T</u>                                                              | 44 |

| 5.2.  |                                                                       | 45 |

| 5.3   | Methodology Summary                                                   | 45 |

| 6     |                                                                       | 46 |

| 6.1   | High-Level Synthesis Tools and Design Methods Comparison Results      | 46 |

| 6.1.  | 1                                                                     | 46 |

| 6.1.  |                                                                       | 47 |

| 6.1.  |                                                                       | 48 |

| 6.1.4 | 4 $12^{\text{th}}$ -order FIR Filter                                  | 49 |

| <b>6.2</b><br>6.2.1<br>6.2.2 | Design Space Exploration Results                                                                                                                                         | 51<br>51<br>53 |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 7 C                          | ONCLUSIONS                                                                                                                                                               | 57             |

| REFE                         | RENCES                                                                                                                                                                   | 59             |

| APPE                         | ENDIX A RESUMO DA DISSERTAÇÃO "ARCHITECTURAL EXPLO-<br>RATION OF DIGITAL SYSTEMS DESIGN FOR FPGAS US-<br>ING C/C++/SYSTEMC SPECIFICATION LANGUAGES"                      | 63             |

| A.1                          | Introdução                                                                                                                                                               | 63             |

| A.1.1                        | Motivação                                                                                                                                                                | 64             |

| A.1.2                        | Contribuições                                                                                                                                                            | 64             |

| A.1.3                        | Organização da Dissertação                                                                                                                                               | 65             |

| A.2                          | Resumo das Contribuições da Dissertação: Exploração Arquitetural no<br>Projeto de Sistemas Digitais para FPGAs Utilizando Linguagens de Es-<br>pecificação C/C++/SystemC | 65             |

| A.3                          | Conclusões                                                                                                                                                               | 66             |

| APPE                         | ENDIX B VLIW PROCESSOR SOURCE CODES                                                                                                                                      | 68             |

| <b>B.1</b>                   | C-code Design Entry                                                                                                                                                      | 68             |

| B.1.1                        | Constants Definitions (r_vex.h)                                                                                                                                          | 68             |

| B.1.2                        | Instruction Memory (r_vex_imem.h)                                                                                                                                        | 71             |

| B.1.3                        | Branches and Memory Access Functions (r_vex_fun.h)                                                                                                                       | 72             |

| B.1.4                        | Functions Prototype (r_vex_top.h)                                                                                                                                        | 73             |

| B.1.5                        | $\rho$ -Vex Processor Core (r_vex_top.c)                                                                                                                                 | 73             |

| B.1.6                        | $\rho$ -Vex Processor Testbench (r_vex_tb.h)                                                                                                                             | 82             |

| <b>B.2</b>                   | Synthesis Directives Generated by DSE Script (directives.tcl)                                                                                                            | 83             |

### 1 INTRODUCTION

FPGA devices are widely used for faster implementation of digital functions in hardware and for ASIC (Application-Specific Integrated Circuit) emulation. However, even state-of-the-art FPGAs have serious limitations in terms of performance, area utilization and power consumption. With the increasing complexity of digital systems, optimization techniques must be performed to make digital projects with these devices competitive.

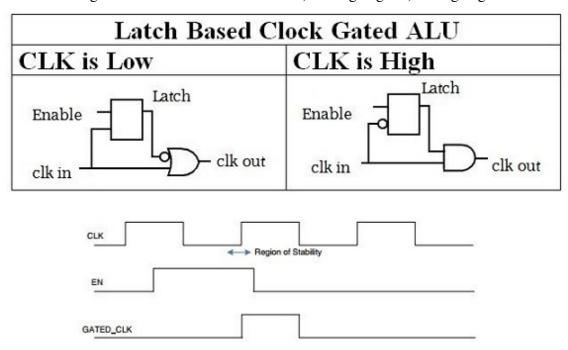

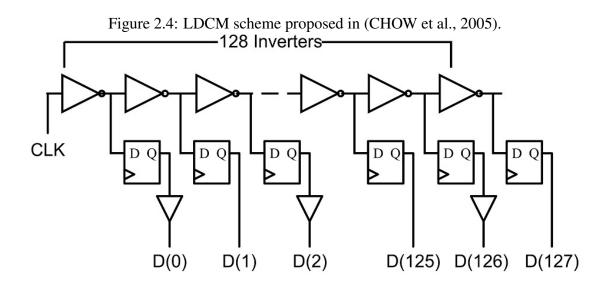

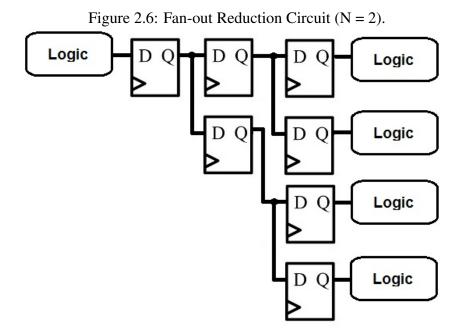

In this work we discuss the most common techniques available in the literature targeting FPGA design optimization. These methods include power savings such techniques as clock gating and frequency/voltage scaling. In terms of area, we will discuss the importance of resource sharing. For performance enhancing, techniques such as pipelining, parallelism and fan-out reduction will be reviewed.

The main purpose of this master thesis is to discuss and to explore high-level design optimization techniques applied to FPGA systems. The Register-Transfer Level (RTL) design is the project schedule bottleneck in digital systems design. HLS (High-Level Synthesis) methods and utilization will be discussed for fast turn-around purpose. Commercial and academic HLS tools will be presented, as well as, advanced design techniques using high-level specification languages, for example C/C++ or SystemC.

Many algorithm standards are open-source available in high-level languages, such as C. In the classic FPGA design flow, hardware designers must to translate these algorithms onto FPGA hardware performing all steps of optimization using register-transfer level languages. RTL development and verification is a complex and expensive task when compared to software implementations. Higher level abstractions allow software designers to develop FPGA hardware using HLS compilers. HLS tool providers affirm that for the certain test-cases, the productivity can be increased up to 50% using HLS methods compared to hand-coded RTL design. The addition of directives/pragmas in the HLS compilers allows the designers to guide the algorithm implementation for a specific design trade-off, for example, performance or area reduction. The verification process in a RTL based flow is very hard due to limitations of HDL languages in describing the real world circuit behaviour, while using higher abstraction languages it is possible to emulate the operation conditions. Moreover, a RTL simulation can take several hours, even days depending of circuit complexity, which normally requires powerful simulation servers.

In this context, this work presents a methodology for digital design using high-level languages through HLS design flow. We explore techniques of code partitioning and pragmas insertion targeting Quality of Results (QoR) improvement. In our work, we developed an iterative method for wide design space exploration with HLS aiming at area reduction. Our method proves to be very effective when compared to a non-guided HLS design flow, being up to 50% more efficient, using an academic VLIW processor as design benchmark.

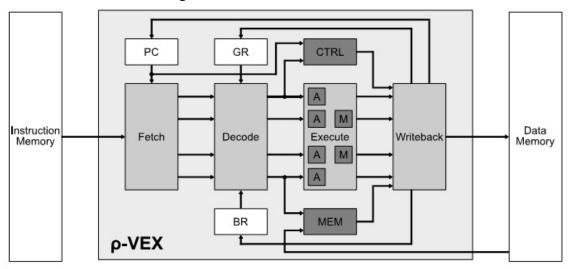

#### 1.1 Motivation