# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

ERIK SCHÜLER

# THREE DIFFERENT TECHNIQUES TO COPE WITH RADIATION EFFECTS AND COMPONENT VARIABILITY IN FUTURE TECHNOLOGIES

Porto Alegre 2007

ERIK SCHÜLER

# THREE DIFFERENT TECHNIQUES TO COPE WITH RADIATION EFFECTS AND COMPONENT VARIABILITY IN FUTURE TECHNOLOGIES

Tese de doutorado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica (PPGEE), da Universidade Federal do Rio Grande do Sul (UFRGS), como parte dos requisitos para a obtenção do título de Doutor em Engenharia Elétrica.

Área de concentração: Automação e Instrumentação Eletro-Eletrônica

ORIENTADOR: Prof. Dr. Luigi Carro

Porto Alegre 2007

#### ERIK SCHÜLER

## THREE DIFFERENT TECHNIQUES TO COPE WITH RADIATION EFFECTS AND COMPONENT VARIABILITY IN FUTURE TECHNOLOGIES

Esta tese foi julgada adequada para a obtenção do título de Doutor em Engenharia Elétrica e aprovada em sua forma final pelo Orientador e pela Banca Examinadora.

Orientador:

Prof. Dr. Luigi Carro, UFRGS Doutor pelo Programa de pós-graduação em Ciência da Computação. Universidade Federal do Rio Grande do Sul, Brasil

Banca Examinadora:

Prof. Dr. Fernando Abel Silveira Noguerol, Universidade de La República Doutor pela Université Catholique de Louvain, Bélgica

Prof. Dr. Antonio Petraglia, Universidade Federal do Rio de Janeiro. Doutor pela University of California, EUA

Prof. Dra. Fernanda Lima Kastensmidt, Universidade Federal do Rio Grande do Sul Doutora pela Universidade Federal do Rio Grande do Sul, Brasil

Prof. Dr. Altamiro Amadeu Susin, Universidade Federal do Rio Grande do Sul Doutor pelo Institut National Polytechnique de Grenoble, França

Prof. Dr. Gilson Ignácio Wirth, Universidade Federal do Rio Grande do Sul Doutor pela Universität Dortmund, Alemanha

Coordenador do PPGEE: \_\_\_\_\_

Prof. Dr. Marcelo Soares Lubaszewski

Porto Alegre, Outubro de 2007.

### **DEDICATORY**

Dedicated to my parents Érico and Isolda for everything. To my wife Carolina for being her. To my sister Ingrid for the friendship and, of course, for Lucca. To my grandmother Ezelinda for her prayers. They say we can not choose our relatives: I guess I am the luckiest person in the world for those I have. Specially dedicated to the memory of my cousin Caco, who introduced me to the electronic when we were just kids. I do miss those times and him.

#### ACKNOWLEDGEMENT

I would like to acknowledge the PPGEE-UFRGS – *Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal do Rio Grande do Sul*, which supported the development of this work and provided the necessary infrastructure, including auxiliary financial support. Special thanks to Miriam Rosek, secretary of PPGEE.

I do acknowledge CAPES - *Coordenação de Aperfeiçoamento de Pessoal de Nível Superior*, which provided scholarship for the development of this thesis both in Brazil and during my excellent and very fruitful stay in France.

Thanks to the professors of the board of examiners for having accepted our invitation and to the professors of the PPGEE-UFRGS and PPGC-UFRGS – *Programa de Pós-Graduação em Computação da UFRGS*, for sharing their knowledge.

Special thanks to Maria Augusta Nunes Neto (Guta), Daniel and Renata Mesquita and Julien Dalmasso for their help in making our arrival and stay in France even better.

Three laboratories were involved during the development of this thesis: LaProT – *Laboratório de Prototipação e Testes*, LaPSI – *Laboratório de Processamento de Sinais e Imagens*, both at the Electrical Engineering Department at UFRGS, and LIRMM – *Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier*, which belongs to the University of Montpellier II, in France. I have made very good friends in all of them, who helped in this work directly or indirectly. Sorry if a miss someone: Adão, Adriane, Álisson, Borin, Balen, Carla, Hermes, Giancarlo, Josias, Letícia, Marcos, Negreiros and Rhod. I would like to stand out two guys who gave a very important contribution for this work: Daniel Scain Farenzena and Marcelo Ienczczak Erigson.

Thanks to Pascal Nouet, my friend and co-advisor in France, for his valuable suggestions. To Luigi Carro, my advisor, my very special acknowledgement. We have done a lot of work during these seven years, since I was a scholarship holder. Thank you for trusting me, for guiding me during all these years of study and for your very good friendship.

Finally, I do must acknowledge my family for all the support I had. Although spread in this big country, they have always helped me whenever necessary. To my family in Rio de Janeiro, Porto Alegre and Veranópolis, my best regards, and to my wife and her family, I just could not ask for more.

### RESUMO

Existe um consenso de que os transistores CMOS irão em breve ultrapassar a barreira nanométrica, permitindo a inclusão de um enorme número desses componentes em uma simples pastilha de silício, mais ainda do que a grande densidade de integração vista atualmente. Entretanto, também tem sido afirmado que este desenvolvimento da tecnologia trará juntamente conseqüências indesejáveis em termos de confiabilidade. Neste trabalho, três aspectos da evolução tecnológica serão enfatizados: redução do tamanho dos transistores, aumento da freqüência de relógio e variabilidade de componentes analógicos. O primeiro aspecto diz respeito à ocorrência de Single Event Upsets (SEU), uma vez que a carga armazenada nos nós dos circuitos é cada vez menor, tornando o circuito mais suscetível a esses tipos de eventos, principalmente devido à incidência de radiação. O segundo aspecto é também relacionado ao choque de partículas radioativas no circuito. Neste caso, dado que o período de relógio tem se tornado menor, os Single Event Transients (SET) podem ser capturados por um latch, e interpretado como uma inversão de estado em um determinado bit. Finalmente, o terceiro aspecto lida com a variabilidade de componentes analógicos, a qual tende a aumentar a distância entre o projeto e o teste analógico e o digital. Pensando nesses três problemas, foram propostas três diferentes soluções para lidar com eles. Para o problema do SEU, um novo paradigma foi proposto: ao invés do uso de redundância de hardware ou software, um esquema de redundância de sinal foi proposto através de uso de sinais modulados em sigma-delta. No caso do SET, foi proposta uma solução para o esquema de Triple Modular Redundancy (TMR), onde o votador digital é substituído por um analógico, reduzindo assim as chances de ocorrência de SET. Para concluir, para a variabilidade de componentes analógicos, foi proposto um filtro de sinal misto no qual os componentes analógicos críticos são substituídos por partes digitais, permitindo um esquema de teste completamente digital, uma fácil substituição de partes defeituosas e um aumento de produtividade.

# Palavras-chaves: SEU. SET. Variabilidade de Componentes. Confiabilidade. Tolerância a Falhas. Produtividade.

### ABSTRACT

It has been a consensus that CMOS transistor gate length will soon overcome the nanometric barrier, allowing the inclusion of a huge number of these devices on a single die, even more than the enormous integration density shown these days. Nevertheless, it has also been claimed that this technology development will bring undesirable consequences as well, for what regards reliability. In this work, three aspects of technology evolution will be emphasized: transistor size shrinking, clock frequency increase and analog components variability. The first aspect concerns the occurrence of Single Event Upsets (SEU), since the charge stored in the circuit nodes becomes ever smaller, making the circuit more susceptible to this kind of events, mainly due to radiation incidence. The second aspect is also related to the hit of radiation particles in the circuit. In this case, since clock period becomes smaller, Single Event Transients (SET) may cross the entire circuit and can possibly be latched and interpreted as a state inversion of a certain bit. Finally, the third aspect deals with the analog components variability, which tends to increase the gap between the analog and digital design and test. Thinking about these three problems, we have proposed three different solutions to deal with them. To the SEU problem, a new paradigm has been proposed: instead of hardware or software redundancy, a signal redundancy approach has been proposed through the use of sigma-delta modulated signals. In the SET case, we have proposed a solution for the Triple Modular Redundancy (TMR) approach, where the digital voter is substituted by an analog one, thus reducing the chances of SET occurrence. To conclude, for the analog components variability, we have proposed a mixed-signal filter solution where critical analog components are substituted by digital parts, allowing a complete digital test approach, an easy faulty parts replacement and yield increase.

Keywords: SEU. SET. Components Variability. Reliability. Fault Tolerance. Yield.

### TABLE OF CONTENTS

| 1 INTRODUCTION                                                                                                                                                                                  |              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2 SIGMA-DELTA MODULATION TO COPE WITH SEU IN DIGI                                                                                                                                               | TAL CIRCUITS |

| 19                                                                                                                                                                                              |              |

| 2.1 ERROR TOLERANT SYSTEMS                                                                                                                                                                      |              |

| 2.2 SIGNAL REDUNDANCY PARADIGM                                                                                                                                                                  |              |

| 2.3 SIGMA-DELTA MODULATED-SIGNALS AND ITS USE IN REDUNDANT SIG                                                                                                                                  |              |

| GENERATION                                                                                                                                                                                      |              |

| 2.3.1 Sigma-Delta Modulation                                                                                                                                                                    |              |

| 6                                                                                                                                                                                               |              |

| 2.3.2 Redundant Signal Generation through Sigma-Delta Modulation                                                                                                                                |              |

| <ul> <li>2.3.2.1 Evaluating bit-flips in digital first-order ΣΔ modulators [SCHÜLER, 200</li> <li>2.3.2.2 First-Order <i>versus</i> High-Order Topologies under Faults [SCHÜLER, 200</li> </ul> |              |

| 2.3.3 Case Studies                                                                                                                                                                              | -            |

| 2.3.3.1 Arithmetic Operations [SCHÜLER, 2005a]                                                                                                                                                  |              |

| 2.3.3.2 Finite Impulse Response (FIR) Filter [SCHÜLER, 2005b, 2006b, 2006c,                                                                                                                     |              |

| 2.3.3.3 Infinite Impulse Response (IIR) Filter [SCHÜLER, 2007a]                                                                                                                                 |              |

| 2.3.4 Functionally Fault Tolerant DSP Microprocessor [SCHÜLER, 20                                                                                                                               |              |

| 2.3.5 Area and Performance Comparison [SCHÜLER, 2005c]                                                                                                                                          |              |

| 2.3.5.1 Area Analysis                                                                                                                                                                           |              |

| 2.3.5.2 Performance Analysis                                                                                                                                                                    |              |

| 2.3.6 0.35µm Technology Chip Development                                                                                                                                                        |              |

| 2.4 CONCLUSIONS                                                                                                                                                                                 |              |

| <b>3</b> ANALOG VOTER TO COPE WITH SET IN TMR APPROACHI                                                                                                                                         |              |

| 3.1 DIGITAL VOTER                                                                                                                                                                               |              |

|                                                                                                                                                                                                 |              |

| 3.1.1 Simulations Results                                                                                                                                                                       |              |

| 3.2 ANALOG VOTER [SCHÜLER, 2005D] [LISBÔA, 2005]                                                                                                                                                |              |

| 3.2.1 Simulations Results                                                                                                                                                                       |              |

| 3.3 CONCLUSIONS                                                                                                                                                                                 |              |

| 4 STATISTICAL SAMPLERS TO COPE WITH COMPONENT VA                                                                                                                                                |              |

| ANALOG CIRCUITS                                                                                                                                                                                 |              |

| 4.1 MIXED-SIGNAL CAPACITANCE-INSENSITIVE FILTER [SCHÜLER, 200'                                                                                                                                  | 7B, 2007C]94 |

| 4.1.1 Input Analog Shift-Register                                                                                                                                                               |              |

| 4.1.1.1 Loss in Resolution due to the Shift Step                                                                                                                                                |              |

| 4.1.1.2 Loss in Resolution due to Capacitance Variation of the Analog Shift-Reg                                                                                                                 | gister       |

| 4.1.1.3 Frequency Response of the Analog Shift-Register                                                                                                                                         |              |

| 4.1.2 Statistical Sampler                                                                                                                                                                       |              |

| 4.1.2.1 Pseudorandom Noise Generation                                                                                                                                                           |              |

| 4.1.3 Adding Spare Parts: testing and replacement scheme                                                                                                                                        |              |

| 4.1.3.1 Testing the Gain of the Analog Shift-Register Buffer                                                                                                                                    |              |

| 4.1.3.2 Testing the Off-Set Voltage of the Statistical Sampler                                                                                                                                  |              |

| 4.2 CONCLUSIONS                                                                                                                                                                                 |              |

| 5 FINAL REMARKS                                                                                                                                                                                 |              |

| 5.1 CONTRIBUTIONS                                                                                                                                                                               |              |

| 5.2 FUTURE WORKS                                                                                                                                                                                |              |

## LIST OF FIGURES

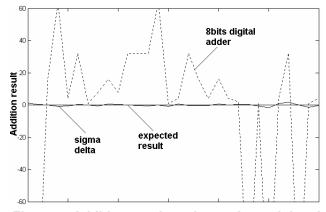

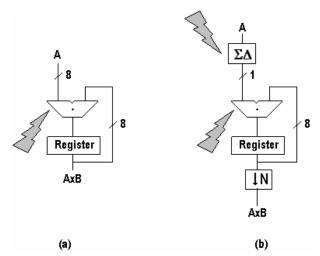

|            | <ol> <li>Multiple faults can occur when technology advances [ROSSI, 2005]20</li> <li>Error tolerant signal generation. In (a), resolution is compatible with system requirements, while in (b) faults make resolution drop below 10 bits24</li> </ol> |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

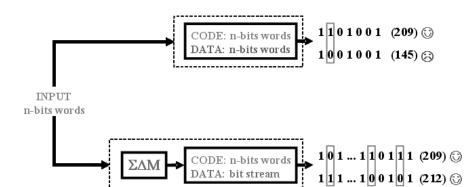

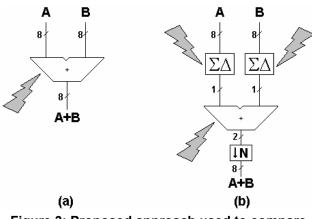

| Figure     | 3: Redundant signal generation through signal/noise comparison. In (a) an n-<br>bit word stream is generated, while in (b) an 1-bit bit stream is achieved26                                                                                          |

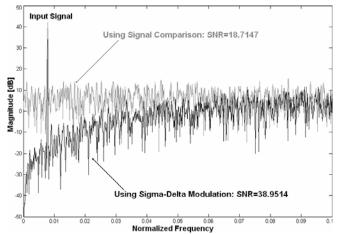

| Figure     | 4: Comparison between two different ways to generate redundant signals:<br>through noise/signal comparison and through sigma-delta modulation28                                                                                                       |

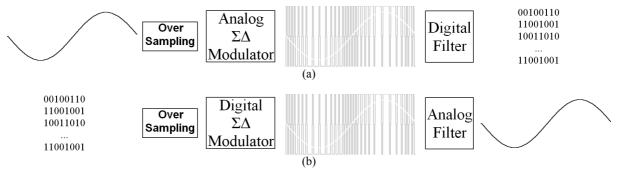

| Figure     | 5: (a) Analog to Digital conversion and (b) Digital to Analog conversion with sigma-delta modulators                                                                                                                                                  |

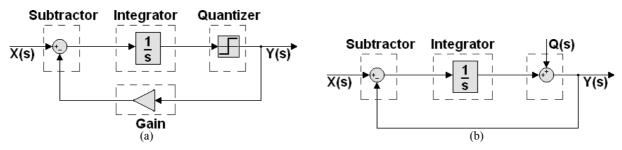

| Figure     | 6: (a) First-order sigma-delta modulator implementation and (b) quantization noise-model. 29                                                                                                                                                          |

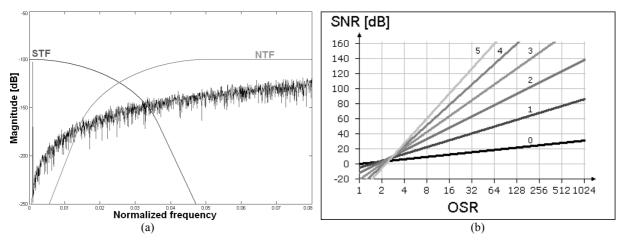

| Figure     | 7: (a) Signal Transfer Function (STF) and Noise Transfer Function (NTF) for<br>a sigma-delta modulator: low-pass and high-pass to achieve high SNR. (b)<br>Increase of the SNR according to the OSR and the modulator order                           |

| Figure     | 8: Replicating first-order modulators to generate high-order ones                                                                                                                                                                                     |

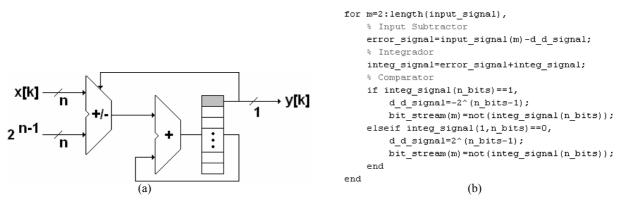

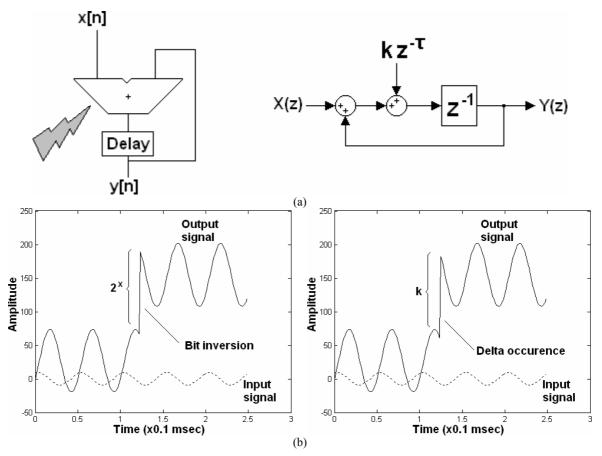

| •          | 9: (a) Example of hardware implementation for a digital modulator and (b)                                                                                                                                                                             |

| riguio     | example of software implementation of the same modulator                                                                                                                                                                                              |

| Figure     | 10: (a) Hardware example to implement a digital Sinc filter, whose impulse                                                                                                                                                                            |

| riguio     | response is shown in (b)                                                                                                                                                                                                                              |

| Figure     | 11: Signal redundancy to be used in error tolerant systems: sigma-delta                                                                                                                                                                               |

| 0          | modulation generates the redundant signal                                                                                                                                                                                                             |

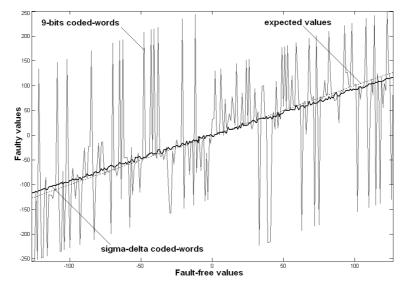

| Figure     | 12: 9-bit and sigma-delta representation of a sequence of 256 values. Faults                                                                                                                                                                          |

| 5          | are injected through single or multiple bit-flips                                                                                                                                                                                                     |

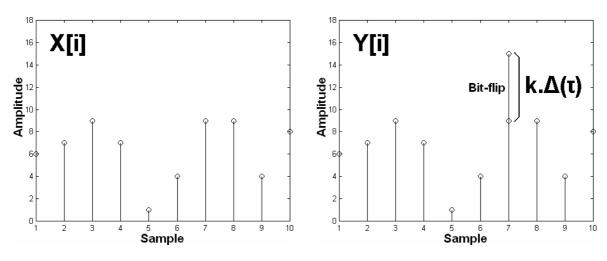

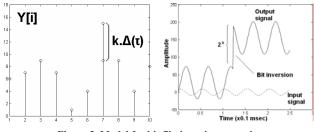

| Figure     | 13: Modeling a bit-flip in a certain sample x[i]                                                                                                                                                                                                      |

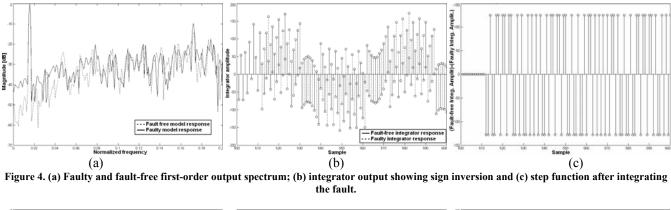

| •          | 14: (a) Circuit and model for an integrator with a bit-flip and (b) input and                                                                                                                                                                         |

| U          | output signal for the integrator circuit and model                                                                                                                                                                                                    |

| Figure     | 15: Complete analytical faulty model for the first order $\Sigma\Delta$ modulator                                                                                                                                                                     |

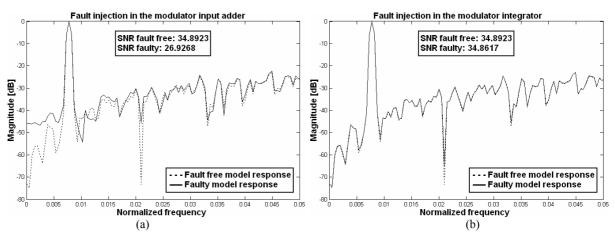

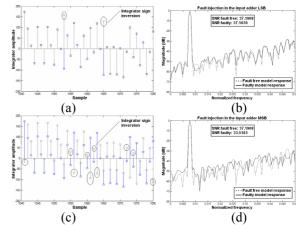

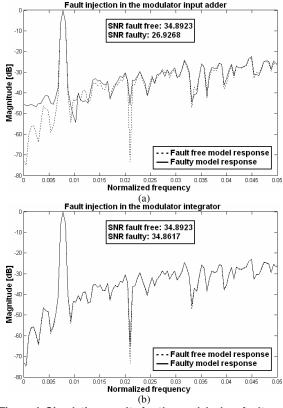

| Figure     | 16: Simulation results for the model when faults are injected (a) in the input                                                                                                                                                                        |

| Ū          | adder and (b) in the integrator                                                                                                                                                                                                                       |

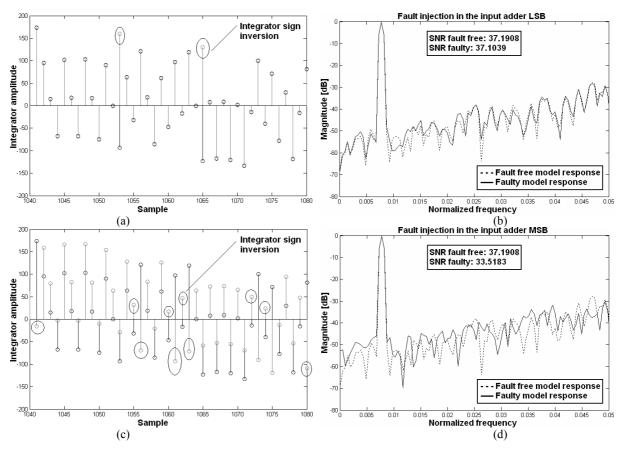

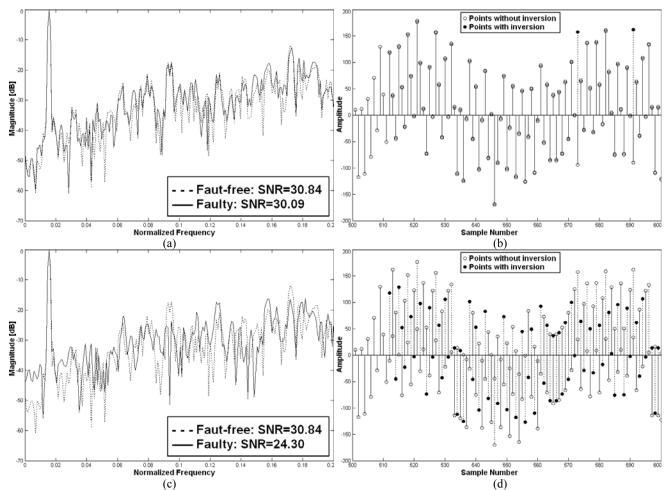

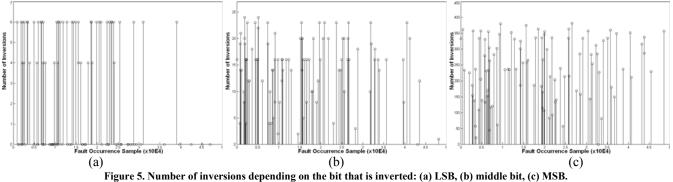

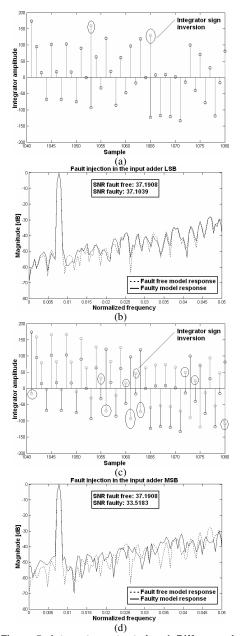

| Figure     | 17: (a) Integrator output with one bit-flip in the LSB and (b) its consequence for the circuit response. In (c), integrator output with MSB inverted and the                                                                                          |

| <u>-</u> . | frequency response in (d)                                                                                                                                                                                                                             |

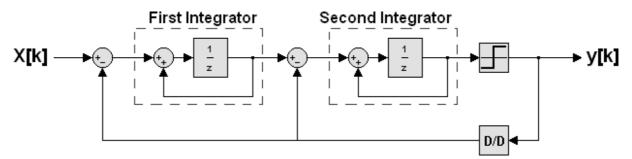

| •          | 18: A second-order digital sigma-delta modulator. 42                                                                                                                                                                                                  |

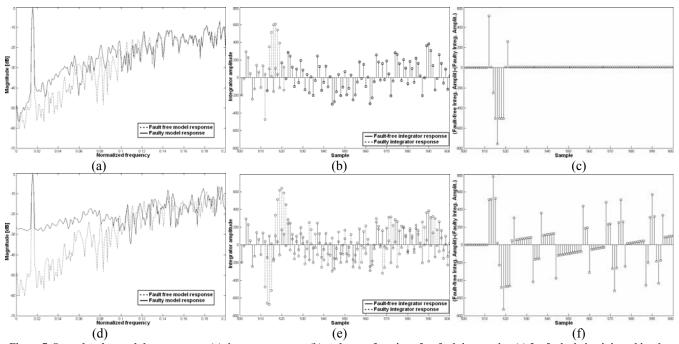

| ⊢igure     | 19: (a) Second-order modulator response, (b) integrator output and (c) ramp                                                                                                                                                                           |

|            | function after fault integration for faults being injected in the second block.                                                                                                                                                                       |

|            | (d) response, (e) integrator output and (f) ramp function after fault                                                                                                                                                                                 |

|            | integration for faults being injected in the first block                                                                                                                                                                                              |

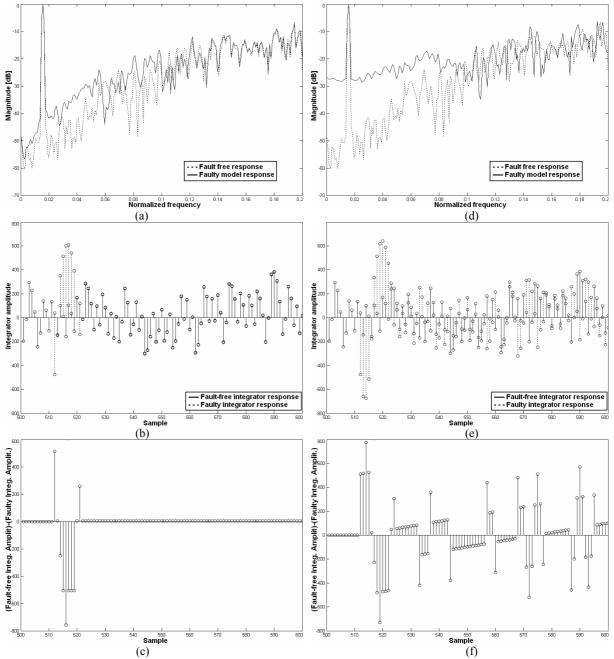

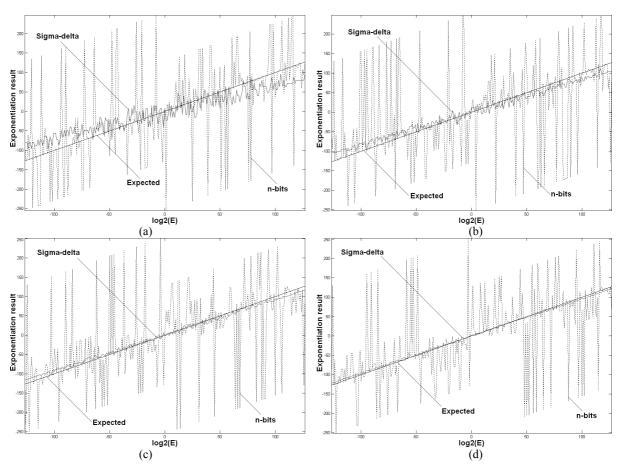

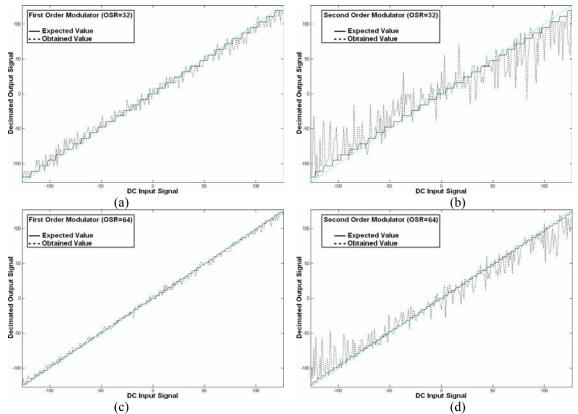

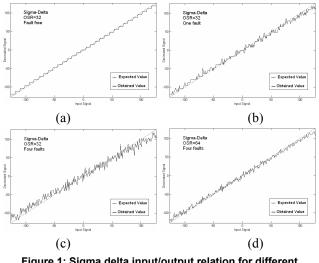

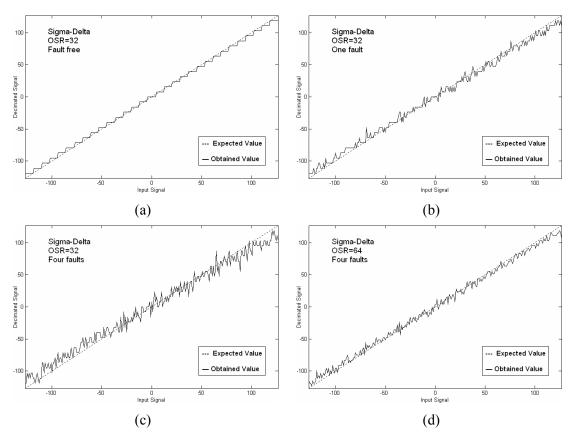

| Figure 20: Delta-sigma input/output relation for different number of faults injected and different OSR: (a) first-order and OSR=32; (b) second-order and OSR=32 | ).<br>., |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| (c) first-order and OSR=64; (d) second-order and OSR=64                                                                                                         |          |

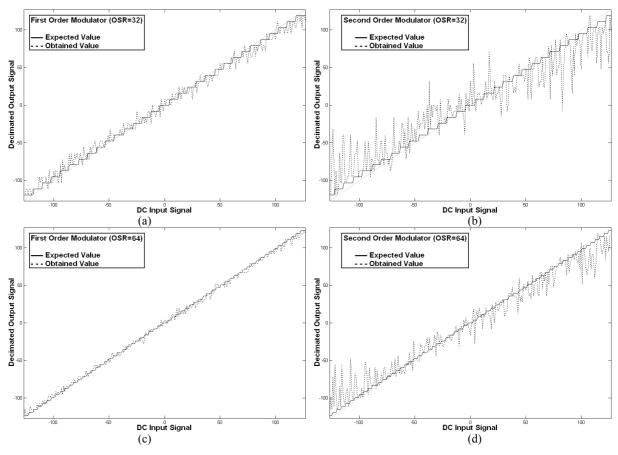

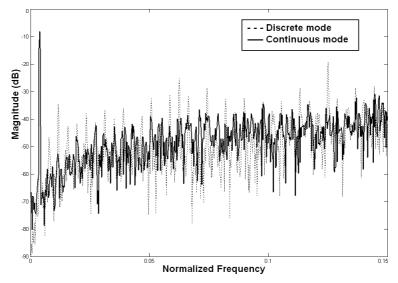

| Figure 21: Continuous and discrete sigma-delta modulation.                                                                                                      |          |

| Figure 22: Spectra of the continuous and discrete sigma-delta modulation modes                                                                                  |          |

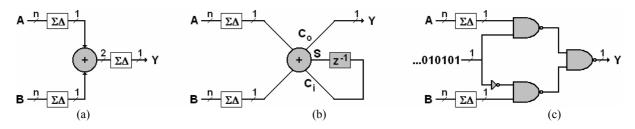

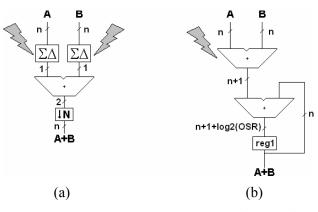

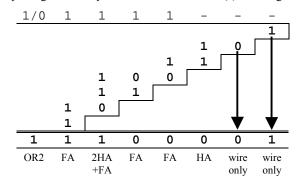

| Figure 23: Three methods to add bit streams: (a) direct addition, (b) carry feedback and (c) interleaving.                                                      | 49       |

| Figure 24: Comparing the three methods to add bit streams: (a) direct addition, (b) carry feedback and (c) interleaving.                                        | 50       |

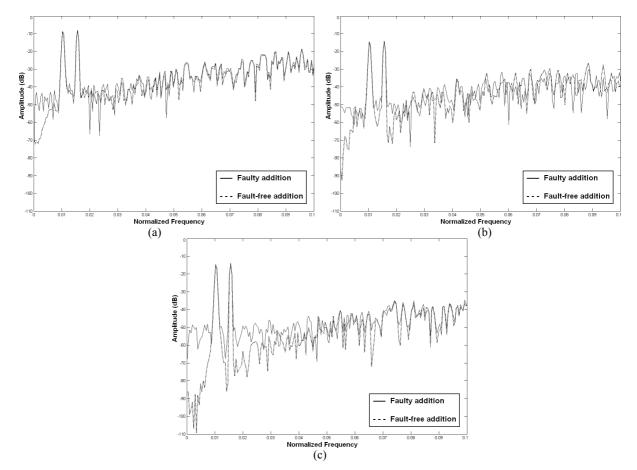

| Figure 25: Comparing the three methods to add bit streams when faults are injected                                                                              |          |

| in the bit streams: (a) direct addition, (b) carry feedback and (c) interleavir                                                                                 |          |

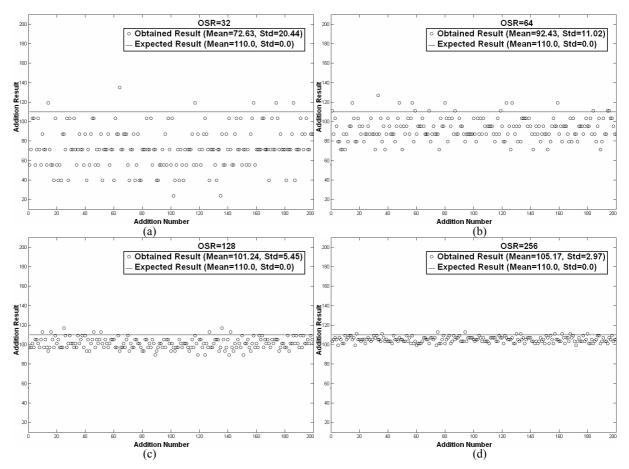

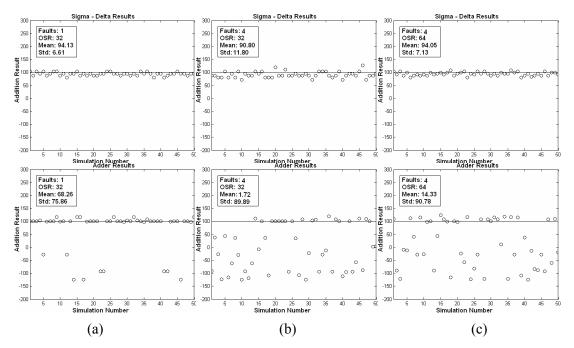

| Figure 26: Addition through interleaving of two sigma-delta modulated bit streams,                                                                              |          |

| with faults injected in the addition process. As the OSR increases, also the                                                                                    | е        |

| final resolution and the fault tolerance increase as well. No fault is injected                                                                                 | b        |

| during modulation process.                                                                                                                                      | 52       |

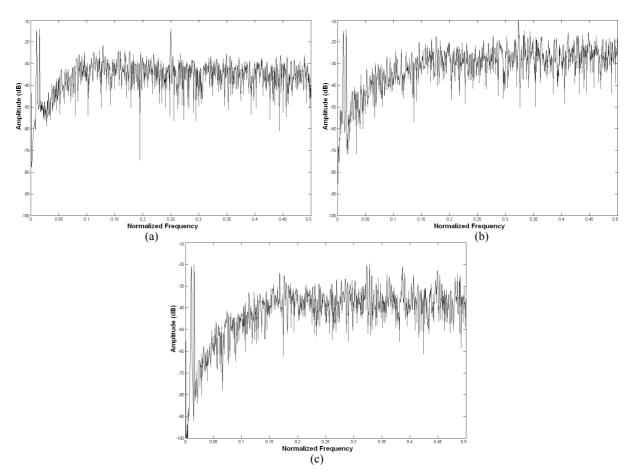

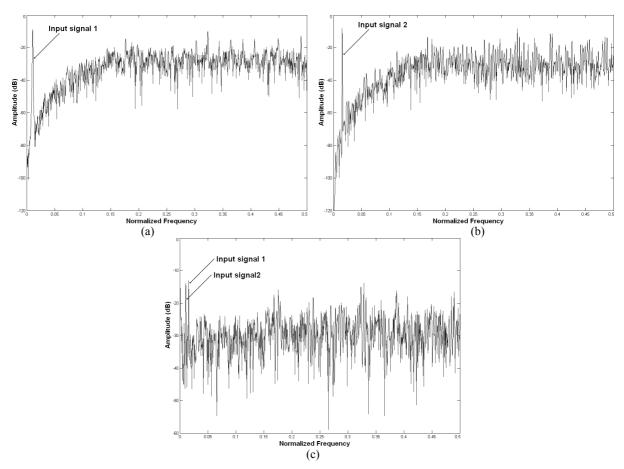

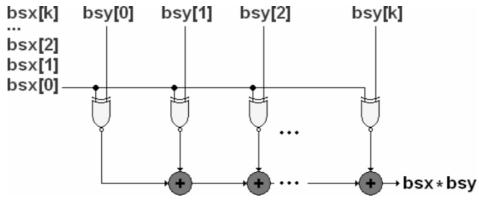

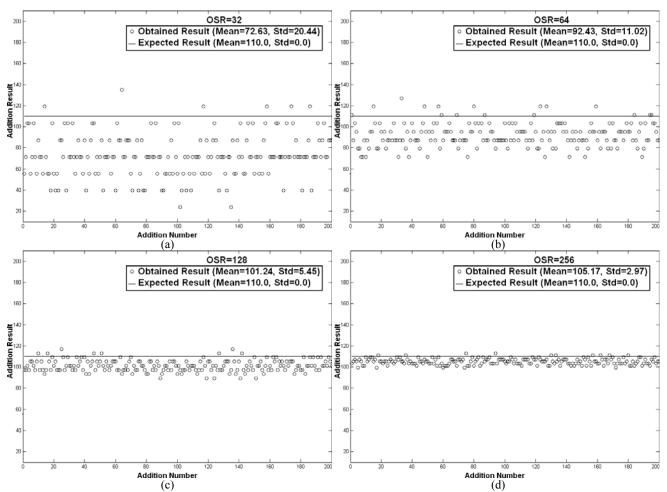

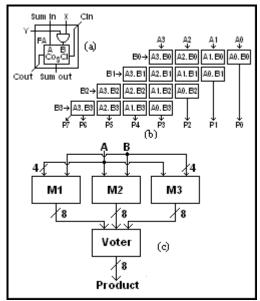

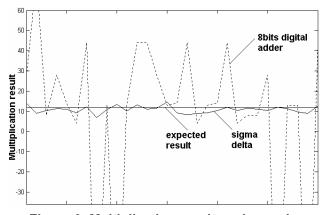

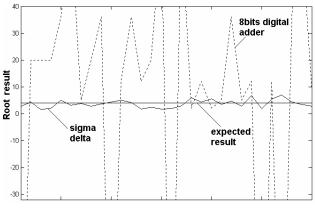

| Figure 27: Multiplication of two bit streams through the AND of the bit streams: (a)                                                                            |          |

| Input signal 1 in $\Sigma\Delta$ , (b) input signal 2 in $\Sigma\Delta$ and (c) multiplied bit streams.                                                         | 54       |

| Figure 28: Bit stream multiplication using XNOR gates.                                                                                                          | 55       |

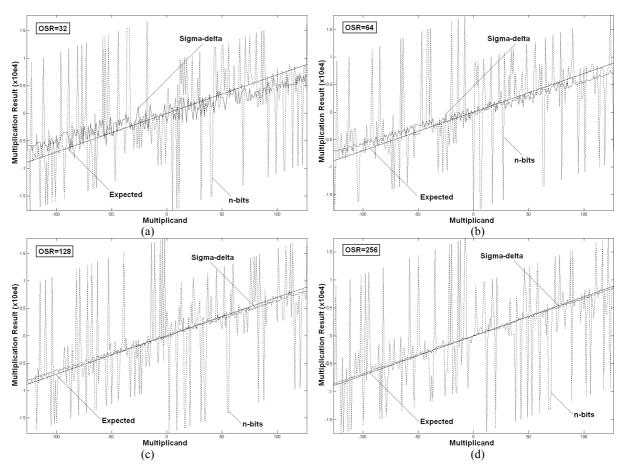

| Figure 29: Multiplication of two constants using sigma-delta modulated values with                                                                              |          |

| different OSR: (a) OSR=32, (b) OSR=64, (c) OSR=128 and (d) OSR=256                                                                                              |          |

|                                                                                                                                                                 | 56       |

| Figure 30: Base 2 in the power of exponent varying in the range [-127 127]                                                                                      |          |

| modulated with different OSR: (a) OSR=32, (b) OSR=64, (c) OSR=128 ar                                                                                            | ۱d       |

| (d) OSR=256                                                                                                                                                     |          |

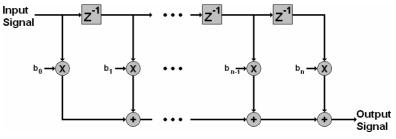

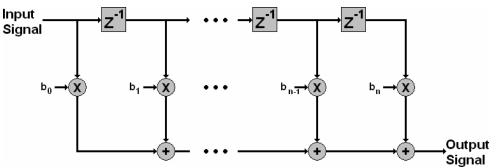

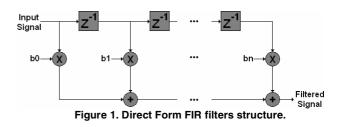

| Figure 31: Direct Form FIR filter implementation                                                                                                                | 58       |

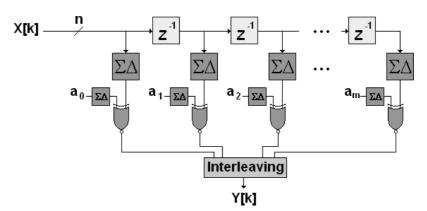

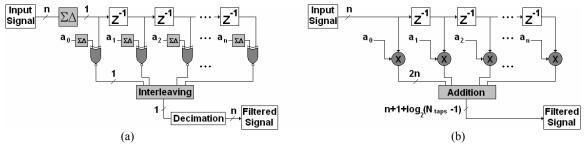

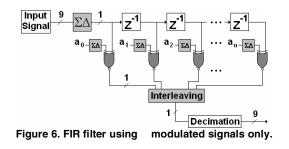

| Figure 32: FIR filter using $\Sigma\Delta$ modulated signals only. Input signal is modulated                                                                    |          |

| through continuous modulation                                                                                                                                   | 59       |

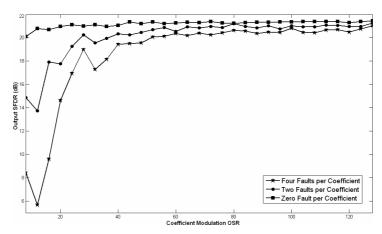

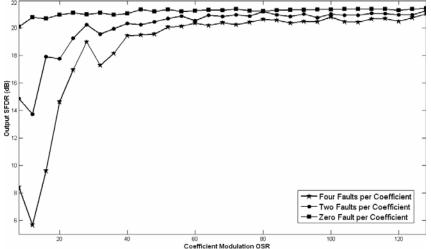

| Figure 33: Resolution measured in SFDR versus OSR used to modulate FIR                                                                                          |          |

| coefficients, for a constant number of faults injected in the coefficients bit                                                                                  |          |

|                                                                                                                                                                 | 59       |

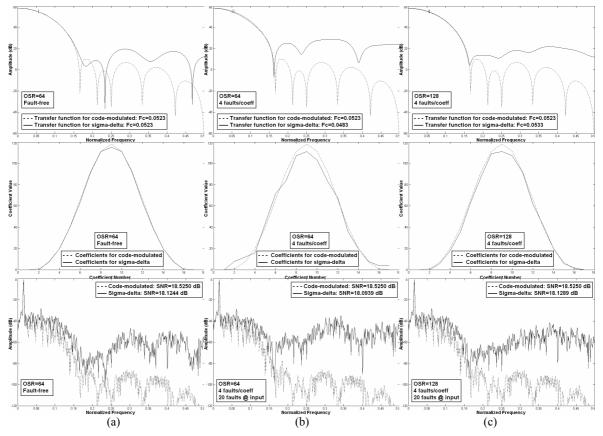

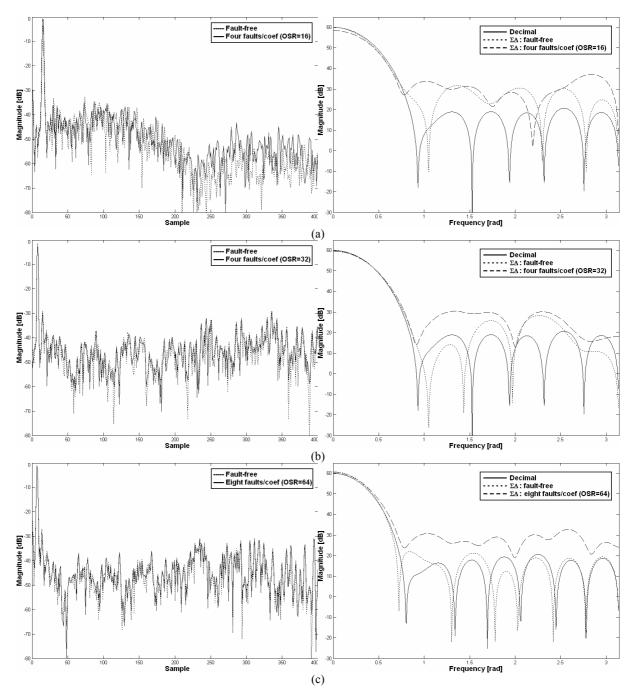

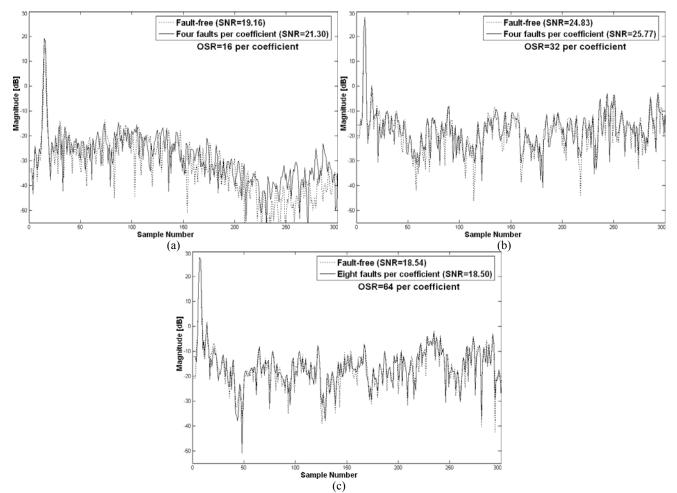

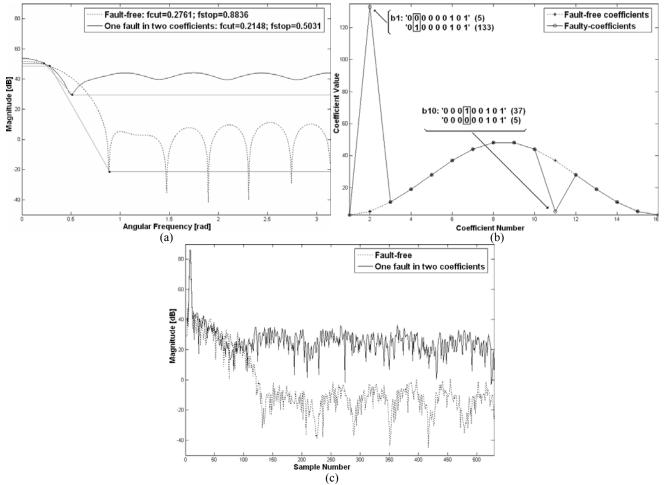

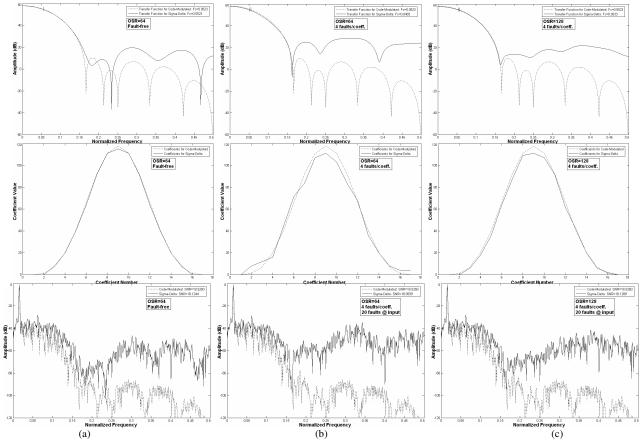

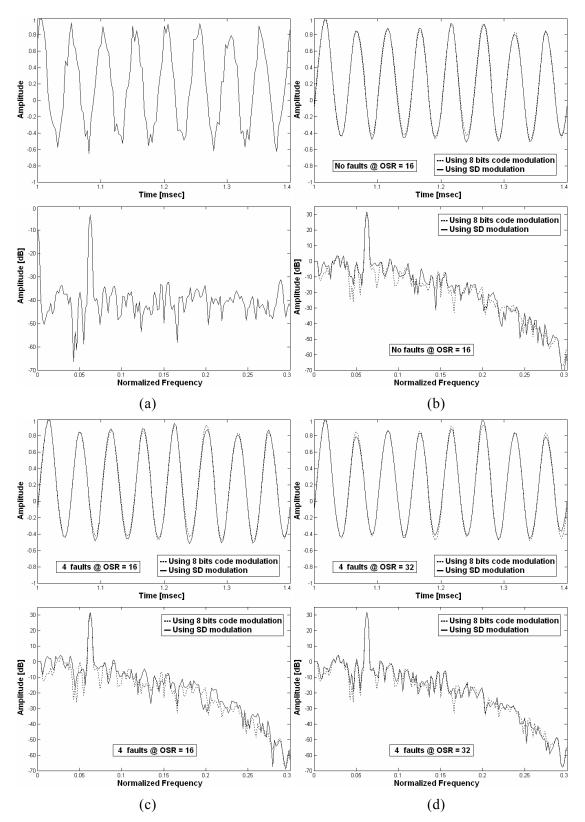

| Figure 34: Filter response, coefficients and output FFT for different number of faults                                                                          |          |

| injected and different OSR used to modulate each filter coefficient                                                                                             | 61       |

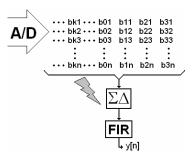

| Figure 35: Representation of the structure used to filter signals using a discrete                                                                              |          |

| sigma-delta-modulation scheme                                                                                                                                   | 62       |

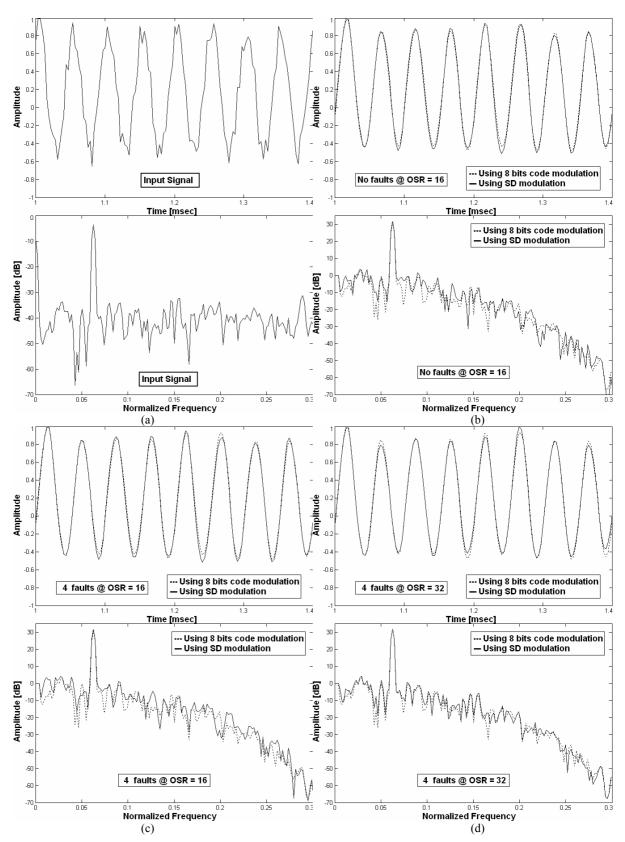

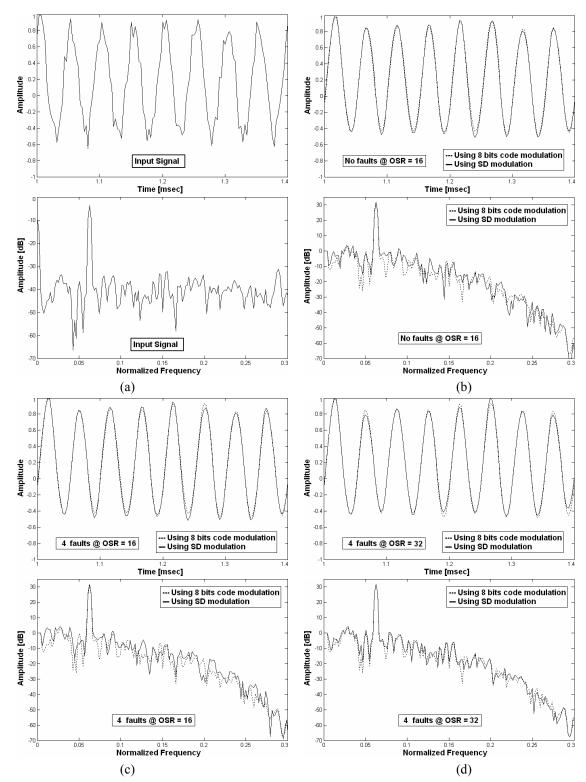

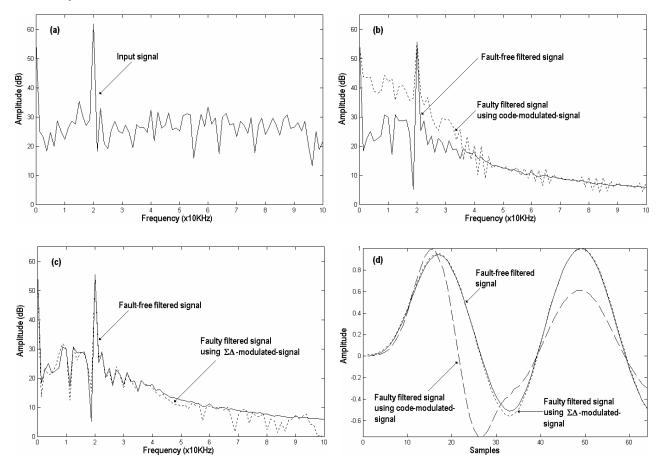

| Figure 36: Results obtained by filtering a noisy 20KHz signal using sigma-delta                                                                                 |          |

| modulated signals. In (a), the input signal, in (b), the filtered signal with no                                                                                | )        |

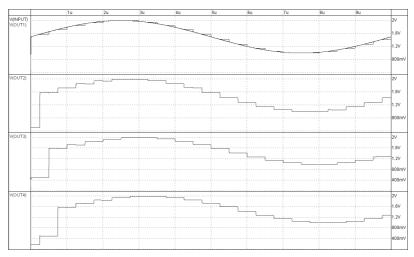

| faults @OSR 16, in (c) with 4 faults @OSR 16 and in (d) with 4 faults                                                                                           |          |

| @OSR 32                                                                                                                                                         |          |

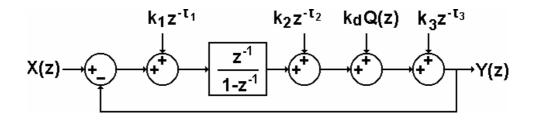

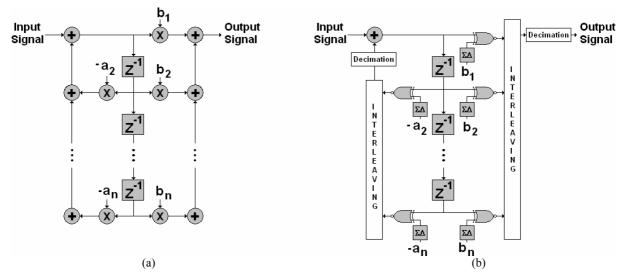

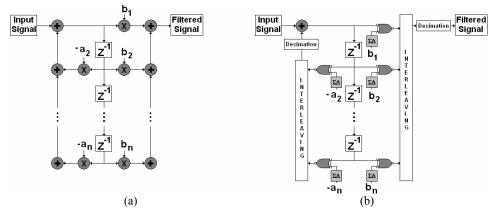

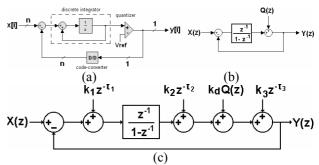

| Figure 37: (a) Infinite Impulse Response filter classical digital implementation, and (                                                                         |          |

| structure using sigma-delta modulated input signal and coefficients for the                                                                                     | ;        |

| same filter                                                                                                                                                     | 64       |

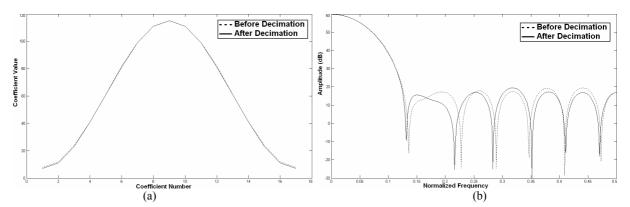

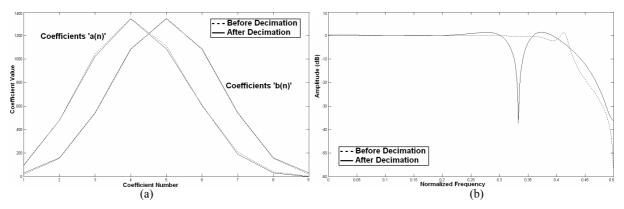

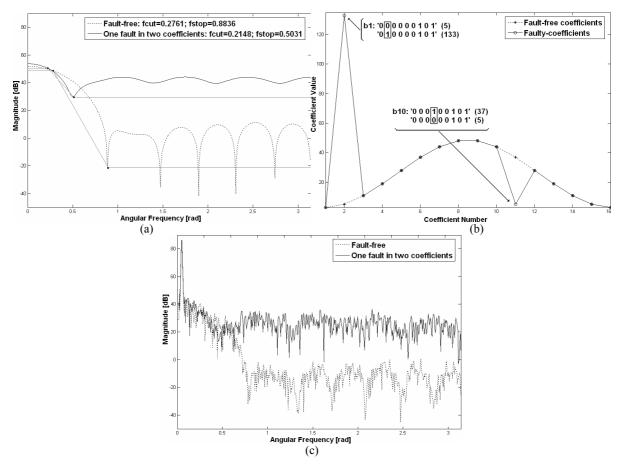

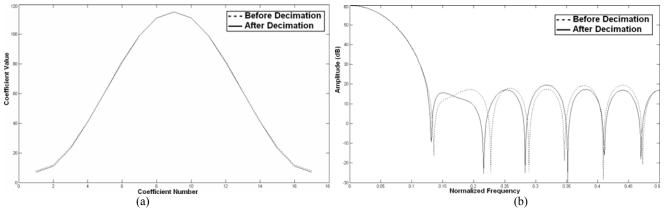

| Figure 38: Finite Impulse Response filter coefficients (a) and filter response (b),                                                                             |          |

| showing the effects of coefficient quantization.                                                                                                                | 65       |

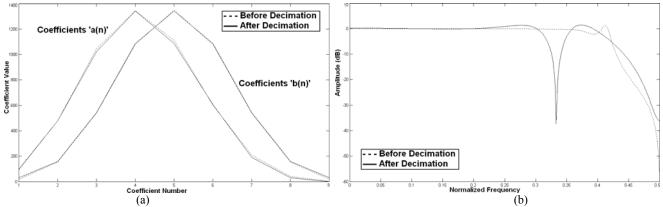

| Figure 39: Infinite Impulse Response filter coefficients (a) and filter response (b),                                                                           | ~        |

| showing the effects of coefficient quantization.                                                                                                                |          |

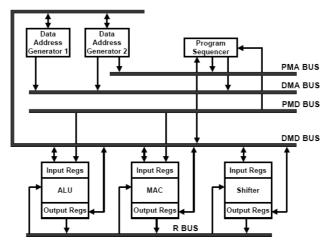

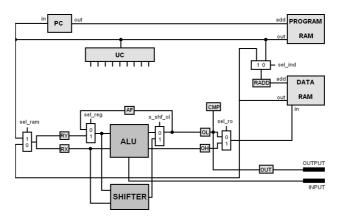

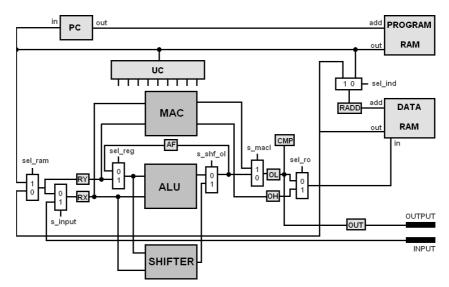

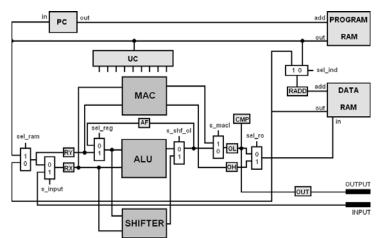

| Figure 40: Block diagram of ADSP2100 DSP microprocessor.                                                                                                        |          |

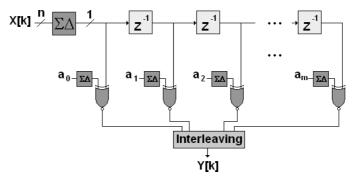

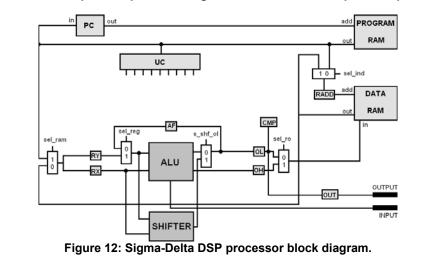

| Figure 41: Sigma-Delta DSP microprocessor structure.                                                                                                            | 68       |

| Figure 42: Practical results from the $\Sigma\Delta$ -DSP implementing a 16 taps FIR filter with different OSR used to modulate the coefficients, and respective filter |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| impulse response70                                                                                                                                                      |

| Figure 43: n-bit PCM words DSP microprocessor structure71                                                                                                               |

| Figure 44: Standard DSP microprocessor simulation results. In (a), fault-free and                                                                                       |

| faulty filter impulse response; (b) filter coefficients, and in (c), FIR output                                                                                         |

| from the fault-free and faulty DSP response                                                                                                                             |

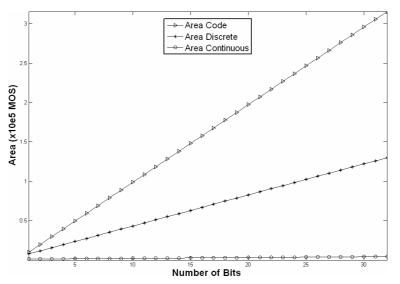

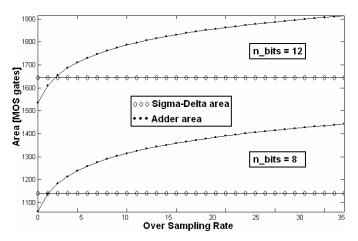

| Figure 45: Comparison of area versus number of bit between FIR filter using code-                                                                                       |

| modulated and sigma-delta modulated signals                                                                                                                             |

| Figure 46: Finite State Machine for (a) the code-modulated FIR, (b) continuous                                                                                          |

| sigma-delta modulation FIR and (c) discrete sigma-delta modulation FIR77                                                                                                |

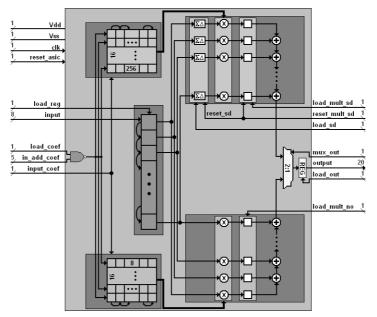

| Figure 47: Proposed circuit to be developed using a 0.35µm technology78                                                                                                 |

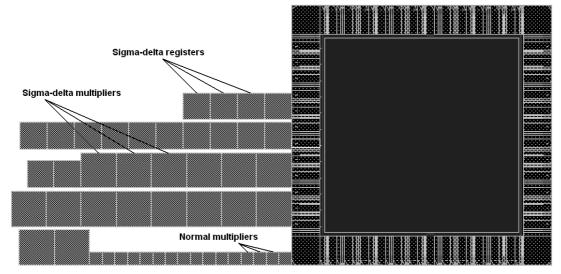

| Figure 48: Top cell view generated through Encounter®                                                                                                                   |

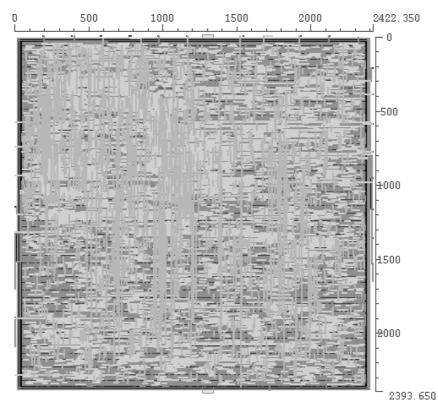

| Figure 49: Final mask to be used in the fabrication process                                                                                                             |

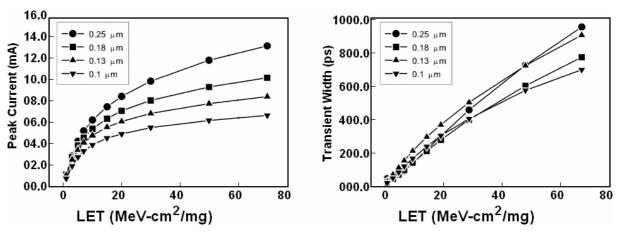

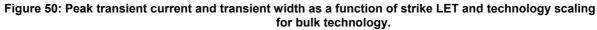

| Figure 50: Peak transient current and transient width as a function of strike LET and                                                                                   |

| technology scaling for bulk technology                                                                                                                                  |

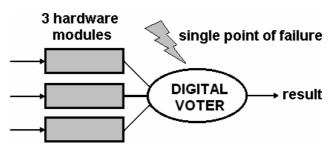

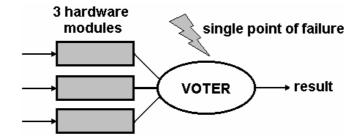

| Figure 51: The TMR approach: voter may become an unreliable point                                                                                                       |

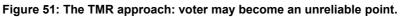

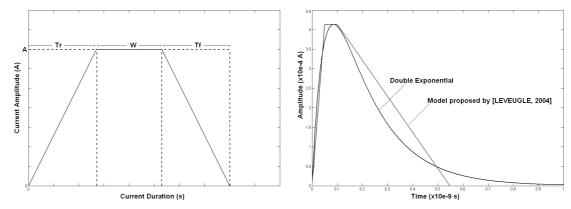

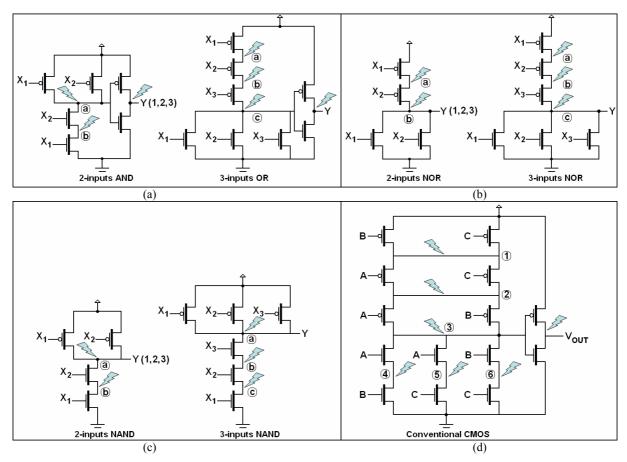

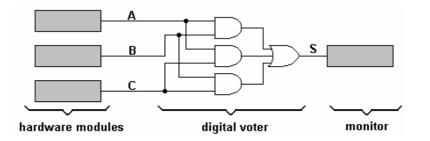

| Figure 52: (a) NAND-NAND voter, (b) NOR-NOR voter, (c) AND-OR and (d)                                                                                                   |

| conventional CMOS static implementation of a voter for a TMR system84                                                                                                   |

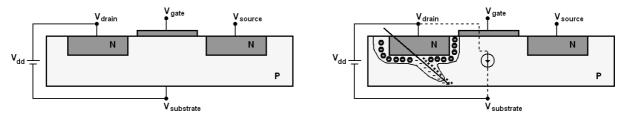

| Figure 53: NMOS section showing a particle hit in a reversed biased PN junction85                                                                                       |

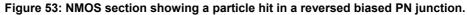

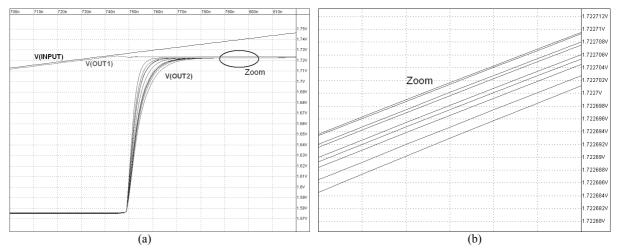

| Figure 54: (a) Proposed model for the double exponential and (b) comparison                                                                                             |

| between the model and the double exponential curve                                                                                                                      |

| Figure 55: Simulated circuits for SET evaluation in a digital TMR voter                                                                                                 |

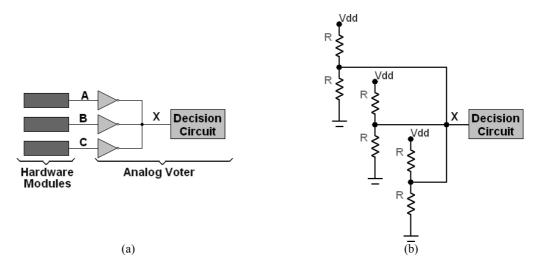

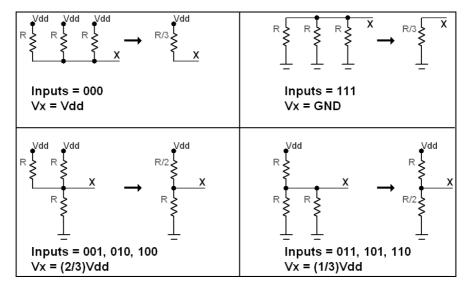

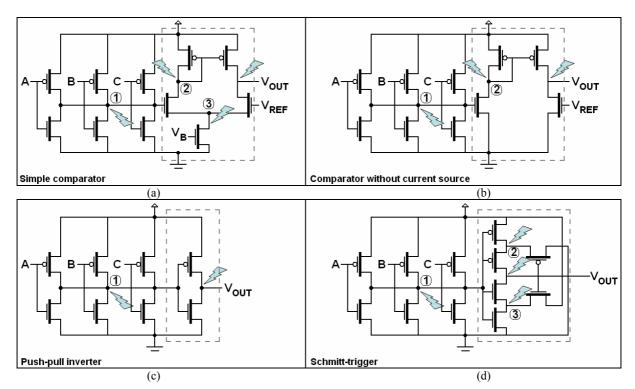

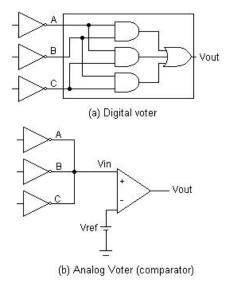

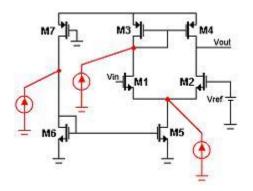

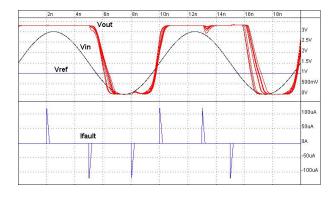

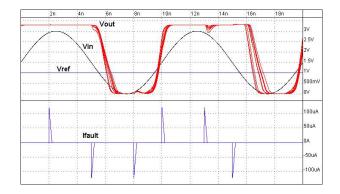

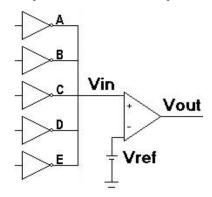

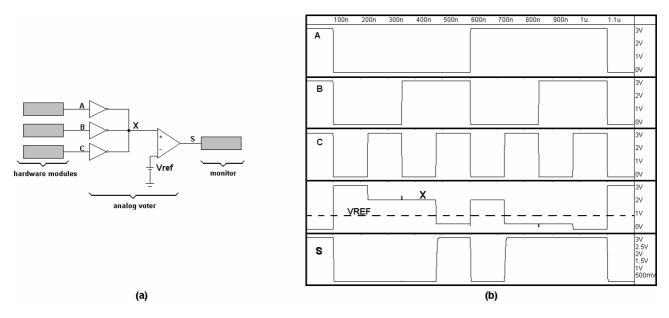

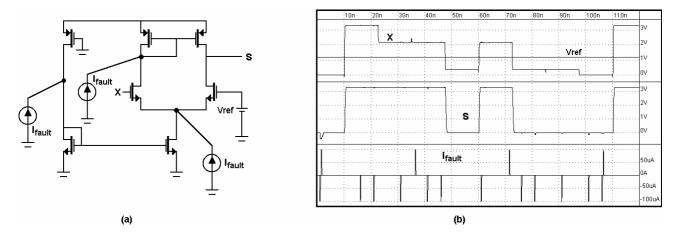

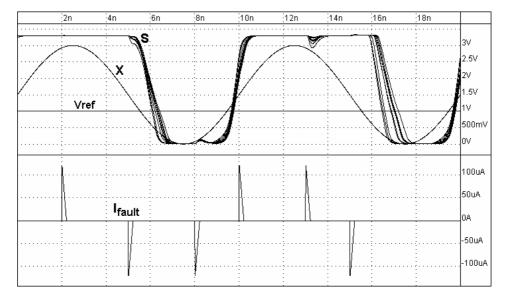

| Figure 56: (a) Analog voter and (b) equivalent electrical circuit                                                                                                       |

| Figure 57: Calculating the short circuited inverters output voltage for all possible input                                                                              |

| situations                                                                                                                                                              |

| Figure 58: Simulated circuits for SET evaluation in an analog TMR voter90                                                                                               |

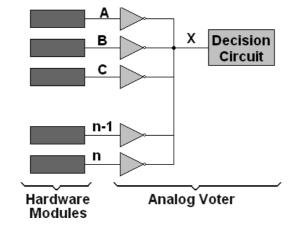

| Figure 59: The analog voter being used in a n-MR scheme                                                                                                                 |

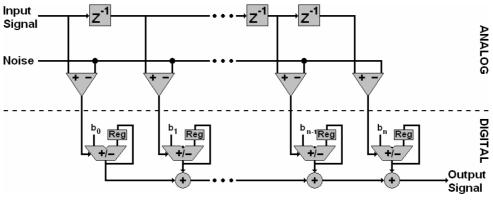

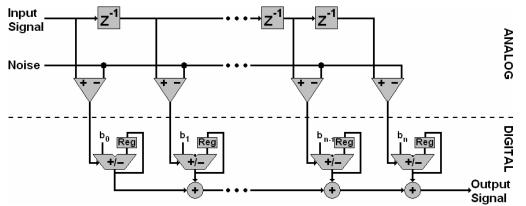

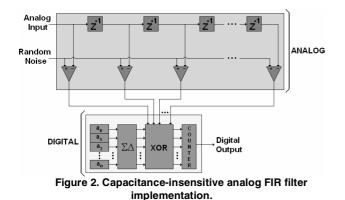

| Figure 60: Mixed-signal implementation of a FIR filter                                                                                                                  |

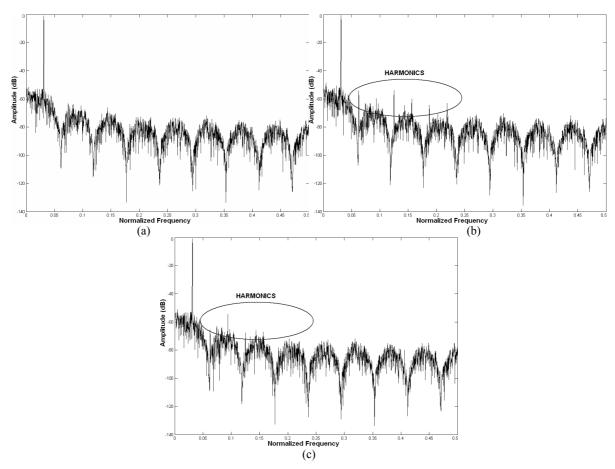

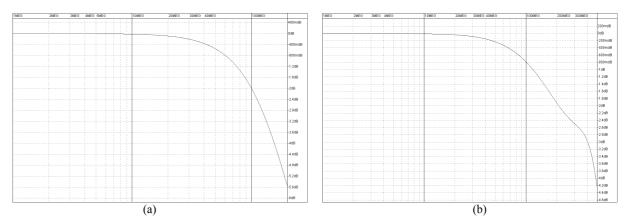

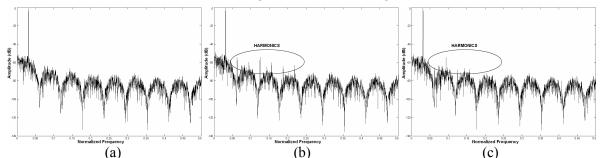

| Figure 61: Frequency spectra to compare the responses of (a) a normal filter, (b) the                                                                                   |

| proposed filter with an OSR of 256 and (c) an OSR equal to 102497                                                                                                       |

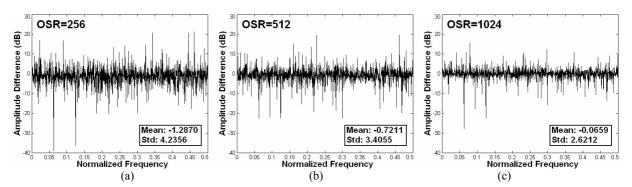

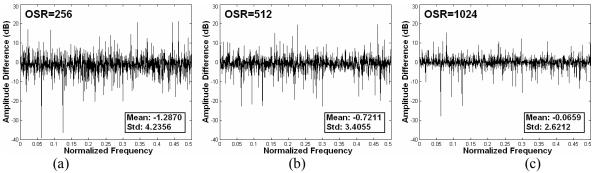

| Figure 62: Noise level plotted by making the difference between a FFT of a normal                                                                                       |

| filter and the proposed one using (a) an OSR equal to 256, (b) 512 and (c)                                                                                              |

| 1024                                                                                                                                                                    |

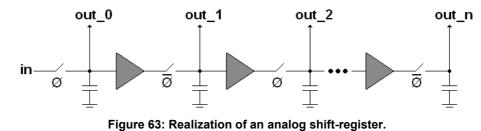

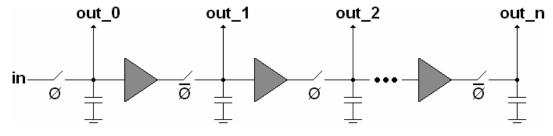

| Figure 63: Realization of an analog shift-register                                                                                                                      |

| Figure 64: Loss due to the shift process in the analog shift-register                                                                                                   |

| Figure 65: 50% Monte-Carlo variation in the 2 <sup>nd</sup> capacitor value of the analog delay                                                                         |

| block                                                                                                                                                                   |

| Figure 66: Analog register and its corresponding model100                                                                                                               |

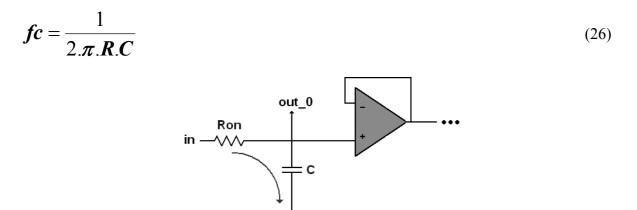

| Figure 67: Frequency limit of the input block: (a) due to the RC circuit and (b) due to                                                                                 |

| the operational amplifier                                                                                                                                               |

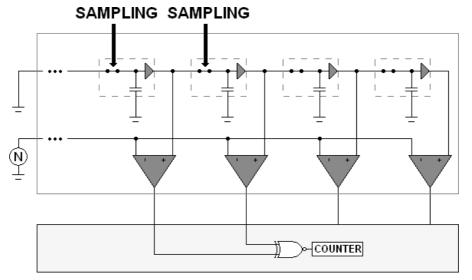

| Figure 68: Statistical sampler: a comparator with a noise in the reference [SOUZA,                                                                                      |

| 2004, 2005]                                                                                                                                                             |

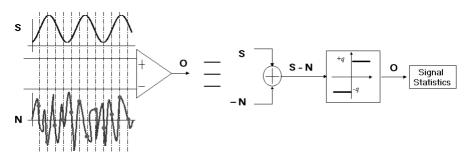

| Figure 69: Statistic acquisition with noise dithering [SOUZA, 2004, 2005]103                                                                                            |

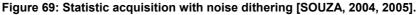

| Figure 70: Distribution of a uniform noise without non-linearity generation (a) and                                                                                     |

| distribution of a Gaussian noise with the respective non-linearity expressed                                                                                            |

| by the harmonic (b)                                                                                                                                                     |

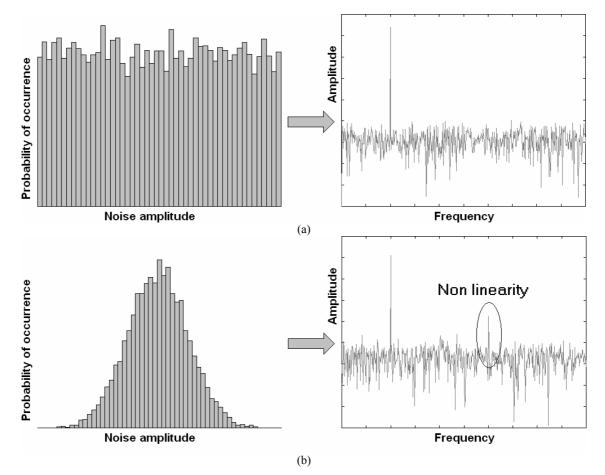

| Figure 71: Pseudo white noise generation proposed in [FLORES, 2002]104                                                                                                  |

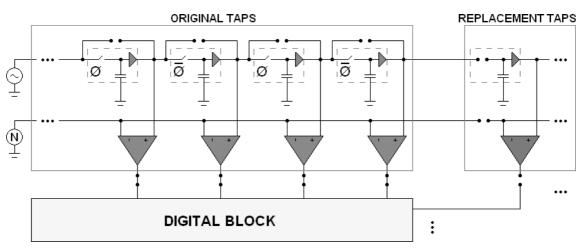

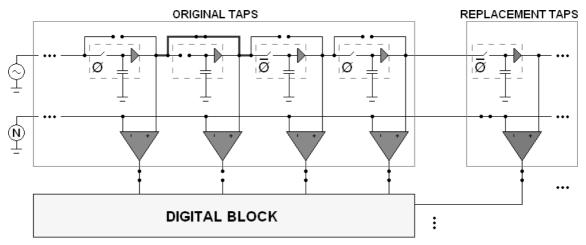

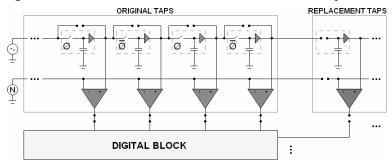

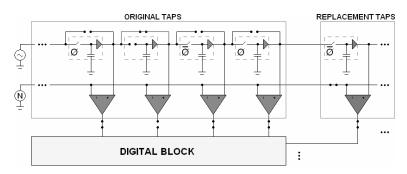

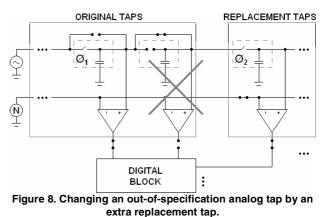

| Figure 72: Adding extra taps to the filter: these spare parts can easily replace non-                                                                                   |

| working analog branches106                                                                                                                                              |

| Figure 73: Second tap is replaced by one the existing replacement taps          |           |

|---------------------------------------------------------------------------------|-----------|

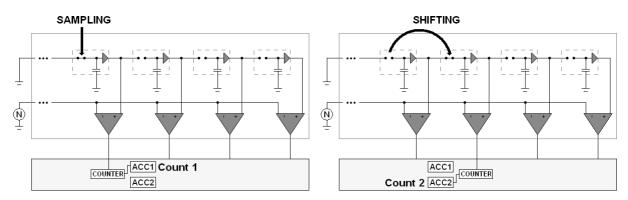

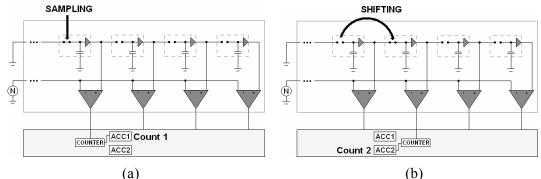

| Figure 74: Sequence for testing the analog shift-register buffer gain. Decision | is        |

| taken by comparing counted values: CASE values ARE "similar" gai                | in is OK; |

| CASE values ARE "different" gain is not OK                                      | 107       |

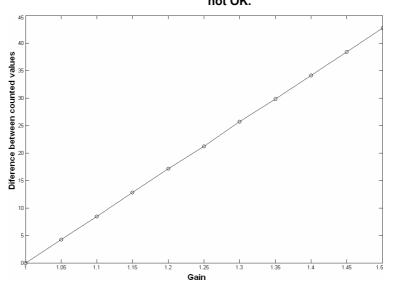

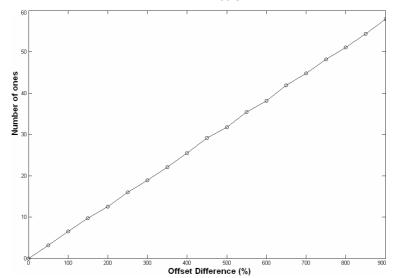

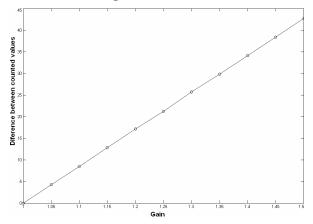

| Figure 75: Gain variation versus difference between counted values during th    | e test of |

| the analog shift-register buffer gain.                                          | 107       |

| Figure 76: Sequence for testing the comparators off-set voltage. Decision is t  | aken by   |

| comparing counted value: CASE value IS "small", off-set voltage is              | OK;       |

| CASE value IS "large", off-set voltage is not OK.                               | 108       |

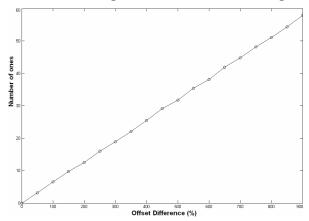

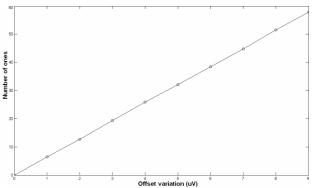

| Figure 77: Off-set voltage variation versus difference counted value during the | e test of |

| the analog comparator off-set voltage                                           | 108       |

## LIST OF TABLES

| Table 1: | Summarizing the bit stream addition methods.                             | 50 |

|----------|--------------------------------------------------------------------------|----|

| Table 2: | Sigma-Delta DSP instruction set.                                         | 58 |

| Table 3: | n-bit PCM DSP instruction set                                            | 71 |

| Table 4: | Sigma-delta and standard DSP microprocessor comparison summary           | 74 |

| Table 5: | Number of gates per bit in each circuit and number of MOS transistors in |    |

|          | each gate                                                                | 75 |

| Table 6: | SET consequences in different nodes of digital voters                    | 88 |

| Table 7: | SET consequences in different nodes of analog voters.                    | 91 |

| Table 8: | Summary of simulations with the digital and the analog voters under SET  |    |

|          | occurrences.                                                             | 91 |

| Table 9: | SET consequences in different nodes of analog voters for a n-MR approac  |    |

|          |                                                                          | 92 |

### LIST OF ABBREVIATIONS AND ACRONYMS

- ADC: Analog to Digital Converter

- ALU: Arithmetic Logic Unit

- CMOS: Complementary Metal-Oxide Semiconductor

- DAC: Digital to Analog Converter

- DSP: Digital Signal Processing

- FFT: Fast Fourier Transformer

- FIR: Finite Impulse Response

- FPGA: Field Programmable Gate Array

- Gm-C: Transconductor-Capacitor

- IIR: Infinite Impulse Response

- LET: Linear Energy Transfer

- LSB: Least Significative Bit

- LSFR: Linear Feedback Shift Register

- MAC: Multiply And Accumulate

- MASH: Multi-stAge noise SHaping

- MOS: Metal-Oxide Semiconductor

- MOSFET: Metal-Oxide Semiconductor Field-Effect Transistor

- MSB: Most Significative Bit

- NTF: Noise Transfer Function

- **OSR: Over Sampling Ratio**

- PCM: Pulse Code Modulation

- PDF: Probability Distribution Function

- RAM: Random Access Memory

- **RC:** Resistor-Capacitor

- SC: Switched-Capacitor

- SDDSP: Sigma-Delta Digital Signal Processing

- SEL: Single Event Latch-Up

- SET: Single Event Transient

- SEU: Single Event Upset

- SFDR: Spurious Free Dynamic Range

- SNR: Signal-to-Noise Ratio

- SoC: System-on-Chip

- SOI: Silicon-on-Insulator

- SRAM: Static Random Access Memory

- STF: Signal Transfer Function

- TMR: Triple Modular Redundancy

- VHDL: Very-High-Speed Integrated Circuit Hardware Description Language

- VLSI: Very-Large-Scale Integration

- $\Sigma\Delta$ : Sigma-Delta

#### **1** INTRODUCTION

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year ... Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be 65,000. I believe that such a large circuit can be built on a single wafer" [MOORE, 1965].

With this empirical observation made in 1965, Doctor Gordon Earle Moore dictated one of the most famous laws of the electronic history. Although today warm debates discuss whether this law will continue to be followed or not, it is a consensus that the MOSFET gate length will soon break the nanometric barrier. Much before that, the number of transistor per chip is expected to exceed the one billion cipher [ITRS, 2006]. On the other hand, there is a branch in the semiconductor industry, which believes that the actual silicon-based CMOS technology will be able to attend the miniaturization needs by the next one or two decades. Beyond this period, different approaches in terms of material and architecture must be adopted. The single electron transistor [HADLEY, 1997], resonant tunneling transistor [CHEN, 1996], carbon nanotubes transistor [HAZEGHI, 2007] and spin-transistor [LENT, 1997] are some of the possible alternatives to silicon devices. However, there is a consensus in one point: regardless of the technology that will be used, this new technology must be able to efficiently deal with signal integrity. As the size of the transistor channel decreases, also the number of electrons (or holes) in the channel decreases. With a lower number of carriers passing through the transistor channel, although the possibility of these carriers be hit by an external particle (e.g. alpha or neutron particles) decreases, if such event occurs, the effect caused will be much higher than if there was a higher number of carriers. Another problem is related to the fact that also the power supply of the circuits has decreased. The critical charge,

that is, the amount of charge required to cause an inversion on the transistor state, depends on the circuit node capacitance in a direct proportion, and on the inverse proportion of the node voltage. Since both these variables are decreasing, also the critical charge is smaller. These two factors contribute to the sprouting of the soft faults, that is, faults induced by the incidence of an external particle or by electromagnetic noise, for example, that may have catastrophic consequences to part of a system or, in the worst case, to the whole system.

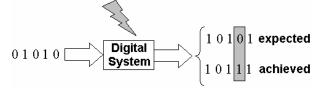

In this work we are mainly concerned about two kinds of soft fault: the Single Event Upset (SEU) and the Single Event Transient (SET). When a single particle strikes an integrated circuit element, it loses its energy via the production of electron-hole pairs, resulting in a dense ionized track in the local region. This ionization causes a transient current pulse, which, when propagated through a combinatorial logic, is named SET. The SET can possibly be stored in a flip-flop, thus generating an error in one or more bits, what is named SEU. Another SEU possibility is when a change of state is caused by a high-energy particle direct strike to a sensitive memory node. That is, an OFF transistor may become ON after a SEU occurrence. As mentioned, since the node capacitances are becoming smaller, the necessary energy to change the state is also smaller.

Another important factor to be taken into account for future technologies is the increase of the gap between the digital and the analog design. The scaling down of CMOS technology leads to great advantages in digital circuits, since low power and faster circuits can be implemented with an increased integration density. Also, design automation and test are relatively mature for medium density and state-of-the-art digital circuits. In the opposite scenario, analog circuits do not take advantage of Moore's law. On the one hand, they are necessary in most of the System-on-Chip (SoC) devices, and analog circuit size is not reduced in the same rate as digital circuits are. On the other hand, scaling down can introduce some problems. The process variability, which affects not only transistors, but also passive

components in a much higher significant amount. Also, testing analog circuits is not that easy as it is for their digital counterparts, since the signals are defined in the whole range of voltage from ground to +/-Vdd, and the output is often embedded in the SoC, thus reducing the observability. One of the main analog circuits that suffer from the scaling problem, specifically the parameter variation problem, is the filter. For analog filters, whose cutoff frequency, gain and quality factor must be, in many cases, extremely accurate, small deviations in capacitors, resistors and/or inductors values may lead to a complete mismatch between the expected and achieved cutoff frequency, for example. Also, parameters like maximum allowed ripple in the pass-band, minimum attenuation in the stop-band and others must be taken into account when designing these systems. Even if one carefully designs a capacitor to obtain a certain value, the fabrication process can not guarantee an exact replication of this capacitor all through the entire circuit, leading, very often, to the increase of expensive trimming circuits, in order to tune the filter response. Moreover, yield becomes a problem due to the same replication problem, that is, it is hard to obtain the same accuracy for all capacitors in a certain filter production lot. Back to manufacturing test, it is then necessary to identify from the specifications those circuits where parametric errors may lead to a single specification out of the  $6\sigma$  range. Offsets, characteristic frequencies, quality factors and many other specifications parameters are considered.

This thesis is organized as it follows: in chapter 2 and 3, respectively, two new solutions are presented to the SEU and SET problems, where more details about SEU and SET occurrence, consequences to the circuit and related solutions will also be explained. In chapter 4 a solution for the mismatch problem is depicted, which will also contribute to a whole digital test approach, thus leading to a yield increase. Each chapter presents its own introduction and conclusion, while chapter 5 presents the final remarks and the main contributions from this work, as much as the future works.

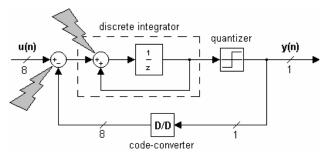

#### 2 SIGMA-DELTA MODULATION TO COPE WITH SEU IN DIGITAL CIRCUITS

It has been a consensus that CMOS transistor gate length will overcome the nanometric barrier, allowing the inclusion of a huge number of these devices on a single die, even more than the enormous integration density shown these days [ITRS, 2006]. Nevertheless, it has also been claimed that this integration phenomenon will bring undesirable consequences as well. One of the most critical ones is the reduction in the circuit node capacitances which, in spite of allowing faster circuits with clock speed reaching many dozens of gigahertz, will also be responsible by the increase in the soft-errors occurrence.

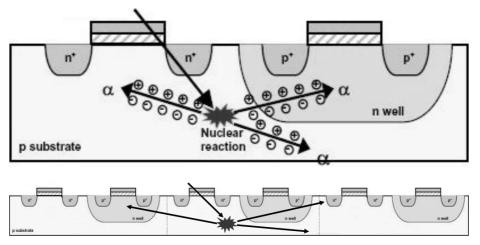

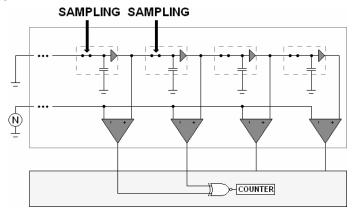

One of the main consequences of soft-errors is the Single Event Upset (SEU), caused by a particle hitting a CMOS junction, which can result in a bit flip that can be propagated all through the rest of the circuit operation [YANG, 1992], [MESSENGER, 1992]. Most of the reported SEU effects concern the manifestation of single faults in digital circuits, caused by the inversion of one single bit. However, multiple bits inversion has also been demonstrated in some works [SMITH, 1992], indicating that this is an expected scenario for future technologies. One can observe in figure 1 [ROSSI, 2005] that, for a given CMOS technology, a particle hit will affect one transistor. Now, if a newer technology is used, more transistors can be constructed in the same area occupied by one transistor in the older technology. As a consequence, the same particle hit can now affect more than one transistor, causing multiple SEUs.

Figure 1: Multiple faults can occur when technology advances [ROSSI, 2005].

Most techniques used to develop robust circuits use different solutions, which can be divided basically in three different categories, described bellow, all of them actuating in different abstraction levels: technology, design and system level.

In the technology level, different processes are used in the transistor fabrication, such as epitaxial-bulk CMOS, which was first conceived to isolate the analog part from the digital one in mixed-signals designs. In this technique, an extra mask is used to etch a trench from the backside of the wafer all the way to the under-surface of the field oxide [BASEDAU, 1995]. Although the use of epitaxial-bulk is efficient to reduce the Single Event Latch-Up (SEL), it does not mitigate the occurrence of SEU. Another technique is the use of Silicon on Insulator (SOI), where a thin layer of silicon is placed on top of an insulator, such as silicon oxide or glass, and then the transistor is built on top of this layer [IBM, 2005]. This technique was first developed to be used in memories for space applications, since these memories built on SOI were perceived to be more resistant to SEU. Further studies showed that in order to reduce power consumption and to increase speed in digital circuits, the use of SOI could be a good alternative. This technique, however, requires the use of special fabrication process, with consequent yield limitation, and does not completely mitigate the occurrence of SEU.

Hardening at the design level includes, for example, the use of hardened gate resistor memory cells [WEAVER, 1987] and hardened CMOS memory cells with feedback structures [RABAEY, 1996], which imply in physically larger memory blocks, since extra parts must be added to the memory cell. For example, in the gate resistor memory cells, two resistors are built using two levels of polysilicon and, although the impact in the circuit density is small, these resistors are temperature sensitive, increasing the memory vulnerability in low temperatures. Another solution in the design level is the use of codification and decodification of logic blocks, using, for example, Hamming [MACKAY, 2003] or Reed-Solomon [PLANK, 1996] techniques. Hamming Code is an error-detecting and error-correcting binary code that can detect all single-bit and double-bit errors and correct all single-bit errors. The Reed-Solomon code, however, is able to detect and to correct multiple and consecutive data errors. Although these are good solutions, when multiple faults must be corrected, the cost to do so, in terms of time and complexity, makes their use impractical. Also, multiple and simultaneous faults can not be corrected using these approaches. Moreover, the coder and decoder circuits are also sensitive to transient upsets, reducing the overall reliability, even with the added costs.

To protect digital circuits at the system level, the use of hardware or software redundancy techniques are the most known ones. For the hardware case, the use of Triple Modular Redundancy (TMR) [CHANDE, 1989] rises as the most diffused scheme. TMR in its various implementations simply implies in triplicating the sensitive block and making a vote, where the correct system response is determined by majority. Of course, some problems stand out here. For example, the area and power penalties, which are triplicated as well. The other limitation appears when one thinks in simultaneous faults, that is, if two blocks give wrong responses, by majority, the final response will also be wrong. Also, with less probability to occur, if the fault happens in the voter block, there is no way to define whether the response is correct or not. Using software redundancy, some techniques such as Algorithm Based Fault Tolerance [HUANG, 1984] and Code Flow Check are used, as well as variable

duplication [REBAUDENGO, 1998], which can automatically be implemented on the highlevel code of the program. This technique, applied to memories and registers, performs two different modifications to the source code; the first one corresponds to duplicating some or all of the program variables in order to introduce data redundancy, and modifying all the operators to manage the introduced replica of the variables. The second source code modification aims at introducing consistency checks inside the control flow to periodically verify the consistency between the two copies of each variable.

Most of the previously proposed schemes are based on hardware or software redundancy, where the hardware block or the software variable is triplicated, and the correct system response is given by majority voting. Looking at the problem from a different perspective, we now propose a new kind of redundancy, based on signal redundancy.

The main idea does not imply in triplicating the signal to be processed, but in creating another way to represent the signal, in such a way that, even under the occurrence of multiple faults, the final response still sustains an acceptable resolution. The technique, which uses sigma-delta modulation (a review can be found in [NORSWORTHY, 1997]) to generate the redundant signal, is to be used in digital circuits and, as it will be shown, can imply, in some cases, in smaller and faster circuits. In the cases where area and time penalties proposed by other solutions are smaller than the solution herein proposed, the achieved fault-tolerance becomes a decisive factor to determine the use of our approach.

A new perspective is presented, where one does not need to worry whether the fault will occur or not, because even if it occurs, the circuit will be protected. That is, we do not try to mitigate or to correct the circuit response corrupted by the faults. We simply let the fault occur, because thanks to the redundancy already presented in the signal, the consequence of the fault will not be so harmful for the system response. This technique, allied to the idea of error tolerance proposed in [GUPTA, 2004], can guarantee that the system will develop appropriate responses even under the occurrence of multiple and simultaneous faults.

#### **2.1 ERROR TOLERANT SYSTEMS**

According to [JOHNSON, 1993], "fault tolerance is the ability of a system to continue correct operation of its tasks after hardware or software faults occur", while correct operation means that no errors occur at any system output. In [GUPTA, 2004], it is mentioned that "fault tolerance tries to provide reliable operation in the presence of lifetime faults and/or externally induced transient errors". This way, it has also been proposed in [GUPTA, 2004] the following definition of error tolerance when considering systems that can tolerate a certain amount of errors at the entire system's output: "a circuit can be error tolerant with respect to an application if it contains defects that cause internal errors and might cause external errors, and the system that incorporates this circuit produces acceptable results".

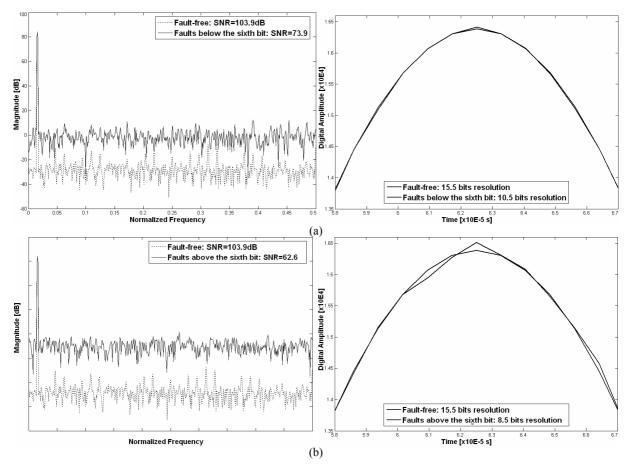

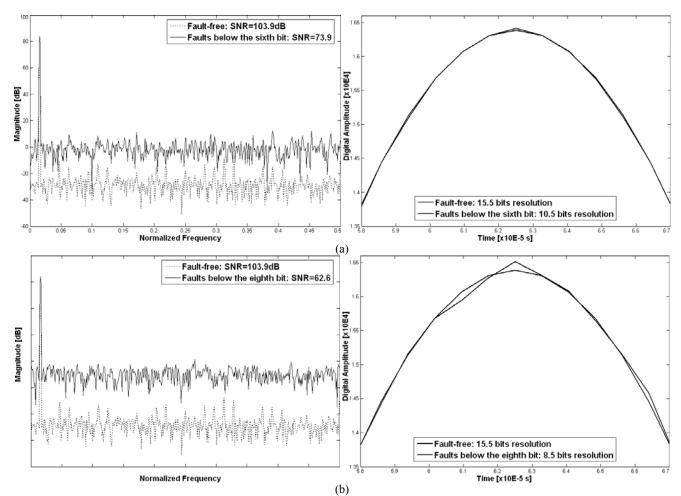

The very simple results presented in figure 2 can clarify the notion of error tolerant system, and the idea behind minimum resolution required to a certain error tolerant system generating correct output responses. In this example, a digital oscillator must generate a 10-bit minimum resolution sine wave with a certain frequency, offset and phase. This is equivalent to say that the expected Signal to Noise Ratio (SNR) of the output signal must be at least 71dB. Thus, any signal generated with a SNR below this threshold shall not be satisfactory to the system operation. However, if the faults occurring during the signal generation do not cause a perturbation high enough to make the SNR drop below this fixed value, the signal will be properly used by the system. In figure 2(a), different bits, below the sixth one, are inverted each time one point is produced by the oscillator, causing a small perturbation in the signal shape, but still maintaining a SNR higher than 73dB (10.5 bits resolution), thus above the requested 71dB. However, when the bits which are inverted change to those above the sixth

one (see figure 2(b)), the output signal presents a significant variation, causing a 11dB drop in the SNR, leading to a malfunction behavior, since the new resolution now is about 8.5 bits (62dB). So, one can say that, for this very simple circuit, it is error tolerant as long as one can be sure that faults do not occur in bits that are higher than the sixth one.

Figure 2: Error tolerant signal generation. In (a), resolution is compatible with system requirements, while in (b) faults make resolution drop below 10 bits.

Another interesting proposition, which also makes use of the error tolerance approach, is the one presented in [NEPAL, 2005], where a probabilistic-based design methodology based on Markov Random Fields is examined. According to [NEPAL, 2005], "the Markov Random Fields approach can express arbitrary logic circuits and the logic operation is achieved by maximizing the probability of correct state configurations in the logic network depending on the interaction of neighboring circuit nodes". The basic idea is that the computation is realized by propagating states through the circuit in a probabilistically fashion, assuming that a large number of nanodevices is presented, thus requiring very low power

operation with consequent probabilistic behavior, since transistor will be operating near the thermal limit. Nevertheless, since the idea presented in [NEPAL, 2005] supposes a huge number of transistors presented in the digital circuit, the solutions make use of many of these transistors to construct a simple logic gate. For example, a simple CMOS inverter, which uses only two transistors, is now developed by using 20 of these devices, while a NAND gate is conceived through the use of 60 MOS transistors, instead of four as the standard one.

With the idea of error tolerance in mind, one can find a lot of applications that contain the property of being error tolerant, that is, applications in which the final response can still be correct, even after the insertion of a large amount of faults, in our case, transient faults caused by radiation or noise interference. Also, as seen before, redundancy is one of the most used techniques to cope with fault occurrence. Based on that, we now propose a new paradigm, which is based on signal redundancy. The idea behind this solution is not based, for example, on triplicating the n-bit words of the input signal, but rather on creating a new version of the input signal, representing it in a redundant fashion through the use of another signal domain representation. The next sections describe the methodology used to create this signal, and give some results that support our decision in using such signal depiction.

#### 2.2 SIGNAL REDUNDANCY PARADIGM

As shown before, the use of redundancy is very common when fault-tolerance must be achieved by a system. Besides the already mentioned TMR in hardware redundancy, and variable duplication in software redundancy, others techniques may be used, such as space and/or time redundancy [ANGHEL, 2000], where the concomitant use of a self-checking combinational circuit and a state-preserving element is employed. Now, based on the idea of redundancy, we propose changing the paradigm, where the redundant element is intrinsic to the data that will be processed. Although this may seem similar to a classical redundant approach, here we do not duplicate the data, but rather we represent information in another domain, which can still be processed in a digital like manner.

The basic idea is to take a single n-bit Pulse Code Modulated (PCM) word, thus in the digital domain, and change the way this word is represented. This change is such that the n-bit word now becomes an m-bit word, where m > n, and it is no more a digital representation of the data, but a redundant representation, which can still be processed by digital circuits.

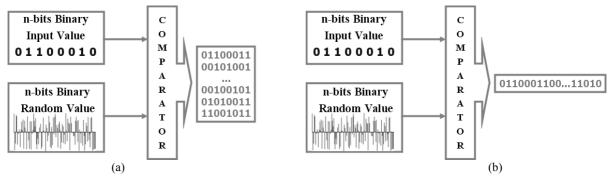

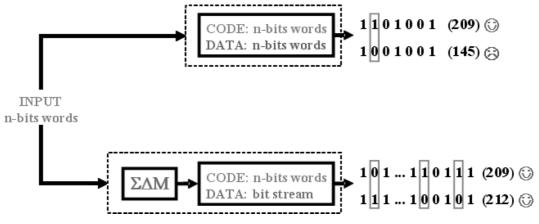

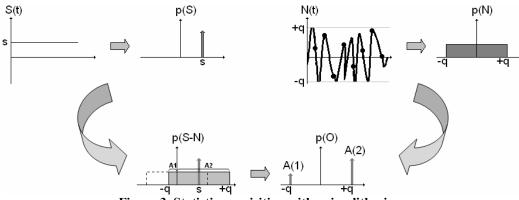

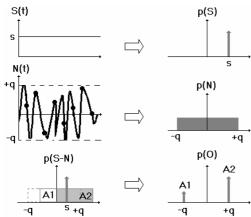

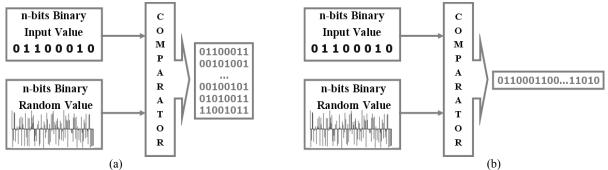

There are different ways to obtain redundant signals. For example, as represented in figure 3(a), one can simply compare an n-bit word with an n-bit random noise, and the output n-bit words will be a representation of the input value [JANER, 1996]. A simpler solution would be based on the same principle, but the signal comparison now generates a 1-bit bit stream, containing the input signal probabilistic representation [JANER, 1996], as shown in figure 3(b). However, in order to obtain a good resolution to represent the input signal, the output bit stream length must be in the range of thousands of bits, as demonstrate some results using this kind of signal representation in [LISBÔA, 2004].

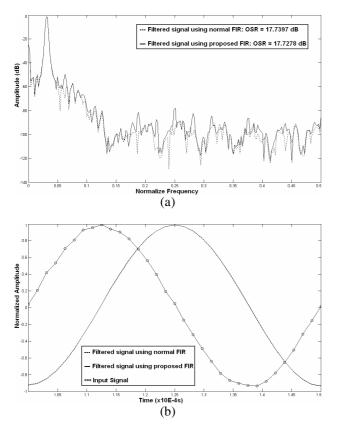

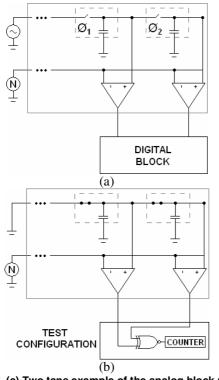

Figure 3: Redundant signal generation through signal/noise comparison. In (a) an n-bit word stream is generated, while in (b) an 1-bit bit stream is achieved.

A better way to produce signals with intrinsic redundancy, capable of representing large bit words, but with a low implementation cost and a much smaller bit stream, is by using sigma-delta modulation [NORSWORTHY, 1997], [CANDY, 1992]. With this kind of signal generation, one can represent signals with a resolution larger than 20 bits, with lots of redundancy by using a very simple scheme. It is important to emphasize that, although sigma-delta modulators are most commonly found in analog-to-digital converters (using analog

sigma-delta modulators), what we are proposing here is the use of digital sigma-delta modulators to transform an n-bit digital word into a sigma-delta representation of the same signal. The modulator output signal, represented by a sequence of zeros and ones, will then be used in the subsequent application. An explanation regarding digital sigma-delta modulators, how they work and which kind of signals they generate is presented in section 2.3.1.

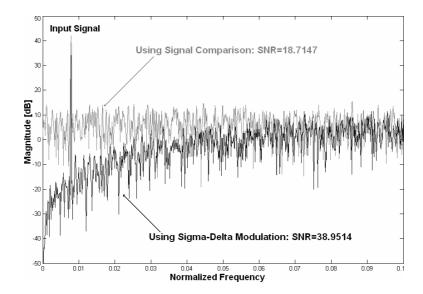

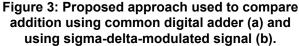

To conclude the idea of signal redundancy and show the advantages of using a sigmadelta representation instead of, for example, the previously mentioned technique of signal/noise comparison, an example comparing these two kinds of signal representation is presented in figure 4. Here, a 10 KHz sine wave is sampled with an Over Sampling Ratio (OSR) equal to 64, that is, it is sampled with a frequency 64 times higher than the signal Nyquist frequency. Firstly, the sampled signal is represented by a bit stream produced through the comparison of each sampled point to a uniformly distributed random noise, as presented before in figure 3(b). On the other hand, the same sampled signal is now modulated through the use of a first-order sigma-delta modulator, generating another bit stream, also representing the input signal. As one can see, for the same OSR, thus for the same output bit stream length (128 bits per signal period in this case), the achieved SNR to the signal comparison case is approximately equal to 19dB, while for the sigma-delta modulation case, the SNR almost reaches 39dB. So, as mentioned and now demonstrated, the use of sigma-delta modulation generates more accurate results with the same number of bits in the bit stream.

Figure 4: Comparison between two different ways to generate redundant signals: through noise/signal comparison and through sigma-delta modulation.

# 2.3 SIGMA-DELTA MODULATED-SIGNALS AND ITS USE IN REDUNDANT SIGNAL Generation

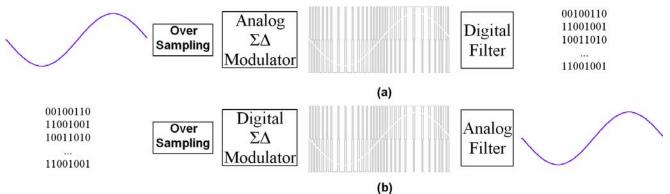

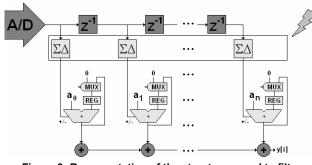

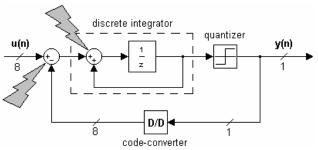

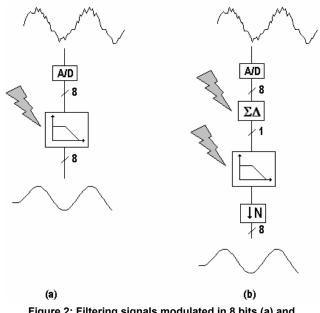

The main utilization of sigma-delta modulation is in Analog-to-Digital Converters (ADC), in the manner presented in figure 5(a), where the analog input signal is over-sampled, converted to a 1-bit representation through the analog sigma-delta modulator, and then down-sampled (or decimated) in order to obtain a digital representation of the analog input signal. This kind of signal modulation can produce converted signals with high resolutions, by using small sampling ratios when compared to others over-sampled converters [CANDY, 1992]. Others applications to sigma-delta modulators are in the generation of test-signals [ROBERTS, 1995], signal-processing [MALOBERTI, 1992] [DIAS, DA FONTE, 1994] and, of course, Digital-to-Analog Converters (DAC) [NORSWORTHY, 1997], [CANDY, 1992]. In the DAC case (see figure 5(b)), the digital input signal is over-sampled, converted to the sigma-delta domain through a digital sigma-delta modulator, and finally low-pass filtered to generate the analog signal representation. A brief explanation of how a sigma-delta modulator works and which kinds of signals are generated after the modulation are presented next, in section 2.3.1.

Figure 5: (a) Analog to Digital conversion and (b) Digital to Analog conversion with sigma-delta modulators.

#### 2.3.1 Sigma-Delta Modulation

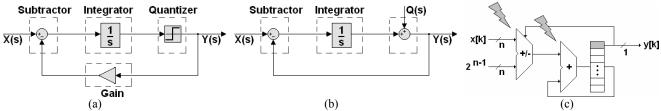

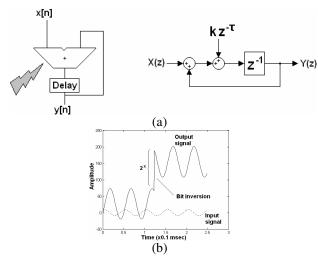

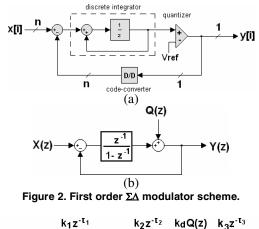

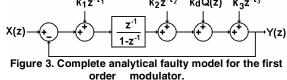

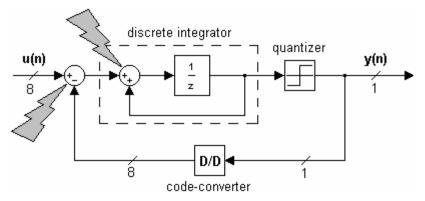

The sigma-delta modulator is the main block in a sigma-delta ADC or DAC (see figure 5), since this is the block that will pass the over-sampled input signal from the analog/digital to the sigma-delta domain for further filtering through a digital/analog low-pass filter, and consequent conversion to digital/analog representation. Consider the generic first-order sigma-delta modulator represented in figure 6(a). The structure, known as an error feedback structure, consists of four basic blocks: an input subtractor, an integrator, a quantizer and a feedback gain. The basic idea is that the quantization error produced by the two-level quantizer is fed back to the circuit input, and subtracted from the input signal. The difference between the input signal and the fed back quantization error is integrated, and then quantized to generate an output represented by a 1-bit bit stream, whose mean value is equal to the mean value of the input signal [NORSWORTHY, 1997].

Figure 6: (a) First-order sigma-delta modulator implementation and (b) quantization noise-model.

Analyzing this kind of circuit by the frequency point of view allows one to understand why one can obtain high resolutions using such a simple circuit. To do that, some considerations must be done regarding the modulator characteristics, mainly, the quantization noise generated by the two-level quantizer. For more details about these considerations, the reader is encouraged to consult references [NORSWORTHY, 1997] and [CANDY, 1992]. At this point, in order to present a brief analysis of how the modulator frequency response behaves, we assume that the modulator presents the following characteristics regarding the quantization error: the quantization error is largely uncorrelated from sample to sample to the input signal, and has equal probability of lying anywhere in the range  $\pm D/2$ , where D is the quantization level amplitude. This way, the quantization error can be represented by a noise Q(s), as shows the model presented in figure 6(b). Analyzing the transfer function of this model from the signal input X(s) and from the quantization noise input Q(s), one has:

$$\frac{Y(s)}{X(s)} = \frac{1}{s+1}$$

Signal Transfer Function (STF) (1)

$$\frac{Y(s)}{Q(s)} = \frac{s}{s+1}$$

Noise Transfer Function (NTF) (2)

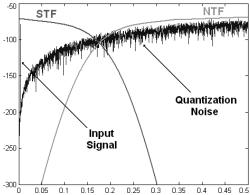

Analyzing equations (1) and (2), one can notice that the signal transfer function (STF) is a low-pass function, while the noise transfer function (NTF) is a high-pass function. As a consequence, the output signal will be represented by the input signal in low-frequencies plus the quantization noise in high-frequencies. Figure 7(a) presents a sinusoidal signal modulated by a sigma-delta modulator with a certain sample frequency. As noted, due to this particular response, one can achieve high signal to noise ratios, which can be increased by increasing the modulator over sapling ratio or the modulator order. It can be shown [NORSWORTHY, 1997] that, for the first-order modulator, the SNR *versus* OSR relation is given by:

$$SNRdb = 10\log\left(\frac{3}{2}2^{2\pi}OSR^{3}\frac{3}{\pi^{2}}\right)$$

(3)

where n is the number of bits of the modulator quantizer. Equation (3) can be written as:

$$SNRdb = 1.76 + 6.02n + 30\log(OSR) - 5.17$$

(4)

that is, one has an increase of 6dB *per* bit of the quantizer and 9dB for each doubling in the sampling frequency. The increase of the SNR according to the modulator order and the OSR is shown in figure 7(b).

Figure 7: (a) Signal Transfer Function (STF) and Noise Transfer Function (NTF) for a sigma-delta modulator: low-pass and high-pass to achieve high SNR. (b) Increase of the SNR according to the OSR and the modulator order.

For the higher-order sigma-delta modulators, different topologies are available. The simplest way to implement such systems is shown in figure 8. Just by substituting the modulator quantizer by a first-order modulator, higher-order modulator can be implemented. However, due to instability factor, this recursive method is limited to third-order modulators [NORSWORTHY, 1997]. The instability problem can be overcame through the use of different topologies, such as cascade-modulators (MASH) [CANDY, 1986] [UCHIMURA, 1988], utilization of multi-bit quantizer [LESLIE, 1992], use of feed-forward and feedback coefficients [CHAO, 1990] and others.

Figure 8: Replicating first-order modulators to generate high-order ones.

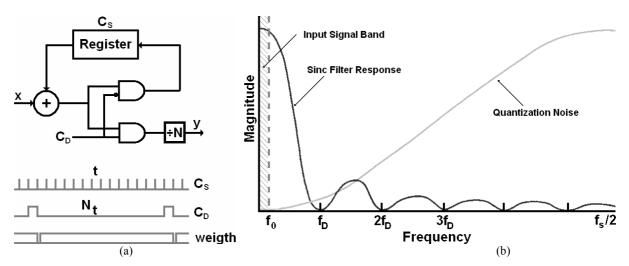

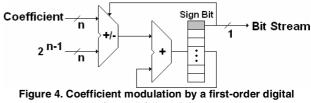

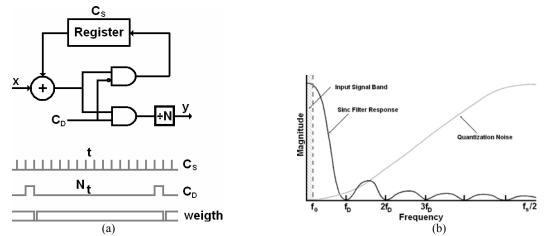

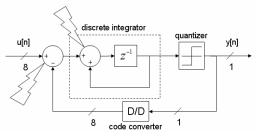

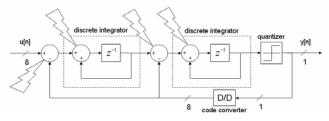

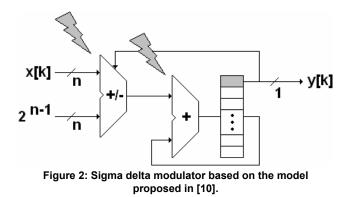

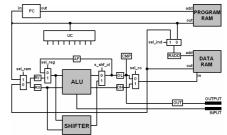

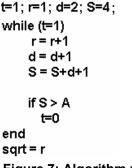

It is important to note that, if one desires to implement an analog modulator, thus an analog version of the blocks in figure 6(a) must be constructed, and the most common technique used to do it is a switched-capacitor implementation [BOSER, 1988]. In this case, the feedback gain is a one-level DAC, which simply feeds back a positive or a negative voltage value, depending on the value of the output bit stream. In our case, we want to make a digital modulator because the input signal is digital, and we want it to be converted to a sigma-delta representation. So, the modulator of figure 6(a) must be implemented either in hardware or software. In figure 9(a) an example of how this simple modulator could be implemented in hardware is presented. Here, the quantizer is substituted by simply taking the integrator sign, and this sign will choose whether an addition or a subtraction of the input value and a constant value is done, substituting, thus, the feedback gain, whose function is to convert the output 1-bit signal to an n-bit value compatible with the input signal. A software implementation of this same modulator is presented in figure 9 (b).

Figure 9: (a) Example of hardware implementation for a digital modulator and (b) example of software implementation of the same modulator.