# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## ISRAEL DA COSTA LOPES

# Convolutional Neural Network Reliability on an APSoC platform - a traffic-sign recognition case study

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Altamiro Amadeu Susin

Porto Alegre November 2017

## **CIP** — **CATALOGING-IN-PUBLICATION**

Lopes, Israel da Costa

Convolutional Neural Network Reliability on an APSoC platform - a traffic-sign recognition case study / Israel da Costa Lopes. – Porto Alegre: PGMICRO da UFRGS, 2017.

94 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2017. Advisor: Altamiro Amadeu Susin.

1. Deep learning. 2. Traffic-sign recognition. 3. Soft errors. 4. System-on-Chip. I. Susin, Altamiro Amadeu. II. Título.

# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

| "If I have seen farther than others,               |

|----------------------------------------------------|

| it is because I stood on the shoulders of giants." |

| — SIR ISAAC NEWTON                                 |

## **ACKNOWLEDGEMENTS**

Agradeço a Deus e minha família que me deram todo o suporte emocional, financeiro e proteção. Ao meu orientador Altamiro Susin que me incentivou e me deu as diretrizes necessárias para a conclusão do meu mestrado. A Professora Fernanda que me introduziu aos conceitos de tolerância a radiação, análise de confiabiliadade e que me apoiou em trabalhos de campo para experimentos de radiação. Aos meus colegas aos quais colaboraram muito para meu crescimento acadêmico e profissional. A CAPES por prover a bolsa de mestrado permitindo que eu pudesse me dedicar exclusivamente ao mestrado. E a todos os técnicos e funcionários da UFRGS que tornaram tudo isso possível.

#### **ABSTRACT**

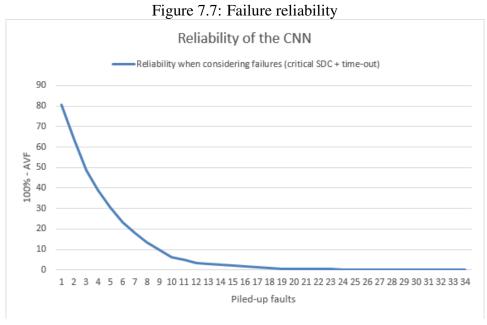

Deep learning has a plethora of applications in computer vision, speech recognition, natural language processing and other applications of commercial interest. Computer vision, in turn, has many applications in distinct areas, ranging from entertainment applications to relevant and critical applications. Face recognition and manipulation (Snapchat), and object description in pictures (OneDrive) are examples of entertainment applications. Industrial inspection, medical diagnostics, object recognition in images captured by satellites (used in rescue and defense missions), autonomous cars and Advanced Driver-Assistance System (ADAS) are examples of relevant and critical applications. Some of the most important integrated circuit companies around the world, such as Xilinx, Intel and Nvidia are waging in dedicated platforms for accelerating the training and deployment of deep learning and other computer vision algorithms for autonomous cars and ADAS due to their high computational requirement. Thus, implementing a deep learning system that achieves high performance with low area utilization and power consumption costs is a big challenge. Besides, electronic equipment for automotive industry must be reliable even under radiation effects, manufacturing defects and aging effects, inasmuch as if a system failure occurs, a car accident can happen. Thus, a Convolutional Neural Network (CNN) VHSIC (Very High Speed Integrated Circuit) Hardware Description Language (VHDL) automatic generator was developed to reduce the design time associated to the implementation of deep learning algorithms in hardware. As a case study, a CNN was trained by the Convolutional Architecture for Fast Feature Embedding (Caffe) framework, in order to classify 6 traffic-sign classes, achieving an average accuracy of about 89.8% on the German Traffic-Sign Recognition Benchmark (GTSRB) dataset, which contains trafficsigns images in complex scenarios. This CNN was implemented on a Zynq-7000 All-Programmable System-on-Chip (APSoC), achieving about 313 Frames Per Second (FPS) on 32x32-normalized images, with the APSoC consuming only 2.057 W, while an embedded Graphics Processing Unit (GPU), in its minimum operation mode, consumes 10W. The proposed CNN reliability was investigated by random piled-up fault injection by emulation in the Programming Logic (PL) configuration bits of the APSoC, achieving 80.5% of reliability under Single-Bit-Upset (SBU) where both critical Silent Data Corruptions (SDCs) and time-outs were considered. Regarding the multiple faults, the proposed CNN reliability exponentially decreases with the number of piled-up faults. Hence, the proposed CNN reliability must be increased by using hardening techniques during the design flow.

**Keywords:** Deep learning. Traffic-sign recognition. Soft errors. System-on-Chip.

# Confiabilidade de uma Rede Neural Convolucional em uma plataforma APSoC - um caso de estudo para reconhecimento de placas de trânsito

#### **RESUMO**

O aprendizado profundo tem inúmeras aplicações na visão computacional, reconhecimento de fala, processamento de linguagem natural e outras aplicações de interesse comercial. A visão computacional, por sua vez, possui muitas aplicações em áreas distintas, indo desde o entretenimento à aplicações relevantes e críticas. O reconhecimento e manipulação de faces (Snapchat), e a descrição de objetos em fotos (OneDrive) são exemplos de aplicações no entretenimento. Ao passo que, a inspeção industrial, o diagnóstico médico, o reconhecimento de objetos em imagens capturadas por satélites (usadas em missões de resgate e defesa), os carros autônomos e o Sistema Avançado de Auxílio ao Motorista (SAAM) são exemplos de aplicações relevantes e críticas. Algumas das empresas de circuitos integrados mais importantes do mundo, como Xilinx, Intel e Nvidia estão apostando em plataformas dedicadas para acelerar o treinamento e a implementação de algoritmos de aprendizado profundo e outras alternativas de visão computacional para carros autônomos e SAAM devido às suas altas necessidades computacionais. Assim, implementar sistemas de aprendizado profundo que alcançam alto desempenho com o custo de baixa utilização de área e dissipação de potência é um grande desafio. Além do mais, os circuitos eletrônicos para a indústria automotiva devem ser confiáveis mesmo sob efeitos da radiação, defeitos de fabricação e efeitos do envelhecimento. Assim, um gerador automático de VHSIC (Very High Speed Integrated Circuit) Hardware Description Language (VHDL) para Redes Neurais Convolucionais (RNC) foi desenvolvido para reduzir o tempo associado a implementação de algoritmos de aprendizado profundo em hardware. Como estudo de caso, uma RNC foi treinada pela ferramenta Convolutional Architecture for Fast Feature Embedding (Caffe), de modo a classificar 6 classes de placas de trânsito, alcançando uma precisão de cerca de 89,8% no conjunto de dados German Traffic-Sign Recognition Benchmark (GTSRB), que contém imagens de placas de trânsito em cenários complexos. Essa RNC foi implementada num All-Programmable System-on-Chip (APSoC) Zyng-7000, resultando em 313 Frames Por Segundo (FPS) em imagens normalizadas para 32x32, com o APSoC dissipando uma potência de somente 2.057 W, enquanto uma Graphics Processing Unit (GPU) embarcada, em seu modo de operação mínimo, dissipa 10 W. A confiabilidade da RNC proposta foi investigada por injeções de falhas acumuladas e aleatórias por emulação nos *bits* de configuração da Lógica Programável (LP) do APSoC, alcançando uma confiabilidade de 80,5% sob *Single-Bit-Upset* (SBU) onde foram considerados ambos os Dados Corrompidos Silenciosos (DCSs) críticos e os casos em que o sistema não respondeu no tempo esperado (*time-outs*). Em relação às falhas múltiplas, a confiabilidade da RNC decresce exponencialmente com o número de falhas acumuladas. Em vista disso, a confiabilidade da RNC proposta deve ser aumentada através do uso de técnicas de proteção durante o fluxo de projeto.

**Palavras-chave:** Aprendizado profundo. Reconhecimento de placas de trânsito. Erros *Soft*, Sistema-em-Chip..

# LIST OF ABBREVIATIONS AND ACRONYMS

ADAS Advanced Driver-Assistance System

AI Artificial intelligence

AVF Architectural Vulnerability Factor

SDC Silent Data Corruption

ACE Architecturally Correct Execution

CNN Convolutional Neural Network

APSoC All-Programmable System-on-Chip

MPSoC Multiprocessor System-on-Chip

FinFET Fin-Field Effect Transistor

SoC System-on-Chip

PS Processing System

PL Programming Logic

DUT Design Under Test

AXI Advanced eXtensible Interface

ICAP Internal Configuration Access Port

GPIO General Purpose Input/Output

BRAM Block Random Access Memory

SRAM Static Random Access Memory

ROM Read Only Memory

DDR Double Data Rate

LUT Look Up Table

FF Flip-Flop

DSP Digital Signal Processing

MACC Multiply and Accumulate

GTSRB German Traffic-Sign Recognition Benchmark

SVM Support Vector Machine

**HOG** Histogram of Oriented Gradients

ReLU Rectified Linear Unit

FSM Finite State Machine

CLAHE Contrast Limited Adaptive Histogram Enhancement

FI Fault Injection

SEU Single-Event-Upset

SBU Single-Bit-Upset

MBU Multibit-Upset

FPGA Field Programmable Gate Array

RISC Reduced Instruction Set Computer

CLB Configurable Logic Block

CPU Central Processing Unit

GPU Graphics Processing Unit

TCAD Technology Computer Aided Design

I2C Inter-Integrated Circuit

CAN Controller Area Network

AMBA Advanced Microcontroller Bus Architecture

SMC Static Memory Controller

ASIC Application Specific Integrated Circuit

Caffe Convolutional Architecture for Fast Feature Embedding

VLSI Very-Large-Scale Integration

VHSIC Very High Speed Integrated Circuits

VHDL VHSIC Hardware Description Language

LMDB Lightning Memory-Mapped Database

BSD Berkeley Software Distribution

UART Universal Asynchronous Receiver/Transmitter

USB Universal Serial Bus

SPI Serial Peripheral Interface

# LIST OF FIGURES

| Figure 2.1 Faster R-CNN Region Proposal Network (RPN)                               | 21 |

|-------------------------------------------------------------------------------------|----|

| Figure 2.2 YOLO Detection System                                                    | 22 |

| Figure 2.3 Block diagram of the SVM method                                          | 22 |

| Figure 2.4 a) DNN architecture b) DNN trainig c) Multi-column deep DNN              | 23 |

| Figure 2.5 a) Multi-block Normalization Local Binary Pattern (MN-LBP) features      |    |

| with threshold b) Split-Flow Cascade structure                                      | 24 |

| Figure 2.6 a) Classical Sparse Representation Classification (SRC) method b) Pro-   |    |

| posed Extended Sparse Representation Classification method (ESRC) method            | 24 |

| Figure 2.7 Block diagram of the SHOG + SBRP/SBMP classification process             | 25 |

| Figure 2.8 The pipeline of the traffic-sign recognition system                      | 25 |

| Figure 2.9 Lenet-based Convolutional Neural Network                                 |    |

| Figure 2.10 2-D image Convolutional                                                 | 28 |

| Figure 2.11 Max pooling illustration                                                |    |

| Figure 2.12 A sketch of a biological neuron                                         |    |

| Figure 2.13 Full-connected neuron                                                   |    |

| Figure 2.14 ReLU activation function                                                |    |

| Figure 2.15 Nvidia DRIVE PX 2 technical characteristics                             |    |

| Figure 2.16 ADAS SoC micrograph                                                     |    |

| Figure 2.17 INT8 Deep Learning Power Efficiency Comparison: Xilinx vs. Intel        |    |

|                                                                                     |    |

| Figure 3.1 The comparison of the effects of a SEU in ASIC and FPGA architecture     | 38 |

| Figure 3.2 Upset in the LUT (logic change)                                          |    |

| Figure 3.3 Upset in the routing (undesirable connection)                            | 40 |

| Figure 3.4 Static cross-section for the configuration of the largest device of each |    |

| family                                                                              | 40 |

| Figure 4.1. One counts of each CTCDD along                                          | 11 |

| Figure 4.1 One sample of each GTSRB class                                           |    |

| Figure 4.2 Variations of one class                                                  |    |

| Figure 4.3 Sub-classes of each super class                                          |    |

| Figure 4.4 One sample of each sub-class of the super class "Others"                 |    |

| Figure 4.5 6 classes of the Prohibitory subclass                                    |    |

| Figure 4.6 Pre-processing steps                                                     |    |

| Figure 4.7 Steps for training a model with Caffe                                    |    |

| Figure 4.8 Reduced LeNet-based CNN model                                            |    |

| Figure 4.9 Training accuracy and loss                                               |    |

| Figure 4.10 Convolution filters                                                     |    |

| Figure 4.11 Feature images                                                          | 52 |

| Figure 5.1 CNN automatic generation steps                                           | 53 |

| Figure 5.2 CNN VHDL code generation steps                                           |    |

| Figure 5.3 CNN implementation in the APSoC platform                                 |    |

| Figure 5.4 Xilinx 7 Series DSP48E1 Slice                                            |    |

| Figure 5.5 CNN implementation top module                                            |    |

| Figure 5.6 Convolution-1 control component state machine                            |    |

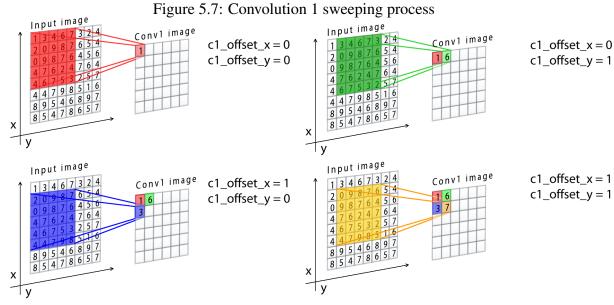

| Figure 5.7 Convolution 1 sweeping process                                           |    |

| Figure 5.8 CNN sweeping process                                                     |    |

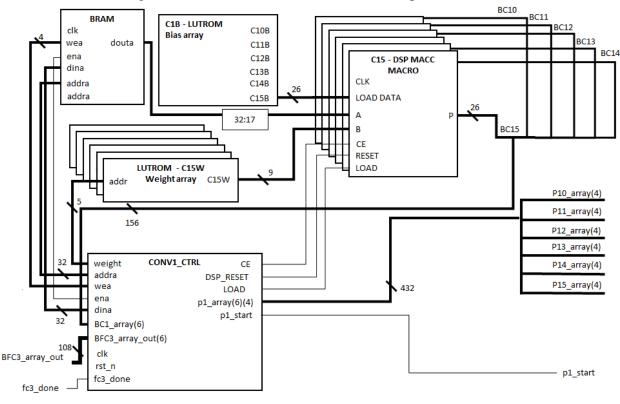

| Figure 5.9 Convolution 1 - Control and datapah                                      |    |

| Figure 5.10 ZedBoard                                                                |    |

| 1 15ulv J. 10 AUDUUU                                                                | ບວ |

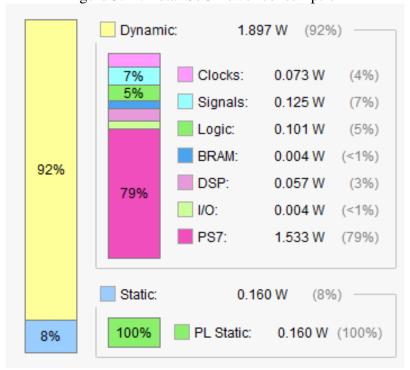

| Figure 5.11 Total So  | oC Power consumption                                       | 67       |

|-----------------------|------------------------------------------------------------|----------|

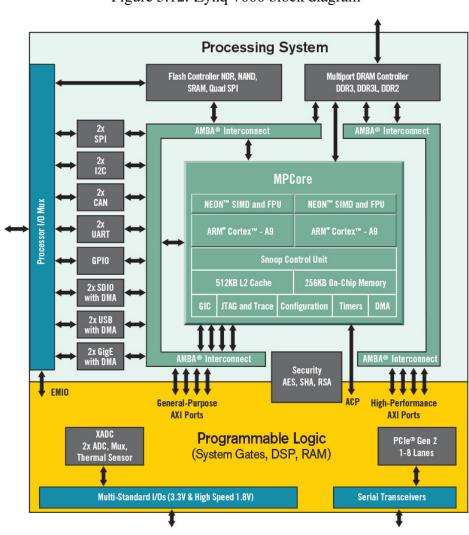

|                       | 000 block diagram                                          |          |

|                       | _                                                          |          |

| Figure 6.1 Piled-up   | fault injection flowchart                                  | 70       |

| Figure 6.2 Faulty hi  | ierarchy                                                   | 71       |

| Figure 6.3 Failure n  | nodel APSoC CNN                                            | 72       |

| Figure 6.4 Fault inje | ection setup                                               | 73       |

| _                     | erface component expansion                                 |          |

| Figure 6.6 ARM ap     | plication algorithm                                        | 75       |

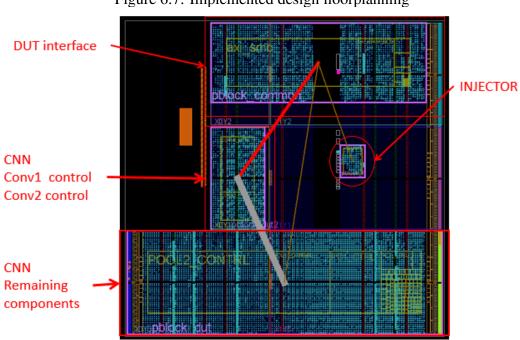

| Figure 6.7 Impleme    | ented design floorplanning                                 | 76       |

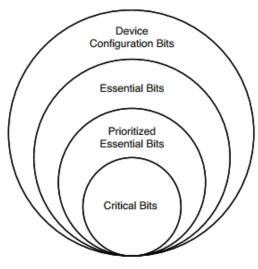

| Figure 7.1 Relations  | ship of Device Configuration Bits, Essential Bits, Prior   | ritized  |

| Essential Bits,       | and Critical Bits                                          | 78       |

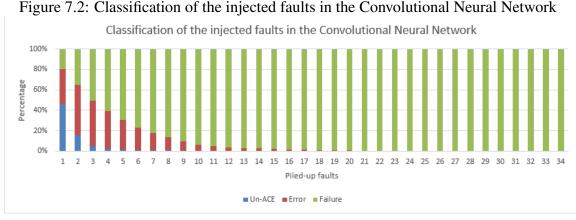

| Figure 7.2 Classific  | ation of the injected faults in the Convolutional Neural N | etwork79 |

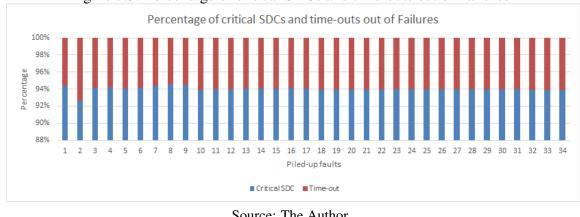

| Figure 7.3 Percentag  | ge of critical SDCs and time-outs out of Failures          | 80       |

| Figure 7.4 Number     | of critical SDCs and time-outs out of the Failures         | 80       |

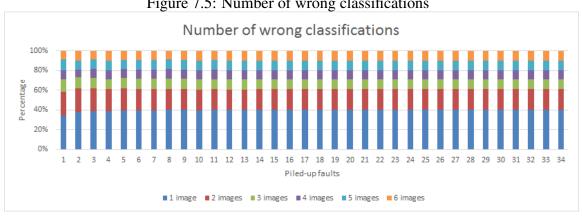

| Figure 7.5 Number     | of wrong classifications                                   | 82       |

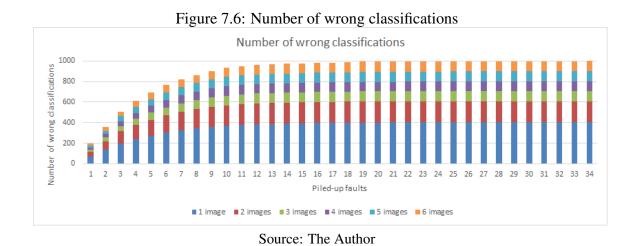

| Figure 7.6 Number     | of wrong classifications                                   | 84       |

| _                     | eliability                                                 |          |

# LIST OF TABLES

| Table 2.1       | CNN Models with Fixed-Point Precision. The numbers in brackets indi- |     |

|-----------------|----------------------------------------------------------------------|-----|

| cate a          | accuracy without fine-tuning                                         | 34  |

|                 |                                                                      |     |

| Table 4.1       | Parameters used in the model                                         | 47  |

| Table 4.2       | Parameters used in the solvers                                       | 48  |

| Table 4.3       | Training accuracy for different solvers                              | 49  |

| Table 4.4       | False negatives and False positives                                  | 51  |

|                 |                                                                      |     |

| Table 5.1       | CNN signal bit widths                                                | 55  |

| Table 5.2       | FPGA resource utilization                                            | 64  |

| Table 5.3       | Performance results                                                  | 65  |

| Table 5.4       | CNN feature abbreviations                                            | 65  |

| m 11 <i>m</i> 1 | N 1 6 12 10DG 12 12 12 13 14 15 15                                   | 0.1 |

|                 | Number of critical SDCs and time-outs out of the Failures            |     |

| Table 7.2       | Number of wrong classifications (absolute values)                    | 83  |

# **CONTENTS**

| 1 INTRODUCTION                                  | 16          |

|-------------------------------------------------|-------------|

| 1.1 Motivation                                  | 18          |

| 1.2 Goals and Contribution                      | 18          |

| 2 DEEP LEARNING ALGORITHMS FOR TRAFFIC-SIGN REC | COGNITION20 |

| 2.1 Convolutional Neural Networks               | 26          |

| 2.1.1 Convolutional Layer                       | 27          |

| 2.1.2 Pooling Layers                            | 29          |

| 2.1.3 Full-connected neurons                    |             |

| 2.1.4 ReLU Activation function                  | 30          |

| 2.1.5 Softmax function                          | 31          |

| 2.2 Acceleration platforms for Deep Learning    | 32          |

| 2.2.1 Embedded GP-GPUs                          | 32          |

| 2.2.2 ASIC SoC and APSoC                        | 33          |

| 3 RADIATION EFFECTS IN INTEGRATED CIRCUITS      | 36          |

| 3.1 Radiation effects in SRAM-based FPGAs       | 38          |

| 4 CONVOLUTIONAL NEURAL NETWORK TRAINING         | 41          |

| 4.1 Dataset                                     |             |

| 4.2 Framework for training                      | 44          |

| 4.2.1 Training process using Caffe              | 45          |

| 4.2.2 Training results                          | 49          |

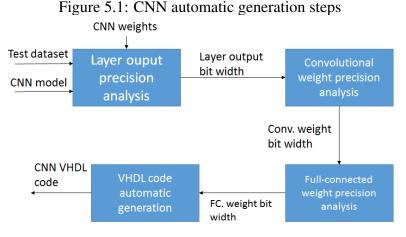

| 5 DEVELOPMENT OF CNN TOPOLOGY                   | 53          |

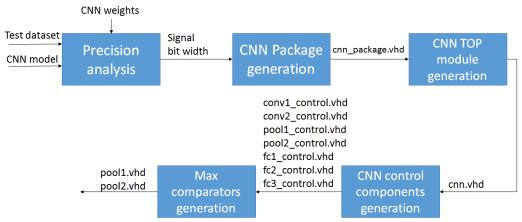

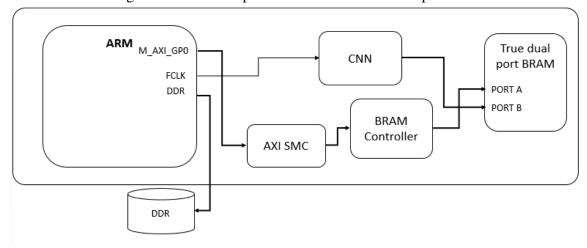

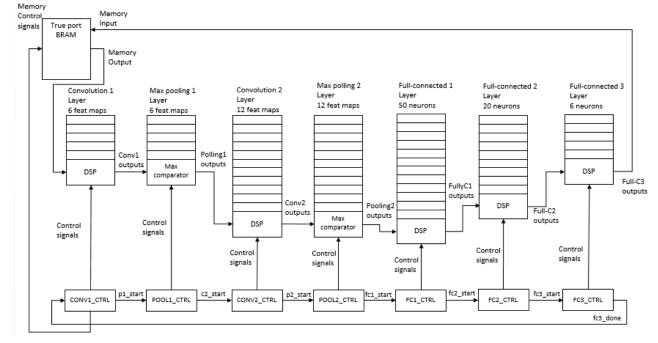

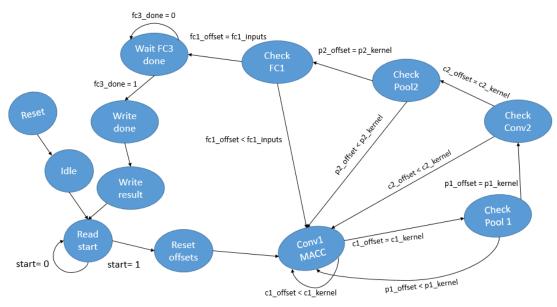

| 5.1 Automatic generator                         | 53          |

| 5.2 Timing Multiplexing Architecture            | 55          |

| 5.3 APSoC Implementation results                |             |

| 6 FAULT INJECTION BY EMULATION                  | 69          |

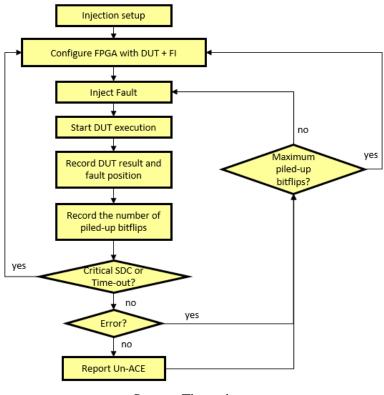

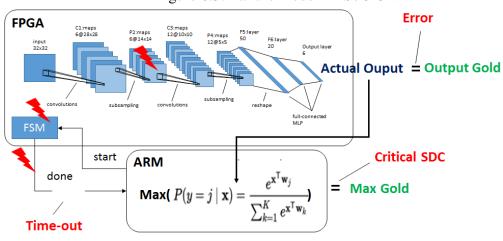

| 6.1 Failure Model                               | 71          |

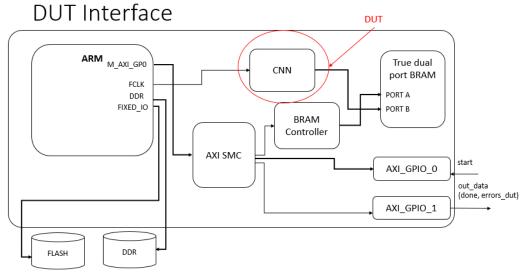

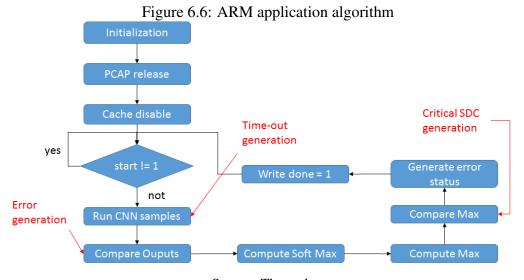

| 6.2 Experimental Setup                          | 72          |

| 7 RELÎABILITY RESÛLTS                           |             |

| 8 CONCLUSIONS                                   | 87          |

| 8.1 Future Work                                 | 88          |

| REFERENCES                                      | 89          |

#### 1 INTRODUCTION

Humankind has trusted on technology to get better living standards since the very early stages of the civilization. The construction of equipment and artifacts is always limited by the available technology. Starting with a stick as defense accessory and a lever to multiply its force, humankind learned to transform energy and to build complex mechanisms during the industrial revolution (DERRY; WILLIAMS, 1960). But it was the use of electricity as a support for signal processing and communication that enabled more sophisticated apparatuses for the daily life and process automation. Even though some digital operations were possible with pneumatic or electromagnetic relay circuits, it was the advent of digital electronic computer that pushed further the possibility of information processing and systems programmability (RABAEY; CHANDRAKASAN; NIKOLIC, 2002). But it is the evolution of the micro and nanoelectronics technology that is nowadays bringing to reality the dream of the electronic brain of the middle of the 19th century (HAYKIN; NETWORK, 2004).

Artificial Intelligence (AI) is an object of research in several domains and even commercial applications are running based on AI. Many tasks that are typically considered "human tasks" like language translation, face recognition, speech recognition and natural language processing are being automated. The most common architecture used in AI is the Neural Network (NN) that was traditionally built with a few levels, typically three, and is now using more than ten levels and is called "deep learning" or Convolutional NN (CNN) (GOODFELLOW; BENGIO; COURVILLE, 2016) (HAYKIN; NETWORK, 2004). The possibility of training such systems to control complex activities like to drive in a city traffic allowed the development of Advanced Driver Assistance System (ADAS) with the goal of decreasing the number of accidents. Also, this technology spurred the development of autonomous cars (XILINX-AUTOMOTIVE, 2016)(HUANG, 2016).

In the context of autonomous cars and ADAS, deep learning is used to emulate the vision of a driver (GOODFELLOW; BENGIO; COURVILLE, 2016). One of the visual tasks that can be performed by means of deep learning algorithms is traffic-sign recognition. In the International Joint Conference on Neural Networks (IJCNN) many machine learning algorithms were evaluated on GTSRB dataset and the Convolutional Neural Networks achieved excellent results even better than the individual human and average human performance (STALLKAMP et al., 2011). Therefore, using Convolutional Neural Networks is an excellent approach to classify traffic-signs.

Deep learning vision systems deployed in autonomous cars must have a fast response time. In addition, this system cannot consume high power to avoid high thermal dissipation. Graphics Processing Units (GPUs) achieve excellent performance results due to their thread-level parallelism but they have high power consumption (HUANG, 2016)(NVIDIA, 2016). Application Specific Integrated Circuits (ASICs) can achieve excellent performance with low power cost (LEE et al., 2017) but deep learning algorithms are constantly evolving, thus a platform with more flexibility has to be chosen. All-Programmable System-on-Chip (APSoC) alternatives are flexible, that is, it is possible to update the implemented deep learning algorithm. In general, the implementations in this platform obtain balanced power and performance results (XILINX-AUTOMOTIVE, 2016), for this reason, it is an excellent choice for autonomous cars and ADAS applications. However, the PL part of the APSoC platform has peculiar radiation effects, therefore these effects must be analyzed in order to characterize an implemented design under soft-errors (KASTENSMIDT; CARRO; REIS, 2006).

CNN training is a very time-consuming task, so the use of a framework is necessary (JIA et al., 2014). Therefore, the Caffe framework was used to train a case study CNN to classify 12 sub-classes within the super class "Prohibitory" from the GTSRB dataset. Initially, a CNN model was trained achieving an average accuracy of 90.0%. However, the implementation of this CNN model on the APSoC platform exceeded the available resources of the PL part. Then, the CNN model was reduced to one that classifies half of the prohibitory sub-classes. The CNN was re-trained and the accuracy results were preserved. A VHDL automatic generator for CNNs was developed in order to reduce the required design time for implementing CNNs in APSoCs.

The proposed CNN reliability was analyzed by means of fault injection by emulation. Three types of effects were considered in the reliability evaluation, errors, failures and un-Application Correct Execution (un-ACE). Errors are discrepancies in the CNN output which do not change the correct traffic-sign classification. Failures can be classified into critical SDCs and time-outs. Critical SDCs are discrepancies in the CNN output which change the correct traffic-sign classification, while time-outs mean the CNN does not send the response in the defined execution time. The un-ACE effect takes place when none of these effects occur (MUKHERJEE et al., 2003).

#### 1.1 Motivation

Statistics show that the majority of accidents is caused by reckless driving (NHTSA, 2013), thus some accidents can be avoided if an autonomous car is available (GERLA et al., 2014). In addition, ADAS is also useful to reduce the chance of accidents happening (GERONIMO et al., 2010). Since driving is mainly performed using human visual senses, computer vision algorithms must be used to emulate human vision. Deep learning is a branch of AI that has many successful applications in computer vision, speech recognition, natural language processing and other areas of commercial interest (GOOD-FELLOW; BENGIO; COURVILLE, 2016).

Autonomous car applications are safety-critical and hard-real-time embedded systems. So, they must have a deterministic and fast response time in order to avoid accidents (BERGER, 2002) (LIU; NARAYANAN; BAI, 2000). If a deep learning vision system is deployed in an autonomous car, it must have a good and predictable execution time. Power consumption is also a concern in embedded system because it will lead to high thermal dissipation.

Electronic systems are susceptible to many sources of fault that can compromise safety of a computer vision application for an autonomous car. Therefore, the faults that can cause a failure or a time mismatch in the system must be analyzed and mitigated. They can be caused by manufacturing defects (stuck-at-0, stuck-at-1 and etc) (KAJIHARA et al., 1995), aging effects (WANG et al., 2007) or radiation effects (SEU, SET and so on) (BAUMANN, 2005). The International Organization for Standardization (ISO) established a standard for the automotive electronic production in 2011, the ISO 26262 (ISO-26262, 2011). This standard requires some fault modes to be analyzed during the design flow, these faults include stuck-at-0, stuck-at-1, Single Event Upset (SEU) and Single Event Transient (SET). On that account, a fault analysis methodology must be incorporated in the design flow to validate the design in terms of dependability (otherwise known as reliability) (SINHA, 2011).

#### 1.2 Goals and Contribution

The main contribution of this work is the analysis of reliability in a traffic-sign recognition CNN operating under soft error and implemented on an APSoC platform. The related work analyzes the performance and average accuracy of their traffic-sign

recognition approaches, but does not analyze their reliability under soft-errors (LEE et al., 2017)(HAN; ORUKLU, 2014)(CIREŞAN et al., 2012)(WANG et al., 2013)(LIU et al., 2016)(YANG et al., 2016) (KASSANI; TEOH, 2017). The goals of this work are as follows:

- To train a deep learning algorithm to recognize traffic-signs in order to obtain good average accuracy results in a short time.

- To perform a hardware acceleration of the trained deep learning algorithm, minimizing its power, area and design time.

- To analyze the reliability of the proposed deep learning approach under soft-errors

Chapter 2 will show a survey concerning the deep learning state-of-the art algorithms and the characteristics of the embedded platforms to accelerate them, as well as the Convolutional Neural Networks foundations. In Chapter 3, the terminology of the radiation effects in integrated circuits will be introduced, then the ground-level effects of the radiation and the specific radiation effects in Field Programmable Gate Arrays (FPGAs) will be addressed. In Chapter 4, the methodologies and tools used for the Convolutional Neural Network training as well as the training results will be discussed. Chapter 5 will explain how the VHDL automatic generator works, then the implementation results will be discussed. In Chapter 6, the reliability analysis alternatives will be compared, then the Fault injection setup will be explained. In Chapter 7, the reliability results will be discussed, as well as their possible causes. Lastly, in Chapter 8, the conclusions will be given followed by prospective future projects.

#### 2 DEEP LEARNING ALGORITHMS FOR TRAFFIC-SIGN RECOGNITION

Autonomous cars are systems whose function is prompt delivery of the passengers to the destination with maximum safety and comfort and minimum impact on the environment (GERLA et al., 2014), whereas Advanced Driver Assistance System (ADAS) is an intelligent on-board system that aims to anticipate accidents in order to avoid them or mitigate their severity (GERONIMO et al., 2010). Some examples of autonomous car and ADAS tasks are lane detection, pedestrian detection, traffic-sign recognition and visual simultaneous localization and mapping (ALVES, 2017)(SANTOS, 2017)(HOELSCHER, 2017) (FUENTES-P; RUIZ-A; RENDÓN-M, 2015).

As autonomous car and ADAS tasks are emulations of the vision of a driver, they are implemented by computer vision algorithms. The computer vision algorithms, in turn, can be developed with computer vision libraries (BRADSKI; KAEHLER, 2008) or by deep learning frameworks (JIA et al., 2014). The difference between computer vision algorithms and deep learning algorithms is that in computer vision algorithms the programmer develops all the steps required for the computer vision solution, whereas deep learning algorithms use artificial intelligence algorithms to solve computer vision tasks. Artificial intelligence algorithms need a dataset to train the deep learning algorithm in order to learn some task (HAYKIN; NETWORK, 2004). For example, if one wants to recognize traffic-signs in an image, a dataset containing traffic-sign images samples must be presented to the deep learning algorithm in order to train it to perform a traffic-sign recognition.

Traffic-sign recognition activity is part of a more generic computer vision task called object classification. In order to recognize one object in an image, two steps are required: detection and classification. Detection is the process of scanning an image to find some objects. While classification is the process of placing these detected objects in classes (i.g. cars, pedestrians or traffic-signs), and then these objects are classified into sub-classes within their super classes (i.g different traffic-signs, types of cars) (YANG et al., 2016).

The state-of-the-art methods either use one machine learning algorithm to detect and classify objects or use image processing algorithms to detect objects and machine learning algorithms to classify these objects. The state-of-the-art machine learning algorithms that detect and classify objects are the Faster Region-based Convolutional Neural Network (Faster R-CNN) (REN et al., 2015) and the You Only Look Only-Once (YOLO)

2k scores

4k coordinates

k anchor boxes

cls layer

256-d

intermediate layer

sliding window

conv feature map

Figure 2.1: Faster R-CNN Region Proposal Network (RPN)

Source: (REN et al., 2015)

(REDMON et al., 2016). The main contributions of the Faster R-CNN are described in the list bellow and Figure 2.1 shows the Faster R-CNN Region Proposal Network (RPN).

- Higher detection quality than R-CNN and Spatial Pyramid Pooling Network (SPPnet) (HE et al., 2014)(GIRSHICK et al., 2014)

- Training is single-stage, using a multi-task loss

- Training can update all network layers

- No disk storage is required for feature caching

The YOLO CNN behavior is described in the list below and Figure 2.2 illustrates the object detection and classification.

- Divides the image into regions

- Predicts bounding boxes and probabilities for each region

- Bounding boxes are weighted by the predicted probabilities

- Threshold the detection by some value to only see high scoring detection

The scope of this chapter is only to evaluate the deep learning algorithms for traffic-sign classification, and the Faster R-CNN and YOLO are models that classify many types of classes. Therefore, the focus will be on deep learning algorithms that have distinct detection and classification blocks. Each block uses its own dataset, i.e. German Traffic-Sign Detection Benchmark (GTSDB) for detection and German Traffic-Sign Recognition Benchmark (GTSRB) for classification. The GTSRB dataset has 43 classes and more than 50,000 (39,209 for training and 12,630 for testing) sub-images and the GTSDB has 900 images (600 for training and 300 for evaluation) (STALLKAMP et al., 2011) (HOUBEN et al., 2013).

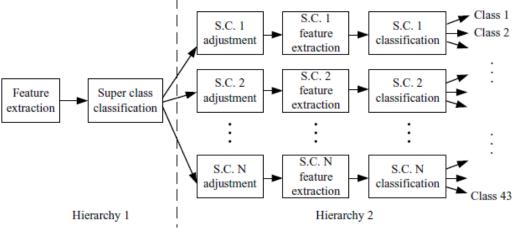

Wang (2013), employs a hierarchical methodology to detect and classify the German traffic-signs. The block diagram of his proposed method is illustrated in Figure

Bounding boxes + confidence

S x S grid on input

Glass probability map

Figure 2.2: YOLO Detection System

Source: (REDMON et al., 2016)

Figure 2.3: Block diagram of the SVM method

Fig. 3. Block diagram of the proposed method

Source: (WANG et al., 2013)

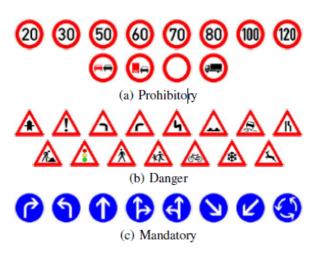

2.3. Firstly, in the detection stage, important features from traffic-signs such as colors and shapes are extracted using medium-level image processing algorithms. Then, these features are used to classify the proposals into super classes (Prohibitory, Danger, Mandatory, Derestriction and Unique) using a Support Vector Machine (SVM). Each super class has a different perspective adjustment. In the classification stage, the adjusted and detected traffic-signs are classified within super classes using another SVM, explaining the meaning of "hierarchical methodology". The key concept in (WANG et al., 2013) is the super-class-oriented adjustment, which improves and simplifies the classification process, reaching a state-of-the-art average accuracy of 99.52%.

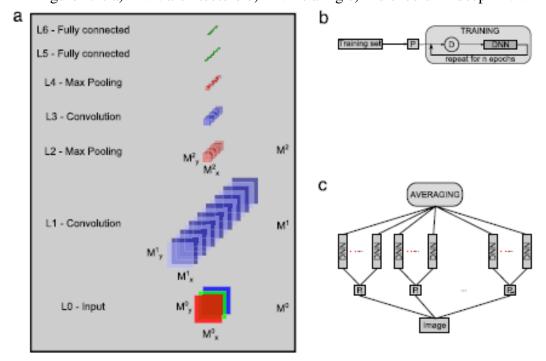

Differently from the former work, the scope of the Multi-column Deep Neural

Figure 2.4: a) DNN architecture b) DNN trainig c) Multi-column deep DNN

Source: (CIREŞAN et al., 2012)

Network (MC-DNN) (CIREŞAN et al., 2012) is only to classify the German traffic-signs, so only the GTSRB dataset is used. When using this approach neither super class nor subclass is used, rather all 43 classes are classified by one complex DNN topology. "Multicolumn deep" means there are 7 DNNs in parallel and the final output is the average of all of the DNN outputs. This methodology permits unseen features by one DNN to be seen by another one, which results in a high average accuracy of 99.46%. Figure 2.4 shows the a) Deep Neural Network topology, training process (b) and Multi-column DNN (c).

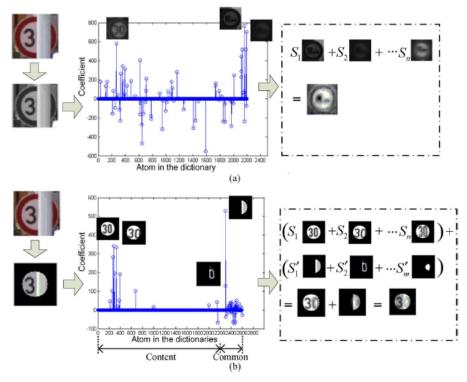

High Contrast Region Extraction (HCRE) and the Extended Sparse Representation (ESR) perform both the detection and the classification tasks (LIU et al., 2016). In the detection phase, the HCRE is performed based on the Viola-Jones-like detector and the Split Flow Cascade (SFC) Tree. Regarding the classifying phase, the ESR approach is based on an under-sampled face recognition algorithm which is considered to be an occlusion robust method. To such degree, this work achieves competitive accuracy (98.5%) and performance results for high resolution images. Figure 2.5 illustrates the detection process and Figure 2.6 illustrates the classification process.

Soft Histogram Oriented Gradient (SHOG) (KASSANI; TEOH, 2017) is focused on the classification block. It is a variant of Histogram Oriented Gradient (HOG) approach because it exploits the symmetry shape of traffic-signs. Through this medium, SHOG is more discriminative than HOG. After the features are generated using the SHOG

Figure 2.5: a) Multi-block Normalization Local Binary Pattern (MN-LBP) features with threshold b) Split-Flow Cascade structure

Source: (LIU et al., 2016)

Figure 2.6: a) Classical Sparse Representation Classification (SRC) method b) Proposed Extended Sparse Representation Classification method (ESRC) method

Source: (LIU et al., 2016)

Figure 2.7: Block diagram of the SHOG + SBRP/SBMP classification process

Source: (KASSANI; TEOH, 2017)

Figure 2.8: The pipeline of the traffic-sign recognition system

Fig. 1. The pipeline of the proposed traffic sign recognition system.

Source: (YANG et al., 2016)

approach, two training methods were introduced, the Sparse Bayesian Multivariate Polynomial (SBMP) and the Sparse Bayesian Reduced Polynomial (SBRP) model. These training methods enabled implicit feature selection and lead to a competitive average accuracy of 98.17%. Figure 2.7 shows the block diagrams involved in the classification process.

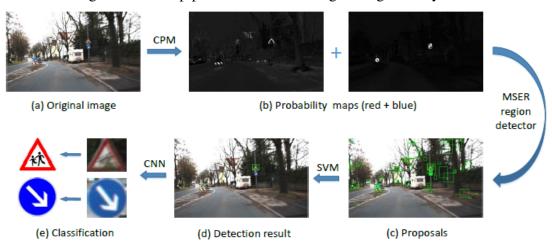

In the work of (YANG et al., 2016), the German traffic-sign detection is performed in four stages as seen in figure 2.8. Firstly, the images are processed by a Color Probability Model (CPM) that produces the probability of a pixel color belonging to a traffic-sign color (Figure 2.8 (b)). Then, the proposals are extracted using the Maximally Stable Extremely Regions (MSER) (Figure 2.8 (c)). After which, the proposal features are extracted using the HOG, and then are classified into super classes (Prohibitory, Danger and Mandatory) using a SVM (Figure 2.8 (d)). Thereafter, in the classification stage, one CNN per super class classifies the detected proposals into sub-classes (Figure 2.8 (e)).

Figure 2.9 illustrates the CNN topology used in the classification phase. This is based on a basic CNN, the LeNET (LECUN; BENGIO et al., 1995), which enables an excellent inference computation time and a competitive average accuracy of 97.75%.

F5:layer C1:maps C3:maps 32@10x10 S4:maps 16@28x28 800 F6:layer S2:maps 32@5x5 output input 16@14x14 layer 32x32 convolutions convolutions subsampling subsampling full-connected MLP

Figure 2.9: Lenet-based Convolutional Neural Network

Source: (YANG et al., 2016)

#### 2.1 Convolutional Neural Networks

Convolutional Neural Networks differ from the other Neural Networks by processing data that have grid-like topology, such as time-series that can be thought as 1-dimension-grid taking samples at regular intervals and image data that can be thought as 2-dimension-grid pixels. Convolutional Neural Networks (CNNs) were designed to extract features and recognize shapes with a high degree of invariance to translation, scaling, skewing and other forms of distortion. A Neural Network is said to be convolutional when it is composed by at least one convolutional layer. Regarding the CNN training, it is performed by supervised or unsupervised learning algorithms (HAYKIN, 1994) (GOODFELLOW; BENGIO; COURVILLE, 2016) (JAIN; MAO; MOHIUDDIN, 1996) (LECUN; BENGIO et al., 1995). The mathematical definition of convolution used in the Convolutional Neural Networks differs from the definition used in engineering and pure mathematics, indeed the correct term for the operation used in Convolutional Neural Networks is cross-correlation. However, it was popularized as "convolution" in literature.

The mathematical representation of a 2-dimension-discrete convolution is given in Equation 2.1, where i and j are the dimensional indexes, K is the convolutional kernel, I is the input, \* is the convolution-operation symbol, and lastly m and n are the sum indexes. The mathematical representation of a 2-dimension-discrete cross-correlation is provided in Equation 2.2. As it can be noted, the only difference between the convolution and the cross-correlation is that in the cross-correlation neither kernel nor input is flipped. Flipping operation is not done in cross-correlation operation because this property is not useful for neural networks (GOODFELLOW; BENGIO; COURVILLE, 2016). When cross-correlation is referred in this work, this will mean convolution, following the

literature.

$$S(i,j) = (K*I)(i,j) = \sum_{m} \sum_{n} I(i-m,j-n)K(m,n)$$

(2.1)

$$S(i,j) = (K*I)(i,j) = \sum_{m} \sum_{n} I(i+m,j+n)K(m,n)$$

(2.2)

## 2.1.1 Convolutional Layer

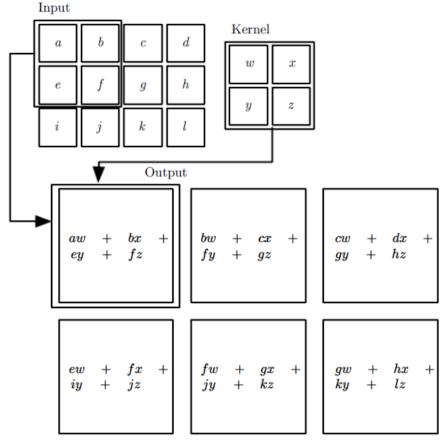

The Convolutional Layer is responsible for extracting features from input images. The convolutional neuron receptive fields are sub-images from the previous layers whose dimensions are defined by the kernel size, thus local features are extracted. Each resultant image is stored in a feature map and all the convolutional neurons from a feature map share the weight matrix that has the same dimensions of the kernel. The weight sharing reduces the number of trainable free parameters, reducing the capacity of the learning machine, which in turn improves its generalization ability (HAYKIN; NETWORK, 2004) (LECUN; BENGIO et al., 1995). The mathematical definition of a convolution for a single image is given in Equation 2.3 (GONZALEZ; WOODS, 2002).

$$g(x,y) = \left[\sum_{s=-a}^{a} \sum_{t=-c}^{c} w(s,t) f(x+s,y+t)\right] + b$$

(2.3)

$$a = floor(kernel\_size\_x/2)$$

(2.4)

$$c = floor(kernel\_size\_y/2)$$

(2.5)

Where g is the resultant pixel from the convolution, x and y are the coordinates of the image, a and c are normalized sum limits calculated from the kernel sizes defined in Equations 2.4 and 2.5, w is the weight or kernel, f is the sub-image or window that is sampling the input image, and lastly b is the convolutional bias. An illustration of the convolutional computation is given in Figure 2.10. Note that when the kernel size dimensions are even values they cannot be normalized, because there is no central pixel.

Equation 2.3 described the mathematical operation of a convolutional layer that succeeds the input layer, i.e. there is only one input image. However, from the second

Figure 2.10: 2-D image Convolutional

Source: (GOODFELLOW; BENGIO; COURVILLE, 2016)

layer onwards, the convolutional inputs are many feature map images instead of only one image, as such each convolutional neuron in the current layer computes the convolution for each one of the feature maps in the previous layer. Therefore, each one of the feature maps in the current layer has a weight matrix for each one of the feature maps in the previous layer. The mathematical representation of the convolution taking into account many input images are given in Equation 2.6 (GOODFELLOW; BENGIO; COURVILLE, 2016).

$$g(x,y) = \left[\sum_{n} \sum_{s=-a}^{a} \sum_{t=-b}^{b} w(s,t,n) f(x+s,y+t,n)\right] + b$$

(2.6)

Where n is the feature map index of the previous layer which is used in the weight tensor and input images.

Input image (4x4)

Polling image (2x2)

2 0 9 8

0 9 8 7

4 7 6 2

2 pixels stride

Figure 2.11: Max pooling illustration

Source: The Author

# 2.1.2 Pooling Layers

Each Convolutional layer is followed by a Pooling layer that performs the operation of subsampling, whereby the resolution of the feature map is reduced. The rate of the resolution reduction depends on the pooling kernel size and stride, as illustrated in Figure 2.11. This subsampling operation reduces the noise sensibility and other types of distortion. It is possible because pooling layers employ statistical ordering, which is also used in low-level image processing spatial filters for noise reduction (GONZALEZ; WOODS, 2002). The pooling layer can be employed using different functions, such as max, average and etc (HAYKIN, 1994) (GOODFELLOW; BENGIO; COURVILLE, 2016). The max pooling was used, therefore it is implemented in the hardware using max-comparator units.

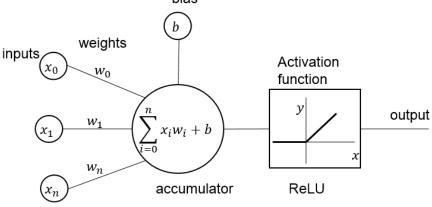

# 2.1.3 Full-connected neurons

Full-connected (FC) neurons are Multi-Layer Perceptron (MLP) feedforward neural networks (HAYKIN, 1994). This class of Artificial Neural Networks (ANNs) is widely used in classification tasks and has many successful implementations in literature (HAYKIN; NETWORK, 2004) (GOODFELLOW; BENGIO; COURVILLE, 2016). The specialty of this neural network is pattern recognition, but can also be used in data analysis. The full-connected neurons are based on biological neurons, as illustrated in Figure 2.12.

Pendrites

Synapse

Nucleus

Source: (JAIN; MAO; MOHIUDDIN, 1996)

Figure 2.13: Full-connected neuron bias

Source: The Author

So they have the dendrites, synapses, cell-body and axon. As illustrated in Figure 2.13, the dendrites are implemented by multiplying the inputs by the weights (synapses). The cell-body, otherwise known as "soma", accumulates the result of the multiplications and adds it with the bias. The axon performs the activation function (ReLU, which is described in the following) that is the output of the neuron and is connected to many other neurons (JAIN; MAO; MOHIUDDIN, 1996) (HAYKIN, 1994). In Hardware, the FC neuron computation can be performed either using MACC units or logic circuits.

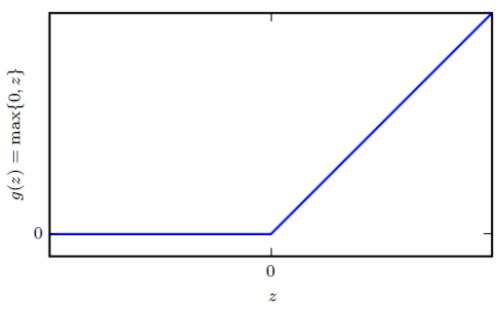

#### 2.1.4 ReLU Activation function

Rectified Linear Unit (ReLU) activation function employs the function g(z) = max(0, z), as illustrated in Figure 2.14. It applies non-linearity either in Convolutional or FC neuron outputs but preserves some linear properties, simplifying the optimization process by learning algorithms (GOODFELLOW; BENGIO; COURVILLE, 2016). Due

Figure 2.14: ReLU activation function

Source: (GOODFELLOW; BENGIO; COURVILLE, 2016)

to its simplicity and efficiency, the ReLU is the default recommendation in modern neural networks (NAIR; HINTON, 2010) (GOODFELLOW; BENGIO; COURVILLE, 2016). In hardware, it has a considerable area-saving in comparison to sigmoid activation functions. The ReLU hardware implementation requires just a greater than 0 comparator.

# 2.1.5 Softmax function

The Softmax function is a way of improving the classification results. It computes the probability vector of the classes and increases the difference between the neuron outputs, as defined in Equation 2.7 (BRIDLE, 1990).

$$O_j = \frac{\exp I_j}{\sum_k \exp I_k} \tag{2.7}$$

Where O is the softmax output, I is the softmax input (FC neuron outputs), j is the index of the neuron being computed and k is the index of the other neurons. Softmax computation requires a great amount of hardware resources due to the sums of exponential, so it will be developed in software.

Figure 2.15: Nvidia DRIVE PX 2 technical characteristics

|         | TITAN X | DRIVE PX 2                                    |

|---------|---------|-----------------------------------------------|

| Process | 28nm    | 16nm FinFET                                   |

| CPU     | _       | 12 CPU cores<br>8-core A57 +<br>4-core Denver |

| GPU     | Maxwell | Pascal                                        |

| TFLOPS  | 7       | 8                                             |

| DL TOPS | 7       | 24                                            |

Source: (HUANG, 2016)

# 2.2 Acceleration platforms for Deep Learning

## 2.2.1 Embedded GP-GPUs

Nvidia corporation releases the first Graphics Processing Unit (GPU) for Personal Computers (PCs) in 1999, revolutionizing the PC industry (NVIDIA, 2017). Initially, this platform was intended to accelerate game applications, but due to its high computation power, it is also used in general-purpose applications, such as deep learning, medicine and etc, as such it is called General Purpose GPU (GP-GPU) (VISWANATHAN; HUSSEIN, 2017) (DING et al., 2011).

Deep-learning GP-GPU implementations achieve high performance results due to their massive parallel computation (NVIDIA, 2016). Thus, GP-GPUs are widely used in CNN training and CNN deployment (STRIGL; KOFLER; PODLIPNIG, 2010). GP-GPU had a high power consumption until last year. As such, it was an inappropriate approach to embedded system applications. Fortunately, in 2016, Nvidia releases the Drive PX 2, an embedded GPU that has a power consumption ranging from 10W to 250W (HUANG, 2016) (NVIDIA, 2016). The Power consumption depends on the operational mode where different chips from the board can be disabled. In addition to the GPU, it has 12 Central Processing Unit (CPU) cores and was manufactured in the 16nm (Fin-Field Effect Transistor) FinFET technology, as can be seen in Figure 2.15.

#### 2.2.2 ASIC SoC and APSoC

When the Very-Large-Scale Integration (VLSI) design arises, the use of dedicated silicon wafers for a design (full-custom) was required, so this design is only economic viable for large quantity productions. One alternative to this style is the semi-custom design that comprises wafers with prefabricated logic gates distributed in array way (gate-array). The connections between the source and the sink of these gates are made by one metallization stage which is defined by the designer and made in a foundry, aiming to develop an Application Specific Integrated Circuit (ASIC) (SEDRA; SMITH, 1998).

Later, a new style of design emerged, the Field Programmable Gate Array (FPGA). This style enables the user to design VLSI systems without worrying about the high initial (non-recurrent) costs and the high design time. However, in general, it presents lower performance outcomes and higher power and area costs than an ASIC (SEDRA; SMITH, 1998). FPGAs use high density circuits in modern processes to design ICs that, as the name suggests, are completely programmable even after the product is sent, or programmable "in the field". There are two types of FPGA, the first is the one-time-configurable FPGA that uses a special process, such as fuse and anti-fuse to permanently program its interconnections and custom the circuit logic. The second type is the reconfigurable FPGA that uses Static Read-Only Memories (SRAMs) or Flash memories to configure the routing and the logic functions, when SRAMs are used the configuration is volatile whereas when Flash memories are used the configuration is non-volatile (WESTE; HARRIS; BANERJEE, 2005).

To deal with the trade-off between performance and power consumption, a figure of merit was created to evaluate implementations in hardware and select the best alternatives. This is the Power efficiency, as defined in Equation 2.8.

$$Power\_efficiency = \frac{GOPS}{Power\_consumption}$$

(2.8)

Where GOPS are Giga (Billions) Operations Per Second and Power Consumption is calculated in watts.

Lee (2017) implemented an ADAS ASIC System-on-Chip (SoC) that, as expected for an ASIC implementation, achieved state-of-the-art results of 560 GOPS with 30 FPS throughput under 720p stereo inputs and low power consumption (0.984 mW). Figure 2.16 illustrates the ADAS SoC micrograph whereby it is possible to see the area utilization of each block of the design.

DRMP Rol Gen. Intention Prediction Engine (IPE)

Object Detection Processor (ODP)

Semi-Global Matching Processor (SGMP)

Figure 2.16: ADAS SoC micrograph

Source: (LEE et al., 2017)

According to (DETTMERS, 2015)(GYSEL; MOTAMEDI; GHIASI, 2016), it is possible to convert the 32-bit floating point outputs of the accumulators of a deep learning algorithm into a 8-bit fixed point representation in order to reduce the area, power consumption but losing an insignificant average accuracy compared to the area and power saving. As can be seen in Table 2.1.

Table 2.1: CNN Models with Fixed-Point Precision. The numbers in brackets indicate accuracy without fine-tuning

|                       | L. Outputs | CONV params | FC params | 32-Bit FLP | FP Accuracy   |

|-----------------------|------------|-------------|-----------|------------|---------------|

| LeNet (Exp1)          | 4-bit      | 4-bit       | 4-bit     | 99.1%      | 99.0% (98.7%) |

| LeNet (Exp2)          | 4-bit      | 2-bit       | 2-bit     | 99.1%      | 98.8% (98.0%) |

| Full CIFAR-10         | 8-bit      | 8-bit       | 8-bit     | 81.7%      | 81.1% (80.6%) |

| SqueezeNet top-1      | 8-bit      | 8-bit       | 8-bit     | 57.7%      | 57.1% (55.2%) |

| CaffeNet top-1        | 8-bit      | 8-bit       | 8-bit     | 56.9%      | 56.0% (55.8%) |

| GoogLeNet top-1 top-1 | 8-bit      | 8-bit       | 8-bit     | 68.9%      | 66.6% (66.1%) |

Source: (GYSEL; MOTAMEDI; GHIASI, 2016)

Where "L. Outputs" are the Layer outputs, "CONV params" are the Convolutional parameters (convolutional weights), "FC params" are the Full-connected neuron parameters (FC weights), "32-bit FL" is the 32-bit Floating-point baseline, and lastly "FP Accuracy" is the Fixed-point average accuracy. For instance, in the first line of Table 2.1 the average accuracy of the LeNet (Exp1) using 32-bit floating-point representation was 99.1%, after the layer outputs, convolutional parameters and full-connected parameters are reduced to 4-bit, the average accuracy slightly decreases to 98.7% without fine-tuning (fine-tuning is the process of retraining the weights of a neural network to obtain a better

Figure 2.17: INT8 Deep Learning Power Efficiency Comparison: Xilinx vs. Intel

Source: (FU et al., 2017)

accuracy result). If fine-tuning is used, this value increases to 99.0% (GYSEL; MOTAMEDI; GHIASI, 2016).

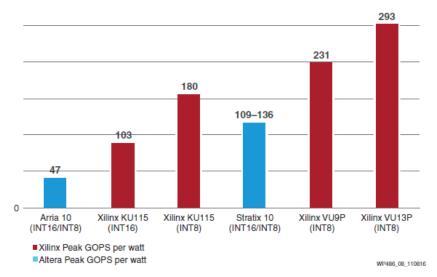

When using this approach, it is possible to use 8-bit integer (INT8) optimization for deep learning implementations in either APSoC or FPGA (FU et al., 2017). Figure 2.17 shows excellent power efficiency results, in terms of GOPS / W, of deep learning architectures implemented on Ultra-scale Xilinx devices.

Han (2014) implemented both APSoC and FPGA trafic-sign recognition systems carrying out both the detection and the classification phases. The performances results of each implementation were compared where the Zynq-7000 APSoC implementation achieves a lower total execution time (96.5 ms) than the Virtex-5 FPGA one (777 ms), whereby 40x40 traffic-sign images were processed.

## **3 RADIATION EFFECTS IN INTEGRATED CIRCUITS**

The development of high-density, functionality, and low-power circuits to meet the increasing consumer's demand for more powerful and capacity circuits, led a to dramatic increase in the radiation effects sensitivity of integrated circuits. Radiation effects in integrated circuits can occur in different ways, such as destructive effects, parametric shifts, data disruptions, and etc. Hard effects cause a damage in an integrated circuit while soft effects may cause an error or a failure in the device, but they do not cause a permanent change in the integrated circuit. Example of hard effect is the Total Ionizing Dose (TID) (OLDHAM; MCLEAN, 2003) which is predominant in space and military environments and it can be seen as a degradation of the component, like aging. Single Event Effects (SEEs), as the name suggests, are radiation effects induced by a single radiation event and are a major concern in space and in some commercial terrestrial applications. SEE can have hard and soft effects. SEE with soft effects, also known as Soft-errors, receives this name because the circuit is not permanently damaged by the radiation. Soft SEEs can be classified into Single Event Upset (SEU), Single Event Transient (SET) (BAUMANN, 2005) and Single Event Functional Interrupt (SEFI) (KOGA et al., 1997). SEE with hard effects are Single Event Burnout (SEB) (HOHL; GALLOWAY, 1987) and Single Event Latch-up (SEL) (STEPHEN et al., 1983), which are a major problem in space applications and must be tolerated by processor or hardening by design techniques.

SEUs occur when a radiation event changes the data state in a memory cell, latch or flip-flop. However, when a single radiation event has a very high energy, the deposited charge can be shared between adjacent bits or memory cells, consequently a Multi-bit Upset (MBU) can occur (MUSSEAU et al., 1996). SET is when a single radiation event occurs in the combinational logic of a circuit. The SET can propagate through the circuit and be latched in the sequential element (BAUMANN, 2005). However, SETs can be logically or electrically masked or even latch window masked, and in this way, they are not observed as errors in the sequential elements. SEFI is a single functional interrupt that occurs in the component, many time related to power issues, clock or configuration of the component (KOGA et al., 1997).

Regarding the physical circumstances, the magnitude of disturbance an ion crossing the semiconductor can cause depends on the Linear Energy Transfer (LET) which in turn depends on the particle energy, type of semiconductor and material mass. The collected charge  $Q_{coll}$  deposited by the ion depends on its type, trajectory and its energy over

a path within or near the junction. The most charge-sensitivity parts of the circuit are the reverse-biased junctions. The amount of collected charge able to change a data state is the critical charge  $Q_{crit}$ . The critical charge is proportional to the node capacitance, operating voltage and strength of feed-back, and depends on the magnitude and temporal characteristics of the pulse generated by the collected charge. In DRAM memories the data value is changed when the collected charge exceeds the critical charge  $(Q_{coll} > Q_{crit})$ , whereas in SRAM memories beyond the collected charge condition  $(Q_{coll} > Q_{crit})$  there is a factor that depends on the reaction speed of the circuit to the fault, i.e. slower reactions lead to an effective  $Q_{crit}$  increasing (BAUMANN, 2005).

There are three significant sources of ionizing particles in electronic devices in the terrestrial environment. The first source of soft-errors are the alpha particles which are emitted by the packaging materials. The Soft Error Rate (SER) from alpha particles can be reduced by purifying the packaging materials (BAUMANN, 2005).

The second source of ionizing particles in electronic devices is related to high-energy cosmic rays. Cosmic rays, collide on the atmosphere, producing secondary particles, such as protons, neutrons, muons and pions. However, less than 1% of the primary flux reaches the sea level and this flux is isotropic. At ground level, high-energy cosmic ray neutrons are one of the highest components of the particle flux and they are the most likely particle that can cause a device failure at ground level. Therefore, high-energy cosmic ray neutrons do not provoke directly the soft errors, they collide with the semiconductor material nucleus that in turn generates lighter particles which transfer energy to the circuit substrate. The high-energy cosmic ray neutrons are more likely to produce MBUs than alpha particles and low-energy cosmic ray neutrons. The device sensitivity to the effects of high-energy neutron collisions can be reduced by design or process modifications (BAUMANN, 2005).

The third source of ionizing particles in electronic devices is related to the low energy cosmic ray and thermal neutrons. Indeed, the third source is the secondary radiation induced from the interaction of low-energy cosmic ray and thermal neutrons, and boron atom. The source of neutrons from cosmic rays was explained previously. As boron is extensively used as a p-type dopant, low-energy cosmic ray neutrons has a significant effect in the boron-doped phosphosilicate glass (BPSG) dielectric layers. Advanced technologies that operate at low voltages are also susceptible to the effects of high energy cosmic ray neutrons interactions. The effects in BPSG dielectric layers can be reduced by changing the dielectric material or enriching the BPSG process without changing their

User's design

Upset type 1

Upset type 2

Upset type 2

Upset type 4

BlockRAM

M Configuration Memory Cell

Bit flip

Figure 3.1: The comparison of the effects of a SEU in ASIC and FPGA architecture

Source: (KASTENSMIDT; CARRO; REIS, 2006)

desirable properties (BAUMANN et al., 1995).

### 3.1 Radiation effects in SRAM-based FPGAs

There are peculiar radiation effects in SRAM-based FPGAs that do not occur in ASICs. In an ASIC, the effect of an energetic particle collision on the combinational circuit results in a transient fault. This transient fault is characterized as a transient logic pulse that may or not be latched in a storage cell, depending on the circuit delay and the topology. However, when a fault occurs in the sequential logic, the bit stored in this cell is inverted. An inversion in a logic state is called "bit flip" (KASTENSMIDT; CARRO; REIS, 2006).

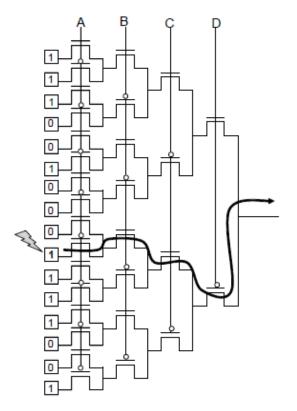

In a SRAM-based FPGA, both the combinational and sequential logic are implemented by the user using SRAM configuration cells (volatile), as illustrated in Figure 3.1. Therefore, one fault in an ASIC combinational logic is equivalent to a bit flip in a FPGA Look Up Table (LUT) that performs the logic (Upset type 1) or in the cells that control internal routing by the multiplexers.

As the LUT performs the combinational logic (See Figure 3.2), one fault in a SRAM configuration cell will modify the implemented logic. Therefore, it will have a permanent effect unless a new configuration bitstream (File that contains the configurations bits to customize the logic) is loaded. Thus, an erroneous value of the combinational

Figure 3.2: Upset in the LUT (logic change)

Source: (KASTENSMIDT; CARRO; REIS, 2006)

logic will be latched in the stored cell unless some fault detection technique is applied. However, faults that occur in the FPGA sequential logic (Figure 3.1 Upset type 2) will have a transient effect if the CLB flip-flop value is overridden by a new flip-flop load.

Other transient fault (SET) can occur in the multiplexer's inputs and outputs that control the CLB internal routing. SEU in the external routing (See 3.3) creates either "short" or "open" in the wires and has a permanent effect (Figure 3.1 Upset type 3) unless a new configuration bitstream is loaded. The Embedded memories (Block Random Access Memory - BRAM) are also susceptible to SEU and also have a permanent effect (Figure 3.1 Upset type 4). As the BRAM cannot be corrected by the bitstream without interrupting the normal operation of the application, it must be corrected by using fault tolerant techniques applied in the architectural or high-level description (KASTENSMIDT; CARRO; REIS, 2006).

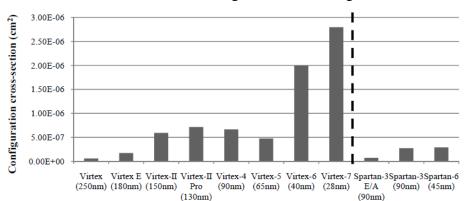

Accordingly to (OHLSSON et al., 1998), as the transistor technology is shrinking, and consequently the logic density is increasing, the SRAM-based FPGA susceptibility to neutron induced soft-errors is also increasing. In a more recent work (NAZAR, 2013), this trend was confirmed in recent SRAM-based FPGA technologies. Tests were carried out by reading back the configuration bits of the FPGAs and verifying how many bit-

CLB CLB

CLB

CLB

Figure 3.3: Upset in the routing (undesirable connection)

Source: (KASTENSMIDT; CARRO; REIS, 2006)

flips occur for a given fluence, i.e. static cross-section. It can be seen in Figure 3.4 that the static cross-section increases as the technology size decreases and the number of configuration bits available increases.

Considering these SRAM-based FPGA peculiar effects, a safety-critical system, as an autonomous car, must be characterized under soft errors in order to evaluate its reliability. Once the system is evaluated as vulnerable, some fault tolerant techniques must be applied.

Figure 3.4: Static cross-section for the configuration of the largest device of each family

Source: (NAZAR, 2013)

#### 4 CONVOLUTIONAL NEURAL NETWORK TRAINING

#### 4.1 Dataset

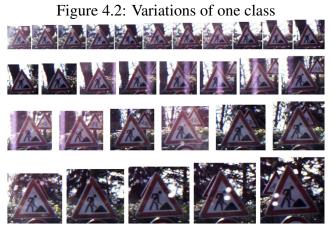

The German Traffic-Sign Recognition Benchmark was used as a training and test dataset. This is a multi-class, single-image classification challenge held at the International Joint Conference on Neural Networks (IJCNN) in 2011 (STALLKAMP et al., 2012). The goal of this dataset is to evaluate the performance of machine learning algorithms for German traffic-sign classification. This dataset contains 43 classes and more than 50,000 images in total, featuring an extensive and realistic dataset. In Figure 4.1 one sample of each class is shown. The dataset has many samples for each class, varying this position with respect to the observer, luminosity, background occlusion, and other types of variation in images. Figure 4.2 shows some variations on an image of one class.

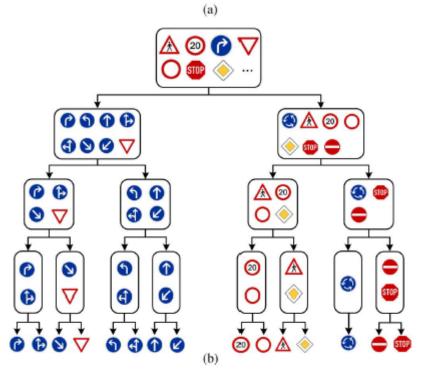

Aiming real-time applications, (YANG et al., 2016) concluded that it is more effective to develop one simple topology CNN for classifying the sub-classes within the super-classes, instead of developing one complex CNN to classify all the 43 classes. Thus, the 43 classes were divided into 4 super classes. Figure 4.3 show the (a) Prohibitory, (b) Danger and (c) Mandatory super classes.

The 8 remaining sub-classes belong to a super class referred to as "Others" that is separated from the other super classes, because they do not have common features. For instance, the super classes in Figure 4.3 have either circular or triangular shapes. The circular ones are either red or blue, and the triangular ones are only red. These super classes are easy of being separated by their color or shape features. Alternatively, the sub-classes within the super class "Others" have no common features, they have octagonal, triangular, diamond or circular shapes. Additionally, they are filled with red or yellow

Source: (STALLKAMP et al., 2012)

Source: (STALLKAMP et al., 2012)

Figure 4.3: Sub-classes of each super class

Source: (YANG et al., 2016)

Figure 4.4: One sample of each sub-class of the super class "Others"

Source: (STALLKAMP et al., 2012)

Figure 4.5: 6 classes of the Prohibitory subclass

Source: The Author

colors or have a stripe or there is no sign in their center. Due to the fact that these classes do not have common features and cannot be clustered in super classes, they were grouped into a super class which is the result of an unexpected classification. For example, if one sub-image is not recognized as a "Prohibitory", "Danger" or "Mandatory" super class, it is recognized as an "Others" super class. Some "Others" super class samples are shown in Figure 4.4.

Due to resource limitations of our available SoC device, the CNN implementation was limited to a 6-class classifier, as such 6 sub-classes of the prohibitory super class were used. Thus, the dataset was reduced to 6 sub-classes, which comprises 9,930 images for training and 3,273 for testing. The 6 prohibitory sub-classes are shown in Figure 4.5.

As shown in Figure 4.2, the images were captured in different lighting and weather conditions, as such, images from the same sub-class present large differences and can be classified into different sub-classes. To deal with this kind of influence some pre-processing must be performed before the images are presented to the CNN classifier. The method used was the same of the work of (YANG et al., 2016) that employed a Contrast Limited Adaptive Histogram Equalization (CLAHE) (ZUIDERVELD, 1994) to adjust the contrast of the images. To apply the CLAHE to the images, the method CLAHE of the OpenCV library was used (BRADSKI; KAEHLER, 2008). As reported by (SERMANET; LECUN, 2011) the color plays little role in the classification, thus, following the work of (YANG et al., 2016), the original images were converted into grayscale to speed up the

CLAHE

Resize

32X32

Figure 4.6: Pre-processing steps

CNN classifier. The same were converted into grayscale by using the OpenCV library (BRADSKI; KAEHLER, 2008). The images in the GTSRB dataset have different dimensions. Since the CNN input image dimensions are fixed, the images were resized. This pre-processing was performed using the Caffe framework, which will be described in the next section. All the steps that the pre-processing encompasses are illustrated in Figure 4.6. This pre-processing was performed during the design time, with an aim of improving the training accuracy. The real-time implementation of this algorithms is outside the scope of this work.

## 4.2 Framework for training

The model definition and training were performed with the Convolutional Architecture for Fast Feature Embedding (Caffe) framework. Caffe is a deep learning framework made with expression, speed, and modularity in mind. It is developed by Berkeley AI Research (BAIR) and by community contributors (JIA et al., 2014). Yangqing Jia created the project during his PhD at University of California (UC), Berkeley. Caffe is released under the BSD 2-Clause license.

Some reasons for Caffe utilization are as follows:

- Expressive architecture Models and optimization are defined by configuration without hard-coding. Switch between CPU and GPU by setting a single flag to train on a GPU machine then deploy to commodity clusters or mobile devices.

- Modularity It has a catalogue within several state-of-the-art layers that can be

combined to develop your own model.

• **Speed** - Caffe can process over 60M images per day with a single Nvidia K40 GPU with the ILSVRC2012-winning SuperVision model and prefetching IO.

A Caffe model anatomy is composed of three components: layers, nets and blobs. Models are defined layer-by-layer where each layer performs a specific computation such as convolutional layer, max pooling layer, softmax layer and etc. The "blobs" are the memories of the layers where the framework stores, manipulates and communicates information such as forward signals and backward signals (derivatives). Lastly, the "net" is a collection of connected layers that characterize a specific model such as LeNet, Yolo, Faster R-CNN and so on. The "net" is defined from input data to "loss". Where "loss" is the error of the classification given an input data and its correspondent label. The layer inputs are defined as "bottom", whereas the layer outputs are defined as "top".

A Caffe model is trained using solvers which are parameterizable learning algorithms. The solvers optimize the model in two computational phases. The "forward pass" whereby the network outputs are computed and the backward pass where the gradients, which are used to optimize the network, are computed. (JAIN; MAO; MOHIUDDIN, 1996) (HAYKIN, 1994). The way by which the blobs are stored is managed by the Caffe framework. Therefore, the user will only need to define the model and solver parameters, the dataset, and the platform (CPU/GPU) to be used in training or deployment phase. The model and solver parameters are defined by a protocol buffer (.prototxt) and the learned parameters (weights) are serialized as binary protocol buffer (binaryproto) .caffemodel files using Google Protocol Buffer language. Protocol buffers enable efficient serialization, minimum-size binary strings (when serialized), interface implementation in multiples languages (manly C++ and Python) and other benefits. The implementation, communication and other issues are performed automatically by the framework.

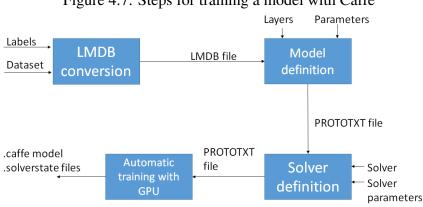

### 4.2.1 Training process using Caffe

Before someone starts the training process with Caffe, the dataset must be prepared in order to be suitable for the framework. There are several ways of reading the dataset with Caffe, it can be read from the memory, operational system directory, data-base and so on. The Lightning Memory-mapped Database (LMDB) and batch processing improve the training performance being an excellent choice for big datasets. Caffe has an embedded

Figure 4.7: Steps for training a model with Caffe

Source: The Author

code that converts an image directory and a .txt file (describing the image paths and labels) into a LMDB file. The GTSRB dataset contains a file describing the image directories and their labels but it is defined by a .csv file and contains other information. Thus, a Python script was created to adjust the .csv file to a .txt file suitable for the Caffe conversion code. Once the dataset is prepared for the framework, the model and solver parameters have to be defined in .prototxt files using the Google Protocol Buffer language. During the CNN training phase, the weights and the solver state are periodically saved into binary protocol buffer .caffemodel and .solverstate files, respectively, every 5000 iterations. These are the snapshots of the training and can be used to go back to a specific state of the training and use these snapshot trained weights for deploying and debugging. The use of the GPU is simply set by a flag in the Python code. The training steps with Caffe are summarized in Figure 4.7.

There is no specific method to determine which is the best Neural Network model for a given task. There is only heuristics to improve the success probability, so it must be discovered by the trial-and-error method (HAYKIN, 1994). However, well-known models in the literature can be used to accelerate the training process. Thus, the LeNetbased CNN model proposed by (YANG et al., 2016) was chosen due to its competitive accuracy and good performance results. However, as explained in section 4.1, this model is not suitable for the available APSoC platform, and then the CNN model had to be reduced to the model illustrated in Figure 4.8.

The reduced model parameters are shown in Table 4.1. Where the layers are shown line by line in a forward way and "in place" means the Full-connected neuron outputs are re-used by the ReLU activation function when the value is greater than 0 enabling memory saving. Data layers specifies how the images are read (back-end), some preprocessing operations, such as cropping, re-sizing, scaling and others, and how many

C1:maps C3:maps F5:layer P2:maps 6@28x28 12@10x10 P4:maps F6:layer 6@14x14 50 input 12@5x5 Output layer 20 32x32 subsampling convolutions subsampling convolutions reshape full-connected MLP

Figure 4.8: Reduced LeNet-based CNN model

Source: The Author

images are processed at time (batch size). Softmax with Loss layer is only used in the training phase while Accuracy layer is only used in the testing phase, both of them do not have parameters. Different batch sizes in the Data layer are used in the training and test phase. These model parameters were written in a prototxt file by using the Python interface with Caffe, simplifying the coding process.

Table 4.1: Parameters used in the model Layers **Parameters** Data batch size: 64 back-end: LMBD kernel size: 5 - feature maps: 6 Convolution 1 Pooling MAX 1 kernel size: 2 - stride: 2 Convolution 2 kernel size: 5 - feature maps: 12 Pooling MAX 2 kernel size: 2 - stride: 2 Fully-connected 1 neurons: 50 ReLU 1 in place: true Fully-connected 2 neurons: 20 ReLU 1 in place: true Fully-connected 3 neurons: 6 Softmax with Loss Accuracy

Source: The author

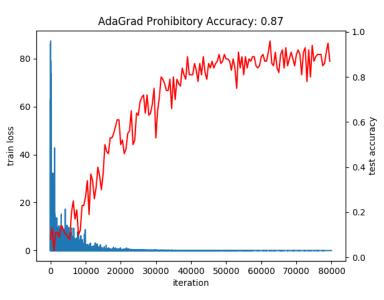

Once the model is defined, the solver type and solver parameters must be defined. Like the model definition, there is no specific method to define which are the solver type and solver parameters to a specific application, requiring the trial-and-error method (HAYKIN; NETWORK, 2004). Since the defined CNN model is based on the LeNET model (LECUN; BENGIO et al., 1995), the solver parameters used in a LeNET Caffe example (CAFFE, 2017) were also used. However, the solver type was defined by using the trial-and-error method. As it will be shown in the results to be seen ahead, the Adaptive gradient had the best accuracy result. This methodology reduces the training time because the Caffe framework has six solver types while the solver parameters combinations have

numerous possibilities. The solver parameters are shown in Table 4.2.

Table 4.2: Parameters used in the solvers

| Parameter         | Value             |

|-------------------|-------------------|

| Learning rate     | 0.01              |

| Momentum constant | 0/0.9             |

| Gamma             | 10E-5             |

| Power             | 0.75              |

| Test iterations   | 60                |

| Test interval     | 500               |

| Learning policy   | inverse           |

| Weight decay      | 5E-4              |

| Max iterations 3  | 80000             |

| Туре              | Adaptive Gradient |

Source: The author

Where "Learning rate" is the rate by which the weights are updated, "Momentum constant" is the factor by which the previous weights are multiplied (Some solver types do not use momentum, thus its value is assigned to 0), "Test iterations" is the number of iteration will be done to generate the accuracy (Each one of the test iterations is done in all the images from the batch, whose quantity is defined by the batch size. So, for a 100 batch size, 6000 images are tested), "Test interval" is the number of training iterations until the point of a test execution, "Learning policy" is the way by which the "Learning rate" is decreased along the training time and is described by the equation 4.1, the "Weight decay", as the name suggests, is the factor by which the weights are decayed, "Max iterations" is the maximum number of training iterations, and lastly "Type" is the solver type.

$$learning\_rate = learning\_rate(1 + gamma * iteration)^{(-power)}$$

(4.1)