### A MODIFIED LIGHTLY DOPED DRAIN MOSFET FOR VERY LARGE SCALE INTEGRATION

1640

5

BIBLIOTECA CPD/PGCP

11

a service and the service of a state of the service of the service

A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

By

Sergio Bampi

March 1987

© Copyright 1987 by Sergio Bampi

Hada Barrison

U F R G S C P D - P G C C EIELIOTECA HO CHANNELL (9138-161.4 (043) 100 FE3. BOMM LUIA: (9138-161.4 (043) 2635 DOMM LUIA: 12 187 D 1419 187 C24 500.00 FUNDO: PRIMA: PGCC - PROF-BAMPI

ii

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy,

10-1

(Principal Adviser)

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

I certify that I have read this thesis and that in my opinion it is fully adequate, in scope and quality, as a dissertation for the degree of Doctor of Philosophy.

Approved for the University Committee on Graduate Studies;

Dean of Graduate Studies

### Acknowledgements

I extend my sincere thanks to Professor James D. Plummer for his direction and support throughout my doctoral research at Stanford. His guidance and continuous flow of ideas and critical suggestions made possible this contribution to the technical world. I also thank Professors Richard Swanson and David Bloom for their careful reading of this manuscript. I am grateful to many students in the Integrated Circuits Laboratory for their valuable input and help and to the staff members and research associates for their technical assistance in the processing work. The excellent working environment of the Laboratory is deeply appreciated. My thanks also go to Mrs. Hortense Shirley for editing the manuscript for clarity and style and to Joyce Pelzl for her help in assembling the final document. This work is dedicated to my wife Mery whose love and support has been a continual inspiration and to our daughter Giovana.

I gratefully acknowledge the support and the Scholarship of the Brazilian agency CNPq during my years of study at Stanford. This work was partially sponsored by the Defense Advanced Research Projects Agency under Contract MDA903-84-K-0062.

#### ABSTRACT

Reducing MOSFET dimensions while maintaining a constant supply voltage leads to higher electric fields inside the active regions of VLSI transistors. Operation of micron and submicron MOSFETs in the presence of high-field effects has required design innovations so that a constant supply voltage, acceptable punchthrough voltage, and long-term reliability are possible as device scaling continues.

Drain engineering is necessary to cope with the susceptibility of MOSFETs to hot-carrier-related degradation. Reducing the electric fields at the drain end of the channel is critical to device reliability because degradation is related to carrier *heating* as they traverse regions with field strength in excess of 100 kV/cm. Optimized lightly doped drain (LDD) structures that spread the high electric field at the drain ensure the reliable 5 V operation of micron-sized n-channel MOSFETs. Recent experimental evidence revealed that LDDFETs are less reliable than conventional transistors if the  $n^-$  region is too lightly doped.

The JMOS transistor, a new n-MOS structure, is introduced to resolve the reliability problems in LDD devices with peak doping densities below  $1 \times 10^{18}$  cm<sup>-3</sup>. A JFET is merged into the n-MOS structure to reduce the high fields under the gate. Two-dimensional simulations and experimental results demonstrate for the first time the operation of this device and its potential for VLSI applications requiring maximum supply voltage. A major experimental finding is that the JMOS can sustain 5 V operation even for submicron effective channel lengths because of the designer-controlled reduction of the maximum electrical field in the region under the gate traversed by carriers. The modification introduced in the LDD design is advantageous in terms of lower gate and substrate currents. Reliability can potentially be improved but at the expense of performance; however, the advantages of 5 V operation in micron-sized devices can outweigh this performance loss.

## Contents

| 1.  | Intr  | oduction                                                     | 1     |

|-----|-------|--------------------------------------------------------------|-------|

|     | 1.1   | MOSFET Scaling                                               | 1     |

|     | 1.2   | Alternative Structures for VLSI                              | 4     |

|     | 1.3   | Scope and Objectives                                         | 6     |

| 2.  | Ligl  | ntly Doped Drain Structures for VLSI MOSFETs                 | 9     |

|     | 2.1   | Overview                                                     | 9     |

|     | 2.2   | High Field Effects in Conventional MOSFETs                   | 16    |

| 23  | 11    | 2.2.1 Hot-Carrier-Related Phenomena                          | 17    |

| -81 |       | 2.2.2 Velocity Saturation                                    | 31    |

| éc: | 2.3   | LDDFETs Engineered for Reliability                           | 32    |

|     |       | 2.3.1 Graded Source/Drain MOSFET                             | 33    |

|     |       | 2.3.2 LDD MOSFET                                             | 37    |

|     | 1.0   | 2.3.3 Other Nonconventional MOSFETs with Lightly Doped Drain | 42    |

|     | 2.4   | Summary                                                      |       |

| •   | 73.60 | 5.5.2 Linear Region ON-Residence Considerations              | 45    |

|     |       | OSFET: An Alternative VLSI Structure                         | 1.000 |

|     | 3.1   | Overview                                                     | 45    |

|     | 3.2   | JMOSFET and Alternative LDD Designs                          | 46    |

|     | 3.3   | JMOS Device Simulation                                       | 53    |

|     |       | 3.3.1 Circuit Simulation                                     | 53    |

|     |       | 3.3.2 Two-Dimensional Device Simulation                      | 59    |

|     |       |                                                              |       |

Experimental Results and

|    | 3.4 | Summary                                          |

|----|-----|--------------------------------------------------|

| 4. | Exp | erimental Results 77                             |

|    | 4.1 | Overview                                         |

|    | 4.2 | Device Fabrication                               |

|    | 4.3 | Experimental Results and Comparisons             |

|    |     | 4.3.1 Device Characteristics                     |

|    |     | 4.3.2 Substrate Current                          |

|    |     | 4.3.3 Gate Current                               |

|    |     | 4.3.4 Speed Performance                          |

|    | 4.4 | JMOS Structure Evaluation                        |

|    | 4.5 | Summary 120                                      |

|    |     | · · · · · · · · · · · · · · · · · · ·            |

| 5. | JM  | OSFET Optimization 123                           |

|    | 5.1 | Overview                                         |

|    | 5.2 | Optimization Methodology 123                     |

|    | 5.3 | Scaling of MOSFET Parameters                     |

|    | 5.4 | JFET Profile Optimization                        |

|    |     | 5.4.1 One-Dimensional Profile                    |

|    |     | 5.4.2 Two-Dimensional Profile Optimization       |

|    | 5.5 | JMOS Design Optimization                         |

|    |     | 5.5.1 Saturation Current Considerations          |

|    |     | 5.5.2 Linear Region ON-Resistance Considerations |

|    | 5.6 | Summary                                          |

| 6. | Con | clusions and Recommendations 147                 |

|    | 6.1 |                                                  |

|    | 6.2 | Recommendations                                  |

|    |     |                                                  |

| ٨  | MO  | SFET Model-Parameter Measurements 151            |

3

# x

|    | A.1 | Conventional MOSFET Model                                 | 151 |

|----|-----|-----------------------------------------------------------|-----|

|    | A.2 | Mobility-Reduction Model                                  | 152 |

|    | A.3 | Saturation Parameters                                     | 154 |

|    | A.4 | Parameter Measurement and Extraction                      | 155 |

|    | A.5 | Effective Channel Length and Series Resistance Extraction | 156 |

| в. | JF  | ET-MOSFET Fabrication 1                                   | .63 |

,

.

### References

7

.

$\leq |B|$

169

a the state of the second state of the second

### List of Figures

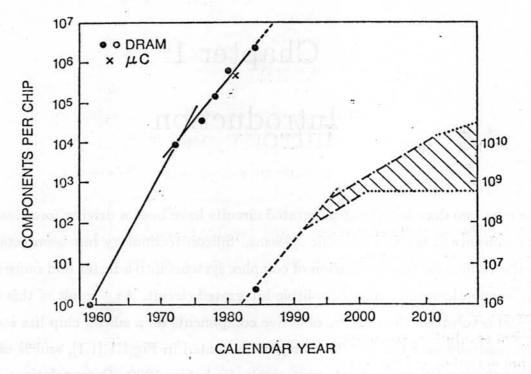

|            | 1.1  | Evolution of the number of active components on a silicon chip  | 2   |

|------------|------|-----------------------------------------------------------------|-----|

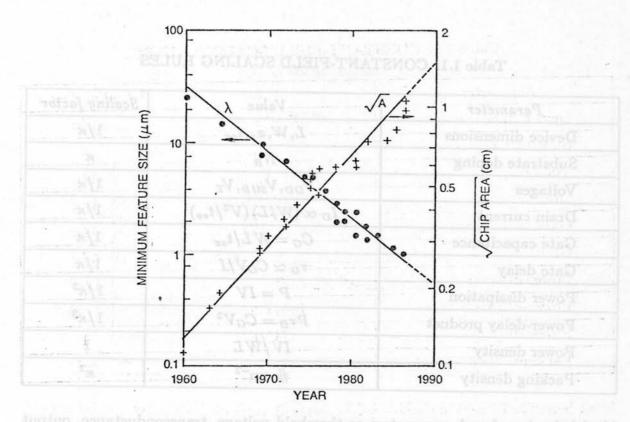

| L.         | 1.2  | Evolution of the minimum feature size and silicon die size      | 3   |

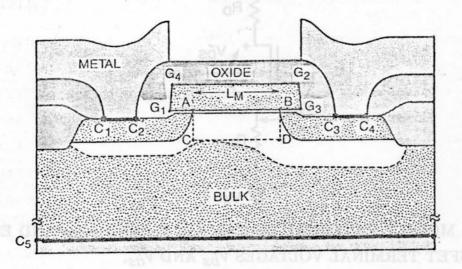

|            | 1.3  | Cross section of a conventional MOSFET                          | 5   |

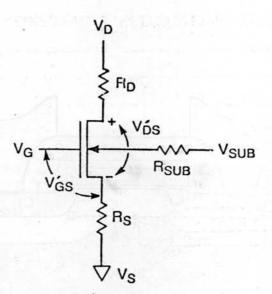

|            | 1.4  | MOSFET external and effective bias                              | 6   |

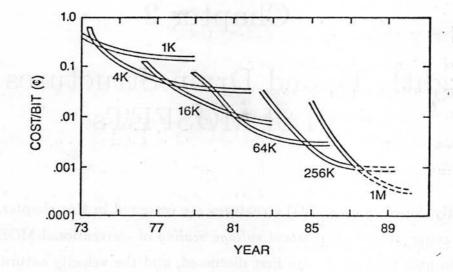

|            | 2.1  | Cost per bit in DRAMSs                                          | 10  |

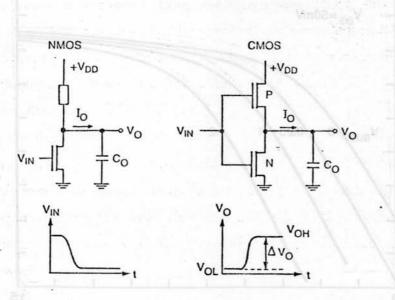

| 74)<br>152 | 2.2  | NMOS and CMOS inverter circuits in a switching transient        | 13  |

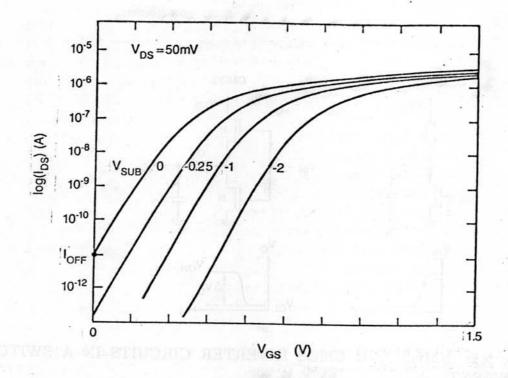

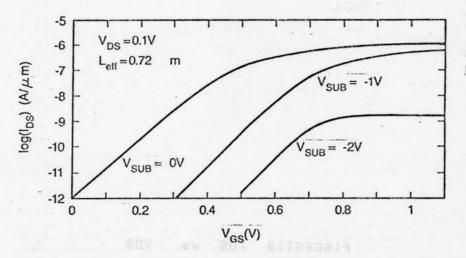

| 22         | 2.3  | Subthreshold I-V characteristics                                | 14  |

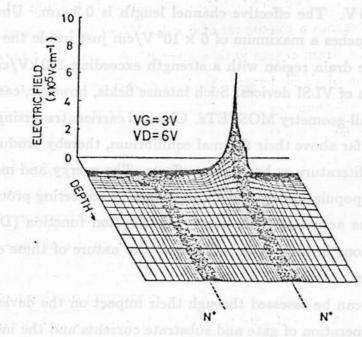

| 90<br>115  | 2.4  | Two dimensional field distribution                              | 17  |

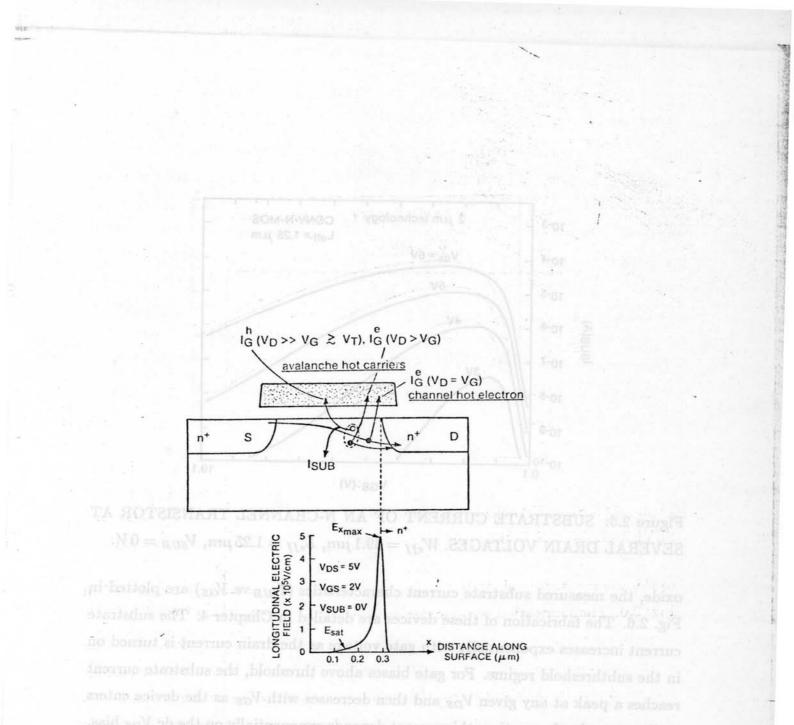

| 1.5        | 2.5  | Hot carrier generation of substrate current                     | 19  |

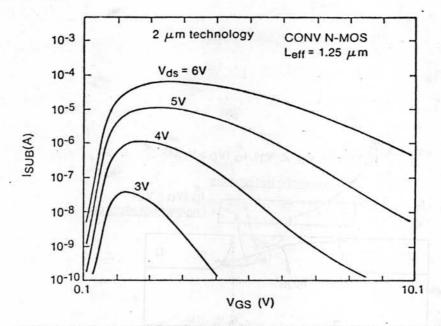

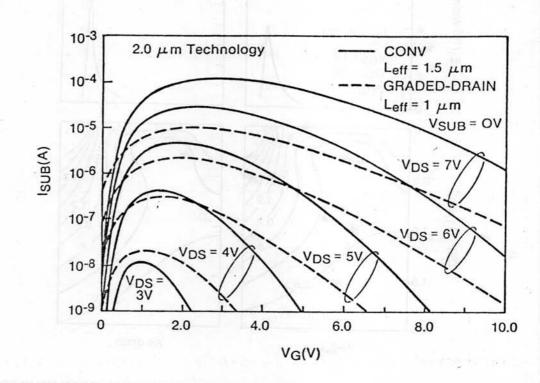

|            | 2.6  | NMOS substrate current characteristics                          | 20  |

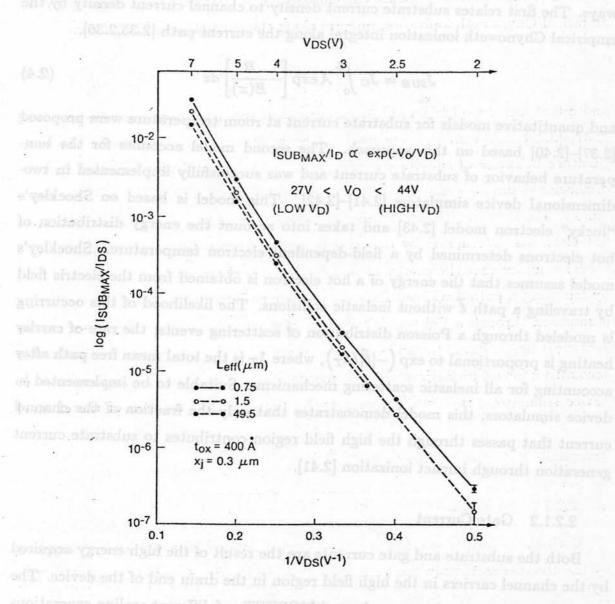

| 20         | 2.7  | Drain dependence of the maximum substrate current               | 21  |

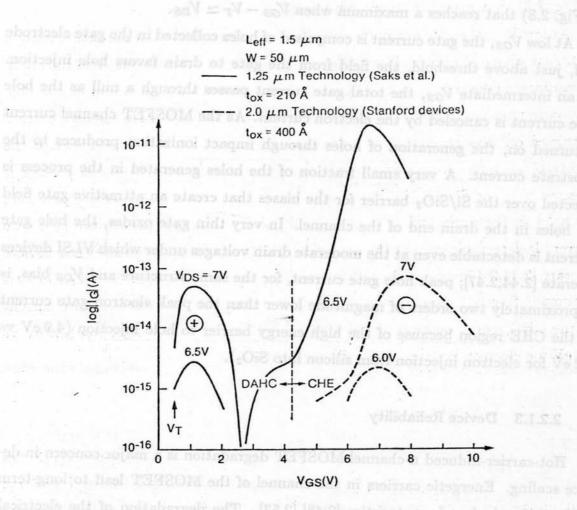

|            | 2.8  | Gate current characteristics                                    | 23  |

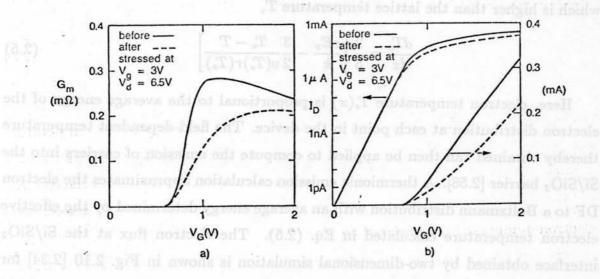

|            | 2.9  | Hot-carrier-induced degradation of MOSFETs.                     | 25  |

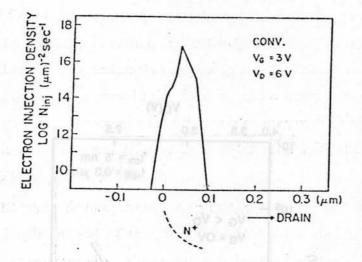

|            | 2.10 | Electron injection density                                      | 27  |

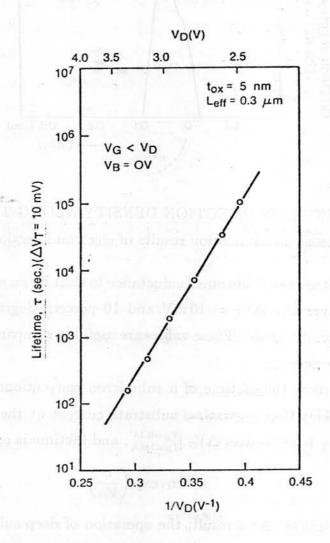

|            | 2.11 | Device lifetime under hot carrier stress vs drain voltage       | 28  |

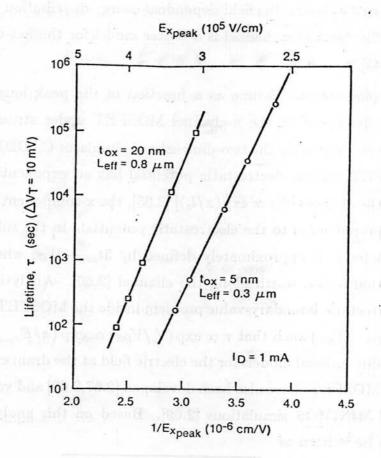

| -          | 2.12 | Device lifetime under hot carrier stress vs peak electric field | 30  |

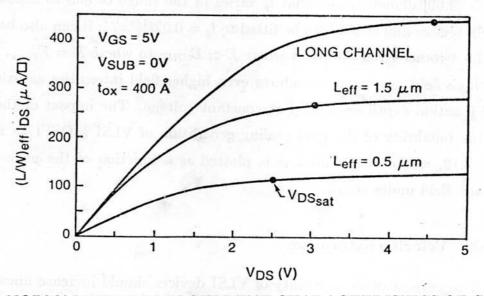

|            |      | Normalized drain current of conventional MOSFETs                | 32  |

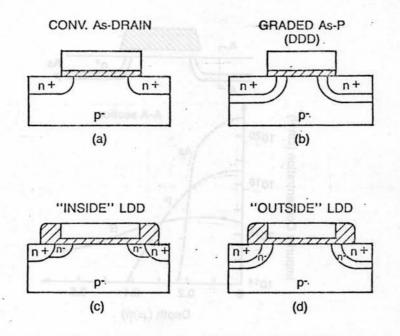

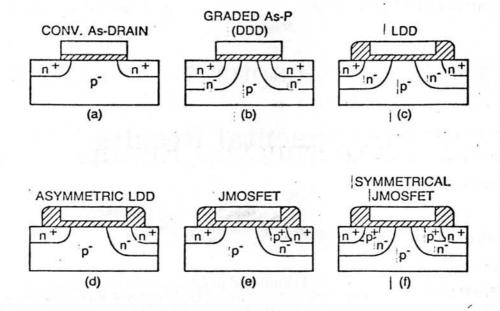

|            |      | Cross sections of LDD transistors                               | 33  |

|            |      | DDD MOSFET cross section                                        | 34  |

|            |      | Equipotential contours in the DDD device                        | 35  |

|            | 2.17 | Substrate current characteristics comparison                    | 36_ |

|            |      | 3.24 GEMINI simulation of an incompletely margod at the         |     |

aniquest GGU tange

200 High voltage PMOS daily

.

| 9 1 9 | Electric field in LDDFETs.                                       | 20 |

|-------|------------------------------------------------------------------|----|

|       |                                                                  | 39 |

|       | LDD trapping-induced series resistance degradation               | 41 |

|       | High voltage PMOS device cross section                           | 42 |

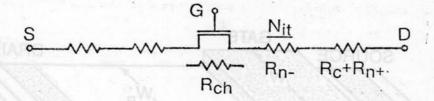

| 2.21  | Equivalent circuit model for LDD PMOS device                     | 43 |

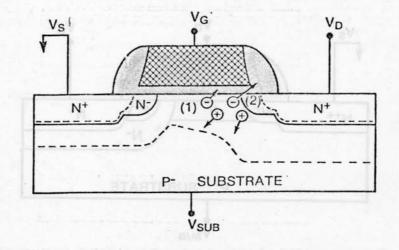

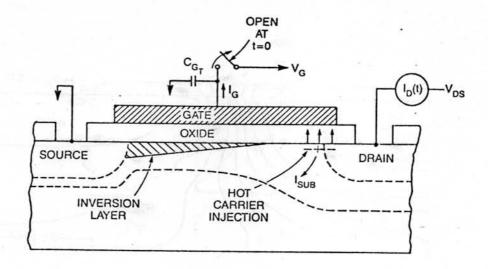

| 3.1   | Schematic hot carrier injection in an LDDFET                     | 47 |

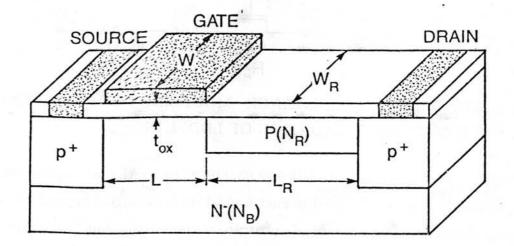

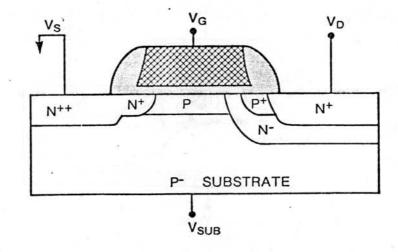

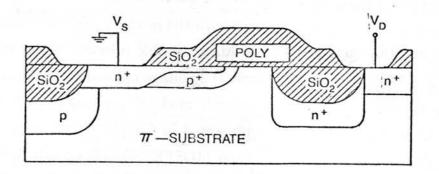

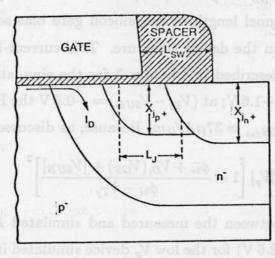

| 3.2   | JMOSFET structure cross section                                  | 48 |

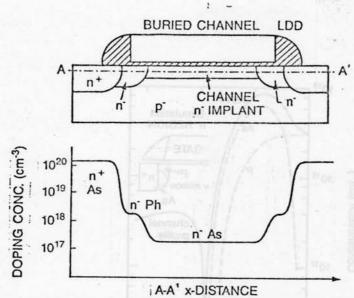

| 3.3   | Buried Channel LDD                                               | 49 |

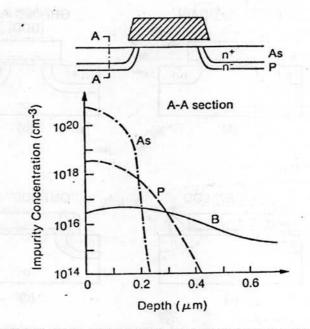

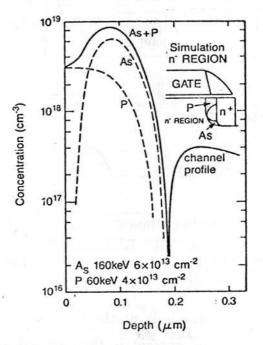

| 3.4   | Buried LDD doping profile                                        | 50 |

| 3.5   | Buried DMOS structure                                            | 50 |

|       |                                                                  |    |

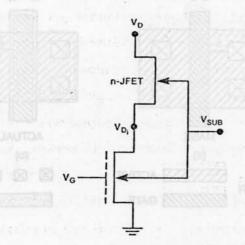

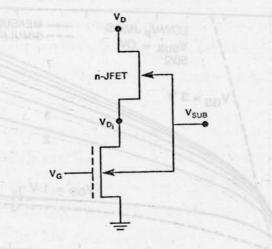

| 3.6   | JMOS equivalent circuit                                          | 51 |

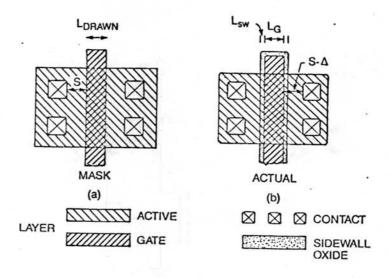

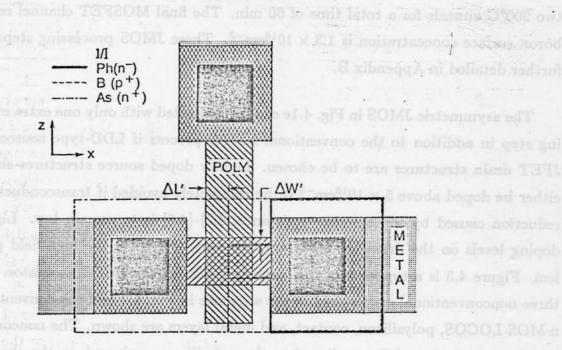

| 3.7   | Layout of the JMOS transistor                                    | 52 |

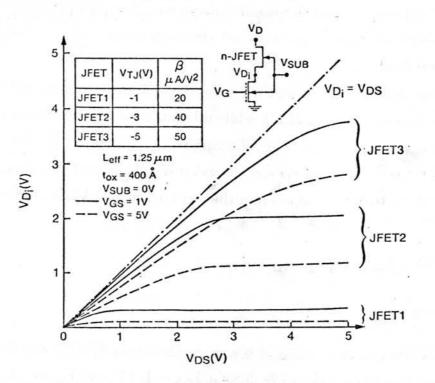

| 3.8   | SPICE Simulation for different JFET designs                      | 54 |

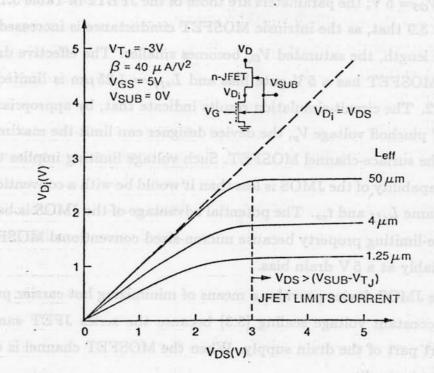

| 3.9   | SPICE Simulation for different MOSFET L                          | 55 |

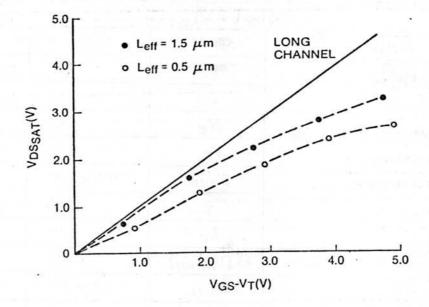

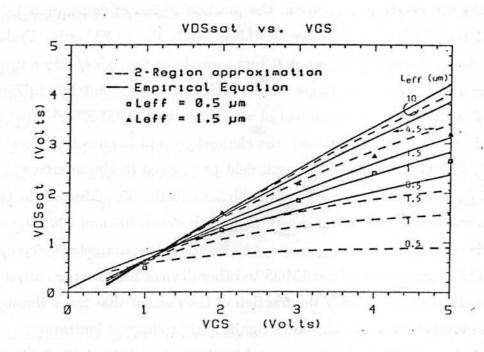

| 3.10  | $V_{DS_{sat}}$ vs $V_{GS}$ depende on channel length             | 58 |

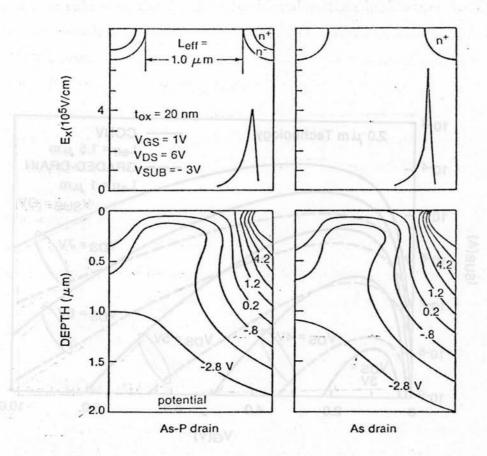

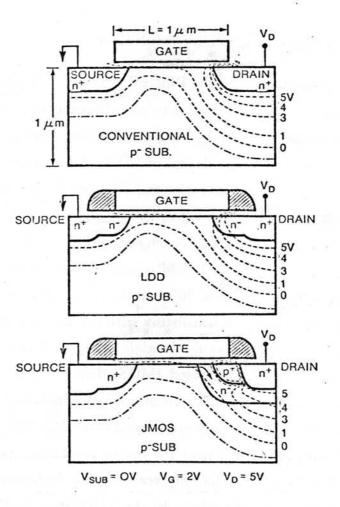

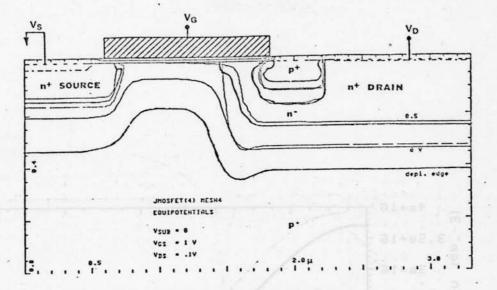

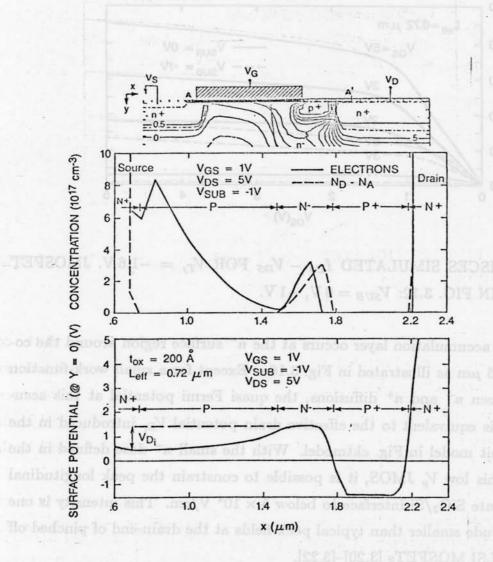

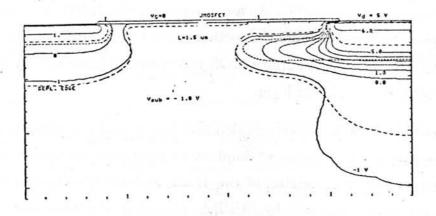

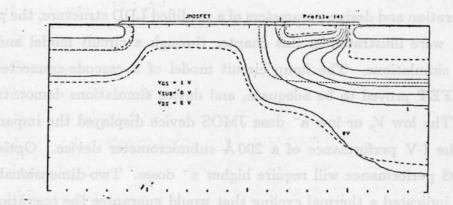

| 3.11  | Equipotential contours for saturated transistors                 | 60 |

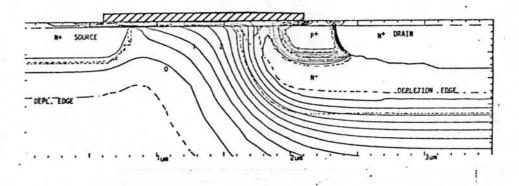

| 3.12  | PISCES equipotential contours for the JMOSFET                    | 61 |

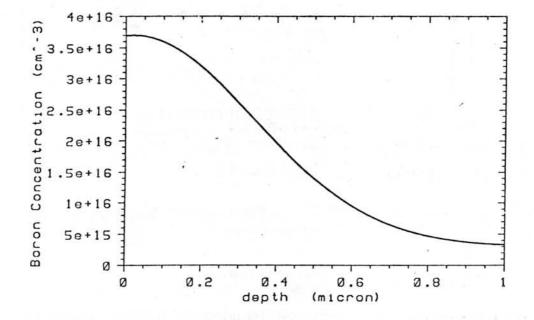

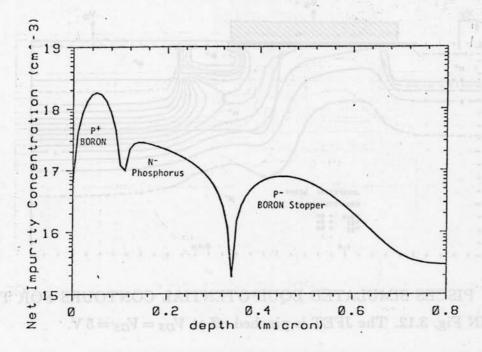

| 3.13  | Channel region profile                                           | 62 |

| 3.14  | JFET channel profile                                             | 63 |

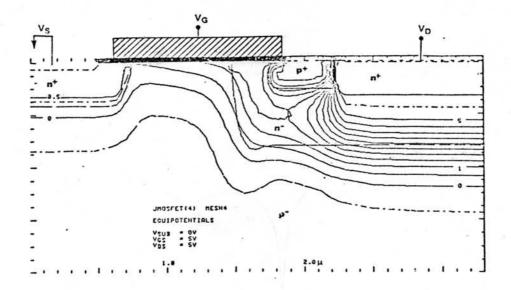

| 3.15  | PISCES equipotential contours for the JMOSFET                    | 64 |

| 3.16  | Simulated potential and electron variation along interface       | 65 |

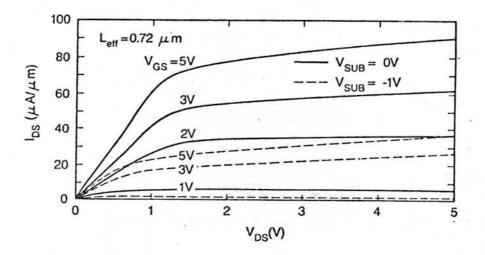

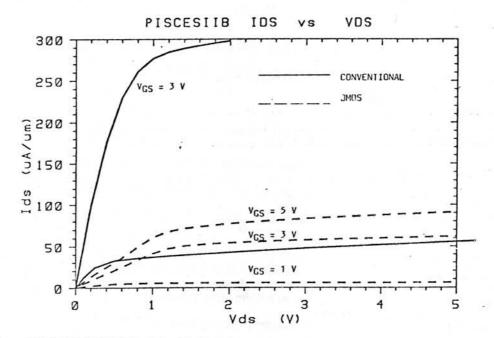

| 3.17  | Simulated $I_{DS} - V_{DS}$ for a low $V_p$ JMOSFET              | 66 |

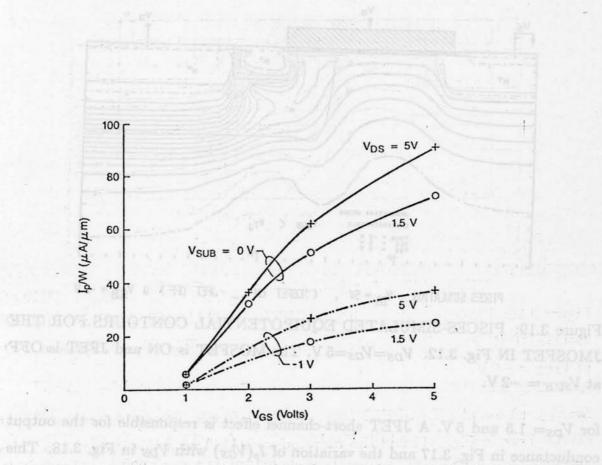

| 3.18  | Plot of JMOS Pinchoff current per unit channel width vs $V_{GS}$ | 67 |

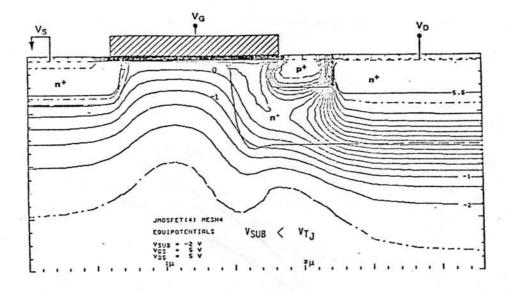

| 3.19  | PISCES equipotential contours for the JMOSFET (JFET OFF)         | 68 |

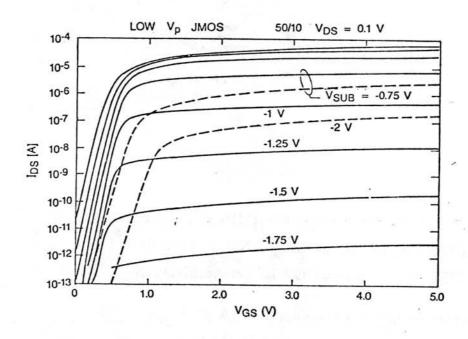

| 3.20  | PISCES simulated subthreshold characteristics                    | 69 |

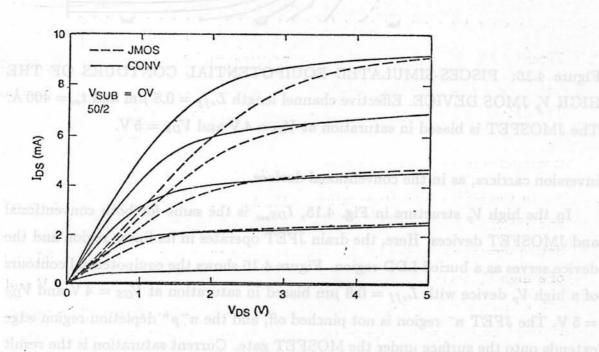

| 3.21  | Simulated $I_{DS} - V_{DS}$ comparison                           | 70 |

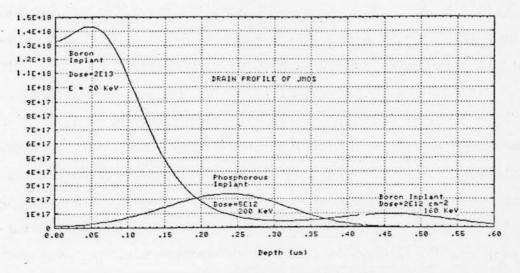

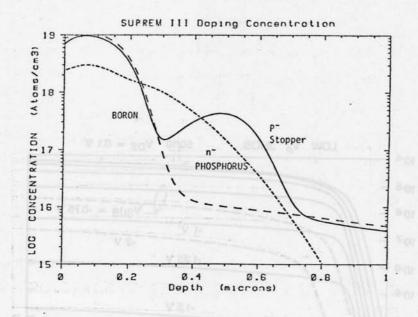

| 3.22  | Supra-simulated JFET profile                                     | 71 |

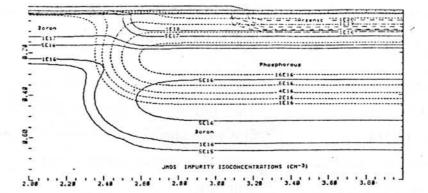

|       | SUPRA-simulated impurity contours                                | 72 |

| 3.24  | GEMINI simulation of an incompletely merged JFET                 | 74 |

-

- 35

ł

.

|   | 3.25 | GEMINI simulation of the low $V_p$ JMOSFET                                     | 75  |

|---|------|--------------------------------------------------------------------------------|-----|

|   | 4.1  | Cross section of source/drain structures fabricated                            | 78  |

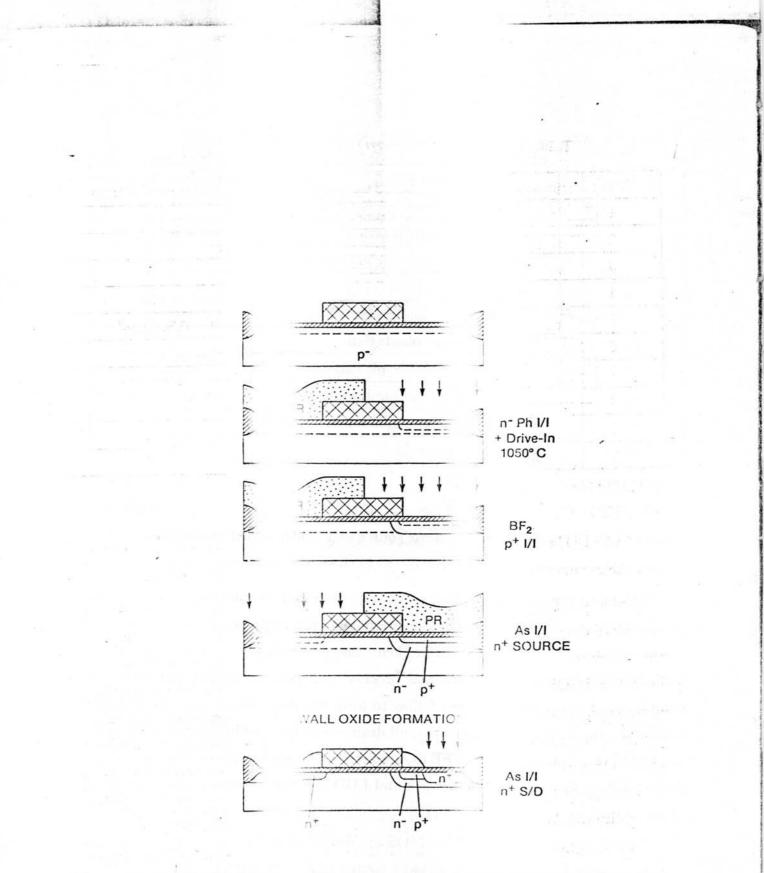

| 1 | 4.2  | Process sequence for device fabrication                                        | 80  |

|   | 4.3  | Layout of the JMOS device                                                      | 81  |

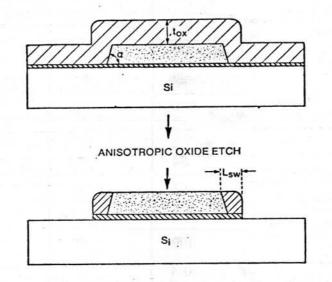

|   | 4.4  | Sidewall oxide process sequence                                                | 84  |

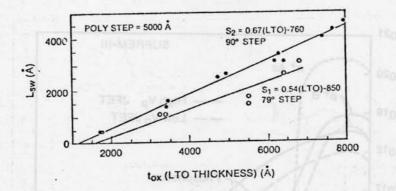

|   | 4.5  | Sidewall width dependence on LPCVD oxide                                       | 85  |

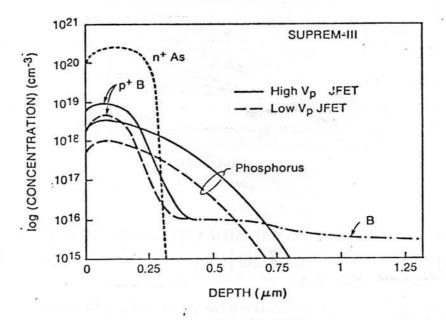

|   | 4.6  | SUPREM simulated impurity profiles                                             | 86  |

|   | 4.7  | SUPREM impurity profiles of high $V_p$ JFET                                    | 87  |

|   | 4.8  | Subthreshold characteristics for the low $V_p$ JMOSFET                         | 88  |

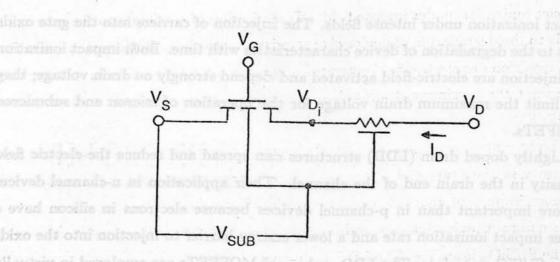

|   | 4.9  | JMOS circuit model                                                             | 89  |

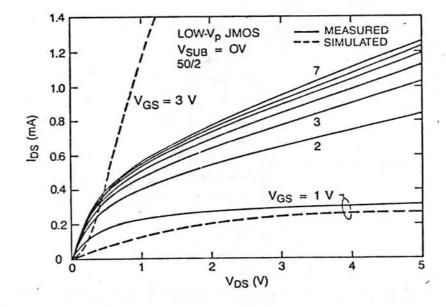

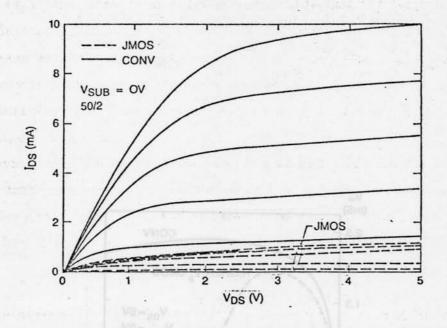

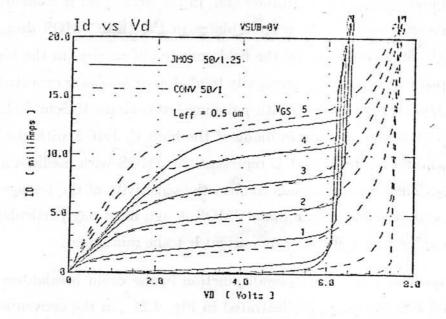

|   | 4.10 | Measured $I_{DS} - V_{DS}$ characteristics for a low $V_p$ JMOSFET             | 90  |

|   | 4.11 | Cross section of the JFET drain region                                         | 93  |

|   | 4.12 | Comparison of measured $I_{DS} - V_{DS}$ characteristics for a low $V_p$ JMOS- |     |

|   |      | FET                                                                            | 95  |

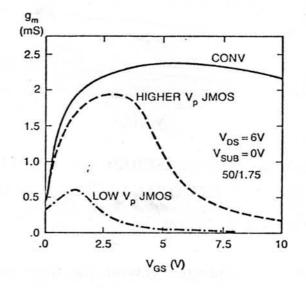

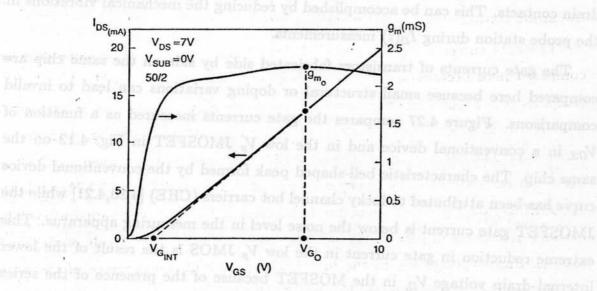

|   | 4.13 | Transconductance comparison for JMOS and conventional devices .                | 96  |

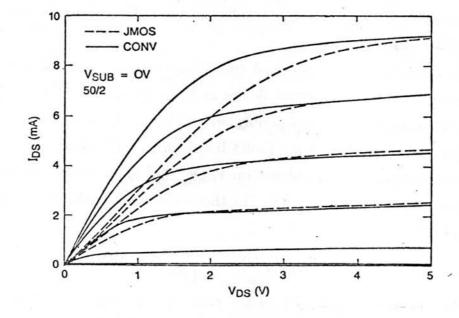

|   | 4.14 | Comparison of measured $I_{DS} - V_{DS}$ characteristics for medium $V_p$      |     |

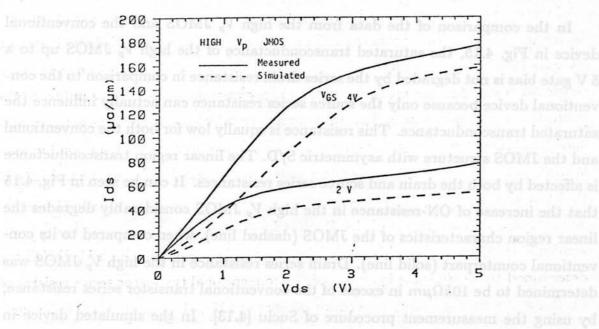

|   |      | JMOSFET                                                                        | 98  |

|   | 4.15 | Comparison of measured $I_{DS} - V_{DS}$ characteristics for the high- $V_p$   |     |

|   |      | JMOSFET                                                                        | 99  |

|   | 4.16 | PISCES equipotential for the high $V_p$ JMOSFET                                | 100 |

|   | 4.17 | Comparison of simulated and measured high $V_p$ I-V                            | 101 |

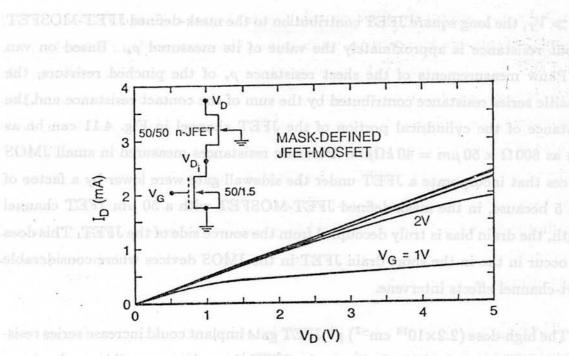

|   |      | I-V characteristics of a mask-defined JMOS                                     |     |

|   | 4.19 | Linear region threshold shift vs $L_{eff}$                                     | 105 |

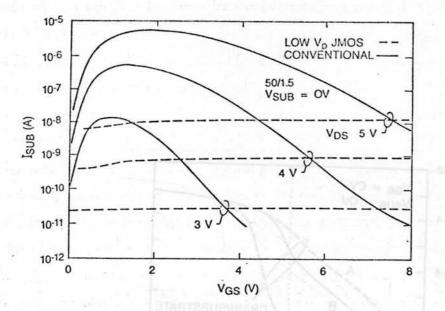

|   |      | Substrate current vs $V_{GS}$ comparison for conventional and low $V_p$ JMOS:  |     |

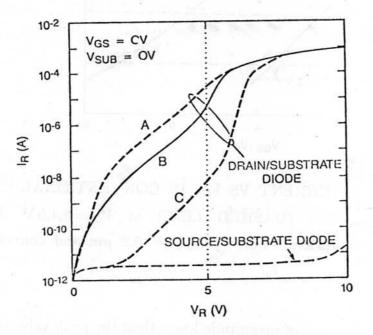

|   | 14   | Reverse source/drain diode characteristics                                     |     |

|   |      | Drain breakdown characteristics                                                |     |

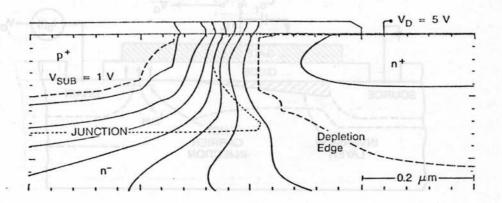

|   |      | GEMINI equipotential contours at breakdown                                     |     |

|   | 4.24 | Floating gate Ic measurement technique                                         | 112 |

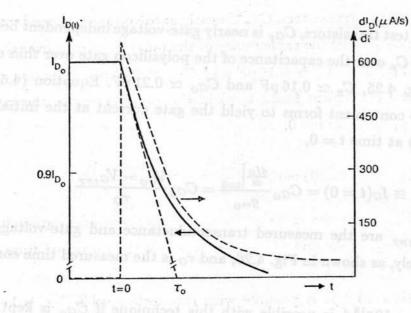

| 4.25 | Typical drain current decay with gate floating                                                                                    |

|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 4.26 | Current and transconductance dependence on $V_{GS}$                                                                               |

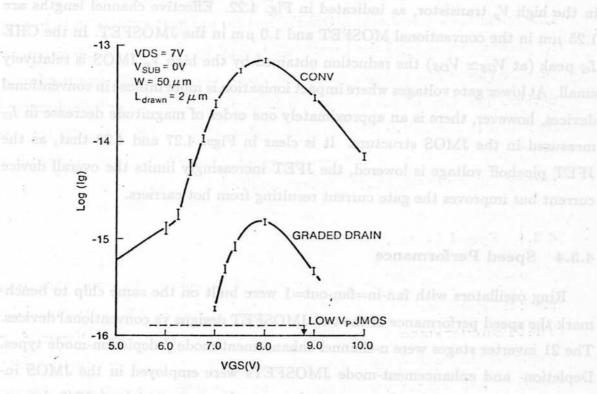

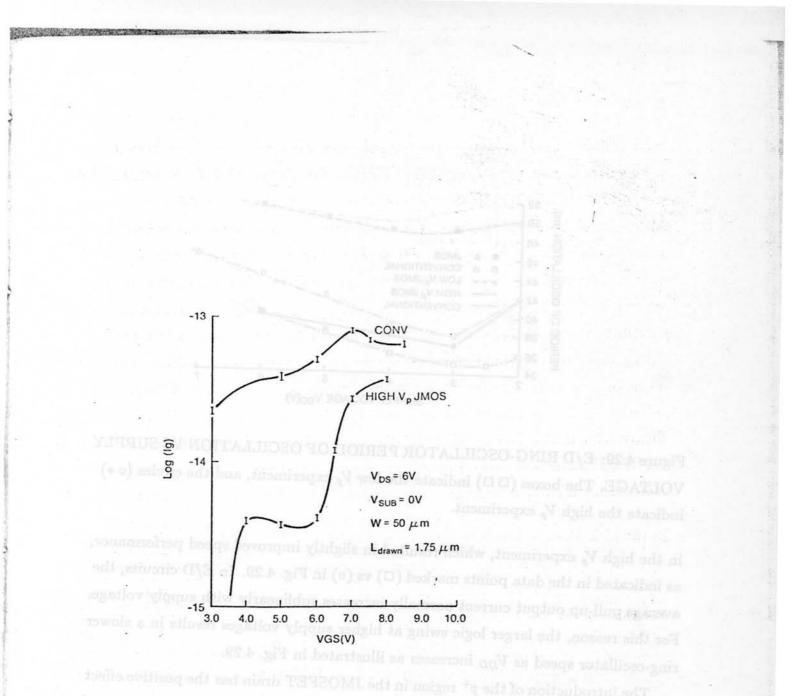

| 4.27 | Gate current vs $V_{GS}$ in conventional and low $V_p$ devices 115                                                                |

| 4.28 | Gate current vs $V_{GS}$ in conventional and high $V_p$ devices                                                                   |

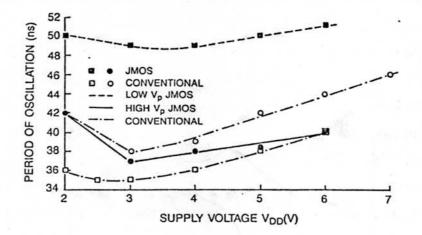

| 4.29 | E/D ring-oscillator period of oscillation vs. supply voltage 118                                                                  |

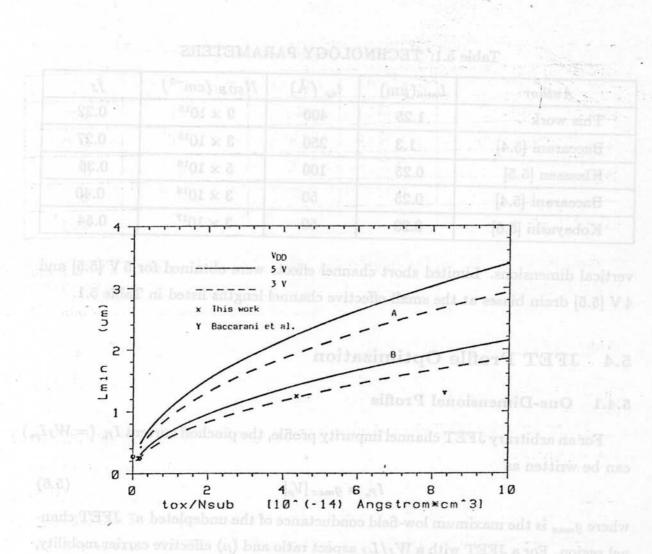

| 5.1  | $L_{min}$ curve for CV scaling                                                                                                    |

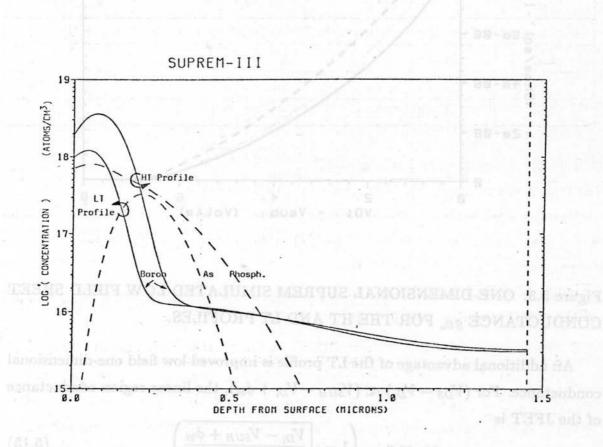

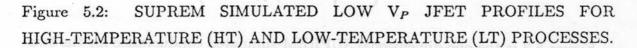

| 5.2  | HT and LT low $V_p$ profiles                                                                                                      |

| 5.3  | Low field simulated sheet conductance                                                                                             |

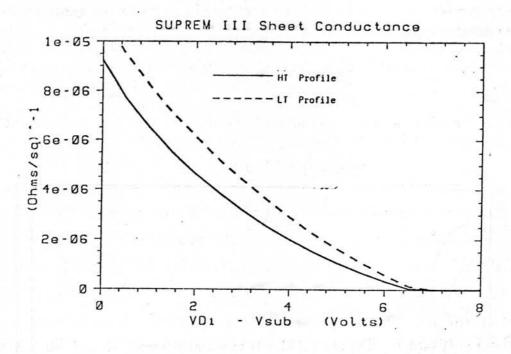

| 5.4  | Equipotential contours and field intensity for low $V_p$ JMOS 136                                                                 |

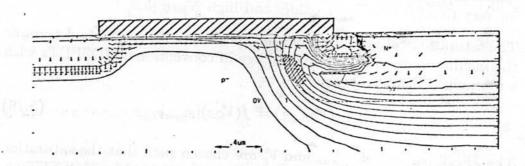

| 5.5  | Equipotential contours and field intensity for high $V_p$ JMOS 136                                                                |

| 5.6  | $V_{DS_{Sat}}$ Dependence on $V_{GS}$                                                                                             |

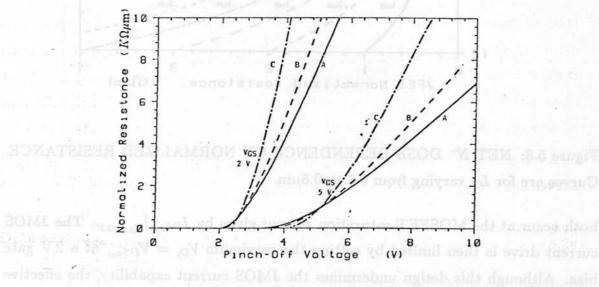

| 5.7  | Normalized resistance dependence on $V_p$                                                                                         |

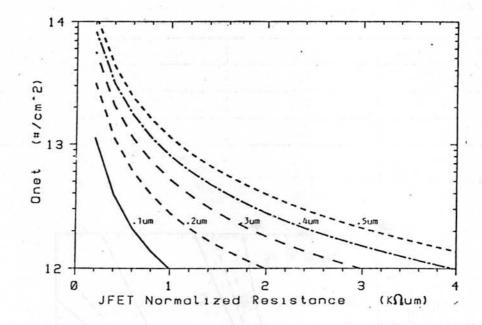

| 5.8  | Net Dose vs. normalized resistance                                                                                                |

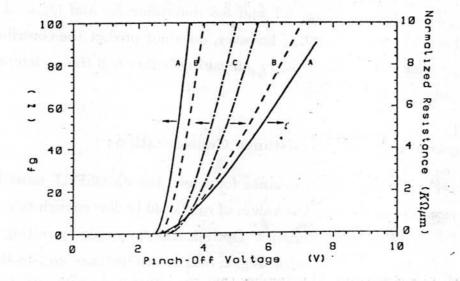

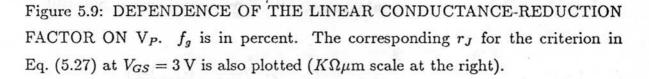

| 5.9  | Linear conductance reduction factor dependence on $V_p$                                                                           |

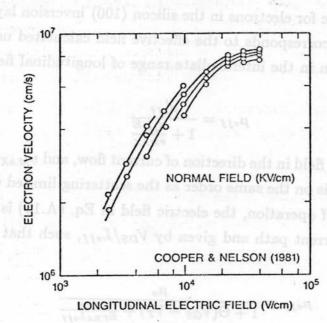

| A.1  | Drift velocity vs longitudinal field                                                                                              |

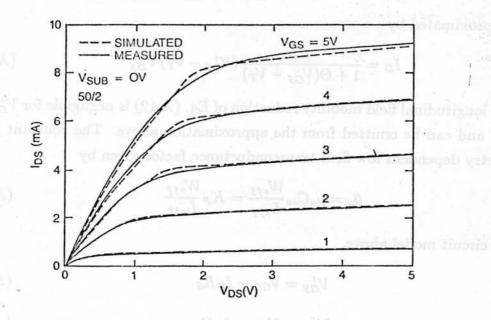

| A.2  | Comparison of measured vs simulated $I-V$                                                                                         |

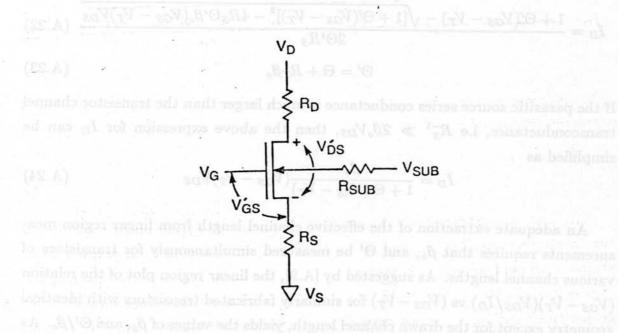

| A.3  | MOS transistor with series source-drain resistance 157                                                                            |

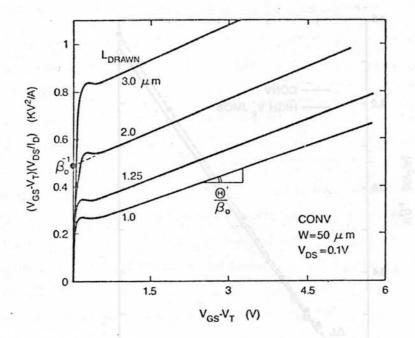

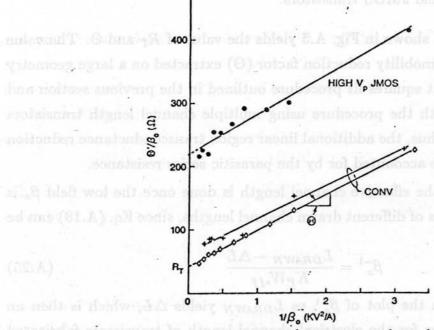

| A.4  | Measurement of low field $\beta_o$ and $\Theta' \ldots 159$ |

| A.5  | Extraction of $\Theta$ and $R_T$                                                                                                  |

| A.6  | $L_{eff}$ measurement technique                                                                                                   |

xvi

. STUDY STUDY

-----

.....

## List of Tables

| 1.1 | Constant field scaling rules 4             |

|-----|--------------------------------------------|

| 2.1 | Scaling Rules 11                           |

| 3.1 | SPICE Device Parameters                    |

| 4.1 | Masking steps in the JMOS process          |

| 4.2 | JMOS process parameters                    |

| 5.1 | $L_{min}$ for different technologies       |

| 5.2 | High and Low Temperature JMOS profiles     |

| 5.3 | $L_{min}$ Parameters for the JMOS Design , |

| A.1 | SPICE MOSFET Parameters 156                |

## List of Symbols

| a                | width of the JFET channel                                     |

|------------------|---------------------------------------------------------------|

| A                | proportionality constant for empirical scaling                |

| $d_{jd}$         | drain junction depletion-layer width                          |

| djs              | source junction depletion-layer width                         |

| dt               | infinitesimal time step                                       |

| D                | $n^-$ impurity dose                                           |

| $E_i$            | intrinsic Fermi energy level                                  |

| $E_{CRIT}$       | critical field for velocity saturation                        |

| $E_f$            | Fermi level                                                   |

| $f_g$            | MOSFET-JFET linear region conductance ratio                   |

| fj               | S/D junction depth scaling ratio                              |

| g <sub>D</sub> , | JFET linear region conductance                                |

| $g_m$            | MOSFET transconductance                                       |

| g <sub>m</sub>   | JMOSFET transconductance                                      |

| gmsym            | symmetrical JMOSFET transconductance                          |

| $g_{m_O}$        | MOSFET transconductance at $t = 0$                            |

| g <sub>max</sub> | maximum conductance of the undepleted JFET                    |

| $I_D, I_{DS}$    | drain current                                                 |

| $I_G$            | gate current                                                  |

| $I_p$            | JFET pinchoff current                                         |

| $I_{po}$         | JFET pinchoff current proportionality constant per unit width |

| I <sub>Po</sub>  | JFET pinchoff current proportionality constant                |

|                  |                                                               |

xix

| _Ipmax              | maximum JMOS pinchoff current                               |

|---------------------|-------------------------------------------------------------|

| $I_{SUB}$           | substrate current                                           |

| I <sub>SUBMAX</sub> | maximum substrate current at fixed $V_{DS}$                 |

| κ                   | MOSFET scaling factor                                       |

| Ks                  | supply-voltage scaling factor                               |

| $K_P$               | MOSFET transconductance factor                              |

| LDRAWN              | drawn mask channel length                                   |

| $L, L_{eff}$        | MOSFET effective electrical channel length                  |

| $L_J$               | JFET effective electrical channel length                    |

| $\Delta L$          | difference between the drawn and electrical channel lengths |

| $L_{min}$           | minimum effective channel length                            |

| $L_{sw}$            | sidewall-spacer oxide length                                |

| $\boldsymbol{y}$    | space coordinate in the depth direction                     |

| n                   | nonuniform JFET channel doping factor                       |

| Ν                   | net impurity concentration in the JFET channel              |

| $N_{Deff}$          | net impurity concentration in the equivalent                |

|                     | uniformly-doped JFET channel                                |

| $N_{SUB}$           | effective substrate doping concentration                    |

| Р                   | power dissipation                                           |

| q                   | elemental charge (= $1.6 \times 10^{-19}$ C)                |

| $Q_B$               | depletion-layer charge per unit area                        |

| $Q_m$               | inversion-layer mobile charge per unit area                 |

| Qnet                | net $n^-$ impurity dose in the JFET channel                 |

| $r_J$               | undepleted-channel JFET resistance per unit width           |

| $R_D$               | drain parasitic series resistance                           |

| $R_S$               | source parasitic series resistance                          |

| $R_T$               | total parasitic series resistance                           |

| t                   | variable time                                               |

|                     |                                                             |

÷

.

xx

| teff                          | effective JFET channel thickness for uniform doping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $t_{ox}$                      | silicon-dioxide thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $V_{DD}$                      | supply voltage for MOS circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $V_{D_i}$                     | drain voltage at the intrinsic MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{DS}$                      | drain-to-source external voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_{DS}^{\prime}$             | effective drain-to-source voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>DS<sub>Sat</sub></sub> | drain-to-source saturation voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $V_{FB}$                      | metal-oxide-semiconductor flatband voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>GS</sub>               | gate-to-source external voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $V_{GS}'$                     | effective gate-to-source voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_p$                         | JFET pinchoff voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{p_o}$                     | pinchoff voltage of the equivalent uniformly doped JFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SUB</sub>              | substrate-to-source external voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_T$                         | MOSFET threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $\Delta V_T$                  | threshold voltage shift in short channel MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_{T_J}$                     | JFET threshold voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| $V_{To}$                      | MOSFET threshold voltage at zero substrate bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $\langle v \rangle$           | average inversion-layer carrier velocity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $v_{sat}, v_{max}$            | bulk scattering-limited velocity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| xj                            | junction depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $x_{j_n-}$                    | $n^-/p$ metalurgical junction depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $x_{j_n+}$                    | $n^+/p$ metalurgical junction depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $x_{j_{p+1}}$                 | $p^+/n^-$ metalurgical junction depth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| W <sub>DRAWN</sub>            | drawn-mask channel width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| W, W <sub>eff</sub>           | effective electrical channel width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| $W_J$ ,                       | JFET effective electrical channel width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| β                             | JFET transconductance factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $\epsilon_{ox}$               | silicon-dioxide dielectric constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                               | 그 같아요. 그는 것 같은 것 같아요. 그는 것 같아요. 그는 것 같아요. 나는 것 같아요. 이 것 같아요. 이 것 같아요. 나는 것 않는 것 같아요. 나는 것 않는 것 같아요. 나는 것 않는 것 같아요. 나는 한 것 같아요. 나는 것 않는 것 않는 것 같아요. 나는 것 않는 것 |

xxi

| silicon dielectric constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bulk Fermi potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| p-n junction built-in potential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| body factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |