# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

# DANIEL ALFONSO GONÇALVES DE OLIVEIRA

# **Hardening Strategies for HPC Applications**

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Philippe Olivier Alexandre

Navaux

Coadvisor: Prof. Dr. Paolo Rech

## **CIP** — **CATALOGING-IN-PUBLICATION**

Oliveira, Daniel Alfonso Gonçalves de

Hardening Strategies for HPC Applications / Daniel Alfonso Gonçalves de Oliveira. – Porto Alegre: PPGC da UFRGS, 2018.

133 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR–RS, 2018. Advisor: Philippe Olivier Alexandre Navaux; Coadvisor: Paolo Rech.

1. HPC. 2. Fault Tolerance. 3. Accelerators. 4. Radiation Experiments. 5. Fault Injection. 6. Reliability. 7. Hardening Strategies. 8. Selective Hardening. I. Navaux, Philippe Olivier Alexandre. II. Rech, Paolo. III. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PPGC: Prof. João Luiz Dihl Comba

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### ACKNOWLEDGEMENT

First of all, I would like to thank Prof. Philippe Olivier Alexandre Navaux, my Ph.D. advisor, and Prof. Paolo Rech, my Ph.D. coadvisor. Thanks for all the support and patience during my academic development. The precious advisement helped me reach farther than I could imagine.

I would also like to thank Prof. Israel Koren, who was my advisor on a Sandwich Ph.D. at the University of Massachusetts at Amherst. Thanks for receiving me and all the ideas and discussions regarding this thesis, especially the CAROL-FI fault injector that was developed during my time at UMass Amherst. I cannot forget Prof. Sandip Kundu who also helped with good discussions about the thesis work.

I am also grateful for the collaborations I had during my Ph.D., especially with the researchers at Los Alamos Nathan DeBardeleben, Sean Blanchard, and Heather M. Quinn.

Many thanks to my colleagues of the Group of Parallel and Distributed Processing (GPPD), for the help that goes beyond technical discussions.

I would also like to thank my family, especially my wife Natalia and my parents Delio and Mary Leusa. I could not have done it without them. Finally, I thank God who brought me to the existence and helped me all this way.

#### **ABSTRACT**

HPC device's reliability is one of the major concerns for supercomputers today and for the next generation. In fact, the high number of devices in large data centers makes the probability of having at least a device corrupted to be very high. In this work, we first evaluate the problem by performing radiation experiments. The data from the experiments give us realistic error rate of HPC devices. Moreover, we evaluate a representative set of algorithms deriving general insights of parallel algorithms and programming approaches reliability.

To understand better the problem, we propose a novel methodology to go beyond the quantification of the problem. We qualify the error by evaluating the criticality of each corrupted execution through a dedicated set of metrics. We show that, as long as imprecise computing is concerned, the simple mismatch detection is not sufficient to evaluate and compare the radiation sensitivity of HPC devices and algorithms. Our analysis quantifies and qualifies radiation effects on applications' output correlating the number of corrupted elements with their spatial locality. We also provide the mean relative error (dataset-wise) to evaluate radiation-induced error magnitude.

Furthermore, we designed a homemade fault-injector, CAROL-FI, to understand further the problem by collecting information using fault injection campaigns that is not possible through radiation experiments. We inject different fault models to analyze the sensitivity of given applications. We show that portions of applications can be graded by different criticalities. Mitigation techniques can then be relaxed or hardened based on the criticality of the particular portions.

This work also evaluates the reliability behaviors of six different architectures, ranging from HPC devices to embedded ones, with the aim to isolate code- and architecture-dependent behaviors. For this evaluation, we present and discuss radiation experiments that cover a total of more than 352,000 years of natural exposure and fault-injection analysis based on a total of more than 120,000 injections.

Finally, Error-Correcting Code, Algorithm-Based Fault Tolerance, and Duplication With Comparison hardening strategies are presented and evaluated on HPC devices through radiation experiments. We present and compare both the reliability improvement and imposed overhead of the selected hardening solutions. Then, we propose and analyze the impact of selective hardening for HPC algorithms. We perform fault-injection campaigns to identify the most critical source code variables and present how to select the best can-

didates to maximize the reliability/overhead ratio.

**Keywords:** HPC. Fault Tolerance. Accelerators. Radiation Experiments. Fault Injection.

Reliability. Hardening Strategies. Selective Hardening.

# Estratégias de Enrobustecimento para Aplicações PAD

#### **RESUMO**

A confiabilidade de dispositivos de Processamentos de Alto Desempenho (PAD) é uma das principais preocupações dos supercomputadores hoje e para a próxima geração. De fato, o alto número de dispositivos em grandes centros de dados faz com que a probabilidade de ter pelo menos um dispositivo corrompido seja muito alta. Neste trabalho, primeiro avaliamos o problema realizando experimentos de radiação. Os dados dos experimentos nos dão uma taxa de erro realista de dispositivos PAD. Além disso, avaliamos um conjunto representativo de algoritmos que derivam entendimentos gerais de algoritmos paralelos e a confiabilidade de abordagens de programação.

Para entender melhor o problema, propomos uma nova metodologia para ir além da quantificação do problema. Qualificamos o erro avaliando a importância de cada execução corrompida por meio de um conjunto dedicado de métricas. Mostramos que em relação a computação imprecisa, a simples detecção de incompatibilidade não é suficiente para avaliar e comparar a sensibilidade à radiação de dispositivos e algoritmos PAD. Nossa análise quantifica e qualifica os efeitos da radiação na saída das aplicações, correlacionando o número de elementos corrompidos com sua localidade espacial. Também fornecemos o erro relativo médio (em nível do conjunto de dados) para avaliar a magnitude do erro induzido pela radiação.

Além disso, desenvolvemos um injetor de falhas, CAROL-FI, para entender melhor o problema coletando informações usando campanhas de injeção de falhas, o que não é possível através de experimentos de radiação. Injetamos diferentes modelos de falha para analisar a sensitividade de determinadas aplicações. Mostramos que partes de aplicações podem ser classificadas com diferentes criticalidades. As técnicas de mitigação podem então ser relaxadas ou enrobustecidas com base na criticalidade de partes específicas da aplicação.

Este trabalho também avalia a confiabilidade de seis arquiteturas diferentes, variando de dispositivos PAD a embarcados, com o objetivo de isolar comportamentos dependentes de código e arquitetura. Para esta avaliação, apresentamos e discutimos experimentos de radiação que abrangem um total de mais de 352.000 anos de exposição natural e análise de injeção de falhas com base em um total de mais de 120.000 injeções.

Por fim, as estratégias de ECC, ABFT e de duplicação com comparação são apresentadas

e avaliadas em dispositivos PAD por meio de experimentos de radiação. Apresentamos e comparamos a melhoria da confiabilidade e a sobrecarga imposta das soluções de enrobustecimento selecionadas. Em seguida, propomos e analisamos o impacto do enrobustecimento seletivo para algoritmos de PAD. Realizamos campanhas de injeção de falhas para identificar as variáveis de código-fonte mais críticas e apresentamos como selecionar os melhores candidatos para maximizar a relação confiabilidade/sobrecarga.

**Palavras-chave:** PAD, Tolerância a Falhas, Aceleradores, Experimentos de Radiação, Injeção de Falhas, Confiabilidade, Estratégias de Enrobustecimento, Enrobustecimento Seletivo.

## LIST OF ABBREVIATIONS AND ACRONYMS

ABFT Algorithm-Based Fault Tolerance

AMR Automatic Mesh Refinement

AVF Architectural Vulnerability Factor

BFI Branch Free Intervals

BID Branch Free Interval Identifier

BSSC Block Signature Self-Checking

CCA Control Flow Checking Using Assertions

CFCSS Control Flow Checking by Software Signatures

CFID Control Flow Identifier

CI Comparison Instructions

COTS Commercial off-the-shelf

CSM Continuous Signature Monitoring

DUE Detected Uncorrectable Error

DWC Duplication With Comparison

ECC Error-Correcting Code

ECCA Enhanced Control-flow Checking Using Assertions

EDAC Error Detection and Correction

EDDI Error Detection by Duplicated Instruction

EMU Extended Math Unit

FDM Finite Difference Methods

FFT Fast Fourier Transform

FIT Failure In Time

FPU Floating Point Unit

FWT Fast Wavelet Transform

GPU Graphics Processing Units

IMCI Initial Many-Core Instructions

ISC Implicit Signature Checking

MBU Multiple Bit Upset

MCA Machine Check Architecture

MEBF Mean Executions Between Failures

MI Master Instructions

MTBF Mean Time Between Failure

MTrans Matrix Transpositions

MWBF Mean Workload Between Failure

NW Needleman-Wunsch

OSLC On-line Signature Learning and Checking

PTX Parallel Thread Execution

PVF Program Vulnerability Factor

R-S Reed-Solomon

RF Register File

SBB Storeless Basic Block

SCP Self-Checking Pair

SDC Silent Data Corruption

SECDED Single Error Correction Double Error Detection

SEE Single Event Effect

SET Single Event Transient

SEU Single Event Upsets

SI Shadow Instructions

SM Streaming Multiprocessors

SWIFT Software Implemented Fault Tolerance

TMR Triple Modular Redundancy

ULA Ultra Low Alpha

VPU Vector Processing Unit

YACCA Yet Another Control-Flow Checking using Assertions

# LIST OF FIGURES

| Figure 2.1 | NVIDIA Kepler Memory Hierarchy                                  | 21  |

|------------|-----------------------------------------------------------------|-----|

|            | Intel Xeon Phi Architecture.                                    |     |

| Figure 3.1 | Triple Modular Redundancy.                                      | 28  |

|            | Reed-Solomon codeword                                           |     |

|            | ABFT Matrix Multiplication Scheme                               |     |

| Figure 4.1 | LANSCE and ISIS neutrons spectra                                | 39  |

|            | SDC and DUE combined Mean Workload Between Failure              |     |

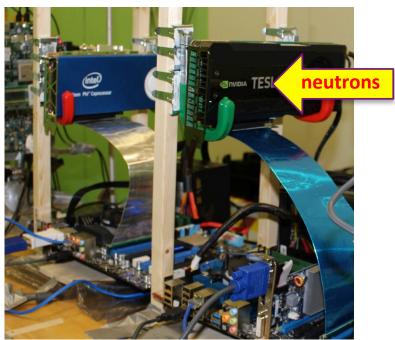

| Figure 5.1 | Experimental setup at LANSCE                                    | 57  |

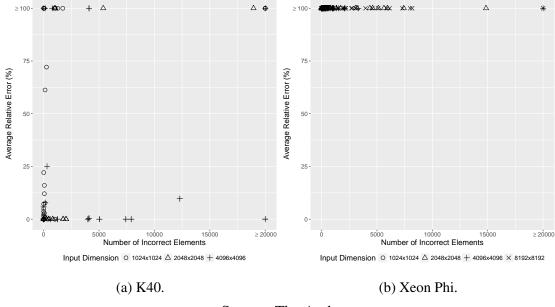

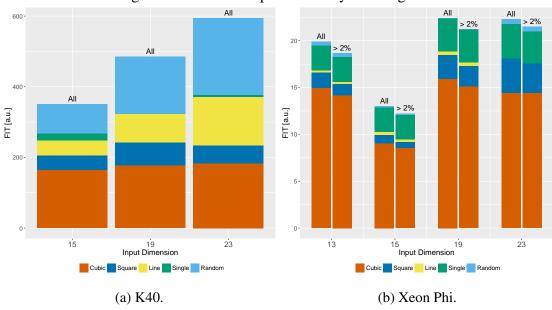

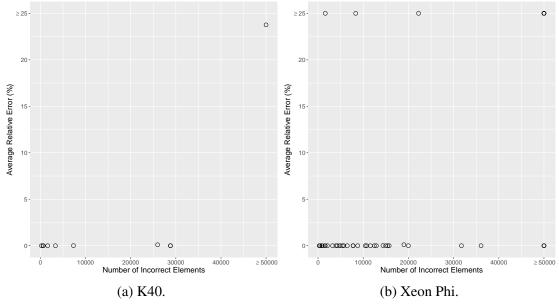

| Figure 5.2 | DGEMM Mean relative error and Incorrect Elements.               | 59  |

| Figure 5.3 | DGEMM spatial locality and magnitude                            | 60  |

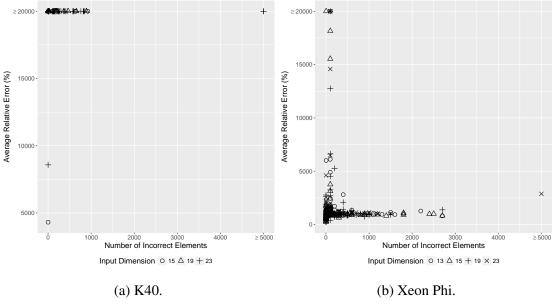

| _          | LavaMD Mean relative error and Incorrect Elements               |     |

| Figure 5.5 | LavaMD spatial locality and magnitude                           | 62  |

| _          | HotSpot Mean relative error and Incorrect Elements              |     |

|            | HotSpot spatial locality and magnitude                          |     |

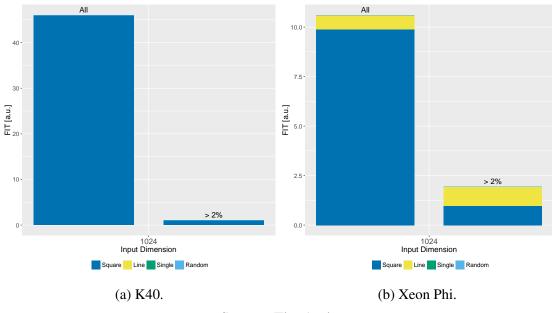

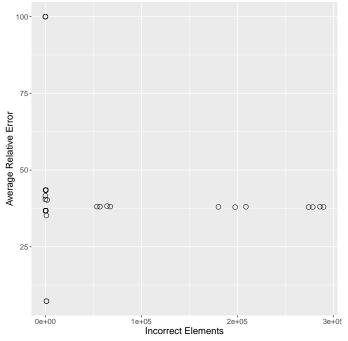

|            | CLAMR Mean relative error and Incorrect Elements for Xeon Phi   |     |

|            | CLAMR Error Locality Map.                                       |     |

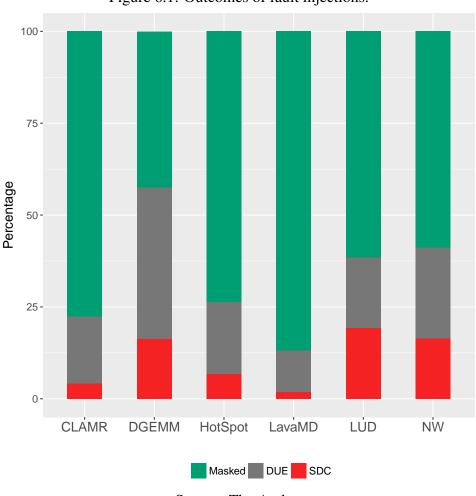

| Figure 6.1 | Outcomes of fault injections.                                   | 73  |

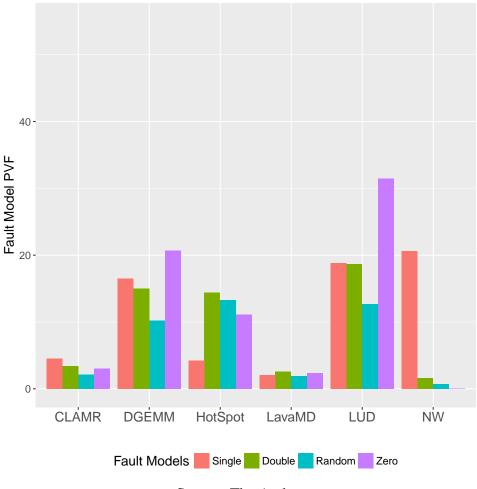

|            | SDC's PVF of the benchmarks for the different fault models      |     |

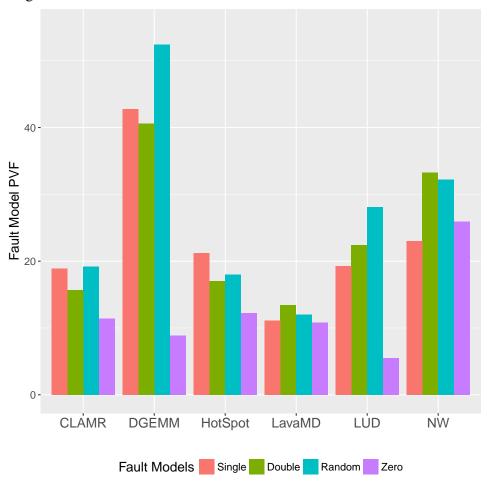

|            | DUE's PVF of the benchmarks for the different fault models      |     |

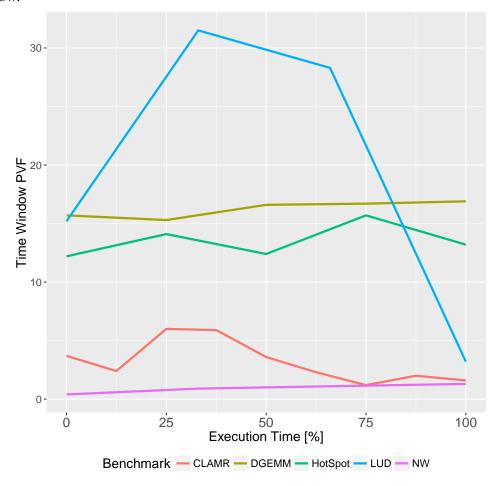

| _          | Dependence of SDC's PVF on execution time window                |     |

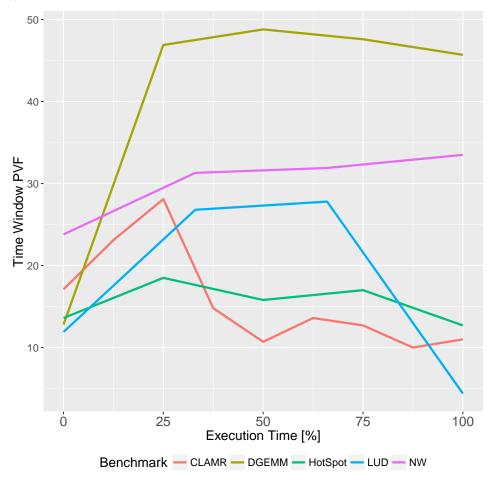

| _          | Dependence of DUE's PVF on execution time window                |     |

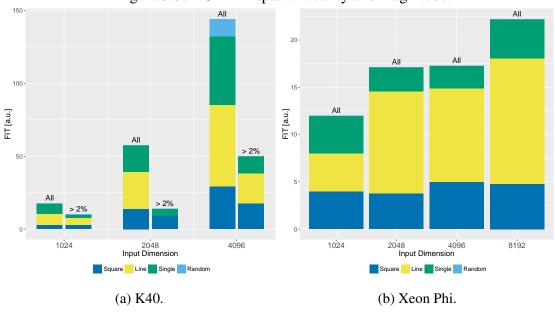

| Figure 7.1 | Radiation test setup at ChipIR                                  | 84  |

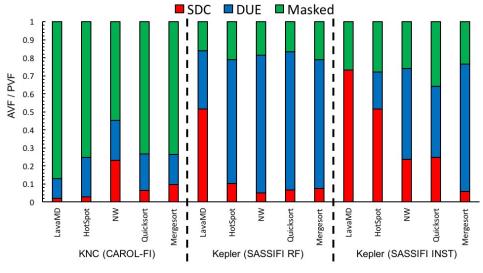

| Figure 7.2 | Fault injections results on the KNC and Kepler.                 | 86  |

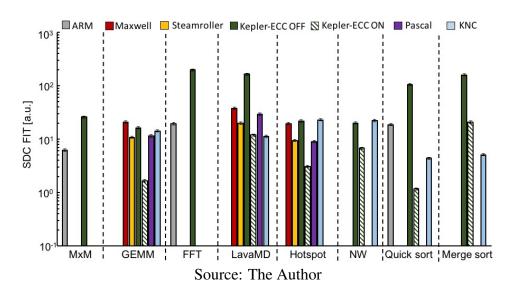

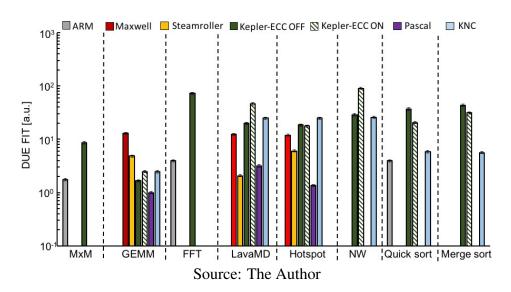

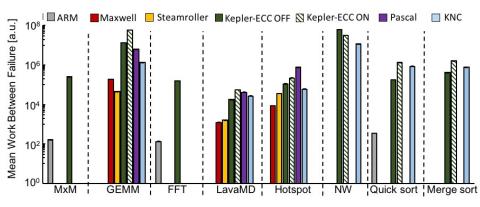

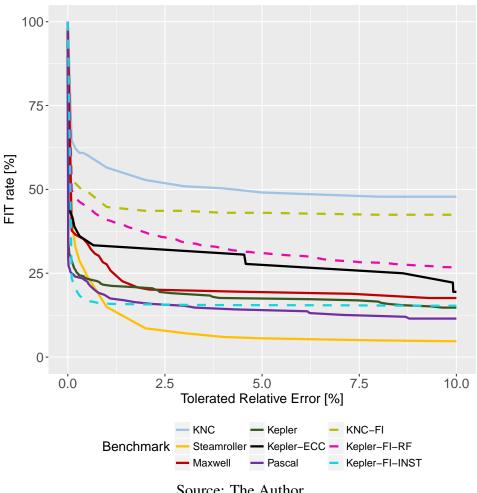

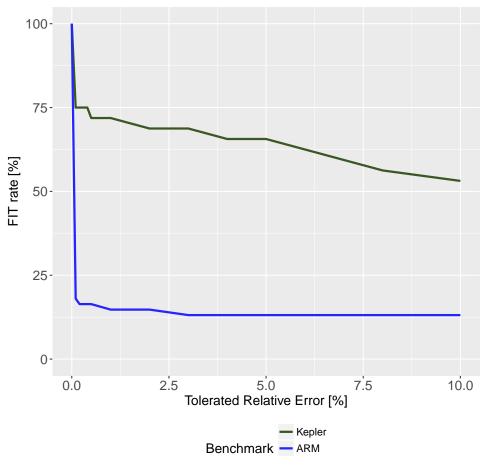

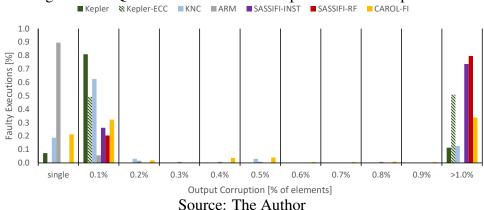

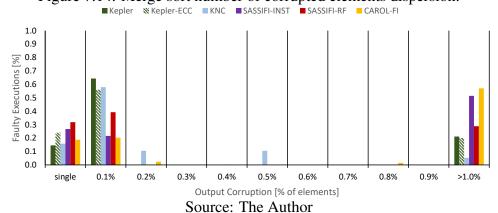

| Figure 7.3 | Beam experiment results, organized as relative FIT rate for SDC | 88  |

| Figure 7.4 | Beam experiment results, organized as relative FIT rate for DUE | 88  |

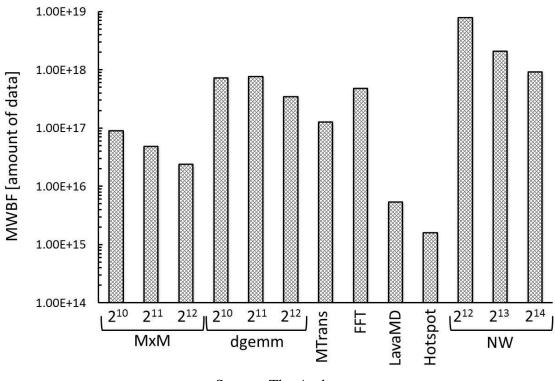

|            | Mean Workload Between Failure                                   |     |

| -          | GEMM relative error reduction.                                  |     |

| _          | HotSpot relative error reduction.                               |     |

|            | LavaMD relative error reduction.                                |     |

|            | FFT relative error reduction.                                   |     |

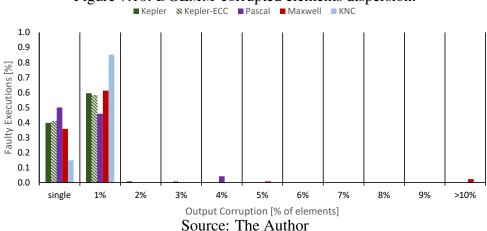

|            | DGEMM corrupted elements dispersion                             |     |

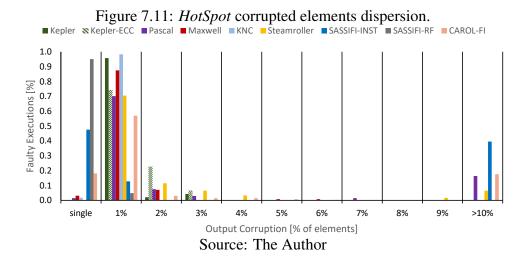

|            | 1 HotSpot corrupted elements dispersion                         |     |

|            | 2 LavaMD corrupted elements dispersion                          |     |

|            | 3 Quick sort number of corrupted elements dispersion            |     |

|            | 4 Merge sort number of corrupted elements dispersion.           |     |

| Figure 8.1 | Algorithm-Based Fault Tolerant for matrix multiplication        | 102 |

| _          | Algorithm-Based Fault Tolerant FFT                              |     |

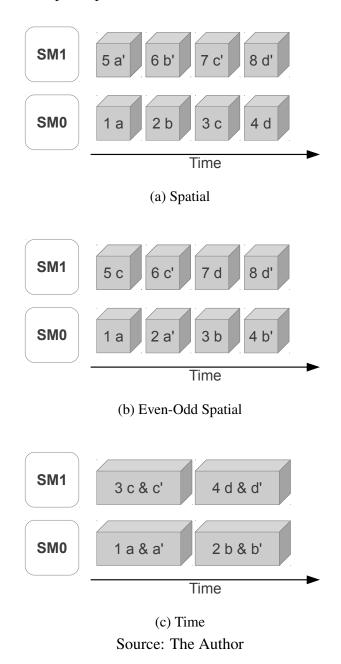

| -          | Duplication With Comparison strategies                          |     |

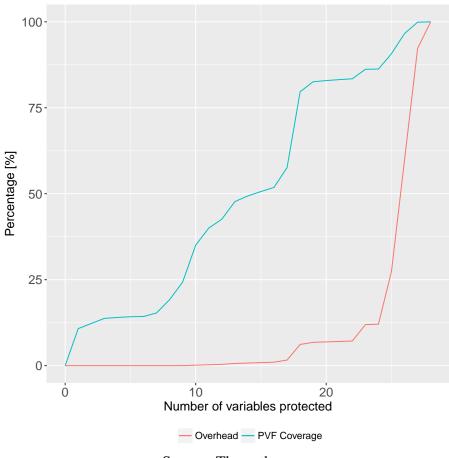

|            | DGEMM selective hardening.                                      |     |

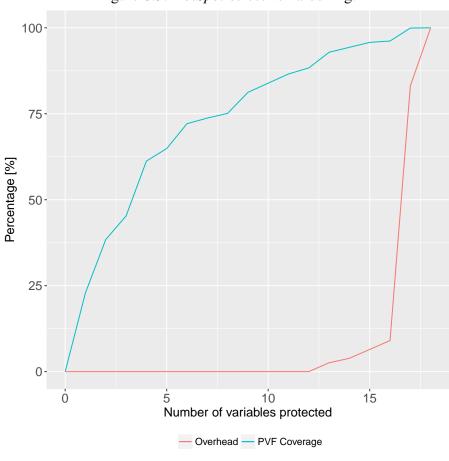

| _          | HotSpot selective hardening.                                    |     |

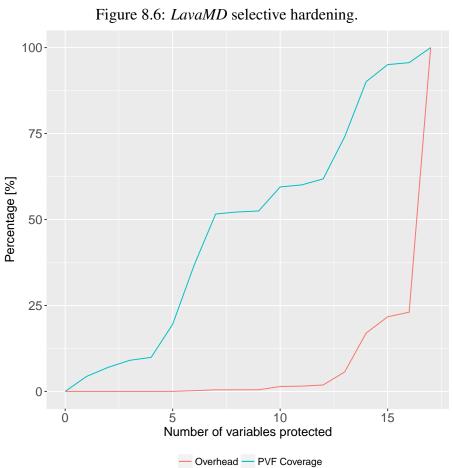

|            | LavaMD selective hardening.                                     |     |

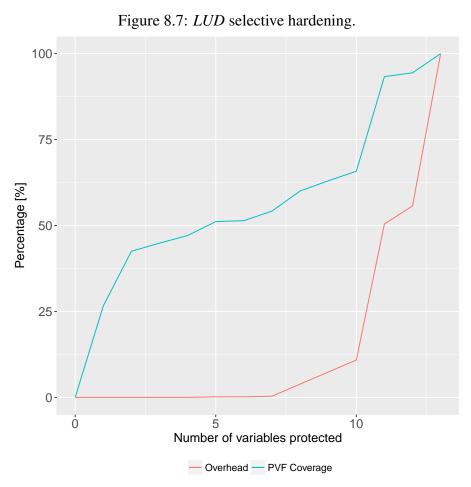

|            | LUD selective hardening.                                        |     |

# LIST OF TABLES

| Table 4.1 | Parallel applications details and experimental results                   | 43  |

|-----------|--------------------------------------------------------------------------|-----|

| Table 5.1 | Classification of parallel kernels.                                      | 55  |

|           | Parallel kernels' details.                                               |     |

| Table 7.1 | Devices under test specifications summary                                | 83  |

| Table 7.2 | Problem size, execution time, and FIT rates for the tested codes         | 85  |

| Table 8.1 | Efficiency and resiliency of the available hardening solutions for GPUs. | 108 |

| Table 8.2 | DGEMM CAROL-FI results                                                   | 110 |

| Table 8.3 | HotSpot CAROL-FI results                                                 | 112 |

|           | LavaMD CAROL-FI results                                                  |     |

| Table 8.5 | LUD CAROL-FI results.                                                    | 114 |

# **CONTENTS**

| 1 INTRODUCTION                                 | 14  |

|------------------------------------------------|-----|

| 2 BACKGROUND                                   | 17  |

| 2.1 Sources of Faults                          |     |

| 2.2 Radiation Effects in HPC Accelerators      | 19  |

| 3 RELATED WORK                                 |     |

| 3.1 Reliability Evaluation                     | 25  |

| 3.2 Hardening Strategies                       |     |

| 4 RELIABILITY ANALYSIS                         |     |

| 4.1 Methodology                                | 38  |

| 4.2 Experimental Results                       |     |

| 4.3 Discussion                                 |     |

| 5 RADIATION EXPERIMENTS CRITICALITY ASSESSMENT | 51  |

| 5.1 Methodology                                |     |

| 5.2 Reliability and Criticality Evaluation     |     |

| 5.3 Discussion                                 |     |

| 6 FAULT INJECTION CRITICALITY ASSESSMENT       |     |

| 6.1 Methodology                                |     |

| 6.2 Results                                    |     |

| 6.3 Discussion                                 |     |

| 7 RELIABILITY AND CRITICALITY COMPARISON       |     |

| 7.1 Methodology                                |     |

| 7.2 Reliability Evaluation                     |     |

| 7.3 Error Criticality Analysis                 |     |

| 7.4 Discussion                                 |     |

| 8 HARDENING SOLUTIONS                          |     |

| 8.1 Hardware-based vs Software-based Hardening |     |

| 8.2 Selective Hardening                        |     |

| 8.3 Discussion                                 |     |

| 9 CONCLUSION                                   |     |

| 9.1 Publications                               |     |

| REFERENCES                                     | 123 |

#### 1 INTRODUCTION

Accelerators are extensively used nowadays to expedite calculations in large HPC centers. Intel *Xeon Phis* and NVIDIA *Kepler* GPUs, for instance, power six of the top 10 supercomputers (DONGARRA; MEUER; STROHMAIER, 2015). Tianhe-2, Cori, Trinity, and Oakforest-PACS are powered by Xeon Phis, while NVIDIA GPUs are used as accelerators in Titan and Piz Daint. The main reasons to use accelerators are their high computational capacity, low cost, reduced per-task energy consumption, and flexible development platforms. However, accelerators are also extremely likely to experience transient errors as they are built with cutting-edge technology, have very high operation frequencies, and include large amounts of resources.

Nowadays, reliability is one of the major concerns not only for safety-critical but for HPC applications as well. Various sources of faults could undermine the system reliability, including environmental perturbations, software errors, manufacturing process, temperature, and voltage variations (LUTZ, 1993; LAPRIE, 1995; NICOLAIDIS, 1999). Such faults may corrupt data values or logic operations and lead to Silent Data Corruption (SDC), Detected Uncorrectable Error (DUE), or be masked and cause no observable error (CONSTANTINESCU, 2002; SAGGESE et al., 2005; SCHROEDER; PIN-HEIRO; WEBER, 2011). This work focus on radiation-induced soft errors that, according to (BAUMANN, 2005), are a considerable concern in modern computing devices because, if uncorrected, may produce a failure rate that is higher than all the other error sources combined. As a reference, DOE's Titan, composed of more than 18,000 Kepler GPUs, has a radiation-induced Mean Time Between Failures (MTBF) in the order of dozens of hours (GOMEZ et al., 2014; TIWARI et al., 2015). As we approach exascale, the resilience challenge will become even more critical due to an increase in system scale (LUCAS, 2014; SNIR et al., 2014; RESEARCH, 2016). In this scenario, a lack of understanding of HPC device resilience may lead to lower scientific productivity and significant monetary loss (SNIR et al., 2014).

For this work, we intent to *evaluate*, *understand*, and *develop mitigation strategies* for reliability issues in current and future supercomputers. To first evaluate the problem we make a thorough analysis of HPC devices radiation reliability based on analytical studies and a series of extensive accelerated beam tests. We evaluate the error rate of registers and caches of two consecutive GPU generations. Details on pattern dependence and multiple error occurrences are also provided. Then, we study a representative set

of parallel algorithms from HPC domains, correlating their characteristics and observed radiation sensitivity.

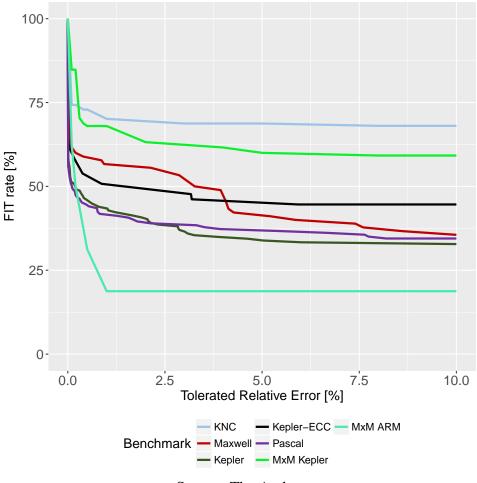

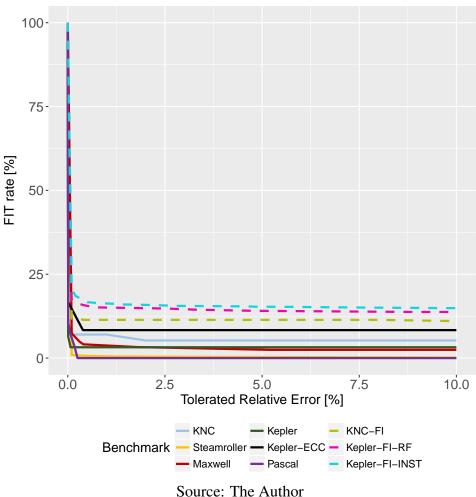

Depending on the application and circumstances, some SDCs that are satisfactory close to the correct results may be tolerated in HPC (PUENTE et al., 2014; BREUER, 2005). To consider the outputs' error severity and better *understand* the reliability issue, we evaluate how errors manifest at the application's output and measures how the error rate reduces as a function of the tolerated level of imprecision in the output. For *HotSpot*, for instance, the error rate is reduced by 85% if a 0.5% variation in the output value is acceptable.

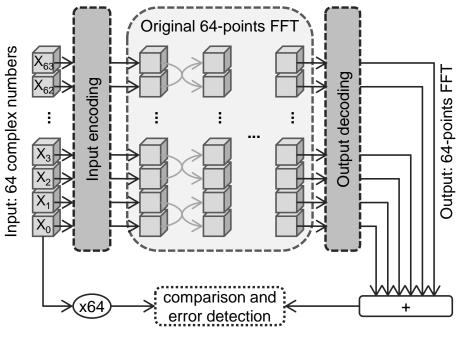

As part of this thesis, we designed a fault-injector, named CAROL-FI, to perform a detailed analysis of the applications' vulnerabilities to transient errors. Unlike most fault-injection frameworks, CAROL-FI injections are made at the highest possible level, to identify the algorithm portions that are more likely to generate an SDC or a DUE. CAROL-FI is intended as a tool to help developers to identify the portions of their code that, once corrupted, are more likely to affect the output and can then provide pragmatic information to develop mitigation strategies for the reliability issue in HPC.

To *understand* deeper the reliability issue, we investigate the reliability of six computing architectures (ARM *Cortex A9*, NVIDIA *Maxwell*, *Kepler*, *Pascal*, AMD *Steam-roller*, and the Intel *Knights Corner (KNC)*). We carefully select a set of eight algorithms to compare the reliability of the considered devices. Each code has peculiar characteristics regarding memory utilization, computing power, control-flow operation, etc. To highlight specific architecture behaviors that could be generalized to similar classes of algorithms.

Finally, to *develop mitigation strategies* for HPC applications we first evaluate hardware and software techniques. We studied specific and generic hardening techniques like Algorithm-Based Fault Tolerance (ABFT) and Duplication With Comparison (DWC), and then compare these techniques with hardware implemented Error Correcting Code (ECC). We showed that ECC has the weakest protection, but it can provide the best overhead if the application is not memory-bound. ABFT has better protection with slightly higher overhead. DWC has the strongest protection but an extremely high overhead. Then, using the CAROL-FI fault injector insights, we show that a selective hardening of just a few variables can achieve protection close to the full DWC but with an overhead similar do hardware implemented ECC.

This thesis is organized as follow. Chapters 2 and 3 describe the background and related work for this thesis. Chapter 4 performs an in-depth analysis of radiation

experiments to *evaluate* the problem in an HPC device. Then, chapters 5 and 6 evaluate and go beyond the quantification of the problem and qualify the experiments to better *understand* the problem. Chapter 7 broadens our understanding performing a thorough comparison of several codes and architectures regarding the reliability issue. Finally, chapter 8 evaluates and proposes mitigation strategies for HPC applications.

#### 2 BACKGROUND

The trend pursued by hardware designers to improve computing devices performance and reduce power consumption is to employ higher-density chips, lower voltage levels, higher clock rates, and to integrate a large number of computing cores on a single chip. While these design factors yield performance enhancements, they also make hardware components less reliable, rendering modern computing platforms very prone to experience transient radiation-induced errors not only in radiation-harsh environments such as space but also at sea level (DODD et al., 2002; GASIOT; GIOT; ROCHE, 2006).

Even a single radiation-induced fault may be harmful to both the correct operation and the performance of the software. If not appropriately detected and corrected faults can be responsible for silent data corruptions leading to altered data, incorrect program executions, erroneous results, and eventually to machine crashes (BAUMANN, 2002). It is worth noting that applying the hardening solutions designed for space applications to terrestrial ones is unfeasible (costs will be prohibitive) and pointless as the error rate at sea level is lower than space one.

These issues are an actual problem for large-scale applications and have already caused severe failures with significant monetary losses. For instance, in 2000, Sun Microsystems reported that interferences of cosmic rays with cache memories were responsible for server crashes at major customer sites, including America Online, eBay, and many others (BAUMANN, 2002). Cypress Semiconductor acknowledged similar experiences (ZIEGLER; PUCHNER, 2004) who reported monthly halts in an automotive supplier factory and havoc at a large telephone company, and also by Hewlett Packard (MICHALAK et al., 2005) reporting frequent crashes of their supercomputer at the Los Alamos Neutron Science Center. A recent large-scale study on the field conducted on Google's server fleet over a period of nearly 2.5 years also observed error rates orders of magnitude higher than previously reported in laboratory conditions (SCHROEDER; PINHEIRO; WEBER, 2011).

#### 2.1 Sources of Faults

Electric charge disturbance is the cause of faults in silicon. This charge disturbance may alter the data state of memory structures or generate an impulse in the logic circuit that will be captured by a memory structure. If the fault affects the operation or

results of the device, it is termed error. Otherwise, the fault was masked. If the device is permanently damaged, the error will be termed hard. If the error is transient, the error is termed soft. The main cause of soft error comes from energetic ions interacting with the silicon and thus generating charge disturbance (ZIEGLER et al., 1996; BAUMANN, 2005).

# 2.1.1 Alpha Particles

Radioactive contaminants in package/solder materials, such as uranium and thorium, generate Alpha particles. External sources of alpha particles are not a problem as these particles penetration range in silicon is less than  $100 \ \mu m$ .

To mitigate soft errors caused by alpha particles, Integrated circuits vendors must provide materials highly purified. To a material be considered Ultra Low Alpha (ULA) impurity must be below about one part per 10 billion. ULA implies emission at or below  $0.002~\alpha/h~cm^2$ . Soft errors induced by alpha particle will probably be less than 20% of the total soft errors if the materials are ULA.

## 2.1.2 Low-Energy Cosmic Rays

One significant cause of ionizing particles comes from the interactions of lowenergy neutrons and boron. Boron is a material that is used intensively in integrated circuits. Low-energy neutrons come from the interaction of cosmic rays with the atmosphere. The residual products of the reaction between low-energy neutrons and boron are alpha particles and lithium recoil, both can induce soft errors.

To mitigate soft errors induced by low-energy neutrons one can simply eliminate boron from the process of fabrication. Moreover, the range of ionized particles from low-energy neutrons (alpha particles and lithium recoil) have a very limited range. Therefore, to mitigate such errors, only the first layers from the silicon should be free of boron materials.

# 2.1.3 High-Energy Cosmic Rays

High-energy particles, especially neutrons, originated from the cosmic rays interactions with the atmosphere, is a significant cause of soft errors. The interaction of neutrons with silicon materials may result in the nucleus breaking into ions that will induce soft errors.

Unlike alpha particles and low-energy cosmic rays, high-energy neutrons cannot be mitigated with high purity materials. Shielding could be a viable option for supercomputers. However, many meters of concrete thickness will be required to reduce the neutron flux sufficiently, increasing the complexity and costs of supercomputers site.

#### 2.2 Radiation Effects in HPC Accelerators

This thesis will focus on soft errors which cause only transient recoverable errors. Hard errors permanently damage the device and are less likely to occur (BAUMANN, 2005). Additionally, expressive research has also been done on hard errors (MEIXNER; SORIN, 2008; POWELL et al., 2009; HONG; KIM, 2015).

Soft errors outcomes are Silent Data Corruption (SDC) and Detectable Uncorrectable Error (DUE); DUEs can be divided into a crash or hang. SDC occurs when the program exit successfully, but the output is incorrect. SDCs cannot be observed by the final user without detection techniques like parity check; Detection techniques may still not be able to detect every SDC. Crash occurs when the program state is changed in such a way that it will exit unsuccessfully, like a division by zero interruption or a segmentation fault exception. Finally, hang occurs when the program enters some infinite loop and are not able to finish at all. For HPC systems, crash and hang can be easily detected by timeout functions and unresponsive machines and will not affect the final output. The affected node of HPC systems can be rebooted, and the task may resume by checkpoint techniques or restart from the beginning. The major problem for HPC systems is, then, SDCs as it cannot be easily observable and can leave the final user with significantly corrupted outputs.

The major architectures used in HPC are accelerators, which are used to get the high performance the applications need. Intel Xeon Phi and GPUs are the two most commonly used accelerators and will be described next. Tianhe-2, the second most powerful supercomputer uses 48,000 Intel Xeon Phi accelerators while Titan, the fifth most power-

ful, uses 18,688 K20x GPUs as accelerators. Details about these architectures are given in the next subsections.

# 2.2.1 NVIDIA Graphics Processing Units

Graphics Processing Units (GPU) started aiming at rendering massively parallel graphics for personal computing. In the personal computing scenario, the probability of radiation-induced errors is low, and the multimedia applications can tolerate some errors (BREUER; GUPTA; MAK, 2004). The massively parallel architecture is also suitable for accelerate scientific applications, and nowadays GPUs are widely used to accelerate different scientific applications providing performance speedups up to 15 times (LEE et al., 2010). Moreover, there are GPUs specifically build to supercomputers. Titan, for example, uses Tesla GPUs (NVIDIA, 2015d) that are built with scientific applications in mind.

#### 2.2.1.1 SIMD Architecture

The nature of image applications, where the same operation must be applied to a large set of pixels, led the GPU to be a SIMD architecture. GPUs can execute hundreds of simultaneous operations.

The GPU is composed of hundreds of simple cores that execute the same flow of instructions on different sets of data. Simple cores are grouped into multiprocessor elements, where the tasks are scheduled. Each core of a multiprocessor executes the same instructions on different sets of data.

The program is structured in blocks of thread that can share data with a fast memory, called shared memory. The threads of each block can also synchronize through barriers. The blocks are scheduled to multiprocessors and execute in this multiprocessors until it finishes. Each multiprocessor can have a certain number of blocks being executed at the same time.

#### 2.2.1.2 Memory and Cache Hierarchy

The memory of GPUs is organized into two levels, the global and shared memory. Global memory is slow but visible for all threads of the GPU. Shared memory is fast and visible only to threads in the same multiprocessor.

For the NVIDIA Kepler architecture, there are also two levels of caches. A unified L2 cache serves all the multiprocessors into the GPU. The L1 cache is private to each multiprocessor and its size is configurable using part of the shared memory. There is also an additional read-only data cache for loading constants. Figure 2.1 shows the memory hierarchy of the Kepler architecture.

Shared L1 Read-Only Data Cache

L2 Cache

DRAM

Figure 2.1: NVIDIA Kepler Memory Hierarchy.

Source: NVIDIA GK110 Whitepaper<sup>1</sup>

# 2.2.1.3 Hardware Scheduler

NVIDIA GPUs hardware thread scheduler is divided into two hierarchical levels providing very fast scheduling with almost no overhead (MAITRE, 2013). The first level, called GigaThread Engine (WITTENBRINK; KILGARIFF; PRABHU, 2011), schedules blocks of threads to SMs. GigaThread provides an immediate blocks assignment to SMs when resources are available (PASSERAT-PALMBACH et al., 2015). The second level schedules warps inside an SM. On Kepler GPUs, each SM has four dual-issue warp schedulers that handle four simultaneous warps issuing two instructions per warp per clock cycle, when possible (NVIDIA, 2015b). The four warp schedulers can handle 64 simultaneous warps of 32 threads or a maximum of 16 blocks.

## 2.2.1.4 Hardware Hardening and Radiation Effects in GPUs

High-End GPUs are protected only by ECC (NVIDIA, 2015d). The ECC implemented in NVIDIA GPUs can detect single and multiple errors, but only correct single

<sup>&</sup>lt;sup>1</sup>Available in: https://www.nvidia.com/content/PDF/kepler/NVIDIA-Kepler-GK110-Architecture-Whitepaper.pdf. Accessed 2016

errors. The resources protected are register files, shared memory, L1 and L2 caches, and main memory. Scheduler and other resources are not protected. The double-bit error detection triggers the device crash by default. ECC can be disabled leaving the device completely unprotected.

Radiation effects in GPUs can affect single or multiple threads. If a shared resource like the cache is corrupted, the radiation-induced error can affect several threads at once. Moreover, multiple bit-flips from a single particle hit can occur affecting more than one resource. The block, thread, or warp scheduler can also be hit with several threads generating SDCs, crashes or hangs. The PCI-e bus driver and hardware functions like ECC can also be hit generating SDCs or crashes. Errors affecting instructions will most likely generate a crash or hang. Therefore, a single particle hit can generate SDCs in several threads at once besides crash or hang if the resource or function executed is critical.

## 2.2.2 Intel Xeon Phi

Intel Xeon Phi is an Intel coprocessor developed to achieve high throughput performance. Xeon Phi aims to compete with GPUs as an accelerator for HPC systems. This architecture is similar to GPUs having many cores, targeting highly parallel applications. However, Xeon Phi features x86 in-order cores with coherent cache, supporting traditional programming models such as pthreads and OpenMP.

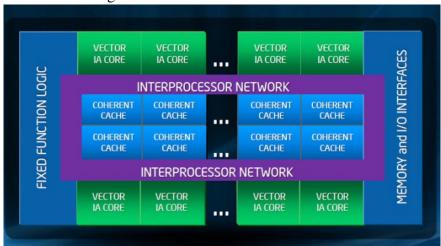

The Xeon Phi architecture is shown in Figure 2.2, it is primarily composed of processing cores, caches, memory controllers, PCIe client logic, and a very high bandwidth, bidirectional ring interconnect. Xeon Phi also supports the Hyper-Threading technology. Each core can execute up to 4 threads simultaneously, hiding memory and multi-cycle instruction latency.

## 2.2.2.1 Vector Processing Unit

Each Xeon Phi core has a Vector Processing Unit (VPU) and features the Intel Initial Many-Core Instructions (IMCI), that is a 512-bit SIMD Instruction set. The VPU can execute up to 16 single precision or 8 double precision operations in a single clock. Fused Multiply-Add instructions are also supported; Hence, it can perform up to 32 single

<sup>&</sup>lt;sup>2</sup>Available in: https://software.intel.com/en-us/articles/intel-xeon-phi-coprocessor-codename-knights-corner. Accessed 2016

Figure 2.2: Intel Xeon Phi Architecture.

Source: Intel X100 Coprocessor Architecture<sup>2</sup>

precision or 16 double precision operations in a single clock.

Transcendental operations such as log and square root can be executed by the VPU as it features an Extended Math Unit (EMU). The EMU unit calculates polynomial approximations of these operations.

## 2.2.2.2 Memory and Cache Hierarchy

Similarly to GPU, Intel Xeon Phi is mounted on a PCIe slot and has a dedicated memory. Therefore, Xeon Phi has a different memory address and communication must be done through message passing.

Two levels of cache are implemented, each core features a single cycle L1 cache divided into 32 KB L1 instruction cache and 32 KB L1 data cache and a 512 KB L2 cache. The second level cache is entirely coherent implementing a directory-based MESI coherence protocol. Xeon Phi also implements prefetch for L1 and L2 caches.

## 2.2.2.3 Hardware Hardening and Radiation Effects in Xeon Phi

The Xeon Phi is equipped with Machine Check Architecture (MCA), which includes various reliability solutions and logging features. Reliability solutions are used to protect memory structures and I/O operations (INTEL, 2015a). MCA covers most of the memory structures available in the Xeon Phi, but the details are intellectual property, and they are not available. MCA can correct single errors and detect some unrecoverable errors. The logging features will provide the system or user routines to react according to the errors, performing checkpoints for instance. MCA unrecoverable error detection

can be disabled to permit continued execution, instead of logging the error and triggering a crash or recovery routine. Error correction cannot be disabled leaving the device unprotected.

SDCs in Xeon Phi could be more contained than GPUs as the resources affected will be used by fewer threads than GPUs. However, errors in L2 cache caused by a single particle hit can also be spread to several threads at once. The scheduler of Xeon Phi should be less sensitive as it is managed by the operating system, with its data residing most of the time in the ECC protected main memory. Crashes and hangs will still occur as an error in critical functions, instruction, and a specific portion of the current application can lead to a crash or hang.

#### **3 RELATED WORK**

In this chapter, we first detail how to measure and evaluate the reliability of HPC applications and devices. We show all the approaches used to collect reliability data and the advantages of each one. Then, we describe the hardening mechanisms available to mitigate faults at hardware and software level. Finally, we detail the applicability of the mitigations mechanisms to HPC devices.

#### 3.1 Reliability Evaluation

Reliability evaluation can be performed using field data providing the most realistic data. Moreover, we can also inject faults at hardware or software level to mimic realistic behaviors or to better understand the reliability issue by collecting additional information. In the following section, we detail the advantages and limitations of each approach.

#### 3.1.1 Field Data

One approach to realistically evaluate the reliability of devices is to collect field data error logs (TIWARI et al., 2015). This approach requires access to supercomputers logs. Then, system error logs such as ECC detection and correction can be parsed and evaluated.

The time one needs to collect statistical relevant data will depend on the size and also the altitude where the supercomputer system is located. The altitude influences the radiation flux which is one of the primary sources of faults described in Section 2.1. The time span one needs to evaluate varies from a couple of months to years.

Field data, however, can only measure detectable errors such as ECC detection and system crash. Silent data corruption cannot be measured since production system cannot afford the time or energy to run the same program twice to compare outputs, or to run a code with a fixed input, without any actual result produced rather than the SDC sensitivity. Thus, there is no viable method to measure silent errors using field data.

# 3.1.2 Fault Injection

Since field data are not easily accessible, and can hardly provide a statistically significant amount of errors, one of the most common approaches to evaluating the reliability of devices or application reliability is to use fault injection. By injecting a fault, it is possible to calculate the Architectural Vulnerability Factor (AVF), which is the probability for corruption to propagate to the output (MUKHERJEE et al., 2003), or the Program Vulnerability Factor (PVF), which is the probability that a fault at the instruction level will affect the program output (SRIDHARAN; KAELI, 2009). If the fault injection can realistically mimic natural phenomena, like radiation beam fault injection, one can accurately measure the error rate a supercomputer is expected to experience.

## 3.1.2.1 Software Fault Injection

Software fault injection can be performed at different levels of abstraction from RTL to software or application level (SAGGESE et al., 2005). As the RTL level descriptions of modern accelerators are not publicly available, RTL injections could be done only on simplified circuits and, thus, may be imprecise or unrealistic (FARAZMAND; UBAL; KAELI, 2012). A higher level software fault injector is also restricted to inject faults into user-accessible resources, like register files, variables, etc. Even if it is hard for software fault injection to mimic realistic error rates and behaviors, hardware fault injections may be unpractical or too expensive. Moreover, software fault injection can provide additional information sometimes impossible to be collected with hardware fault injection, such as fault location and time of insertion.

There are several available software fault injection tools that differ in terms of injection methods and domains of application. Some examples are described below.

**Ferrari** (KANAWATI; KANAWATI; ABRAHAM, 1995) provides an injection mechanism based on software traps that are activated under certain conditions, like accessing a specific memory location or after a timeout. Under these conditions, a trap is activated and a fault is introduced. Ferrari can also make the fault transient or permanent depending on the user's needs.

**FTAPE** (TSAI; IYER, 1995) is capable of inserting faults into memory, registers, and in disk accesses. To achieve fault injection into a disk, FTAPE uses a special disk driver. Then, the data being read or written can be corrupted and delivered to the application.

SASSIFI (HARI et al., 2015) is a tool designed by NVIDIA that enables fault injection at micro architectural level on GPUs. This toll is particularly useful as GPUs are essential to many HPC and safety-critical applications. An interesting example of the latter is reliability analysis of self-driving cars. SASSIFI implements fault injection by using a low-level assembly-language tool called SASSI which profiles the code and injects faults. As SASSIFI is executed on the device, it is fast, introducing an overhead of about 5x the normal execution time.

**GPU-Qin** (FANG et al., 2014) is a fault injection tool whose goal is to obtain information regarding transient faults on GPUs. GPU-Qin provides a fault injection methodology that can achieve representative results even when considering the massive parallelism of applications which can cause simulations to last longer than acceptable simulation time. GPU-Qin is based on the debugger mode in NVIDIA GPUs. Unfortunately, as several host-device synchronizations are required to inject a fault, GPU-Qin's overhead is extremely high (up to 100x the normal execution time).

## 3.1.2.2 Hardware Fault Injection

Hardware fault injection usually requires extra hardware or a facility to mimic some of the events that can cause faults, such as power variation and radiation (HSUEH; TSAI; IYER, 1997). Thus, the effort to inject faults at the hardware level can be much higher, or expensive such as the need for a particle accelerator to induce radiation errors.

Methods with contact to the device attach hardware directly to the device under test to insert current or produce electrical disturbance. This method can more precisely control the place and time of fault injection. Contact methods can also mimic well permanent failures like stuck-at failures that force a permanent value in a specific place of the circuitry.

Ionizing radiation (e.g., heavy-ion or neutron beam radiation) and laser tests do not require contact, and some radiation tests mimic natural physical phenomena. Thus, such methods are the most realistic fault injection to measure error rate. However, we cannot control a specific place and time to inject a fault.

Module Voter

Module

Figure 3.1: Triple Modular Redundancy.

Source: The Author

# 3.2 Hardening Strategies

Several hardening techniques may be applied both at hardware and software level to increase the reliability of a system. Hardware hardening includes, for instance, the enlarging of transistor capacitance, hardened memory cells, or the implementation of Triple Modular Redundancy (TMR) that typically require costly layout or architecture modifications (ZIEGLER; PUCHNER, 2004). Software hardening includes repeated code execution, either at the compiler-level or through binary code instrumentation (ZHANG et al., 2012), checkpoints, and checksum calculation (MITRA, 2012). The scope of this work is to use Commercial off-the-shelf (COTS) devices. Techniques that can only be implemented at hardware level will not be detailed.

#### 3.2.1 Modular Redundancy

The modular redundancy is the most well-known technique to improve the reliability of hardware or software system. Modular redundancy was first envisioned by Von Neumann (NEUMANN, 1956). The most common implementation of modular redundancy is called Triple Modular Redundancy and can be illustrated by the Figure 3.1. The boxes are identical modules that can be a memory cell, logic circuit, a complete system, or any replicated module. The circle is called the majority voting circuit; This circuit takes as input the output of each replicated module and the output is the majority voter. Therefore, if one of the modules produces faulty outputs, the voter will forward the output of the other two modules masking the faulty module output.

TMR is a technique that can detect faults and mask them. Because there are more than two modules, if an error occurs, the majority voter can still be considered correct. With error masking, TMR can perform a continuous operation as the fault module output

will not be propagated and the execution will safely continue. When there are only two modules, the system is called Self-Checking Pair (SCP). It is not possible to perform a continuous operation using SCP systems, and this configuration can only detect if a fault occurs if the outputs of the identical modules do not match. When faults are detected in SCP systems, it can trigger the full re-execution, a smarter rollback strategy, or any defined error treatment strategy.

Modular redundancy was studied with the simultaneous multithreading chips leading to ideas such as partial redundant multithreading (PARASHAR; SIVASUBRAMANIAM; GURUMURTHI, 2006; MUKHERJEE; KONTZ; REINHARDT, 2002). The main idea of partial redundant multithreading is to efficiently use hardware resources and reuse data to improve performance. The key principle is to define a sphere of replication where faults in the leading or trailing thread will be detected.

The strategy proposed by Mukherjee in (MUKHERJEE; KONTZ; REINHARDT, 2002) is to set the largest possible sphere of replication including processor pipeline and register files, but not replicating L1 data and instructions caches. The hardware is modified to delay the trailing thread so that cache misses for the leading thread will be fetched before the trailing thread executes the load. Another optimization is to eliminate control flow misprediction by using the result of the leading thread branches. Additionally, Slice-based threading and value and control flow locality optimizations were included in (PARASHAR; SIVASUBRAMANIAM; GURUMURTHI, 2006) to further improve the performance.

## 3.2.2 Control Flow Checking by Signature Monitoring

Signature-monitoring techniques have been proposed to detect control flow errors. The main idea is to assign signatures to all Basic Blocks of the code. The signatures can be assigned arbitrarily or derived from some characteristics such as binary code or instructions addresses. During program execution, runtime signatures are generated and checked against precomputed signatures to check control flow errors. The signatures can be computed using the current and previous Basic Blocks characteristics. The scheme used to generate signatures will determine which control flow error it can detect, such as an illegal branch or branching in the middle of the Basic Block.

Many techniques propose the use of dedicated hardware to generate runtime signatures and compare to the ones calculated at compile time. Dedicated hardware is used

for: Continuous Signature Monitoring (CSM) (WILKEN; SHEN, 1991), On-line Signature Learning and Checking (OSLC) (MADEIRA; SILVA, 1992), and Implicit Signature Checking (ISC) (OHLSSON; RIMEN, 1995). Many approaches use software-only techniques to be able to use COTS hardware, such as Block Signature Self-Checking (BSSC) (MIREMADI et al., 1992), Control Flow Checking by Software Signatures (CFCSS) (OH; SHIRVANI; MCCLUSKEY, 2002a), and the Concurrent Control Flow Checking approach in (YAU; CHEN, 1980)

CFCSS were evaluated in (GOLOUBEVA et al., 2003), the memory and performance overhead range from 107% to 338% for a Sparc V8 microprocessor. The fault injection was performed inserting bit-flips only in immediate operands of the branch instructions. For the fifth order elliptical wave filter benchmarks, CFCSS increase the percentage of incorrect results. In general, CFCSS reduced the percentage of incorrect results by 7% to 86%.

# 3.2.3 Control Flow Checking Using Assertions

Control Flow Checking Using Assertions (CCA) divides the instructions into sets of Branch Free Intervals (BFIs), each BFIs then has two identifiers. The Branch Free Interval Identifier (BID) is unique for each BFIs; BIDs are set to a variable at the entry-point of the BFI and checked at the end of BFI. If the BID does not match, the BFI starts at a different point than the entry-point and a control-flow error is detected. Control Flow Identifier (CFID) is the second identifier and is the same among the BFIs that share the same parent BFI. CFID is checked to ensure the correct sequence of BFIs. The CFIDs are stored in a queue of size two. The CFID of the next BFI is enqueued at the beginning of the BFI. A CFID is dequeued at the end of BFI and checked against the CFID of the current BFI. If the program attempts to enqueue in a full queue, dequeues an empty queue or fails the CFID check, an error is detected.

The main problems of CCA are the high overhead and the additional branches inserted by the technique, which remains vulnerable to control flow errors. To solve the high overhead, Enhanced Control-flow Checking Using Assertions (ECCA) (ALKHALIFA et al., 1999) divides the code into blocks, which can be a collection of BFIs where there are only one entry point and one exit point. By tuning the size of the block, ECCA can reduce the number of assertions inserted in the protected code. To solve the additional control flow instructions, ECCA uses a scheme with prime number defined at preprocessing time

and one variable assignment at runtime. The assignment is devised in such a way that if a control flow occurs a division by zero will also occur, raising then the division by zero exception. The scheme can also identify if the division by zero occurred because of control flow error or a data divided by zero.

ECCA is unable to detect control flow errors that remain in the same Basic Block. Yet Another Control-Flow Checking using Assertions (YACCA) (GOLOUBEVA et al., 2003) improves the error detection capability by using signature monitoring technique. YACCA generates the signatures at compile and runtime to use in the assertions. Additionally, YACCA inserts a rule in the assertions to detect faults in the decision operand of a conditional branch.

Results in (GOLOUBEVA et al., 2003) showed a memory and performance overhead ranging from 107% to 630%. The fault injection model used inserts random bit-flips in the immediate operands of the branch instructions. The unhardened version of the codes showed correct results for 49% to 56% of the faults injected. A maximum of 25% of the faults generates incorrect results in the fault injecting campaign. When ECCA and YACCA are applied, a maximum of 4% and 1% of the faults produce incorrect results respectively.

## 3.2.4 Error Detection by Duplicated Instruction

The main goal of Error Detection by Duplicated Instruction (EDDI) is to detect errors introduced in the systems (OH; SHIRVANI; MCCLUSKEY, 2002b). The idea is to include duplicated instructions into the code. The original instructions are called Master Instructions (MI), and the duplicated ones are Shadow Instructions (SI). The general purpose registers, as well as memory, are also duplicated for the use of MI and SI. Comparison Instructions (CI) are also included to compare registers and memory values from both partitions, original and duplicated, to detect an error. If a mismatch is detected by CIs, an error handling function will be invoked.

Consider the following instruction:

ADD R3, R1, R2 ; R3

$$\leftarrow$$

R1 + R2

The code will then be transformed in the following MI, SI, and CI:

The register R1, R2, and R3 are the master registers while R21, R22, and R23 are the shadow ones. As the values of master and shadow registers should be the same, the

ADD R3, R1, R2 ; MI ADD R23, R21, R22 ; SI BNE R3, R23, gotoError ; CI

result stored in R3 and R23 should also be the same. Therefore, the CI is inserted using a conditional branch to compare the values of R3 and R23.

The overhead of SI and CIs can be lowered as the results that need to be checked are only the ones before store instructions or conditional branches. Therefore, CIs will only be inserted after the end of blocks of computation; the authors call such blocks as Storeless Basic Block (SBB). Each SBB is a store and branch-free sequence of instructions; then a CI is inserted before the store or branch instruction at the end of each SBB.

The results in (OH; SHIRVANI; MCCLUSKEY, 2002b) show a performance overhead ranging from 13% to 111% for the eight benchmarks executed in a 4-way superscalar R10000 MIPS processor. Without the EDDI protection, 30% to 60% of the faults injected did not produce incorrect results. The high percentage of correct results despite the faults inserted is because the value corrupted was masked or never used. Moreover, from 6% to 38% of the faults injected produced incorrect results without EDDI. Using EDDI, only a maximum of 2% for the benchmarks tested produced incorrect results.

#### 3.2.5 Error Detection and Correction

Error Detection and Correction (EDAC) (LABEL et al., 1996) can be used to detect and even correct a limited number of bit-flips in a sequence of binary data. The first example of an EDAC method is the parity check bit. The parity check is a detect only method where the idea is to simply count the number of logic ones in the binary data. Then, the extra parity bit is set to indicate if there is an odd or even number of logic ones. This parity check technique can detect if there were an odd number of bit-flips, but is unable to detect an even number of bit-flips.

Hamming code is another technique that can detect single or two bit-flips and can correct single bit-flips (MOON, 2005). A simple Hamming code inserts r redundancy bits to n data bits such that  $2^r \ge n + r + 1$ . For example, it needs 7 bits to protect 64 bits of data. The redundant bits are then positioned inside the data bit word in a  $2^n$  bit pattern. For example, for a 7-bit word with four redundant bit, the positions of redundant bits are 1, 2, 4, and 8. The final word can be defined as PPBPBBBPBBB where B is data bit, and P is parity bit. If only a single bit-flip occurred, the error pattern of parity bits could

be used to identify the erroneous bit position and corrected it.

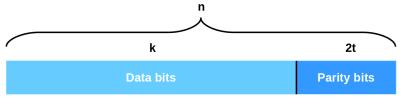

Another EDAC method is called Reed-Solomon (R-S) coding (WICKER, 1994). This R-S method can detect and correct multiple and consecutive bit-flips. R-S is constructed by using k data symbols of s bits each. With 2t parity symbols, the final codeword will consist of n data symbols such that n = k + 2t. The example is depicted in the Figure 3.2.

Figure 3.2: Reed-Solomon codeword.

Source: The Author

Decoding the codeword using finite field arithmetic, R-S can detect 2t erroneous symbols and correct t erroneous symbols. One common example of R-S is the examples called (255,233) where n=255, k=223, and the symbols are 8-bit size, then, 2t=36 and t=16. For (255,233), R-S can correct 16 8-bit erroneous symbols, each symbol can have one erroneous bit or all of them.

#### **3.2.6 SWIFT**

Software Implemented Fault Tolerance (SWIFT) (REIS et al., 2005b) is a technique which applies compiler transformations to duplicate instructions and insert comparisons at code generation. Basically, the idea is to use EDDI, ECC, and Control Flow Checking techniques in conjunction and apply some optimizations. SWIFT is a software-based technique that requires main memory to be hardware protected by ECC, then, it cannot be applied to any system.

The first optimization comes from the conjunction use of EDDI and main memory with ECC protection. Considering the main memory protected, EDDI duplicates only values outside of the main memory. Then, using EDDI and ECC will reduce the number of load and store instructions by half, improving performance. The memory footprint will also be reduced, as the main memory will not be duplicated.

SWIFT insert Control Flow Check as EDDI will detect data errors, but control flow errors can still occur. Another optimization is that control flow correctness can be checked only in Basic Blocks that have store instructions. The erroneous value will only

leave the sphere of replication, and cannot be detected afterward when store instructions are executed. SWIFT, then, update the signature in all Basic Blocks but checks only in Basic Blocks with a store. This late check reduces the number of instructions and increases the performance while the fault detection will remain the same.

There are two main point-of-failures in this approach. The first one is when the data is corrupted between the value validation and store instruction. If the data value or address is corrupted when the store is executed, the error will not be detected. The second one is when the opcode of instruction is changed to a store, this store will be executed without validation and can corrupt values out of the sphere of replication.

Fault injection was performed using PIN to modify register values in (REIS et al., 2005b). Unprotected code finished 15% of executions with an error while SWIFT had no finished executions with error, detecting 70% of the faults. 63% of the executions finished successfully for the unprotected code, and 18% for the SWIFT protected code. The high number of successful execution of unprotected code is because most of the faults were masked, not affecting the final output. The low number of correct executions for SWIFT is because unharming faults, that not affect the final output, is detected nevertheless and the execution is marked as faulty. The rest of the executions crashed with a segmentation fault error.

# 3.2.7 Checkpoint and Rollback

The checkpoint is a common strategy used from large scale to reliable systems (MITRA, 2012; NAKSINEHABOON et al., 2008; EGWUTUOHA et al., 2013; BAUTISTA-GOMEZ et al., 2011; MARUYAMA; NUKADA; MATSUOKA, 2010). The main idea is to save the program state to a safe memory, creating checkpoints of correctly known states. When an error is detected, a rollback strategy is then applied to return the program to a correct state and resume the execution from there. This technique can be applied to recover from crashes and easily detected errors. However, if some fault detection mechanism is available, checkpoint and rollback can also be applied to recover from faults that could generate incorrect results and would otherwise be assumed to be correct.

The main drawbacks of the checkpoint are the memory overhead, used to save the program state, and the performance overhead as the program needs to be paused during the checkpoint creation. To better use this strategy, the user needs to evaluate the error frequency to define the best checkpoint interval.

# 3.2.8 Algorithm Specific Techniques for Fault Tolerance

Algorithms resilient to silent faults have been developed so far in a variety of clean but often unrealistic models. Among others, we remind: the liar model (PELC, 2002) which assumes transient comparator failures but no corruption of data, the models for the design of resilient data structures residing in large and unreliable memories in a checking scenario (BLUM et al., 1994; CHU; KANNAN; MCGREGOR, 2007) and in a recovery setting (AUMANN; BENDER, 1996), the adversarial faulty-RAM model (FINOCCHI; ITALIANO, 2008), where a malicious adversary can arbitrarily corrupt at any time a fixed number of memory cells. In particular, many resilient solutions for a variety of fundamental algorithmic problems (such as sorting (FINOCCHI; ITALIANO, 2008) and suffix trees (CHRISTIANO; DEMAINE; KISHORE, 2011)) have been studied in the faulty-RAM. The connection between fault tolerance and I/O-efficiency has been preliminarily investigated in (BRODAL; JØRGENSEN; MØLHAVE, 2009). Many significant problems are still unsolved in faulty computational models: most notably, no resilient data structures for storing graphs are known in the literature, and even basic graph traversal algorithms are very poorly understood. Algorithm engineering work on resilient algorithms is also in a very early stage, and only a few experimental papers contribute carefully engineered implementations (see, e.g., (FERRARO-PETRILLO; FINOCCHI; ITALIANO, 2009)).

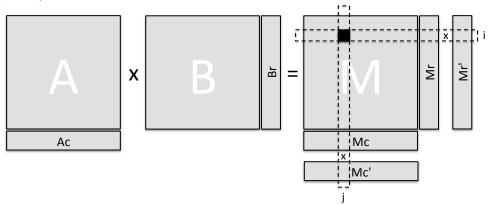

All these works focus on sequential models of computation. However, the work of Abraham in (HUANG; ABRAHAM, 1984; JOU; ABRAHAM, 1988), which is called Algorithm-Based Fault Tolerance (ABFT), can be directly applied to parallel algorithms. For matrix operations, Abraham showed that the checksum of the input matrices, A and B, will preserve some characteristics after certain matrix operations such as multiplication. For example, in a matrix multiplication where  $M = A \times B$ , transforming the input matrices A and B to include the checksums of each column and row respectively, we can use these values in the resulting M matrix to detect and correct some errors. This matrix transformation is depicted in the Figure 3.3. The Fast Fourier Transform can be hardened in a similar way as demonstrated in (JOU; ABRAHAM, 1988).

$\sum \left\{ \begin{array}{c} A \\ A \end{array} \right\} X \qquad B \qquad \left\{ \begin{array}{c} A \\ B \end{array} \right\} = M \qquad \left\{ \begin{array}{c} A \\ B \end{array} \right\} = \left\{ \begin{array}{c} A \\ Col-check \end{array} \right\}$

Figure 3.3: ABFT Matrix Multiplication Scheme.

Source: (RECH et al., 2013a)

# 3.2.9 Hardening Techniques Applicability to HPC Devices

The techniques presented in the previous subsections are among the best options to include in HPC devices as software-based technique. There are some variations of the techniques which were not described here, but the key ideas presented in the techniques here are sufficient to give an overall good insight on how to improve the resilience of HPC devices.

Modular redundancy can be used to achieve high levels of reliability. However, modular redundancy can substantially increase the costs and complexity of the design at the hardware level. Software modular redundancy can be easily implemented eliminating the hardware cost and complexity, but the execution time overhead will significantly increase. However, limiting the sphere of replication, duplicating only a few portions of the code can be a good strategy if the code portions are wisely chosen. Later in section 8.1.3, we show the results of software modular replication applied in HPC devices.

EDDI technique is very similar to modular replication. One of the benefits of using this instead of modular replication would be to lower the scheduling stress, which can be beneficial if the architecture has a sensitive scheduler, as is the case of GPUs (RECH et al., 2013b). However, Modular redundancy and EDDI cannot be indiscriminately applied as the performance overhead rapidly increases resulting in poor performance, which can be unacceptable to HPC.

Control flow checking can be used to detect errors faster than other techniques, such as modular replication, that would wait for the entire execution to finish and check the outputs. Therefore, control flow check could speed up the recovery time from faults. However, this technique will not suffice if the scientific applications are mainly data flow, and many of the scientific applications are engineered to be mainly data flow as the devices are designed to be more efficient this way. The nature of HPC applications that executes

in an accelerator, then, limits the gain that could be obtained by control flow strategies.

EDAC techniques can be efficiently implemented in HPC devices (CURRY et al., 2008). Software-based implementation can be used to verify the consistency of data produced by an application. However, the main drawback would be to change the algorithm to use the extra bits necessary to check and correct the output data. EDAC, then, could lead to increased costs and time to write a scientific application with performance overhead and resilience gains that can vary widely according to the specific EDAC used.

The checkpoint technique may face problems such as different memory address space from HPC accelerators and host server. Another issue is the cost to copy the memory back to accelerators and restart the application, inserting an extra overhead. However, this technique can also be applied, and some accelerator like Xeon Phi already implement some checkpoint (INTEL, 2015a) that can be used.

SWIFT technique introduces the idea to bring together techniques to best suit the hardware and software. SWIFT also presents the idea to harden only portions of the code to lower the overhead. The results were expressive, and HPC devices could benefit from such approach.

Algorithm specific fault tolerance techniques can yield great results, even when using COTS hardware. This work will not focus on a specific algorithm or class of algorithms, but in a more general way to improve the resilience of several applications. However, well known and well used algorithms, like matrix operations, are used inside bigger applications and the ABFT hardening can still be used to improve the overall resilience of such applications.

The available hardening techniques can then be applied to HPC devices with particular advantages for the algorithm and hardware used. Therefore, well understanding the device and algorithm, we can match the best hardening techniques or some variation of them to produce the best results for HPC applications and devices.

## **4 RELIABILITY ANALYSIS**

In this section, a reliability analysis using radiation experiments for a representative set of parallel algorithms for HPC applications is presented. Usually, when performing radiation experiments, the error propagation observability is limited in a way that is not possible to identify the source of the observed failure unequivocally. As a result, the evaluation may be limited to the tested configuration and be hardly generalizable. The aim is to go a step further with the experiments by selecting a broad set of applications and configurations that cover a wide range of computational and data movement requirements.

## 4.1 Methodology

The natural flux of heavy ions that wanders in the deep space, protons that surround the earth and fast neutrons created by the incidence of cosmic rays on the earth's atmosphere can be simulated through the use of particle accelerator facilities. Such facilities attempt to mimic the energy spectrum of particles, but with a flux that is millions of times greater than the terrestrial one, one hour of a test at these facilities represents many hundreds of years of natural exposure. This accelerated flux, in turn, allows performing extensive testing to assess the sensitivity of electronic devices to radiation.

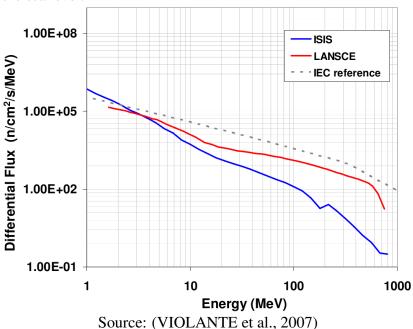

The radiation experiments presented in this work were performed at the Los Alamos National Laboratory (LANL) Los Alamos Neutron Science Center (LANSCE) Irradiation of Chips and Electronics House II, and at the VESUVIO beam line in ISIS, Rutherford Appleton Laboratories, Didcot, UK. Figure 4.1 shows that LANSCE and ISIS provide a white neutron source that emulates the energy spectrum of the atmospheric neutron flux from 10 to 750 MeV. Moreover, the beam at ISIS and LANSCE was empirically demonstrated to mimic the terrestrial radiation environment (VIOLANTE et al., 2007).

The neutron flux used in both facilities was higher than the neutron flux at sea level (JEDEC, 2006). However, it is important to notice that is very unlikely to have more than one neutron hit inducing an error per execution in normal condition, then, we carefully designed the experiments to make sure that the probability of more than one neutron generating a failure is negligible. The observed error rates were lower than  $10^{-2}$  errors/execution.

The beam was focused on a spot with a diameter of 2 inches, which provided uniform irradiation of the device chip without directly affecting nearby board power control

Figure 4.1: LANSCE and ISIS neutrons spectra plotted against the reference of neutrons spectrum at the sea level.

circuitry and DRAM chips. The beam focus implies that data stored in the main memory is not corrupted, allowing an analysis focused on just the device cores. Actually, having the DRAM exposed would have masked most of the device cores behavior under radiation that was intended to highlight. Moreover, DRAM sensitivity to radiation has already been deeply analyzed and proved to decrease with the shrinking of technology nodes (BAU-MANN, 2005), and modern DRAM chips are provided with efficient ECC circuits that increase device reliability by several orders of magnitude (KIM et al., 2007). It is worth noting that such a consideration does not apply to caches, for which technology shrinking, compact design, and performance requirements increase the probability of having failures as well as the efforts and penalties of adding ECC (ASADI et al., 2005).

A host computer initializes the test sending pre-selected input to the accelerator and gathers results, comparing them with a pre-computed golden output. When a mismatched is detected, the execution is marked as affected by a *Silent Data Corruption* (SDC). To avoid precision and round-off issues, golden outputs were calculated on the very same device used for experiments. Input values were ensured to be small enough to avoid overflow but still big enough to be considered representative. Additionally, to avoid biases on input values, small input sizes are a subset of big input sizes and input has been generated balancing the number of 0s and 1s.

Copying memory from the host computer to the devices through the PCIe bus is a very time consuming operation, even longer than the code execution time itself when working with accelerators. During the memory copy, the device is in idle mode and DRAM is not irradiated. Thus, the time spent during memory copy is wasted and should be reduced at the minimum. The input vector is copied from the host to the device DRAM only at the beginning of each run, and those inputs are used for several code executions. Once an error is detected, DRAM content is dumped and checked to ensure input consistency. Observed SDCs were never caused by input errors (DRAM is not irradiated). As SDC rate is relatively low (about one error every  $10^3$  executions), this methodology smooths memory copy overhead and improve the effective device exposure time.

Software and hardware watchdogs were included in the setup. The software watchdog monitors the application under test detecting *DUEs*, i.e., application crashes or control flow errors that prevent the device from completing assigned tasks (e.g., the device enters an infinite loop). The hardware watchdog is an Ethernet controlled switch that performs a power cycle of the host computer if the host computer itself does not acknowledge any ping requests in ten minutes. The hardware watchdog is necessary as radiation can corrupt the PCIe controller on the device board as well, possibly causing the host computer to hang.

## **4.1.1** Metrics to Evaluate Experimental Results

Radiation experiments aim at measuring the *cross section*, which is the sensitive area of the device. i.e., that portion of area that, if hit by an impinging particle, causes an observable failure. When an algorithm is tested, the cross section is measured dividing the observed error rate (errors/s) by the average particle flux ( $particles/(cm^2 \times s)$ ), yielding an area. The larger the cross section, the higher the use of sensitive resources (BAU-MANN, 2005; MUKHERJEE et al., 2003). So, the cross section depends on the overall amount of resources required for computation and on their criticality, but does not include any information on execution time. As ISIS and LANSCE reasonably mimic the atmospheric neutron flux, the probability of having a neutron corrupting the device during our experiments or at sea level during normal operation is very similar (VIOLANTE et al., 2007). The experimentally observed cross section is then an intrinsic characteristic of the device and code, independent on the neutron source. Multiplying the cross section ( $cm^2$ ) with the expected neutron flux on the device  $(13n/(cm^2 \times h))$  at sea level (JEDEC, 2006)), one can estimate the device error rate or Failure In Time (FIT), expressed as  $errors/10^9h$ .

### 4.1.2 Device Under Test

In this chapter, we consider NVIDIA *K20* which was the accelerator used in the Titan supercomputer at Oak Ridge National Laboratory. Titan was the second fastest supercomputer at the time measurements were performed.

Kepler K20 GPUs are designed by NVIDIA in a 28nm technology node (NVIDIA, 2015d). The K20 is composed of 13 SM, each of which is divided into 192 CUDA cores. K20 features a 706MHz SM core clock, 1.25MB L2 cache, a total of 832KB in L1 cache, and a total of 3.25MB of register file storage. Register files, shared-memory, L1 and L2 caches are SECDED protected, read-only data cache is parity protected. The tested devices have CUDA capability 3.5, which allows each SM to execute a warp of up to 192 parallel threads in a single computing cycle. If the block size exceeds 192, the execution of some threads will be delayed until the computation of the preceding warps of the block has been completed. Each SM has two schedulers. At every instruction issue time, the first scheduler issues one instruction for some warp with an odd ID and the second scheduler issues one instruction for those with an even ID, when double-precision floating-point instructions have to be executed, the second scheduler cannot issue any instruction.

The experiments with K20 were conducted with the ECC mechanism disabled. On the NVIDIA GPUs ECC can be disabled using nvidia - smi tool (NVIDIA, 2015d). Performing the experiments with reliability mechanisms enabled would require a large amount of time to gather a statistically significant amount of data. Additionally, while disabling mitigation mechanisms seems unrealistic, disabling them is fundamental to find the raw architectures reliability. ECC, for instance, could mislead SDC and DUE distinction. In fact, when the ECC is disabled, a double bit error may be masked without affecting the code output (WILKENING et al., 2014). The same double bit error will trigger an application DUE when ECC is ON (NVIDIA, 2015d). Later in this thesis, we also evaluate the efficiency and efficacy of ECC in section 8.1.4, we discovered that ECC reduces the SDC rate by about one order of magnitude.

# **4.1.3 Selected Algorithms**

Several benchmark suites are available for performance and efficiency evaluation of computer architectures (BAILEY et al., 1994; WOO et al., 1995; BIENIA et al., 2008; CHE et al., 2009). A standard set of benchmarks for the reliability evaluation of HPC

devices has not been established, yet. General guidelines for reliability evaluation of computing devices suggest to consider codes from different domains and comprising different computation and communication patterns (ASANOVIC et al., 2006; QUINN et al., 2015). Therefore, we selected algorithms representative of different domains and application classes. The algorithms are detailed in the following.

Matrix Transpose is a procedure that copies a complete matrix to another swapping columns and lines element by element. Matrix Transpose is a representative tool for various graphical procedures that do not make any operation on data, but reorders it. Such data transfers are common on matrix rotation and many matrix transformations. The Matrix Transpose workload can also be considered to be similar to sorting algorithms, where elements are not modified but only rearranged.