## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

# FÁBIO LUÍS LIVI RAMOS

# Efficient High-Throughput and Power-Saving Hardware Architectural Design for the HEVC Entropy Encoder

Ph.D. Thesis

Thesis presented as partial requirement for the Ph.D. degree in Computer Science

Advisor: Prof. Dr. Sergio Bampi

Co-Advisor: Prof. Dr. Marcelo Schiavon Porto

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

Ramos, Fábio Luís Livi

Efficient High-Throughput and Power-Saving Hardware Architectural Design the HEVC Entropy Encoder / Fábio Luís Livi Ramos. -- 2019.

187 f.:il.

Orientador: Sergio Bampi;

Co-orientador: Marcelo Schiavon Porto.

Tese (Doutorado) — Universidade Federal do Rio Grande do Sul, Instituto de Informática, Programa de Pós-Graduação em Computação, Porto Alegre, BR — RS, 2019.

1. HEVC. 2. CABAC 3.Binary Arithmetic Encoder 4. Real-time Video Processing 5. Power-saving Hardware Design. I. Bampi, Sergio, orient. II. Porto, Marcelo Schiavon, coorient. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitor: Prof <sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Gianetti Loureiro Chaves Diretor do Instituto de Informática: Prof <sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PPGC: Prof a. Luciana Salete Buriol

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

There are places I'll remember

All my life, though some have changed

Some forever, not for better

Some have gone, and some remain

All these places had their moments

With lovers and friends, I still can recall

Some are dead, and some are living

In my life, I've loved them all

John Lennon

Stop you're trying to bruise my mind I can do it on my own

Stop you're trying to kill my time

It's been my death since I was born

I don't remember half the time

If I'm hiding or I'm lost

But I'm on my way, on my way

Chris Cornell

Toda vez que falta luz Toda a vez que algo nos falta O invisível nos salta aos olhos Um salto no escuro da piscina

Humberto Gessinger

I can't see, the end of me My whole expanse, I cannot see I formulated infinity Stored deep inside me

Curt Kirkwood

#### **AGRADECIMENTOS**

Uma tese de doutorado, apesar de ser, a grosso modo, o trabalho de uma pessoa só, requer uma rede de apoio de pessoas amadas e queridas para dar suporte durante todo o processo. De alguma forma, todas essas pessoas são coautoras desse trabalho, seja no apoio emocional e carinho dados, seja efetivamente em contribuições técnicas para essa tese, seja em ambos.

Primeiramente, as duas pessoas mais importantes na minha vida, que são a minha esposa Betina e meu filho Pedro, os quais são o centro do meu universo, sem sombras de dúvidas. Minha esposa, que é, sem dúvida, minha melhor amiga e companheira, que estamos há mais de uma década juntos aprendendo juntos sobre a vida, e a quem eu amo muito! E meu filho, que fez com que minha percepção sobre o que é o amor e sobre o que é a vida mudar de uma forma como nunca antes, por quem eu tento ser um ser humano melhor, e a quem eu amo muito! Obrigado por todo o amor, carinho, ajuda e incentivo!! Sem vocês dois, nada disso teria sido possível e sem vocês dois também não teria valido a pena!

Meus pais, Gregório e Rosa, e minha irmã, Renata, são parte fundamental de quem eu sou. Os agradeço por terem me dado uma criação digna, respeito, amor, carinho, por sempre terem estado presentes, sempre terem me incentivado no que tange a questão do ensino, e também pelos (merecidos) puxões de orelha. Hoje percebo como sou privilegiado de ter tido uma família como a que tive, o que nem sempre é verdade no mundo que vivemos. Obrigado por tudo, amos vocês!

Meus sogros, Carmo e Leoni, e minha cunhada, Fernanda, que foram como uma segunda família para mim, igualmente sempre me apoiando em tudo desde e época do mestrado, sendo igualmente companheiros e fundamentais em quem eu sou hoje. São pessoas dignas, a quem devo meu reconhecimento e respeito. Obrigado por tudo!

Meu orientador, professor Sergio Bampi, pela sua orientação, apoio e respeito ao longo de todo o processo de doutoramento, além de me ensinar pontos muitos importantes que vão além da questão técnica da orientação. Cabe destacar o seu apoio incomensurável durante o começo do doutoramento onde, por questão burocráticas, quase tive que interromper o curso. Graças a sua ajuda (literalmente comprando briga com algumas pessoas para me apoiar) pude seguir no curso da forma como planejada. Meu reconhecimento e agradecimento ao prof. Bampi!

Meus co-orientadores Marcelo Porto (oficialmente) e Bruno Zatt (não oficialmente) por todo o apoio, aconselhamento e, por último, mas não menos, pela amizade. Os agradeço

profundamente por toda ajuda que me deram ao longo do doutoramento, os eventos durante minhas estadias em Pelotas, e pela parceria e amizade desde a época da graduação/mestrado. As suas orientações, sem dúvida, facilitaram as decisões sobre os caminhos a seguir ao longo do doutoramento! Muito obrigado, gurizada!!

A gurizada de "Imbé", cuja a amizade vem desde a nossa época da graduação na Engenharia de Computação, especialmente: irmãos Zatt (Bruno e Gordo), Osvaldo, Kunz, Giancarlo, gêmeos (Artur e Guilherme), Nondillo e Jonas. Agradeço pela parceria e amizade. Uma pena não podermos nos ver mais tanto quanto antes, visto que cada um mora em uma parte do mundo, mas o elo e amizade continuam firmes e fortes!! Não vejo a hora de podermos nos reunir novamente em Imbé ou onde quer que seja!

A gurizada do CEITEC, onde trabalhei por quase cinco anos, e onde formamos um círculo forte de amizade e respeito: Wagston, Hervé, João, Fred, Ferrão, Rohde, Rubinei, Marcelo, Zé, Lauro, Garibotti, Cyrille e Jana. Fico no aguardo para nosso próximo churrasco de confraternização! Além disso, cabe um agradecimento ao Muru e ao Alain, que foram meus gerentes durante o período que lá estive, e foram líderes dignos e justos.

Também cabe meu agradecimento aos meus alunos da Unipampa, especialmente meus orientados, e mais especialmente a Camila, a Luana, e o Alessandro, cujos TCCs estiveram envolvidos no escopo dessa tese.

Um reconhecimento especial ao pessoal da época do colégio militar, da época do curso de Engenharia de Computação na UFRGS, da época da Datacom, e também da época do mestrado no Laboratório 215, assim como a alguns colegas professores da Unipampa. Muitos eu acabei perdendo o contato, mas ainda tenho carinho e reconhecimento a todos.

Devo também um agradecimento a algumas pessoas e entidades, seja por elas serem identitárias a meu respeito, seja por fazerem parte da minha vida de forma intrínseca: as bandas Soundgarden, Beatles, Engenheiros do Hawaii, Alice in Chains, Nirvana, Kyuss, Meat Puppets, Helmet, Raimundos, QOTSA, Pixies, Ween, Faith No More, Red Hot Chili Peppers, Led Zeppelin, Black Sabbath, Silverchair, Foo Fighters, Pearl Jam, Pantera, Rammstein, Offspring, Weezer, para citar as mais importantes. Aos artistas Van Gogh, Raul Seixas, Noel Guarany, Cenair Maicá, Júpiter Maçã, Bert Jansch, Jackson C. Frank, os comediantes do Chaves e do Hermes e Renato. Ao filme Clube da Luta e aos dois primeiros filmes do Predador e Alien. Às universidades UFRGS, Unipampa e UFpel. Às cidades de Porto Alegre, Santa Cruz do Sul, Imbé, São Borja, Canela e Bagé. Uma menção honrosa às bandas Temple of the Dog, Mad Season, Rage Against the Machine, Green Day, Legião Urbana, Titãs,

Queen, Creedence Clearwater Revival, Stone Temple Pilots, Red Fang, Stoned Jesus, Morphine, Ace of Base, Banzai e Slayer, e ao artista José Mendes e Michael Jackson.

Por fim, dentro da minha atual crença de vida, creio que uma coisa tão complexa como a nossa consciência não suma simplesmente ao morrer. Assim sendo, creio que as coisas podem ter um propósito e espero estar cumprindo, dentro do possível, ao meu. Agradeço por estar vivo, ter saúde, poder trabalhar, estudar, e viver com minha família e amigos momentos bons e ruins, como a vida tem que ser! Sou um privilegiado por tudo!

#### **ABSTRACT**

The advances in digital video processing, such as the new generation of videos resolutions, led to new challenges in order to transmit and storage the related data. In this scenario, realtime digital video processing is an important goal, which requires specific video-processing architectures to accomplish the demanded constraints. Moreover, tethered devices that transmit and receive video draw the attention to power-saving design for these architectures, due to the energy constraints of the battery-based context of these solutions. HEVC (High-Efficiency Video Coding) standard emerges as an alternative to cope with the mentioned situations involving digital video processing. In HEVC, only one entropy-encoding algorithm exists, which is the CABAC (Context-Adaptive Binary Arithmetic Coding). A single highthroughput instance of a hardware CABAC block is a desirable goal in order to save power, area, and coding efficiency. Therefore, the global goal of this research is configurable highthroughput power-efficient single-instance CABAC design, where high-throughput scheme along with power saving techniques are integrated, considering a compromise trade-off between both performance and power/energy dissipation, adapting the architecture according to it. This Thesis focused on the BAE (Binary Arithmetic Encoder) block, which is the processing bottleneck of the CABAC. As a first contribution, a low-power hardware BAE design is presented, where fine-grain insertion of power-saving reduction techniques into different proposed BAE designs, leading to power savings ranging from 10-40% for different BAEs architectural designs. Towards ultra-high throughput performance, the novel Multiple-Bypass Bins Scheme (MBBS) proposition happens within the context presented, where multiple values of a particular type of BAE data (i.e., bypass bins) are processed at the same time. The integration of the MBBS with prior-art techniques for the BAE blocks led to an increase of around 13% more bins/s compared to the highest prior-BAE design found in the literature. Additionally, an efficient BAE design with MBBS is proposed, achieving closely related throughput values compared to the highest performance of prior-art design, at the advantage of using smaller and easier-to-scale design. This latter design was used as the baseline of the final contribution of this Thesis, combining the power-saving approach and MBBS propositions: a configurable BAE design, which can configure itself to accomplish a better trade-off in terms of performance and energy dissipation through the video processing.

**Keywords**: HEVC. CABAC. Binary Arithmetic Encoder (BAE). Multiple-Bypass Bins Processing. Low-power CMOS Design. Configurable Design.

# Design em Hardware Arquitetural Eficiente para Alta-Vazão e Economia de Potência para o Codificador de Entropia HEVC

#### **RESUMO**

Os avanços no processamento digital de vídeos, geraram novos desafios para transmitir e armazenar os dados relacionados. Nesse cenário, o processamento de vídeo em tempo real requer arquiteturas específicas para se alcançar as demandas relacionadas. Ademais, dispositivos móveis que transmitem e recebem vídeo necessitam de projetos visando eficiência energética, devido às restrições do uso de bateria nesse contexto. O padrão HEVC (High-Efficiency Video Coding) é uma alternativa para lidar com as situações apresentadas, onde apenas um algoritmo de codificação de entropia existe, que é o CABAC (Context-Adaptive Binary Arithmetic Coding). Uma única instância de um bloco em hardware do CABAC é desejável para economizar potência, área, e manter a eficiência de codificação. Portanto, o objetivo global dessa pesquisa é um projeto configurável de alta-vazão e eficiente energeticamente em uma única instância do bloco CABAC, onde técnicas para alta-vazão junto de técnicas para redução do consumo de potência são integradas, adaptando a arquitetura de acordo com isso. Essa tese focou no bloco BAE (Binary Arithmetic Encoder), pois esta etapa é o gargalo em termos de processamento do CABAC. Uma primeira contribuição é a inserção de técnicas em baixo nível para redução do consumo de potência em diferentes projetos do bloco BAE. O uso das técnicas escolhidas gerou economia de potência variando entre 10% a 40%. Em buscas de ultra-alta-performance, ocorreu a proposta para processamento de múltiplos bins bypass (MBBS), onde múltiplos valores de um tipo especifico de dados (i.e., bypass bins) são processados ao mesmo tempo. A integração do MBBS com técnicas da literatura para o BAE gerou um aumento de vazão na ordem de 13% quando comparado com o trabalho de maior vazão encontrado na literatura. Adicionalmente, uma alternativa eficiente do bloco BAE com MBBS é proposta, alcançando valores muito próximos quando comparada com a solução anterior com maior vazão da literatura, com a vantagem de um projeto menor e com maior escalabilidade. Essa última arquitetura foi utilizada como base para a contribuição final dessa tese, combinando as técnicas low-power e a proposta MBBS: um design BAE configurável, que consegue se modificar para alcançar um melhor balanceamento em termos de vazão e energia durante o processamento do vídeo.

**Palavras-chave**: HEVC. CABAC. Codificador Aritmético Binário. Processamento de Múltiplos Bins Bypass. Design CMOS de Baixo Consumo. Design Configurável.

# FIGURE LIST

| Figure 1.1 – Main Thesis contributions                                                      | 26 |

|---------------------------------------------------------------------------------------------|----|

| Figure 2.1 – RGB image decomposition                                                        | 28 |

| Figure 2.2 – YCbCr image decomposition                                                      | 28 |

| Figure 2.3 – Sub-sampling examples                                                          |    |

| Figure 2.4 – Example of video sequence decomposition into frames                            | 30 |

| Figure 2.5 – HEVC block diagram                                                             |    |

| Figure 2.6 – Example of CUs division and CU tree structure                                  |    |

| Figure 2.7 – PUs possible divisions                                                         |    |

| Figure 2.8 – ME behavior                                                                    |    |

| Figure 2.9 – Visual example of Transform process in a 4x4 block of residues                 |    |

| Figure 2.10 – Visual example of Quantization process in a 4x4 block of residues             |    |

| Figure 2.11 – Example of SAO Filter application                                             |    |

| Figure 2.12 – Example of Deblocking Filter application                                      |    |

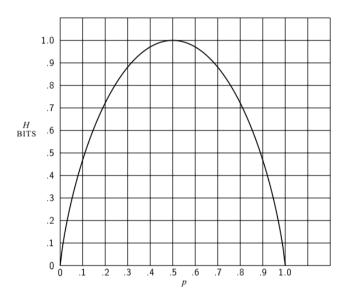

| Figure 2.13 – Function H of (2.2)                                                           |    |

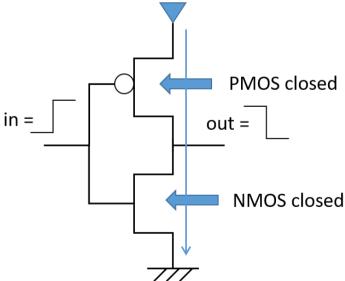

| Figure 2.14 – CMOS inverter organization and behavior                                       |    |

| Figure 2.15 – CMOS switching consumption on inverter                                        |    |

| Figure 2.16 – CMOS short-circuit consumption on inverter                                    |    |

| Figure 2.17 – Clock-gating technique                                                        |    |

| Figure 2.18 – Operand Isolation technique                                                   |    |

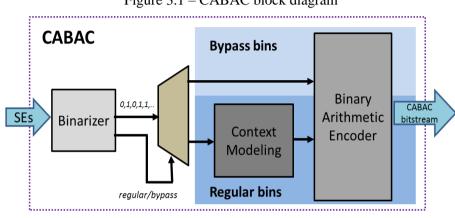

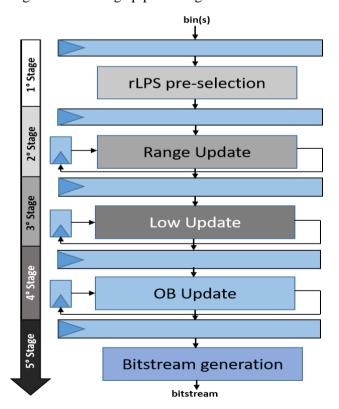

| Figure 3.1 – CABAC block diagram                                                            |    |

| Figure 3.2 – Example of Range and Low update                                                |    |

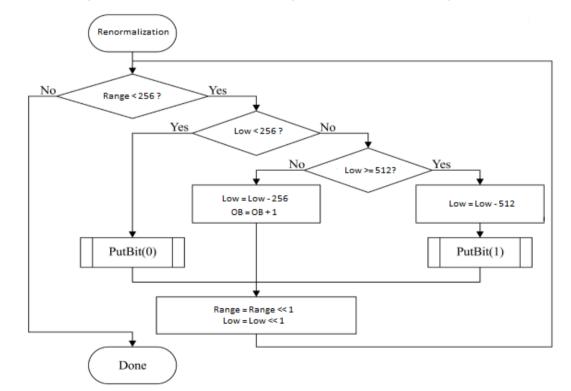

| Figure 3.3 – Renormalization of Range and Low variable for regular bins                     |    |

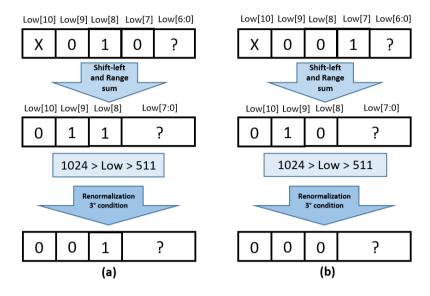

| Figure 3.4 – Low renormalization for bypass bins                                            |    |

| Figure 3.5 – Bitstream PutBit(B)generation function                                         |    |

| Figure 3.6 – One-round bitstream generation pseudo-code for regular bins                    |    |

| Figure 3.7 – HPC technique depiction                                                        |    |

| Figure 3.8 – LH rLPS technique depiction                                                    |    |

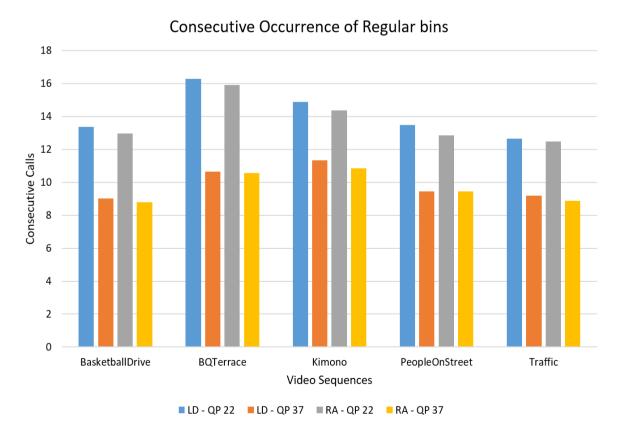

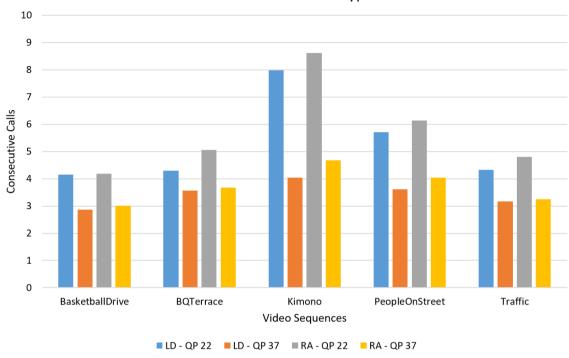

| Figure 4.1 – Consecutive occurrence of regular bins for test video sequences                |    |

| Figure 4.2 – Consecutive occurrence of bypass bins for test video sequences                 |    |

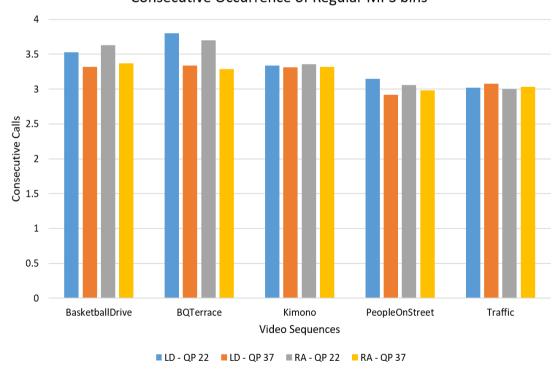

| Figure 4.3 – Consecutive occurrence of regular MPS bins for test video sequences            |    |

| Figure 4.4 – Consecutive occurrence of regular LPS bins for test video sequences            |    |

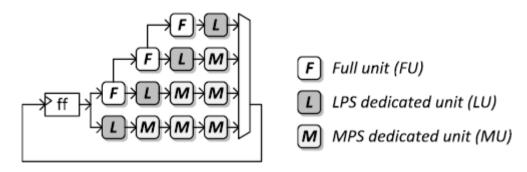

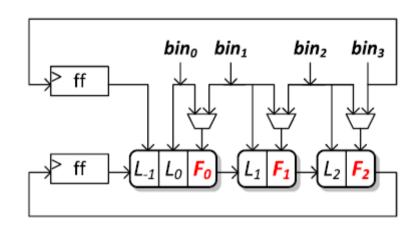

| Figure 4.5 – Four-BAE core structure                                                        |    |

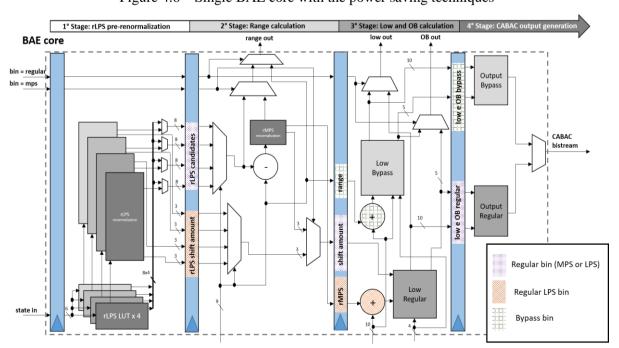

| Figure 4.6 – Single BAE core with the power saving techniques                               |    |

| Figure 5.1 – Pseudo-code for Low renormalization, OB update and bitstream generation for    |    |

| bypass bin                                                                                  |    |

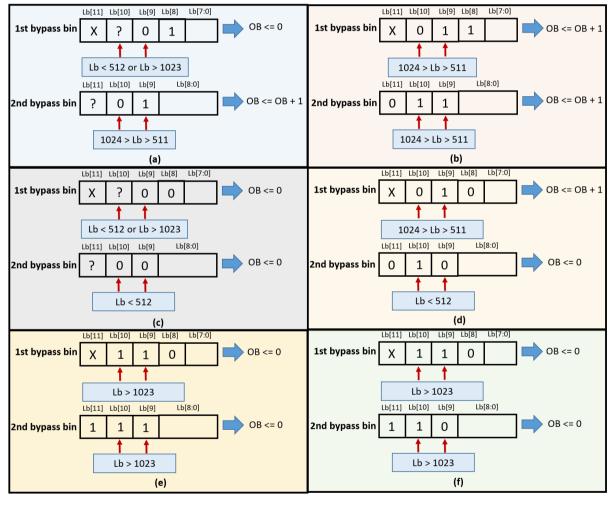

| Figure 5.2 – Low renormalization possibilities when a bypass with value '0' occurs - part   |    |

| Figure 5.3 – Low renormalization possibilities when a bypass with value '0' occurs - part 2 |    |

| Figure 5.4 – Low renormalization possibilities when a bypass with value '1' occurs - part   |    |

| Figure 5.5 – Low renormalization possibilities when a bypass with value '1' occurs - part 2 |    |

| Figure 5.6 – Structure for Low update of the MBBS                                           |    |

| Figure 5.7 – OB update for two consecutive bypass bins                                      |    |

| Figure 5.8 – Pseudo-code for bitstream generation of MBBS for two bypass bins               |    |

| Figure 5.9 – BAE core with MBBS and power-saving techniques                                 |    |

| Figure 6.1 – Regular PIPO address organization                                              |    |

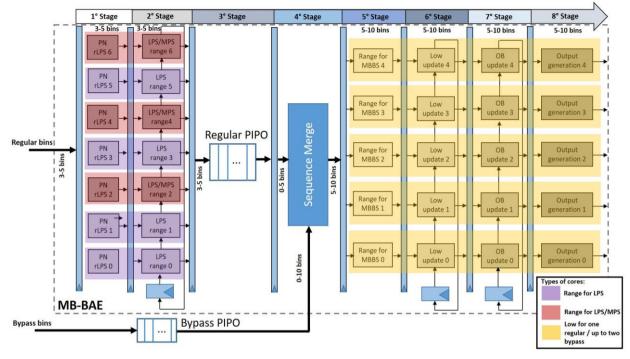

| Figure 6.2 – MB-BAE architecture                                                            |    |

| Figure 6.3 – Bypass PIPO address organization                                               |    |

| Figure 6.4 – RMBB structure for MBBS for up to two bypass bins with value '0'               |    |

|                                                                                             |    |

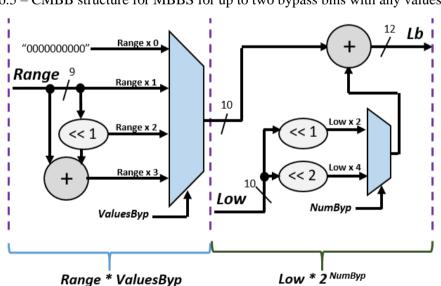

| Figure 6.5 – CMBB structure for MBBS for up to two bypass bins with any values           |       |

|------------------------------------------------------------------------------------------|-------|

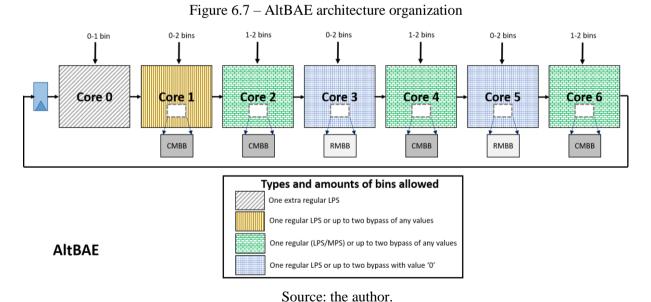

| Figure 6.7 – AltBAE architecture organization                                            |       |

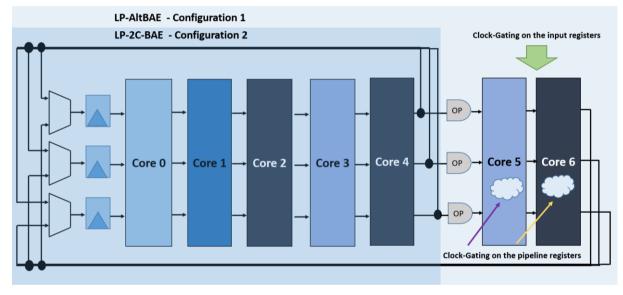

| Figure 7.1 – AltBAE granularity, and the internal 2C-BAE and 1C-BAE                      | . 103 |

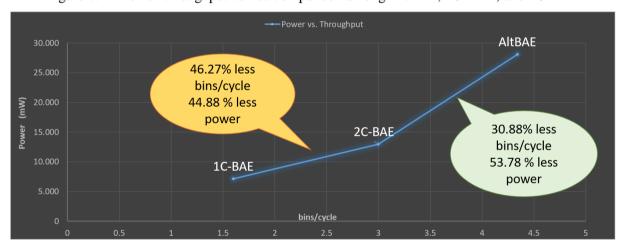

| Figure 7.2 – Power-throughput curves comparison among AltBAE, 2C-BAE, and 1C-BAI         |       |

|                                                                                          |       |

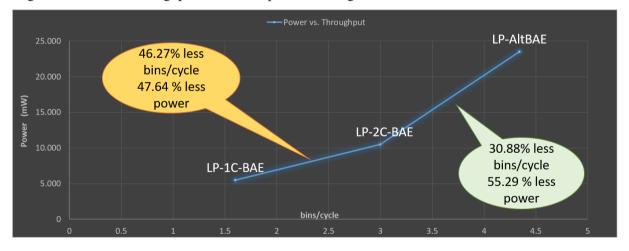

| Figure 7.3 – Power-throughput curves comparison among LP-AltBAE, LP-2C-BAE, and I        |       |

| 1C-BAE                                                                                   |       |

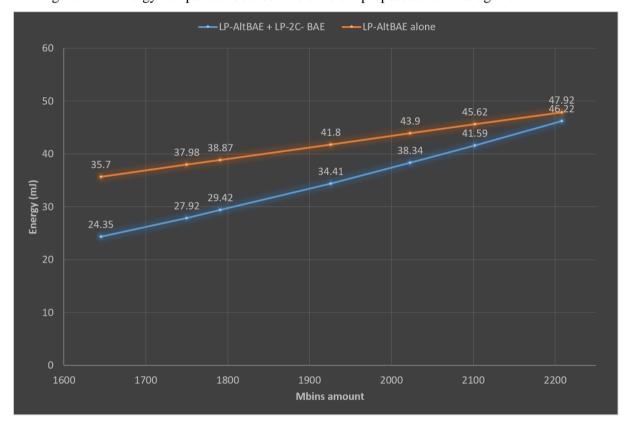

| Figure 7.4 – Energy comparison between the different proposed scenarios against LP-AltI  |       |

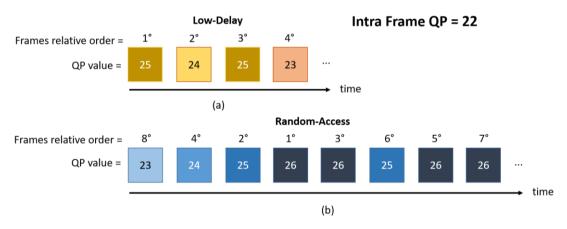

| Figure 7.5 – GoP structure for recommended test video sequences – Intra Frame QP 22      |       |

| Figure 7.6 – GoP structure for recommended test video sequences – Intra Frame QP 37      |       |

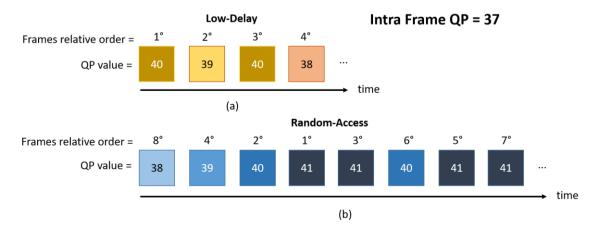

| Figure 7.7 – Example of dynamic methodology for energy-efficient BAE design              |       |

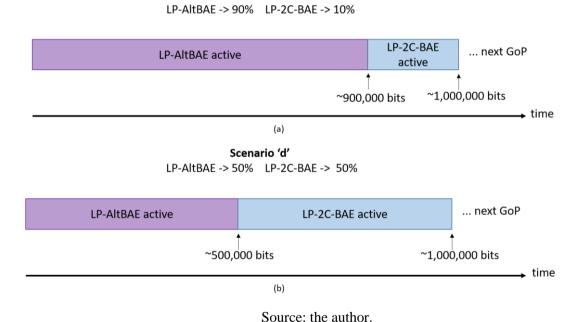

| Figure 7.8 – ET-BAE architecture and configurations                                      |       |

| Figure 7.9 – Energy comparison of ET-BAE against LP-AltBAE                               |       |

| Figure 7.10 – All proposed BAE designs characteristics for power dissipation and through |       |

| proposed 2122 designs enumeration for power dissipation and unough                       | -     |

| Figure A.1 – Total average percentage and average consecutive calls for the PeopleOnStre |       |

| sequence                                                                                 |       |

| Figure A.2 – Total average percentage and average consecutive calls for the BasketballDr |       |

| sequence                                                                                 |       |

| Figure A.3 – Four cores binarizer architecture                                           |       |

| Figure A.4 – Binarizer core architecture                                                 |       |

| Figure A.5 – Operand Isolation insertion on binarization methods                         |       |

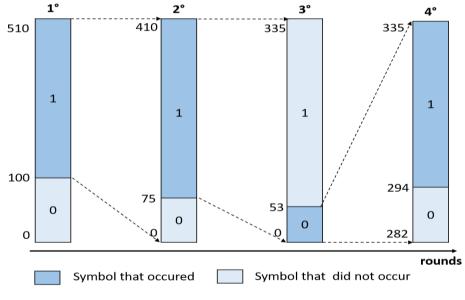

| Figure B.1 – The first example of MBBS description                                       |       |

| Figure B.2 – The second example of MBBS description                                      |       |

| Figure B.3 – The third example of MBBS description                                       |       |

| Figure B.4 – The fourth example of MBBS description                                      |       |

| Figure B.5 – The fifth example of MBBS description                                       |       |

| Figure B.6 – Low renormalization for MBBS                                                |       |

| Figure B.7 – OB update for MBBS                                                          | .153  |

| Figure B.8 – Bitstream generation for MBBS                                               |       |

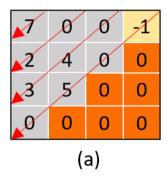

| Figure C.1 – Generic 4x4 group of residues undergoing Transform and Quantization         |       |

| Figure C.2 – Example of CSBF signaling                                                   |       |

| Figure C.3 – Example of residual SEs generation for generic 4x4 block of coefficients    | .159  |

| Figure C.4 – Residual SEs generation for the original HM approach                        |       |

| Figure C.5 – Residual SEs generation for the MAE approach                                | .162  |

| Figure C.6 – Residual SEs generation for the MRSET approach                              |       |

| Figure C.7 – Prior residual syntax element treatment logic                               |       |

| Figure C.8 – Four cores MRSET behavior                                                   |       |

| Figure C.9 – Internal structure of a MRSET single core                                   | .169  |

# TABLE LIST

| Table 2.1 – Examples of raw videos size and required bandwidth                           | 30    |

|------------------------------------------------------------------------------------------|-------|

| Table 3.1 – Examples of basic binarization types                                         | 48    |

| Table 3.2 – Summary of related prior-art works                                           | 62    |

| Table 4.1 – Proportion of bin types occurrence for test video sequences                  | 65    |

| Table 4.2 – Power results of the power-saving techniques within four-BAE cores design    |       |

| Table 4.3 – Comparisons with related works of the power-saving BAE design                | 72    |

| Table 5.1 – Examples of Low update for arbitrary bypass bins sequences                   | 77    |

| Table 5.2 – Throughput increase related to baseline BAE by using MBBS                    | 85    |

| Table 5.3 – Power values and power savings of related BAE architectures                  | 86    |

| Table 5.4 – Comparison with related prior-arts works                                     | 87    |

| Table 6.1 – Throughput comparisons of MB-BAE and BS-BAE                                  |       |

| Table 6.2 – Throughput comparisons of AltBAE, PrelBAE, and BA-BAE                        | 98    |

| Table 6.3 – Comparisons of MB-BAE and AltBAE against prior-arts                          | . 100 |

| Table 7.1 – Throughput and estimated power dissipation comparison between AltBAE and     | d     |

| MB-BAE                                                                                   |       |

| Table 7.2 – Throughput requirement for different levels of the HEVC standard             | . 102 |

| Table 7.3 – Simulation and synthesis results for AltBAE, 2C-BAE, and 1C-BAE              |       |

| Table 7.4 – Power dissipation results for the Traffic sequence on AltBAE versions        | . 104 |

| Table 7.5 – Power dissipation results for the Kimono sequence on AltBAE versions         |       |

| Table 7.6 – Power dissipation results for the PartyScene sequence on AltBAE versions     |       |

| Table 7.7 – Power dissipation results for the BlowingBubbles sequence on AltBAE version  | ns    |

|                                                                                          |       |

| Table 7.8 – Power dissipation results for the Johnny sequence on AltBAE versions         |       |

| Table 7.9 – Power dissipation results for the ChinaSpeed sequence on AltBAE versions     |       |

| Table 7.10 – Comparison between power saving and throughput degradation among AltB.      |       |

| versions                                                                                 |       |

| Table 7.11 – Estimated time values for standard HEVC levels High tier constraints        |       |

| Table 7.12 – Estimated time values for standard HEVC levels Main tier constraints        |       |

| Table 7.13 – Estimated energy values for standard HEVC levels High tier constraints      |       |

| Table 7.14 – Estimated energy values for standard HEVC levels Main tier constraints      |       |

| Table 7.15 – Synthesis results of the power-saving AltBAE versions                       | .109  |

| Table 7.16 – Power dissipation results for the Traffic sequence on power-saving AltBAE   | 100   |

|                                                                                          | .109  |

| Table 7.17 – Power dissipation results for the Kimono sequence on power-saving AltBAE    |       |

| versions                                                                                 |       |

| Table 7.18 – Power dissipation results for the PartyScene sequence on power-saving AltB  |       |

| versions                                                                                 | . 109 |

| Table 7.19 – Power dissipation results for the BlowingBubble sequence on power-saving    | 110   |

| AltBAE versions                                                                          | .110  |

| Table 7.20 – Power dissipation results for the Johnny sequence on power-saving AltBAE $$ | 110   |

| versions                                                                                 |       |

| Table 7.21 – Power dissipation results for the ChinaSpeed sequence on power-saving AltH  |       |

| versions                                                                                 | .110  |

| Table 7.22 – Summary of power-saving AltBAE versions and comparisons with original       | 111   |

| designs  Table 7.22 Comparison of power soving AltDAE versions against each other        |       |

| Table 7.23 – Comparison of power saving AltBAE versions against each other               |       |

| Table 7.24 – Estimated throughput and power consumption on 525 MHz                       | .113  |

| Table 7.25 – Estimated time and energy dissipation on hypothetical future real-time scenar | ios |

|--------------------------------------------------------------------------------------------|-----|

|                                                                                            |     |

| Table 7.26 – Estimated energy savings using energy-efficient approach against LP-AltBAH    |     |

|                                                                                            |     |

| Table 7.27 – Occurrence percentage for each value QP within a GoP – Intra Frame QP 22.     | 116 |

| Table 7.28 – Occurrence percentage for each value QP within a GoP – Intra Frame QP 37.     |     |

| Table 7.29 – Example of static methodology for QP 22 sequences                             |     |

| Table 7.30 – Pseudo-dynamic approach for QP 23 drop in bitstream contribution              |     |

| Table 7.31 – Pseudo-dynamic approach for QP 23 increase in bitstream contribution          |     |

| Table 7.32 – Summary of the methodologies for the energy-efficient BAE approach            |     |

| Table 7.33 – Synthesis results for ET-BAE                                                  |     |

| Table 7.34 – ET-BAE power dissipation results for the Traffic sequence                     |     |

| Table 7.35 – ET-BAE power dissipation results for the Kimono sequence                      |     |

| Table 7.36 – ET-BAE power dissipation results for the PartyScene sequence                  |     |

| Table 7.37 – ET-BAE power dissipation results for the BlowingBubbles sequence              |     |

| Table 7.38 – ET-BAE power dissipation results for the Johnny sequence                      | 124 |

| Table 7.39 – ET-BAE power dissipation results for the ChinaSpeed sequence                  | 124 |

| Table 7.40 – Average power dissipation results for ET-BAE and power degradation            | 124 |

| Table 7.41 – ET-BAE estimated energy savings against LP-AltBAE                             | 125 |

| Table 7.42 – Proposed BAE designs comparison                                               | 127 |

| Table A.1 – Proposed binarizer synthesis results                                           | 144 |

| Table A.2 – Power results for the single-core binarizer architectures                      |     |

| Table A.3 – Power and throughput results for the four-core binarizer architectures         | 145 |

| Table A.4 – Comparison with related works                                                  |     |

| Table C.1 – Main syntax elements proportion among different types of HEVC frames           |     |

| Table C.2 – Major bins contributors among HEVC data hierarchy                              |     |

| Table C.3 – Videos characterization for residual SEs generation                            |     |

| Table C.4 – Execution time for original HM method against modified HM with MRSET           |     |

| Table C.5 – MRSET dependencies and limits amounts                                          |     |

| Table C.6 – Related HEVC entropy encoder characteristics                                   |     |

| Table C.7 – Synthesis results for the MRSET designs                                        | 172 |

| Table C.8 – Power results for the LP-MRSET designs                                         |     |

| Table C.9 – Synthesis results for the PRSET                                                |     |

| Table D.1 – Throughput for MB-BAE full architecture                                        |     |

| Table D.2 – Throughput for MB-BAE 2-Cores architecture                                     |     |

| Table D.3 – Throughput for MB-BAE 1-Core architecture                                      | 178 |

| Table D.4 – Throughput for AltBAE full architecture                                        |     |

| Table D.5 – Throughput for 2C-BAE architecture                                             |     |

| Table D.6 – Throughput for 1C-BAE architecture                                             |     |

| Table D.7 – Traffic sequence first second bitrate distribution                             |     |

| Table D.8 – Kimono sequence first second bitrate distribution                              |     |

| Table D.9 – PartyScene sequence first second bitrate distribution                          |     |

| Table D.10 – BlowingBubbles sequence first second bitrate distribution                     |     |

| Table D.11 – Johnny sequence first second bitrate distribution                             |     |

| Table D.12 – ChinaSpeed sequence first second bitrate distribution                         | 190 |

### **ABBREVIATIONS**

AMP Asymmetric Motion Partition

ASIC Application Specific Integrated Circuit

AVC Advanced Video Coding

BAE Binary Arithmetic Encoding

BC Binarization Core

BPBS Bypass Bin Splitting

CABAC Context-Adaptive Binary Arithmetic Coding

CAVLC Context-Adaptive Variable Length Coding

CMBB Complete Multiple Bypass Bins

CMOS Complementary Metal-Oxide Semiconductor

COEFF1 coeff\_abs\_level\_greater1\_flag

COEFF2 coeff\_abs\_level\_greater2\_flag

CSBF coded\_sub\_block\_flag

CTU Coding Tree Unit

CU Coding Unit

DCT Discrete Cosine Transform

DST Discrete Sine Transform

EG Exponential Golomb

FL Fixed Length

FPGA Field-Programmable Gate-Array

FSE Full Syntax Element

FU Full Unit

GoP Group of Picture

GND Ground

HD High Definition

HEVC High-Efficiency Video Coding

HM HEVC Reference Model

HPC Hybrid Path Coverage

JVET Joint Video Exploration Team

LAST last\_sig\_coeff\_x, last\_sig\_coeff\_y

LD Low-Delay

LH Look-ahead

LPS Least Probable Symbol

LU LPS Unit

LZD Leading Zero Detector

MAE Memory-Access Efficient Approach

MBBS Multiple Bypass Bins Scheme

MRSET Multiple Residual Syntax Element Treatment

MC Motion Compensation

ME Motion Estimation

MPS Most Probable Symbol

MU MPS Unit

MV Motion Vector

NMOS Negative Metal-Oxide Semiconductor

OB Outstanding Bits

PDK Project Design Kit

PIPO Parallel-In Parallel-Out

PMOS Positive Metal-Oxide Semiconductor

PN Pre-renormalization

PRSET Prior Residual Syntax Element Treatment

PU Prediction Unit

PVT Process Voltage Temperature

QP Quantization Parameter

RA Random Access

RGB Red, Green, Blue

RMBB Reduced Multiple-Bypass Bins

RQT Residual Quad Tree

RTL Register Transfer Level

PVT Process, Voltage, Temperature

REM coeff\_abs\_level\_remaining

SAO Sample Adaptive Offset

SE Syntax Element

SIG sig\_coeff\_flag

SIGN coeff\_sign\_flag

SMP Symmetric Motion Partition

SSE Simplified Syntax Element

UHD Ultra-High Definition

YCbCr Luminance, Chrominance Blue, Chrominance Red

YUV Luminance, Chrominance Component 1, Chrominance Component 2

TR Truncate Rice

TU Transform Unit

TU Truncate Unary

U Unary

VDD Voltage

VVC Versatile Video Coding

WPP Wavefront Parallel Processing

WQXGA Wide Quad Extended Graphics Array

# **SUMMARY**

| 1 INTRODUCTION                                                   | 19 |

|------------------------------------------------------------------|----|

| 1.1 Motivation and Problem Definition                            | 20 |

| 1.2 Main Contributions of the Thesis                             | 23 |

| 1.3 Outline                                                      | 25 |

| 2 VIDEO PROCESSING, ARITHMETIC CODING, AND POWER DISSIPATION     |    |

| CONCEPTS                                                         |    |

| 2.1 Digital Video Basic Concepts                                 | 27 |

| 2.2 Digital Video Encoding                                       |    |

| 2.2.1 Spatial Redundancy                                         |    |

| 2.2.2 Temporal Redundancy                                        |    |

| 2.2.3 Entropic Redundancy                                        |    |

| 2.3 HEVC Video Coding Standard                                   |    |

| 2.3.1 Coding Tree Units and Subdivision.                         |    |

| 2.3.2 Predictions                                                |    |

| 2.3.3 Transforms                                                 |    |

| 2.3.4 Quantization                                               |    |

| 2.3.5 Filters                                                    |    |

| 2.3.6 Entropy Encoding                                           |    |

| 2.4 Communication Theory and Arithmetic Coding Basic Concepts    |    |

| 2.4.1 Entropy Definition for Comunication Theory                 |    |

| 2.4.2 Arithmetic Coding                                          |    |

| 2.5 Power Consumption Concepts on CMOS Components                |    |

| 2.5.1 CMOS Dynamic Power Consumption                             |    |

| 2.5.2 Architectural Techniques for Dynamic Consumption Reduction |    |

| 3 CABAC ALGORITHM                                                |    |

| 3.1 CABAC Concepts                                               |    |

| 3.1.1 Binarization                                               |    |

| 3.1.2 Context Modeling                                           |    |

| 3.1.3 Binary Arithmetic Encoding                                 |    |

| 3.2 Related BAE Prior-art                                        |    |

|                                                                  |    |

| 3.2.2 Work of Fei et al                                          |    |

| 3.2.4 Work of D. Zhou et al.                                     |    |

| 3.2.5 Summary of Related Works                                   |    |

| 4 LOW-POWER DESIGN FOR BAE BLOCK                                 |    |

| 4.1 Methodology for Low-power Design                             |    |

| 4.2 Analysis of the BAE Behavior                                 |    |

| 4.3 Statistical Analysis of the BAE Inputs                       |    |

| 4.4 Power-saving BAE Architecture Design                         |    |

| 4.5 Synthesis Results and Comparisons                            |    |

| 5 NOVEL MULTIPLE-BYPASS BINS PROCESSING FOR HEVC BAE             |    |

| 5.1 Low Update and Renormalization for Bypass Bins               |    |

| 5.2 Multiple-Bypass Bins Scheme                                  |    |

| 5.3 Results of MBBS and Power-saving Approach in BAE Design      |    |

| 6 ARCHITECTURAL DESIGNS FOR HIGH-THROUGHPUT BAE USING            | 00 |

| MULTIPLE-BYPASS BINS SCHEME                                      | 89 |

| 6.1 Ultra-High-Throughput BAE Architecture with MBBS                             | 89   |

|----------------------------------------------------------------------------------|------|

| 6.2 Efficient High-Throughput BAE Architecture with MBBS                         |      |

| 6.3 Simulation, Synthesis Results, and Comparisons                               |      |

| 7 TOWARDS HIGH-THROUGHPUT AND ENERGY-EFFICIENCY TRADE-OFF                        | 3    |

| BAE DESIGN                                                                       |      |

| 7.1 Preliminary Power-Analysis Comparison between High-Throughput BAE            |      |

|                                                                                  | 101  |

| 7.2 AltBAE Different Configurations Proposal: Throughput and Power Consumptio    | n    |

| Analysis                                                                         |      |

| 7.3 Power Saving Techniques within the Scope of the Energy-Efficient High-Throug | hput |

| BAE                                                                              | 108  |

| 7.4 Performance and Energy Trade-off Architecture BAE                            | 111  |

| 7.4.1 Proposal of Use Methodology.                                               | 112  |

| 7.4.2 ET-BAE Architecture.                                                       |      |

| 7.5 Overall Comparisons of BAE Architectural Proposals of the Thesis             | 126  |

| 8 CONCLUSIONS AND FUTURE WORKS                                                   |      |

| 8.1 Publications by the Author                                                   |      |

| 8.1.1 Journals.                                                                  |      |

| 8.1.2 Conferences.                                                               | 131  |

| REFERENCES                                                                       | 133  |

| APPENDIX A <low-power architecture="" binarization=""></low-power>               | 139  |

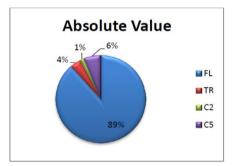

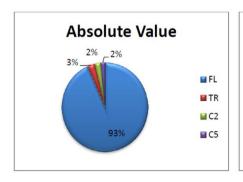

| A.1 Statistical Analysis of Binarization Methods Occurrence Rate                 | 139  |

| A.2 Low-Power Binarization Proposal                                              | 141  |

| A.3 Simulation and Synthesis Results                                             | 143  |

| APPENDIX B < ALTERNATIVE APPROACH TO EXPLAIN MBBS INCEPTION:                     |      |

| APPENDIX C < HEVC RESIDUAL SYNTAX ELEMENTS GENERATION FOR                        |      |

| HIGH-THROUGHPUT CABAC DESIGNS                                                    | 155  |

| C.1 Motivation                                                                   | 155  |

| C.2 HEVC Syntax Elements Analysis                                                | 156  |

| C.2.1 Major SEs Contributos for CABAC processing                                 | 156  |

| C.2.2 Residual SEs Processing.                                                   | 157  |

| C.2.3 HEVC Reference Software Analysis.                                          |      |

| C.3 Preliminary MRSET Software Version Analysis                                  | 163  |

| C.4 MRSET Hardware Proposal                                                      |      |

| C.4.1 Prior Residual Syntax Elements Treatment (PRSET)                           | 165  |

| C.4.2 MRSET Hardware Approach                                                    |      |

| C.4.3 Power-saving MRSET Approach                                                | 170  |

| C.5 ASIC Synthesis Results and Discussion                                        |      |

| APPENDIX D < SUPPORT DATA FOR EFFICIENT ENERGY-THROUGHPUT                        |      |

| TRADE-OFF BAE ARCHITECTURE – ET-BAE >                                            | 177  |

#### 1 INTRODUCTION

Video coding is a field of high interest in the past few years, due to increasing demand for video processing, storage, and transmission. For instance, the limitation in traffic bandwidth causes the transmission of raw video (i.e., a given video sequence without any compression) to be prohibitive, especially considering real-time processing. Moreover, the amount of internet traffic share already occupied by video streaming providers, such as YouTube, Hulu, HBO, Netflix, and so on, has already reached 50% of the total data flowing through internet (SUMMERS, 2016), and tends to increase even more in the next years, reaching more than 82% of total internet share by 2022 (CISCO, 2014), (CISCO, 2017).

The scenario presented drives the research for efficient tools to compress, store, and transmit high-resolution video sequences. Therefore, video coding standards have been developed and updated for that purpose. Currently, the H.264/AVC (ITU-T, 2003) is the most used coding standard for many of the all-day devices one may use (e.g., smartphones, smart-TVs, etc.), even though its first version is dated from 2003 (HEADJACK, 2018).

The evolution of increasing video resolutions (e.g., bigger television screens with more pixels within), of increasing sample rates (i.e., the frequency that the frames of a video are updated throughout the video processing flow), and constraints for real-time processing, due to the higher amount of data to be processed, led to research for new methods to compress video. For instance, the 4K resolution has 3840 x 2160 pixels within each frame of video, whereas 8K resolution has 7680 x 4320 pixels. Considering also that sample rates currently may range from 24 up to 300 frames per second. For example, a single second of a raw 8K video at 120 frames per second may generate up to 15-Gigabits of data. The HEVC (High-Efficiency Video Coding) is the H.264/AVC successor, being able to achieve up to twice the compression capabilities of H.264/AVC, whereas keeping the same subjective visual quality when compared to its predecessor (SULLIVAN, 2012). The first version of the HEVC standard dates from 2013, whereas extensions were further developed (ITU-T, 2013).

The new generation of video coding standards has proved to be more efficient regarding data compression compared to the older standards. Nevertheless, real-time processing for video encoding is still a major bottleneck when a software solution is used. The alternative is to use specific silicon devices to achieve the required constraints, where either FPGA (Field-Programmable Gate-Array) or ASIC (Application Specific Integrated Circuit) are suitable for that purpose. Therefore, the usage of accelerators is mandatory to achieve that real-time processing goal. Moreover, battery-based devices (e.g., smartphones) drive a

potential scenario where the application of these hardware blocks occurs. Thus, a low-power-driven design is another crucial step towards an energy-efficient silicon architecture.

The video coding standards are composed of macro operations, which are the focus of research to accomplish efficient hardware designs for dedicated architectures to execute these specific operations. For instance, one may cite for HEVC encoder: inter-prediction (motion estimation and compensation), intra-prediction, transforms, quantization, filters, and entropy coding.

The HEVC standard allows only one type of entropy coding algorithm, which is the CABAC (Context-Adaptive Binary Arithmetic Coding) (MARPE, 2003), whereas its predecessor, the already cited H.264/AVC, allowed two algorithms: the CABAC, and the CAVLC (Context-Adaptive Variable Length Coding) (ITU-T, 2003). The usage of CABAC offers coding improvements when compared to CAVLC, at the cost of increased computational cost (SZE, 2013). For instance, the challenge to process more than one bit of data at once in CABAC is more difficult, since the previous data bit will often create dependencies for the current datum processed. Many studies and researches in the past few years have pointed out possible solutions for high-throughput CABAC hardware designs: (CHEN, 2010), (LIU, 2011b), (FEI, 2011), (PENG, 2013), (ZHOU, 2013), (VIZZOTTO, 2015) and (ZHOU, 2015), as examples. Hence, the next sub-section presents the motivation and the problem definition of this Thesis.

#### 1.1 Motivation and Problem Definition

Video coding (where coding has the same meaning of compression within the scope of video processing) is a mandatory part of the current scenario of video storage and transmission, considering the scope of real-time processing for increasingly higher videos resolutions and sample rates. The HEVC standard is one of the most recent alternatives to accomplish efficient video processing (ITU-T, 2013), offering some new features to increase higher parallelism processing, such as the use of Tiles and WPP (Wavefront Parallel Processing). The previously mentioned techniques divide a frame (which is a single image of a given video coding sequence) into partitions using different approaches, where an entropy encoder instance can process each partition. Hence, it increases the throughput of the video coded bitstream generation, at the cost of a decrease in coding gains (i.e., a higher amount of bits are generated by the coded video when compared to a sequence which was coded without the parallel-processing techniques mentioned). For instance, the usage of Tiles and WPP lead

to a loss in coding efficiency, which may decrease, on average, 3.73 % and 1.07%, respectively (CHI, 2012).

Nevertheless, the use of the parallel processing techniques implies in multiple instances of the CABAC block, which undoubtedly leads to an increase in area and power dissipation for the encoder as a whole, considering the case where one is using an ASIC approach for HEVC encoder. The use of specific accelerator leads to a suitable option to reach the real-time constraints for high-resolution video sequences processing, when compared to the software option. Hence, a single CABAC instance seems to be a reasonable alternative, in case that single instance can achieve a given throughput requirement for a target real-time video resolution processing, whereas also keeping the coding efficiency at an optimal value (for instance, around 800 Mbits/s for real-time level 6.2 high tier, as defined by the HEVC standard).

One may ask about the contribution that the CABAC has within the HEVC encoder. In fact, the predictions (inter or intra) are the most time-consuming step of HEVC encoder, ranging from 42.5% up to 88.7% of total encoding execution time (WON, 2015). Nevertheless, the impact of CABAC in execution time is not negligible, being able to reach up to 11% of the total time contribution, with an average contribution of 4.7% (WON, 2015). Furthermore, CABAC behavior implies in heavily computational complexity, which affects, for instance, in its parallelization opportunities to increase throughput, or for efficient rate-estimation for mode decision (WON, 2015), becoming a potential bottleneck of the encoding flow, therefore. The reported data are another reason towards a high-performance hardware HEVC entropy encoder, as attested by the related CABAC designs cited before.

A power-saving CABAC approach is a desirable goal, considering that video encoding occurs within battery-based devices, such as smartphones, and they may be delivered in real-time for a live broadcast, for instance. HEVC seems to be more energy consuming than the previous generation of video encoding standards (MONTEIRO, 2015), where significant power dissipation increase is reported. Thus, since the HEVC encoder as a whole consumes more power, one may consider that it is an appropriate research focus to diminish the dissipated power in all encoding steps, including the entropy encoding.

Detailing some important literature efforts within the context presented before, in the work of (LIU, 2011b) we find one of the first alternatives to increase throughput for a CABAC hardware design, where renormalization steps required by the CABAC block runs in a single cycle. This work was done in the context of the previous H.264/AVC standard, but its architectural proposal is still valid for the CABAC of the HEVC standard since it affects the

main sub-block of the entropy coding, which has not changed from one standard to the other: the Binary Arithmetic Encoder (BAE). Moreover, in one of the most recent and successful works concerning ultra-high-throughput results, the work of (ZHOU, 2015) presents many architectural novelties, gathering also prior-art proposals of (FEI, 2011) and (ZHOU, 2013), which will be further presented in this Thesis. Thus, the work of (ZHOU, 2015) is the up-to-date state-of-the-art in terms of CABAC design, which is able to reach the constraints for real-time 8K UHD (Ultra-High Definition) video resolution (CHEN, 2015).

The mentioned works point the interest of recent research for a high-throughput single-core CABAC hardware design, even with the parallel novelties the HEVC standard has proposed. Nevertheless, none of them focuses also on low-power design or low-power opportunities in their designs, which is, as one may notice, a relevant field of research for hardware video processing architectures. Moreover, since no recent work deals with the power dissipation issue, there is also no relevant data to use as a reference on where or how to seek for power reduction opportunities within the CABAC block in an efficient manner.

State-of-the-art CABAC design already surpasses the minimum requirement for the HEVC standard defined maximum constraint (i.e., the 6.2 Level at High tier). However, future real-time requirements can potentially be even more restrictive and far beyond the current ones, which will demand newer high-throughput approached for that reason. For instance, the intended successor of HEVC is already under development, named Versatile Video Coding (VVC) (BROSS, 2018). Power dissipation is crucial to take into account, considering the scope of battery-based encoding architectures. Considering that future scenarios may demand higher processing capabilities, which will consume more power due to the hardware increase to cope with these hypothetical scenarios, power-saving approaches seem necessary along with the performance-driven design.

Hence, some points may be drawn considering the global scope of this Thesis, which provide directions for the research described herein:

- Is it possible to increase the throughput of a CABAC hardware design beyond the current state-of-the-art for future real-time video processing constraints, especially considering a type of input data that suffers from fewer dependencies and thus is potentially more feasible to parallelize its processing? If possible, how is the implementation of this approach? What are the potential gains in terms of performance?

- Are there modules which may potentially be dissipating power which otherwise could be turned off? How to assure that these modules would, under

- a real environment, save power effectively? Does this approach, in case possible, affects the throughput of the CABAC block?

- Is it possible to integrate into a configurable high-throughput low-power CABAC design, where, depending on the characteristics of a given video sequence being processing, an on-the-fly choice can be made considering the best throughput and energy required trade-off, turning on or off parts of the architecture? For instance, state-of-the-art CABAC designs focus on reaching throughput constraints for real-time 8K UHD video processing. However, considering that this same ultra-high-throughput architecture would process video sequences with smaller resolutions (e.g., Full-HD), would it not be overestimated for this resolution and therefore be dissipating additional power/energy? Moreover, for future real-time video constraints, is possible to have an energy vs. throughput CABAC design, which presents the best trade-off between the referred variables and still achieves the real-time requirements?

#### 1.2 Main Contributions of the Thesis

The scope of this Thesis is the entropy-encoding step, according to the HEVC coding standard, which is the CABAC block. The reasons to focus on CABAC were presented previously (e.g., difficulties in the processing parallelization, being a potential bottleneck of the HEVC encoder flow; and the advantages of a single high-throughput CABAC instance design for power saving and coding efficiency). Efficient architectural for the critical part of the algorithm (i.e., the BAE block), targeting ultra-high-throughput and low-power design, are the primary goals, where the global objective is a configurable entropy encoder block, considering the best trade-off configuration between the two variables for the possible gamma of different video sequence characteristics: throughput and power.

For the desired objectives, recommended video sequences analysis (BOSSEN, 2013), running under the HEVC reference software HM (HM, 2016) was performed, in order to analyze and to validate novel techniques targeting increasing throughput for the CABAC block. Moreover, statistics were gathered for insertion of fine-grain low-power efficient techniques, based on the data assessed, reducing the power dissipation of designed BAE architectures. Furthermore, a novel scheme for parallel processing of bypass bins is derived (i.e., a type of CABAC data with less dependencies for processing), and its efficiency is

measured in the BAE hardware design described as a gate-level netlist. Additionally, the integration of prior-art high-throughput approaches within a BAE block, along with the novel scheme for multiple-bypass bins processing of this Thesis, is carried out followed by simulations and hardware synthesis results. Finally, based on the multiple-bypass bins novel BAE approaches, an energy-throughput configurable BAE architecture is introduced for the first time. This approach can deliver possible current and future scenarios real-time throughput, and keep the energy consumption on an optimal level, when compared with the non-configurable BAE circuits, by adding a feature that isolate parts of the architecture and thus avoids extra power dissipation.

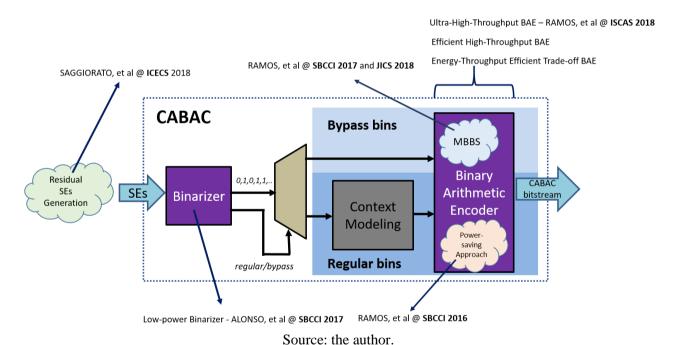

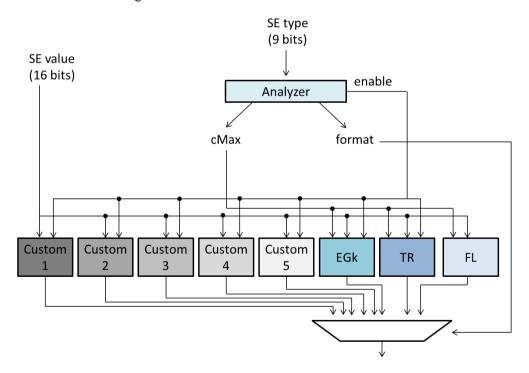

As a summary, the main contributions presented in this Thesis are as follows, and are depicted in Figure 1.1 in a macro point of view within a zoomed-in CABAC block diagram (one may notice that additional contributions also appear in Figure 1.1, which are shown in the Appendixes of this Thesis):

- Statistical Analysis for Low-Power Opportunities (Chapter 4): recommended video sequences were run in the HM software, and the generated statistics pointed out possible power-saving possibilities within a hardware BAE block.

- Low-Power High-Throughput Binary Arithmetic Encoder Proposal (Chapter 4): using the statistics gathered for low-power design, a Low-Power High-Throughput BAE architecture is presented, for which gate-level netlist power values are shown along with the power savings achieved by the use of the fine-grain low-power insertions herein.

- Novel Multiple-Bypass Bin Processing Scheme MBBS (Chapter 5): a novel scheme is proposed, based on the behavior of CABAC variables that controls the processing during video encoding flow, to increase the throughput of hardware BAE design. The proposed approach takes into consideration the increasing amount of a specific data type of HEVC encoded video sequences (i.e., the bypass bins), which has smaller dependencies among them and, therefore, are more feasible to be processed in parallel.

- Ultra-High-Throughput Binary Arithmetic Encoder Architecture using MBBS (Chapter 6): combining prior-art techniques from literature along with the novel MBBS, a new BAE architecture is presented, having the highest throughput found in the literature, whereas the throughput results come from

recommended video sequences using different parameters settings (BOSSEN, 2013).

- Efficient High-Throughput Binary Arithmetic Encoder using MBBS (Chapter 6): a second BAE architecture is proposed, presenting a faster time-to-market design, where the usage of MBBS achieves a similar throughput to prior-art BAE designs, at the advantage of less penalty in terms of area and potentially power.

- Efficient Energy-Throughput Trade-off Binary Arithmetic Encoder Architecture and Methodology of Use (Chapter 7): as the last novel contribution of this Thesis, the Efficient High-Throughput BAE presented in Chapter 6 is assessed, by analyzing smaller versions of the original design. In the end, together with the low-power approach of Chapter 4, a configurable BAE architecture is presented, using on-the-fly different cores, accomplishing potential energy efficiency for current and future real-time video processing scenarios, keeping the real-time throughput requirements.

- Power-saving Binarization Design (Appendix A): a power-saving Binarization block is presented, and the power results measured and compared with related literature works, attesting the power gains of the proposal.

- Efficient Residual Syntax Elements Generation Architecture for High-Throughput CABAC Designs (Appendix C): an approach to deliver the data that corresponds to the major input contributor of CABAC is presented, assuring sufficient input data rate and avoiding recent CABAC designs to starve of incoming symbols.

#### 1.3 Outline

The text is organized as follows: **Chapter 2** presents the background concepts for video processing, video coding, the HEVC standard, information entropy and arithmetic coding basics, and power-consumption in CMOS circuits. **Chapter 3** gives an overall description of the CABAC algorithm, its main sub-steps, and variables, along with details of the most relevant reference CABAC works found in the literature. The statistical analysis to assess the opportunities for low-power insertions into a BAE design and the proposed BAE architecture using the low-power approach driven by the statistical analysis appear in **Chapter 4**, along with preliminary synthesis results. The novel Multiple-Bypass Bins Scheme

definitions are presented in **Chapter 5**, along with the throughput gains achieved by the use of the technique into a baseline BAE design. **Chapter 6** presents the two new ultra-high-throughput proposed BAE architectures using the MBBS and other prior-art techniques, along with simulation and synthesis results, and comparisons with related relevant works. The efficient energy-throughput BAE design (gathering techniques and proposals from previous chapters of this Thesis), along with the methodology of use and the synthesis results related appear in **Chapter 7**. **Chapter 8** discusses the results obtained at this Thesis, along with future works within the same scope. **Appendix A** presents the low-power Binarization architecture, and **Appendix B** a different approach to explain the MBBS inception. **Appendix C** presents the residual Syntax Element architecture proposed within the context of high-throughput CABAC design, whereas **Appendix D** contains support data for the architecture proposed in Chapter 7.

Figure 1.1 – Main Thesis contributions

# 2 VIDEO PROCESSING, ARITHMETIC CODING, AND POWER DISSIPATION CONCEPTS

This chapter will describe basic concepts related to video processing, such as how a video is composed, the color spaces that may be used. The HEVC standard, along with its basic concepts, also appears in this chapter. Furthermore, the depiction of the primordial explanation on the concept of entropy from communication theory, along with the basic understanding of general arithmetic coding, appears in this chapter. Additionally, the backbone elements regarding power consumption on CMOS circuits are presented, along with the techniques related to power saving on the architectural level of implementation.

## 2.1 Digital Video Basic Concepts

A digital video is a composition of several images that appear in sequence, which intends to emulate to the viewer the sensation that movement is occurring during those images presentation. The images are referred as frames, and a given sampling rate for those frames shall be achieved to transmit the mentioned sensation of movement to the viewer. The minimum sampling rate is 24 frames per second (RICHARDSON, 2010). Higher sampling rates (e.g. 30, 60, 120 frames per second) present smoother sensation during the transition between frames and are suitable options when the desired smoothness is a goal (RICHARDSON, 2010).

The basic primitive or cell of a frame is a pixel, which represents the color intensity that minimal point into a given picture space has. The more pixels a frame has, the more accurate compared to reality is that frame. The resolution of a video is the number of pixels we have into both horizontal and vertical axis. For example, 1920x1080 pixels (Full-HD), 2560x1600 pixels (WQXGA), and so on. A pixel is a composition of more than one aspect of color or brightness, which is called color space. For instance, a widely used color space is the RGB (Red Green Blue), where each pixel is composed of a value for the red, for the green, and for the blue color intensities (called color components). The composition of the values for the three colors mentioned forms a wide variety of color the human eye is able to recognize. Figure 2.1 presents an example of RBG image composition.

Another color space is the YCbCr (Luminance Chrominance Blue and Chrominance Red), also called YUV (MIANO, 1999). For that color space, the pixel composition is formed by a brightness/light (luminance) component (i.e., Y), and two color components (i.e., Cb and

Cr, or U and V). The main difference between the YCbCr compared to RGB is the disassociation of the luminance and color components at YCbCr. Moreover, the fact that the human eye is more sensitive to the light than to color (RICHARDSON, 2010) leads to an interesting potential for subsampling of the different components, without prejudice to the subjective visual information a frame has. Figure 2.2 presents an example of YCbCr composition into an image.

Figure 2.1 – RGB image decomposition

Source: http://www.augustrs.com/fractal-camouflage/

Cr Cb

Figure 2.2 – YCbCr image decomposition

Source: https://hisour.com/pt/ycbcr-color-spaces-26075/

Each color component representation is as a binary value into an n-bits vector. The more bits this vector has, the wider the variety of colors an image can represent. For instance, 8-bit pixel representation leads to 256 possible colors possible, whereas 32-bit pixel representation leads to more than four billions colors. Nevertheless, the distribution of

information among the components of given color space may vary. One may notice that, since the human eye is more sensitive to the luminance component compared to the color components of a YUV color space, the amount of information for the color components could be smaller than the luminance. For instance, for every four samples of the component Y, one may have a single sample for U and a single sample for V. This kind of processing is called sub-sampling (also known as pixel decimation). Below are presented some alternatives to sub-sampling, whereas Figure 2.3 presents the sub-sampling formats visually:

- Sub-sampling 4:4:4: For every four Y samples, also four U and four V samples exist (in other words, there is no sub-sampling). This pattern is used for high-fidelity applications since no loss will occur by using it.

- **Sub-sampling 4:2:2**: For every four horizontal Y samples, two U and two V samples exist (i.e., there is no sub-sampling in the vertical axis).

- **Sub-sampling 4:2:0**: For every four Y samples, there will be one U and one V samples. This sub-sampling pattern leads to 50% of data saving and is the most used when comes to video compressions (RICHARDSON, 2010).

Y U+V YUV + → → 4:4:4 + → → 4:2:2 + → → 4:2:0 + → → 4:1:1

Figure 2.3 – Sub-sampling examples

Source: http://www.ravepubs.com/chroma-subsampling/

#### 2.2 Digital Video Encoding

Digital video encoding has the same meaning as video compression. The main reason for video encoding is the prohibitive amount of data a raw video generates, which leads to increasing demand for video storage. Moreover, in the context of video transmission through

an internet channel, the bandwidth would be extremely limited for transmission of raw video, for instance. For example, Table 2.1 presents the estimated data amount required for storage and the required bandwidth for raw 10 minutes videos at different resolutions, considering 12-bits for each color component (MONTEIRO, 2017).

Table 2.1 – Examples of raw videos size and required bandwidth

| Resolution | Size (GBytes) | Bandwidth (Mbytes/s) |

|------------|---------------|----------------------|

| 834x480    | 10            | 17.13                |

| 1920x1080  | 52            | 88.98                |

| 2560x1600  | 103           | 175.78               |

| 3480x2160  | 189           | 322.58               |

Source: (MONTEIRO, 2017).

The basic leverage of video encoding is to explore redundancies in the image. For instance, Figure 2.4 shows a video sequence composed of a certain amount of frames. One may notice that, within a single frame, many pixels will have a very close (if not the same) color. Moreover, it is easy to observe by comparing the frames within the pointed sequence that some pixels are just "moving" between one frame to the other (possibly keeping the same color during this "movement," or with a slight difference compared to the pixel from the previous frame). Therefore, there is no need to send the same or closely the same information related to pixels among different frames. One may sample the closely related value of a neighbor pixel from the current or a different frame and send this information just once. Hence, the redundancies categories among images within a video sequence are spatial, temporal, and entropic.

Figure 2.4 – Example of video sequence decomposition into frames

Source: http://www.danielearmillotta.eu/2039/articoli/sigle-nei-video-risoluzione-e-frame-rate/

#### 2.2.1 Spatial Redundancy

Neighbor pixels within the same frame can have the same or a very similar color. Therefore, an encoding process could send the information of a chosen pixel inside that similarity group, and consider the color values of this chosen pixel as the base value. The information sent from the other pixel within the similarity set is the difference between their color values and the base value of the chosen pixel, named residues. Since the color difference tends to be minimal if a suitable group of pixels is selected, the difference values that are sent instead of the original pixel color values are smaller and, therefore, compression is accomplished. This type of redundancy is also known as intra-frame redundancy (GHANBARI, 2003). Usually, the intra-frame redundancy is the chosen to be applied when no other type of redundancy is available (for instance, at the very first frame of a video sequence), or in case random insertion points are required during the video encoding.

#### 2.2.2 Temporal Redundancy

Pixels among different frames can simply "move" from one to another (i.e., from one frame to another, a given pixel is at another position within a different frame). Nevertheless, the color values of this pixel have just moved and can have changed slightly or have not changed at all. Hence, the same reasoning derived from the spatial redundancy can be applied, with one extra information: the encoding process has to discover the amount of movement that pixel (or group of pixels) has undergone, and the difference of values from the original pixel (or pixels), i.e., the residues. This temporal redundancy is also known as inter-frame redundancy (GHANBARI, 2003). The inter-frame redundancy is the major contributor for the data savings when comparing the original raw video to the final encoded sequence at the cost of being the bottleneck for video encoding performance (ZATT, 2012).

## 2.2.3 Entropic Redundancy

The derivation of this type of redundancy comes from statistical symbols distributions within given video sequences, instead of the contents of the images (BHASKARAN, 1997). For instance, the pixels movements among different frames related to the inter-frame redundancy have to be encoded using some binary representation. Furthermore, the statistics of whether there will be more zeros or ones for a given video sequence can be known prior to the encoding process and can be updated during the encoding. Hence, the symbols that are

more probable to occur will have shorter bit representation, whereas symbols that are less probable to occur will have a longer bit representation, saving bits at the final bitstream generation, without data loss. This type of redundancy is the focus of this Thesis since it is the concept behind the CABAC entropy algorithm within the HEVC standard.

#### 2.3 HEVC Video Coding Standard

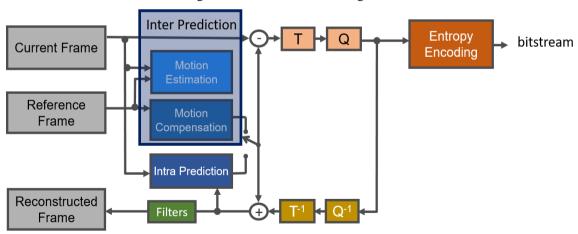

The HEVC video coding standard is a relatively recent alternative for digital video compression (ITU-T, 2013). It is the successor of H.264/AVC (ITU-T, 2003), where it achieves twice the coding capabilities of its predecessor, keeping the same visual subjective quality (SULLIVAN, 2012). The inception of HEVC standard is the result of a new era of High Definition (HD) video resolutions, demand for video streaming through the internet, and urge for better compression capabilities. The HEVC is a hybrid-block based standard (RICHARDSON, 2002), where it is composed by some macro-operations, based on the redundancies concepts presented before. Figure 2.5 depicts the block diagram of the generic HEVC encoder, where its blocks are: (i) Intra-prediction and inter-prediction (Motion Estimation and Motion Compensation) (ii) Transforms; (iii) Quantization; (iv) Filters; and (v) Entropy Encoding, which will be further explained.

Figure 2.5 – HEVC block diagram

Source: the author, modified from H.264/AVC diagram in (AGOSTINI, 2007).

One may notice that the HEVC encoder has Inverse Transform and Quantization steps, and then the filtering steps occur. The requirement of the inverse steps comes from the necessity to keep the same reference frames (i.e., with the same pixels values) to be used for redundancy discoveries when different frames are used (i.e., inter-frame redundancy). The reason for that is simple: Quantization step inserts losses in the encoding process (i.e., some

data after this step cannot be regenerated to their original value, as will be further explained). Hence, in case the currently processed frame is used as the reference for pixels of not-yet-processed frames in the decoder side, the same values have to be used at the encoder side, which implies the usage of the reconstructed frame after the losses insertion (i.e., after the Quantization step).

### 2.3.1 Coding Tree Units and Subdivisions

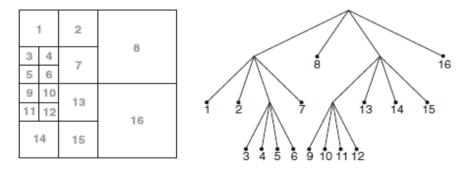

Frames are two-dimensional arrays of millions of pixels. Therefore, the HEVC splits the image into smaller blocks of pixels, and the encoding occurs at this level. The splitting starts at 64x64 group of pixels, whose name is Coding Tree Units (CTUs), but can also be groups of 32x32 and 16x16 pixels. The update comparing HEVC to the H.264/AVC is the inflation of the prior macro-blocks (block of 16x16 pixels) up to this new CTU abstraction maximum size. One of the reasons for the increase in the size of the CTU compared to the macro-blocks is the increase in the video resolutions of the new era of video processing (e.g., 4K, 8K) that did not exist at H.264/AVC development time. Thus, the 64x64 pixel structure is a more suitable approach for processing of this vast amount of pixels for Ultra High Definition (UHD) video resolutions (SZE, 2014).

The CTUs can be further split into smaller units, called Coding Units (CUs), which can be as large as the root CTU itself, or can be further split at the bottom level of 8x8 group of pixels, using the abstraction of a Coding Unit (CU) Tree structure. Hence, groups of pixels that present more similarities or correlations are processed together in order to achieve a more efficient redundancy finding process (which is called Prediction). Figure 2.6 depicts the possible values of CTUs and CUs divisions and sizes within the HEVC context and the correspondent CU Tree.

Figure 2.6 – Example of CUs division and CU tree structure

Source: (SZE, 2014).

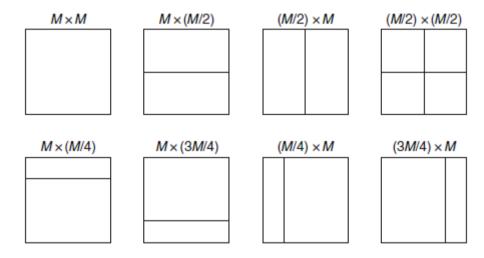

#### 2.3.2 Predictions

The Predictions are the process to find pixels that present more similarities with the currently processed set of pixels. The Prediction can either be within the same frame (i.e., intra-frame prediction) or among different frames (i.e., inter-frame prediction). The input to the prediction process is the Prediction Units (PUs) which are a group of pixels derived from the current processed CUs. Figure 2.7 illustrates the possible sizes for PUs in an inter-frame prediction process, which, as one may notice, could be Symmetric Motion Partitions (SMP) or Asymmetric Motion Partitions (AMP), where M is the dimension of a CU. The intra-prediction process allows only 2Mx2M and MxM divisions.

Figure 2.7 – PUs possible divisions

Source: (SZE, 2014).

### 2.3.2.1 Intra-frame Prediction

The intra-frame prediction uses pixels located at the same frame the current encoding pixels are (i.e., intra-frame redundancy). HEVC updates the prediction modes; allowing 35 directions to find the most suitable pixels to be used as the reference for the current processed ones (i.e., to find the pixel base color value that has more similarities with the current pixel). The intra-frame prediction will be used at the first frame of a given video sequence, or for random point access during video encoding process. Nevertheless, an HEVC encoder could support only intra-frame prediction, for instance, since HEVC defines only how the decoder has to work (i.e., the HEVC decoder has to support all possible configurations any given HEVC encoder may allow) (ITU-T, 2013).

#### 2.3.2.2 Motion Estimation

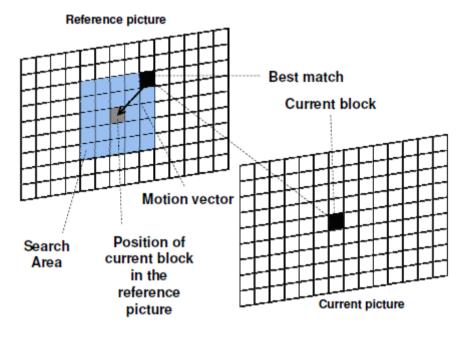

A pixel (or pixels) can change position across frames in a sequence. The inter-frame prediction is responsible for finding the more suitable groups of pixels in the different reference frame (or frames) that can be used as the reference value for the current group of pixels (i.e., the current PU). The process within the inter-frame prediction responsible for that is the Motion Estimation (ME). The ME tries to find the group of pixels in different frames where the difference of color values compared to the current PU is the minimal possible, if not zero. Therefore, the generation of a Motion Vector (MV) occurs, indicating the amount of motion (movement) the pixels at the other frames have dislocated compared to the current one (i.e., the change in the horizontal and vertical axis of the image). Figure 2.8 depicts the ME behavior. The ME is the most complex operation of HEVC encoder but is where most of the encoding gains occur (CHEN, 2007), (ZATT, 2011).

Figure 2.8 – ME behavior

Source: (PORTO, 2008),(DINIZ, 2015).

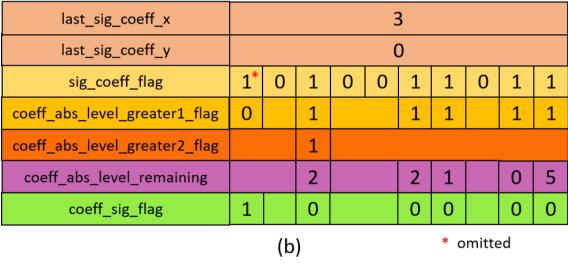

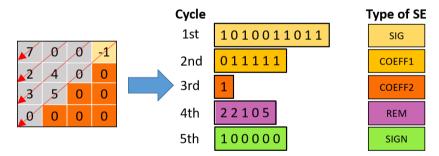

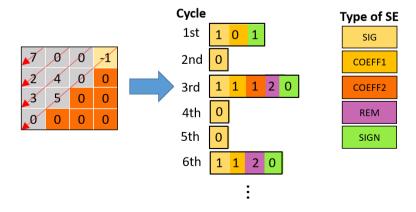

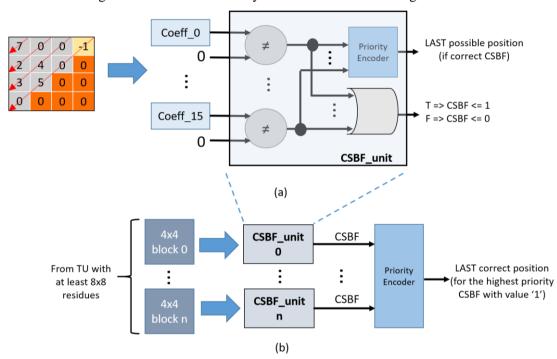

#### 2.3.2.3 Motion Compensation