# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

CEZAR RODOLFO WEDIG REINBRECHT

# Architectural Channel Attacks in NoC-based MPSoCs and its Countermeasures

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Advisor: Prof. Dr. Altamiro Amadeu Susin

Porto Alegre July 2017 Reinbrecht, Cezar Rodolfo Wedig

Architectural Channel Attacks in NoC-based MPSoCs and its Countermeasures / Cezar Rodolfo Wedig Reinbrecht. – Porto Alegre: PPGC da UFRGS, 2017.

146 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2017. Advisor: Altamiro Amadeu Susin.

1. MPSoC. 2. Hardware security. 3. Network-on-chip. 4. Side-channel attack. 5. NoC timing attack. I. Amadeu Susin, Altamiro. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PPGC: Prof. João Luiz Dihl Comba Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"The only truly secure system is one that is powered off, cast in a block of concrete and sealed in a lead-lined room with armed guards." — GENE SPAFFORD

### GREETINGS

I would like to thank everyone who, in one way or another, contributed to the research and writing of this thesis for my doctorate graduation in the Post-graduation Program in Computation (PPGC) of the Federal University of Rio Grande do Sul (UFRGS).

To my advisor, Prof. Dr. Altamiro Amadeu Susin, for his dedication, friendship, guidance and for his vision of the future that inspires many of his students. In spite of my partial dedication, Prof. Susin put a great effort to provide me everything I needed to succeed in the doctorate. Also, Prof. Susin looked for research opportunities during my doctorate, which culminated in the partnership with Dr. Johanna Sepulveda.

To my co-advisor, Profa. Dr. Johanna Sepúlveda, who played a vital role in the development of this research. During the development of the thesis, Dr. Sepulveda has contributed in many ways: i) by defining the directions of the research of the thesis, which was derived by its original publication "NoC-based Protection for SoC time-driven Attacks "at IEEE Embedded Systems Letters; ii) by proposing and discussing the threat model, attacks and security countermeasures; and iii) by engaging my intership at the Embedded System Security and Hardware Architecture group from Hubert Curien Laboratory at University of Lyon (France), headed by her partner Prof. Dr. Lilian Bossuet. In order to support this collaboration she contributed by co-writing the granted project: "Development and evaluation of traffic management techniques to avoid side-channel attacks on network-on-chip based multi-processors-system-on-chip" supported by The CNPQ Brazilian scholarship (1.12.2015 - 31.07.2016). Besides, I thank Dr. Sepúlveda for all patience and support during the hard deadlines and experiments.

To the other teachers who guided me and taught me during the postgraduate course: Tiago Balen, Marinho Barcellos, Sérgio Bampi, Ricardo Reis, Luigi Carro, Alexandre Bonatto, Gabriel Nazar, Rafael Iankowski, and Everton Carara.

I would like to thank the fellows of scientific initiation who contributed greatly to the development of the work, and I quote here Bruna Carvalho, Bruno Forlin, Paulo Kipper, Pedro Portugal, Ana L. Brodt, and Jefferson Johner. I thank also the friends of Lapsi in the post-gratuation, Fabio Irigon, Igor Hoelscher, Tiago Waszak, and Luft.

To my friends, who felt my absence, but nevertheless they continued always supporting me.

To my mother and sister, Lisete Beatriz Wedig Reinbrecht and Stéfani Karine Wedig Reinbrecht, who are responsible for the person I am and for the values and principles that I bring with me. They always supported me and helped me in what I needed to move on and pursue my dreams. To my relatives,

To my beautiful wife, Paula Cardoso Rodrigues Reinbrecht, who was always by my side, acting as my inspiration, and given me courage to face all adversities. Thank you for supporting even in the moments of absence, of anguish and of stress. Together we achieved another important step, and from now on we will face many others. Thank you for being my half.

To all, my sincere gratitude!

# ABSTRACT

Multi-Processors Systems-on-Chips (MPSoC) became the established hardware platform for a wide variety of applications and devices. Even more devices and systems will be interconnected by the Internet. The Internet link already brings several security concerns because all sensitive information stored on these devices can be reachable by external agents, and this prognostics will only increase the security issues. One of the most dangerous attacks is the Side Channel Attack (SCA). This type of attack explores features of the target system that reveals some secret or valuable data. This threat can be implemented physically through specialized instrumentation coupled directly to the device, or logical from architectural behavior accessed remotely through the network. The present thesis defines this particular logical SCA as a sub category called Architectural Channel Attack (ACA). This research project revised the bibliography to identify, analyze and explore the potential vulnerabilities of MPSoCs. The most vulnerable parts recognized were the shared cache and the Network-on-Chip (NoC). Within this knowledge, this thesis developed four new attacks aiming MPSoCs - Hourglass, Firecracker, Arrow, and Earthquake. Besides, the proposition that the hardware can provide security being transparent to applications resulted in a proposal of a hardware countermeasure, the Gossip NoC. The proposed attacks executed in a real MPSoC environment in an FPGA, breaking the Advanced Encryption Standard (AES). These evaluations were the first practical demonstration of an ACA performed in a NoC-based MPSoC entirely. The efficiency of different countermeasures, the Gossip NoC and three other ones from the literature, was evaluated under these attacks. Results showed that i) the shared cache and the NoC are critical vulnerabilities of complex MPSoCs; ii) the proposed attacks optimize the traditional cache ACAs found in literature making possible to attack even in limited environments; iii) the Earthquake makes the differential collision strategy feasible; iv) the NoC is a suitable candidate to implement security mechanisms, since it can access all elements in the system; v) the Gossip NoC avoids only one type of attack, but a protection mechanism for such complex systems demands multiple countermeasure strategies integrated to be a complete solution.

**Keywords:** MPSoC. hardware security. network-on-chip. side-channel attack. NoC timing attack.

# Ataques de Canal Arquitetural em MPSoCs baseados em NoCs e suas Contramedidas

#### RESUMO

Sistemas em Chip Multi-Processados (do inglês, MPSoCs) tornaram-se a plataforma de hardware estabelecida para uma ampla variedade de aplicações e dispositivos. Cada vez mais dispositivos e sistemas serão interligados pela Internet. A conexão com a Internet já traz várias preocupações de segurança, porque todas as informações confidenciais armazenadas nesses dispositivos podem ser acessadas por agentes externos, e esse prognóstico só aumentará as questões relacionadas à segurança. Um dos ataques mais perigosos é o Ataque de Canal Lateral (do inglês, SCA). Este tipo de ataque explora características do sistema de destino (informação indireta) que revela alguns dados secretos ou valiosos. Esta ameaça pode ser implementada fisicamente através de instrumentação especializada acoplada diretamente ao dispositivo, ou lógica pelo comportamento arquitetural que é acessado remotamente através da rede. Esta tese define este SCA lógico em particular como uma subcategoria chamada Ataque de Canal Arquitetural (do inglês, ACA). Este projeto de pesquisa revisou a bibliografia para identificar, analisar e explorar as potenciais vulnerabilidades dos MPSoCs. As partes mais vulneráveis reconhecidas foram as Caches compartilhadas e a Rede-em-Chip (do inglês, NoC). Uma vez adquirido este conhecimento, esta tese desenvolveu quatro novos ataques para MPSoCs - Hourglass, Firecracker, Arrow, e Earthquake. Além disso, a proposição de que o hardware pode fornecer segurança sendo transparente para aplicações culminou em uma proposta de uma contramedida de hardware, o Gossip NoC. Os ataques propostos foram executados em um ambiente real de MPSoC em um FPGA, quebrando a criptografia AES. Estes experimentos práticos foram a primeira demonstração de um ACA realizado em um MPSoC baseado em NoC. A eficiência de diferentes contra-medidas foi avaliada sob estes ataques. Os resultados mostraram que i) a Cache compartilhada e a NoC são vulnerabilidades críticas em MPSoCs; ii) os ataques propostos otimizam os ACAs tradicionais de Cache encontrados na literatura; iii) o Earthquake torna viável a estratégia de colisão diferencial; iv) a NoC é uma candidata adequada para implementar mecanismos de segurança; v) a Gossip NoC evita apenas um tipo de ataque.

**Palavras-chave:** MPSoC, Segurança, Ataque de Canal Lateral, Rede-em-Chip, Sistemaem-Chip, Timing Attack, NoC Timing Attack, NoC Segura..

# LIST OF ABBREVIATIONS AND ACRONYMS

- 3DIC Three Dimension Integrated Circuit

- ACA Architectural Channel Attack

- AES Advanced Encryption Standard

- API Application Programming Interface

- ASIC Application Specific Integrated Circuit

- ASLR Address Space Layout Randomization

- BP Bad Positive

- CAESAR Competition for Authenticated Encryption: Security, Applicability, and Robustness

- CMOS Complementary Metal Oxide Semiconductor

- CPU Central Processing Unit

- DES Data Encryption Standard

- DPA Differential Power Analysis

- DSP Digital Signal Processing

- DTA Distributed Timing Attack

- EM Electromagnetic

- EtM Encrypt-then-MAC

- FP False Positive

- FPGA Field Programmable Gate Array

- GCM Galois Counter Mode

- GPU Graphical Processor Unit

- HAL Hardware Abstraction Layer

- IC Integrated Circuit

- ICC International Chamber of Commerce

- IDE Integrated Development Environment

| IoE         | Internet-of-Everything                             |

|-------------|----------------------------------------------------|

| IoT         | Internet-of-Things                                 |

| IP          | Intelectual Property                               |

| IT          | Information Technology                             |

| ITRS        | International Technology Roadmap for Semiconductor |

| KSM         | Kernel Samepage Merging                            |

| L1          | Level one                                          |

| L2          | Level two                                          |

| LLC         | Last Level Cache                                   |

| Malware     | Malicious Software                                 |

| MLS         | Multi-Level Security                               |

| MPSoC       | Multi-Processor System-on-Chip                     |

| NI          | Network Interface                                  |

| NIST        | National Institute of Standards and Technology     |

| NoC         | Network-on-Chip                                    |

| OS          | Operating System                                   |

| P+P         | Prime+Probe                                        |

| PA          | Power Analysis                                     |

| PUF         | Physically Unclonable Functions                    |

| QoS         | Quality of Service                                 |

| RR          | Round-Robin                                        |

| SCA         |                                                    |

|             | Side Channel Attack                                |

| SER         | Side Channel Attack<br>Secure-enganced-router      |

| SER<br>SLAT |                                                    |

|             | Secure-enganced-router                             |

| SPI  | Serial Peripheral Interface                 |

|------|---------------------------------------------|

| SSL  | Secure Sockets Layer                        |

| TA   | Timing Attack                               |

| TDM  | Time-Division Multiplexing                  |

| TNP  | Temporal Network Partitioning               |

| TP   | True Positive                               |

| TPS  | Transparent Page Sharing                    |

| TSV  | Through Silicon Via                         |

| UART | Universal Asynchronous Receiver Transmitter |

| VLIW | Very Large Instruction Word                 |

| VM   | Virtual Machine                             |

| WFRL | West First Routing Logic                    |

| XOR  | Exclusive-Or                                |

# LIST OF FIGURES

| Figure 2.1 AES-128 encryption diagram, representing the main operations exe-              |      |

|-------------------------------------------------------------------------------------------|------|

| cuted over the iterative process of ten rounds                                            | 31   |

| Figure 2.2 Memory organization strategies in MPSoCs: Shared, Distributed, and             |      |

| Shared Distributed.                                                                       |      |

| Figure 2.3 NoC topologies examples. a) Mesh; b) Torus; c) Ring; and d) Tree               | 37   |

| Figure 2.4 Software Architectures. a) Full; b) Partial; c) Bare-metal                     | 40   |

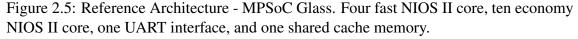

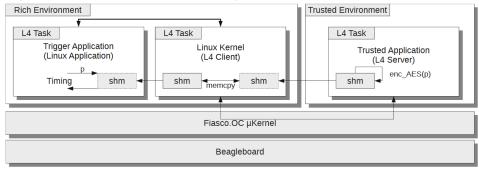

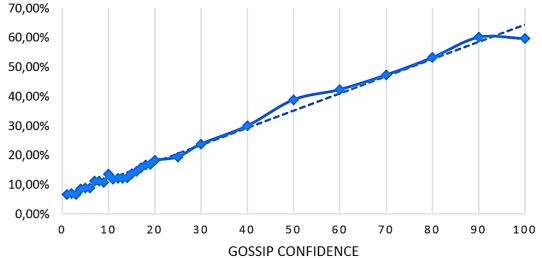

| Figure 2.5 Reference Architecture - MPSoC Glass. Four fast NIOS II core, ten              |      |

| economy NIOS II core, one UART interface, and one shared cache memory                     | 42   |

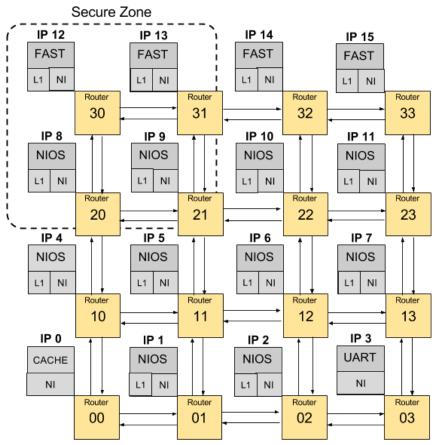

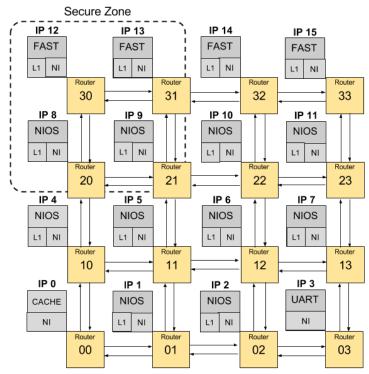

| Figure 3.1 Profiling Phase - Signature of the position 0.                                 | 46   |

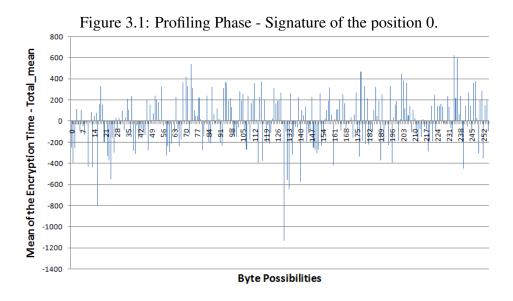

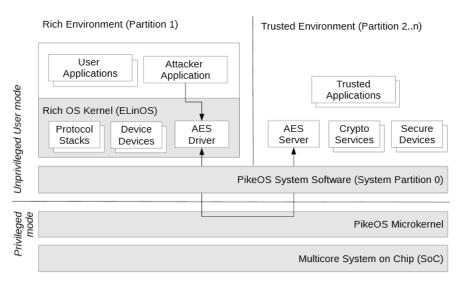

| Figure 3.2 Rich operating system making an system call to the trusted operating           |      |

| system. Source: (WEISS; HEINZ; STUMPF, 2012).                                             | 48   |

| Figure 3.3 Communication between partitions inside PikeOS. Source: (WEISS et              |      |

|                                                                                           | 49   |

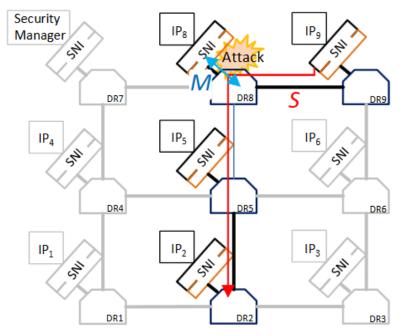

| Figure 3.4 Malicious software M performing the NoC timing attack. The sensitive           |      |

| traffic S is the victim. Source: (SEPULVEDA et al., 2016)                                 | 59   |

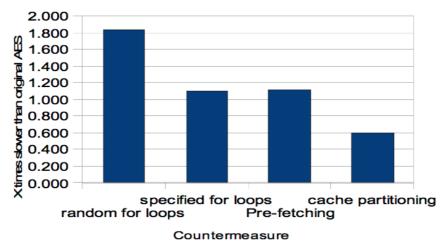

| Figure 3.5 Latency overhead of software-based countermeasures against cache tim-          |      |

| ing attacks. Source: (ALAWATUGODA; JAYASINGHE; RAGEL, 2011)                               | 61   |

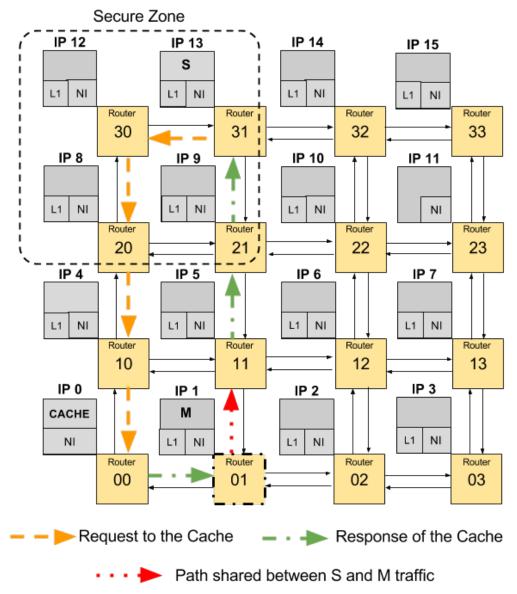

| Figure 4.1 Example scenario of a NoC timing attack running in an MPSoC                    | 68   |

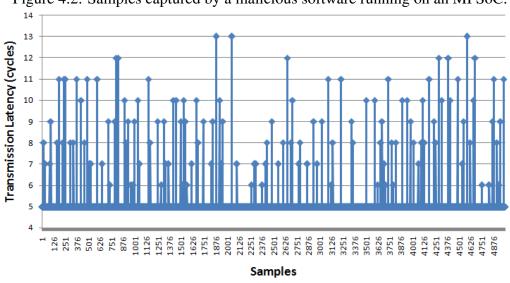

| Figure 4.2 Samples captured by a malicious software running on an MPSoC                   |      |

| Figure 4.3 Flowchart of the five steps to perform the NoC Timing Attack.                  | 71   |

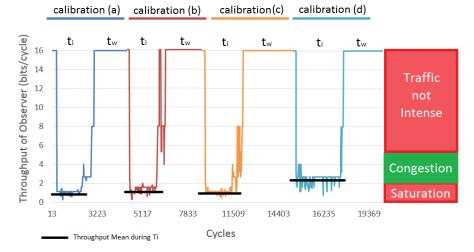

| Figure 4.4 Throughput Trace sensed by attacker of four calibration scenarios: a)          |      |

| Injection rate of 70%; b) Injection rate of 50%; c) Injection rate of 40%; d)             |      |

| Injection rate of 30%                                                                     | 72   |

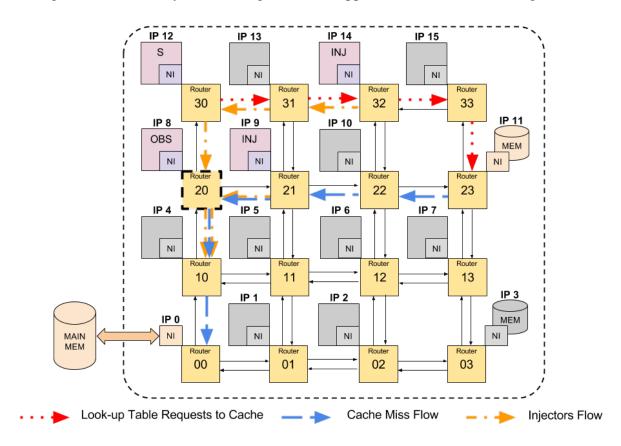

| Figure 4.5 MPSoC system running a sensitive application, after infection stage            | 74   |

| Figure 4.6 Placement experiment scenarios. The dashed routers are the experiment          |      |

| targets. $S$ is the source and $D$ the destination of the sensitive traffic. High-        |      |

| lighted arrows shows the allowed route at each scenario.                                  | 77   |

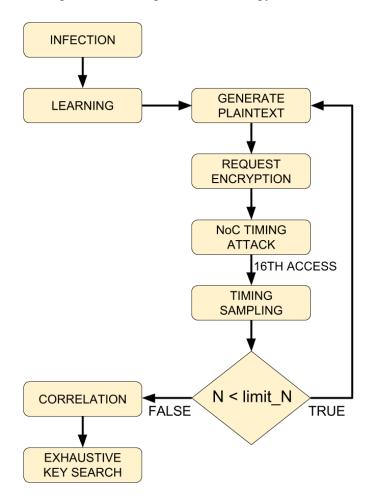

| Figure 5.1 Hourglass methodology flowchart.                                               | 83   |

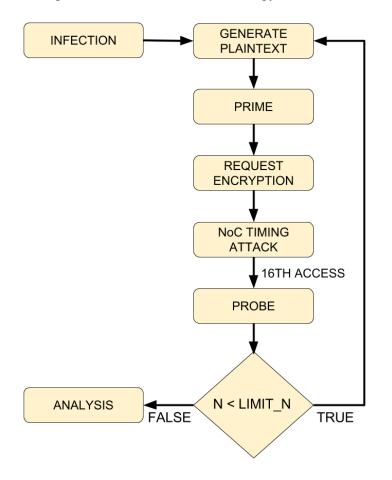

| Figure 5.2 Firecracker methodology flowchart.                                             |      |

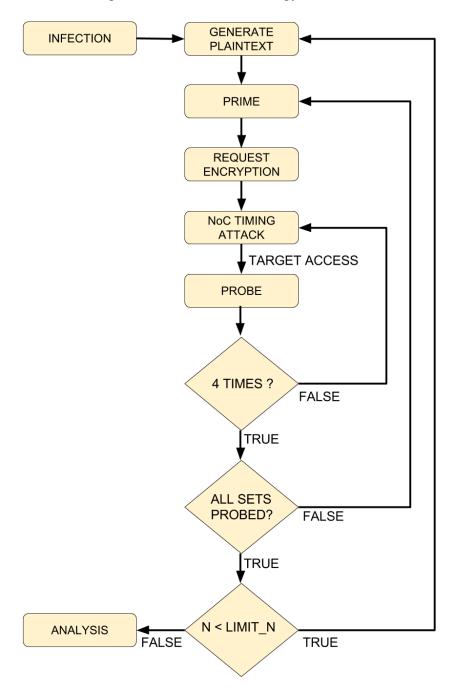

| Figure 5.3 Arrow methodology flowchart.                                                   |      |

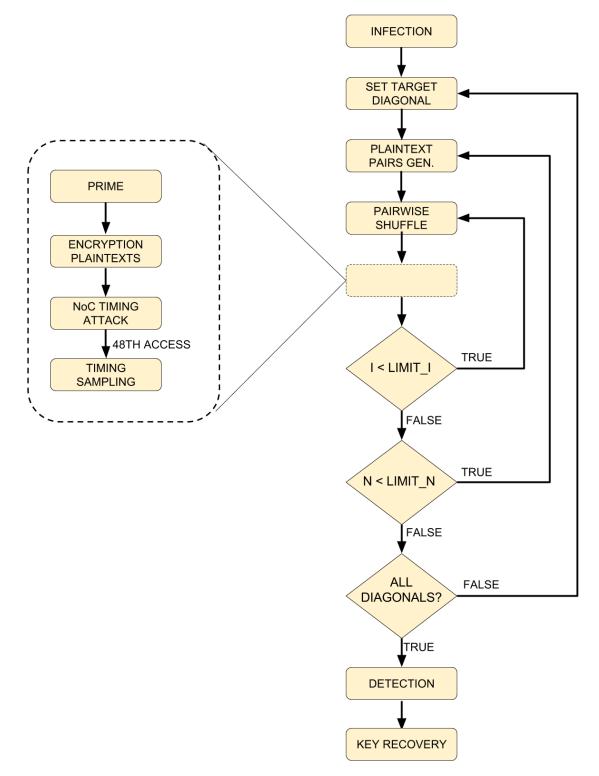

| Figure 5.4 Earthquake methodology flowchart                                               |      |

|                                                                                           |      |

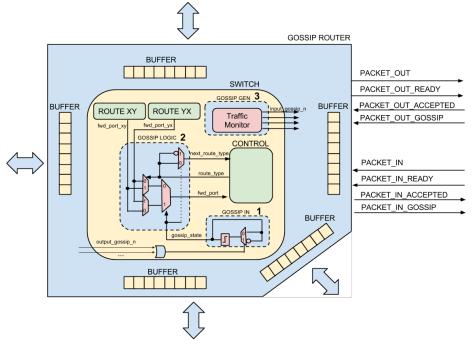

| Figure 6.1 <i>Gossip router</i> microarchitecture: (1) Gossip In Block; (2) Gossip Logic; |      |

|                                                                                           | 96   |

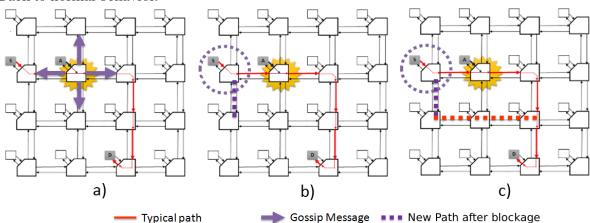

| Figure 6.2 <i>Gossip NoC</i> functionality: (a) Gossip Messages; (b) Routing changing;    |      |

| (c) Back to normal behavior                                                               | 97   |

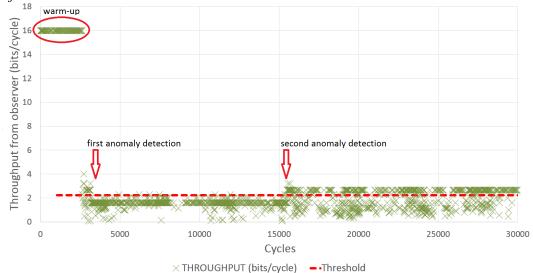

| Figure 6.3 Trace throughput of the distributed timing attack under Gossip NoC.            |      |

| Gossip confidence of 1                                                                    |      |

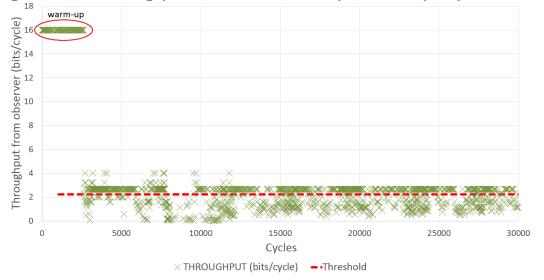

| Figure 6.4 Trace throughput of the DTA under Gossip NoC. Gossip confidence of 10          | )99  |

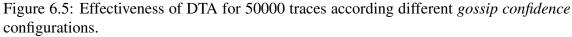

| Figure 6.5 Effectiveness of DTA for 50000 traces according different gossip confi-        |      |

| dence configurations.                                                                     | .100 |

| Figure 7.1 Reference Architecture - MPSoC Glass. Four fast NIOS II core, ten              |      |

| economy NIOS II core, one UART interface, and one shared cache memory                     | 103  |

|                                                                                           | .105 |

| Figure 7.2 Learning phase - Byte 0 signature.                                             |      |

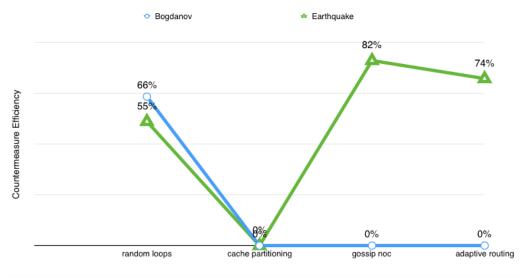

| Figure 7.4 Countermeasures Evaluation under timing-based attacks. Two cache-       |

|------------------------------------------------------------------------------------|

| and two NoC- protections techniques were evaluated                                 |

| Figure 7.5 Osvik (Prime+Probe), Firecracker, and Arrow attack results. Arrow was   |

| performed in a fast and a slow scenario111                                         |

| Figure 7.6 Countermeasures Evaluation under access-based attacks. Two cache-       |

| and two NoC- protections techniques were evaluated                                 |

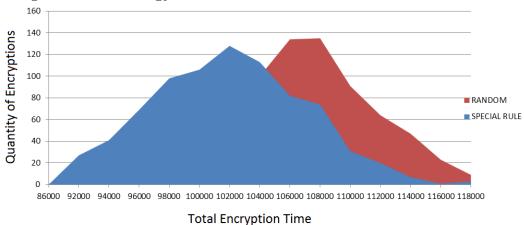

| Figure 7.7 Histogram of the encryption times of pairs of plaintexts generated by a |

| random and Bogdanov's rule strategy115                                             |

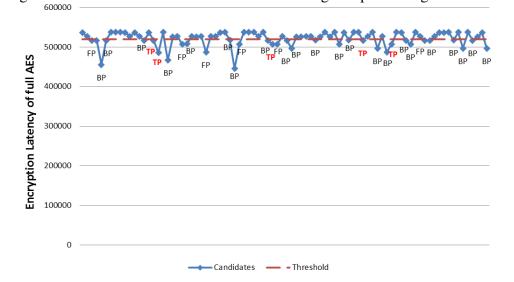

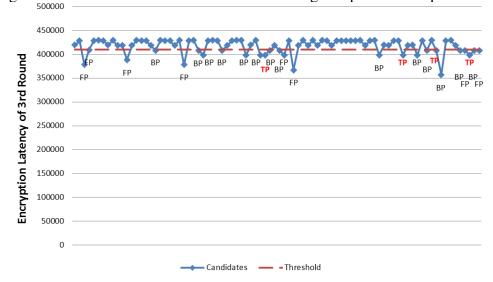

| Figure 7.8 Detection candidates of the online stage output of Bogdanov attack116   |

| Figure 7.9 Detection candidates of the online stage output of Earthquake attack118 |

| Figure 7.10 Countermeasures Evaluation under collision-based attacks. Two cache-   |

| and two NoC- protections techniques were evaluated                                 |

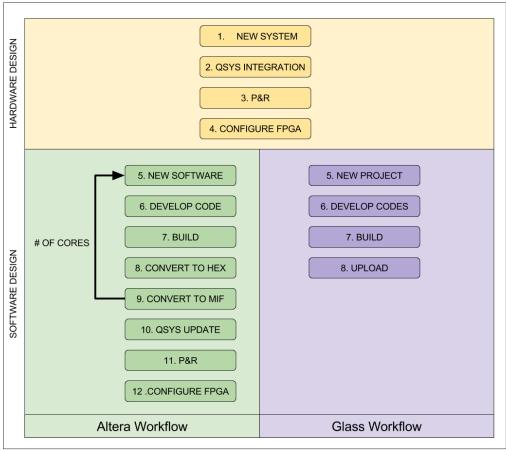

| Figure 11.1 Nios II Embedded System Design and MPSoC Glass Flowcharts              |

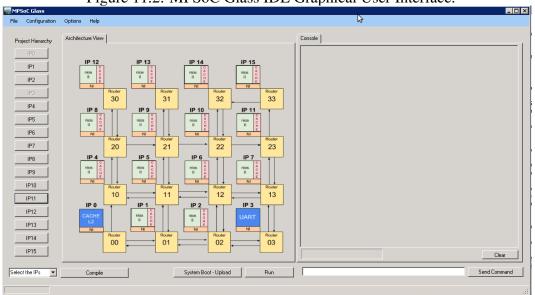

| Figure 11.2 MPSoC Glass IDE Graphical User Interface                               |

# LIST OF TABLES

| Table 2.1 Proposed Side Channel Attacks Classification                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.2 Summary of MPSoC architectures.    41                                                                                                                                         |

| Table 2.3 FPGA Cyclone IV GX synthesis results of the MPSoC Glass components43                                                                                                          |

| Table 3.1 Number of measurements to implement the attack on different mobile phone devices.    49                                                                                       |

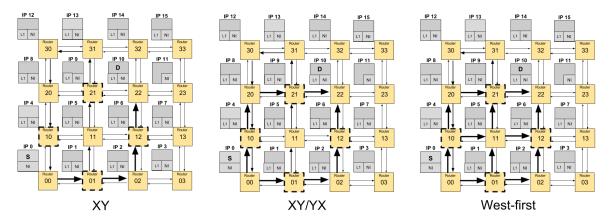

| Table 4.1 Detection efficiency and false-positives of the NoC timing attack under six different scenarios. Each scenario used a different interference period. System running at 100MHz |

| Table 4.2 Placement experiments results under three routing algorithms                                                                                                                  |

| Table 4.3 Distributed Timing Attack under west-first routing algorithm                                                                                                                  |

| Table 4.4 Relation between packet size and detection rate                                                                                                                               |

| Table 6.1 Effectiveness (% of matches) of DTA using a threshold of 2.23 bps under      Gossip NoC.                                                                                      |

| Table 6.2 Effectiveness (% of matches) of DTA using a threshold of 2.23 bps underGossip NoC. Gossip confidence of 10                                                                    |

| Table 6.3 Synthesis results for the Unprotected and Gossip routers for 65 nm ASIC technology.      100                                                                                  |

| Table 7.1Setup of the experiments on the following attacks: Bernstein, Hourglass,<br>Prime+Probe, Firecracker, Bogdanov and Earthquake                                                  |

| Table 7.2 Setup of the experiments on Arrow attack.       104                                                                                                                           |

| Table 7.3 Approximate execution time of the attacks, during the execution of the                                                                                                        |

| attack (online time), and after in the post-processing step (offline time)                                                                                                              |

# LIST OF CODES

| 7.1 A | Adapted C code of the Timing Attack.                                          | .104 |

|-------|-------------------------------------------------------------------------------|------|

| 7.2 I | Data reception and first key byte analysis of Prime+Probe/Firecracker code in |      |

|       | Python                                                                        | .109 |

| 7.3 H | Key search stage code in C.                                                   | .116 |

| 11.1  | Code to call external compiler to the Cross-compilation task                  | .141 |

| 12.1  | Functions provided by NoC API                                                 | .143 |

| 12.2  | Source code of NoC services.                                                  | .143 |

| 12.3  | Functions provided by Crypto API                                              | .145 |

| 12.4  | Source code of Crypto services                                                | .145 |

# CONTENTS

| 1 INTRODUCTION                                                                                                                            | .18                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 1.1 Motivation                                                                                                                            | .22                                                                |

| 1.2 The Thesis                                                                                                                            | .22                                                                |

| 1.3 Objectives                                                                                                                            |                                                                    |

| 1.4 Methodology                                                                                                                           | .23                                                                |

| 1.5 Structure of the Thesis                                                                                                               |                                                                    |

| 2 BASIC CONCEPTS                                                                                                                          | .25                                                                |

| 2.1 Hardware Security                                                                                                                     |                                                                    |

| 2.1.1 Side Channel Attacks                                                                                                                |                                                                    |

| 2.1.2 Proposed SCA Classification                                                                                                         | .28                                                                |

| 2.2 Cryptographic Engineering                                                                                                             | .29                                                                |

| 2.2.1 Advanced Encryption Standard - AES                                                                                                  | .30                                                                |

| 2.2.1.1 Encryption Process                                                                                                                | .30                                                                |

| 2.2.1.2 Decryption Process                                                                                                                | .32                                                                |

| 2.2.2 Performance-oriented AES                                                                                                            | .32                                                                |

| 2.2.3 Crypto-libraries                                                                                                                    | .33                                                                |

| 2.3 Multi-processors Systems-on-Chip                                                                                                      | .34                                                                |

| 2.3.1 Architecture Model                                                                                                                  | .35                                                                |

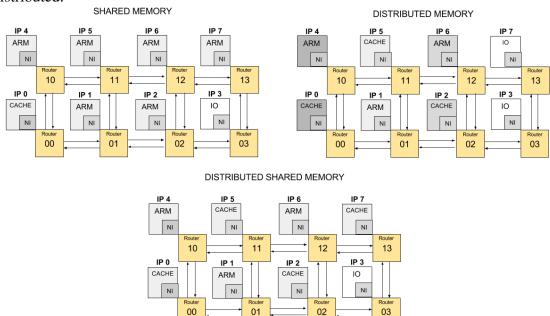

| 2.3.2 Memory Model                                                                                                                        | .35                                                                |

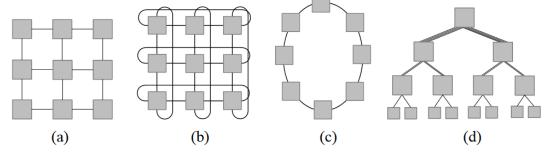

| 2.3.3 Communication Model - Network-on-Chip                                                                                               | .36                                                                |

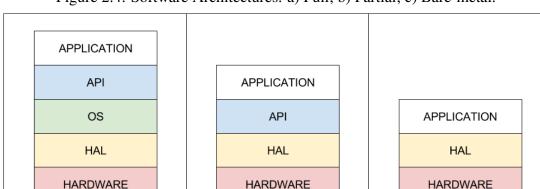

| 2.3.4 Software Architecture                                                                                                               | .39                                                                |

| 2.3.5 MPSoC Examples                                                                                                                      | .40                                                                |

| 2.3.6 Reference Architecture - MPSoC Glass                                                                                                | .40                                                                |

| 2.3.6.1 Hardware Costs                                                                                                                    | .43                                                                |

| 2.4 Considerations                                                                                                                        | .43                                                                |

| 3 STATE-OF-THE-ART                                                                                                                        | .44                                                                |

| 3.1 Cache Attacks                                                                                                                         | .44                                                                |

| 3.1.1 Timing-based Cache Attacks                                                                                                          | .44                                                                |

| 3.1.1.1 Bernstein's Attack                                                                                                                | .45                                                                |

| 3.1.1.2 Neve's Optimization                                                                                                               | .47                                                                |

| 3.1.1.3 Application: Virtualized Embedded Environments                                                                                    |                                                                    |

| 3.1.1.4 Application: Mobile phone devices                                                                                                 | .48                                                                |

| 3.1.1.5 Application: Virtualized Cloud Environments                                                                                       | .50                                                                |

|                                                                                                                                           |                                                                    |

| 3.1.2 Access-based Cache Attacks                                                                                                          |                                                                    |

| 3.1.2 Access-based Cache Attacks<br>3.1.2.1 Prime+Probe Attack                                                                            | .51                                                                |

|                                                                                                                                           |                                                                    |

| 3.1.2.1 Prime+Probe Attack                                                                                                                | .52                                                                |

| <ul><li>3.1.2.1 Prime+Probe Attack</li><li>3.1.2.2 Xinjie et al. Optimization</li></ul>                                                   | .52<br>.53                                                         |

| <ul><li>3.1.2.1 Prime+Probe Attack</li><li>3.1.2.2 Xinjie et al. Optimization</li><li>3.1.2.3 Application: Last Level Caches</li></ul>    | .52<br>.53<br>.53                                                  |

| <ul> <li>3.1.2.1 Prime+Probe Attack</li> <li>3.1.2.2 Xinjie et al. Optimization</li> <li>3.1.2.3 Application: Last Level Caches</li></ul> | .52<br>.53<br>.53<br>.54                                           |

| <ul> <li>3.1.2.1 Prime+Probe Attack</li></ul>                                                                                             | .52<br>.53<br>.53<br>.54<br>.55                                    |

| <ul> <li>3.1.2.1 Prime+Probe Attack</li></ul>                                                                                             | .52<br>.53<br>.53<br>.54<br>.55<br>.57                             |

| <ul> <li>3.1.2.1 Prime+Probe Attack</li></ul>                                                                                             | .52<br>.53<br>.53<br>.54<br>.55<br>.57<br><b>.58</b>               |

| <ul> <li>3.1.2.1 Prime+Probe Attack</li></ul>                                                                                             | .52<br>.53<br>.53<br>.54<br>.55<br>.57<br><b>.58</b><br>.58        |

| <ul> <li>3.1.2.1 Prime+Probe Attack</li></ul>                                                                                             | .52<br>.53<br>.53<br>.54<br>.55<br>.57<br>.57<br>.58<br>.58<br>.58 |

| <ul> <li>3.1.2.1 Prime+Probe Attack</li></ul>                                                                                             | .52<br>.53<br>.54<br>.55<br>.57<br>.58<br>.58<br>.58<br>.59<br>.60 |

| <ul> <li>3.1.2.1 Prime+Probe Attack</li></ul>                                                                                             | .52<br>.53<br>.54<br>.55<br>.57<br>.58<br>.58<br>.58<br>.60<br>.60 |

| 3.4.3 Sepúlveda et al Random Arbitration and Adaptive Routing NoC       |    |

|-------------------------------------------------------------------------|----|

| 3.4.4 Sepúlveda et al SER                                               |    |

| 3.4.5 Stefan and Goossens NoC                                           | 64 |

| 3.5 Considerations                                                      |    |

| 4 EXPLORING THE NOC TIMING ATTACK                                       | 67 |

| 4.1 Understanding the NoC Leakage                                       | 67 |

| 4.2 Threat Model                                                        | 69 |

| 4.3 Attack Methodology                                                  | 70 |

| 4.3.1 Calibration                                                       |    |

| 4.4 Expanding the Attack to a Distributed Attack                        |    |

| 4.5 Evaluation                                                          |    |

| 4.5.1 Traffic Interference                                              |    |

| 4.5.2 Placement in the Network                                          |    |

| 4.5.3 Size of the Packet                                                |    |

| 4.6 Considerations                                                      |    |

| 5 DEVELOPED ATTACKS                                                     |    |

| 5.1 Hourglass Attack                                                    |    |

| 5.1.1 Threat Model                                                      |    |

| 5.1.2 Attack Methodology                                                |    |

| 5.2 Firecracker Attack                                                  |    |

| 5.2.1 Threat Model                                                      |    |

| 5.2.2 Attack Methodology                                                |    |

| 5.3 Arrow Attack                                                        |    |

| 5.3.1 Threat Model                                                      |    |

| 5.3.2 Attack Methodology                                                |    |

| 5.4 Earthquake Attack                                                   |    |

| 5.4.1 Threat Model                                                      |    |

| 5.4.2 Attack Methodology                                                |    |

| 5.5 Considerations<br>6 PROPOSED PROTECTION                             |    |

| 6.1 Gossip Network-on-Chip                                              |    |

| 6.1.1 Architecture                                                      |    |

|                                                                         |    |

| <ul><li>6.1.2 Functionality</li><li>6.2 Gossip NoC Evaluation</li></ul> |    |

| 6.3 Considerations                                                      |    |

| 7 EXPERIMENTAL STUDY                                                    |    |

| 7.1 Experimental Setup                                                  |    |

| 7.1 Experimental Setup                                                  |    |

| 7.2.1 Bernstein Adaptation                                              |    |

| 7.2.2 Attacks Evaluation                                                |    |

| 7.2.3 Countermeasures Evaluation                                        |    |

| 7.3 Access-based Attack Experiments                                     |    |

| 7.3.1 Attacks Evaluation                                                |    |

| 7.3.2 Countermeasures Evaluation                                        |    |

| 7.4 Collision-based Attack Experiments                                  |    |

| 7.4.1 Analysis on the Differential Collision Cache Attack               |    |

| 7.4.2 Attacks Evaluation                                                |    |

| 7.4.3 Bogdanov Evaluation                                               |    |

| 7.4.4 Earthquake Evaluation                                             |    |

| 7.4.5 Countermeasures Evaluation                                        |    |

| 7.5 Considerations                                                      |    |

| 8 CONCLUSION                               |     |

|--------------------------------------------|-----|

| 9 CONTRIBUTIONS OF THE THESIS              |     |

| 10 FUTURE WORKS AND RESEARCH OPPORTUNITIES |     |

| REFERENCES                                 |     |

| 11 MPSOC GLASS IDE                         |     |

| 11.1 Altera Design Flow                    |     |

| 11.2 Glass Flow                            |     |

| 11.3 MPSoC Glass IDE                       |     |

| 11.3.1 Cross-compilation Feature           |     |

| 11.3.2 Binaries Upload Feature             |     |

| 12 MPSOC GLASS API                         |     |

| 12.1 NoC Communication Services            |     |

| 12.2 Cryptography Services                 | 145 |

# **1 INTRODUCTION**

Systems-on-Chip (SoC) is a computational system assembled in a single chip. SoCs are composed of software and hardware components, such as operating systems, processors, memories, accelerators (co-processors), among several elements (MEYR, 1997). SoC is the hardware platform of several types of applications, from conventional electronic devices (appliances) to high-performance servers. This complete solution inside the same silicon has fewer costs to the final product because it does not need extra components. Furthermore, few components result in fewer energy requirements, a key feature for the current technology trends, such as the mobile segment.

Although SoCs became a standard on electronic devices, the market has been increasing the demand for more performance, power efficiency and flexibility to run different applications. As a result, a new architectural concept was proposed as a promising platform, the Multi-Processor System-on-Chip (MPSoC) (CHEN et al., 2009). This system brings the potential of high parallelism as the novelty. MPSoCs are SoCs composed of several processing elements. These processors can be assembled with identical or different architectures, being homogeneous or heterogeneous respectively. According to ITRS 2015 (International Technology Roadmap for Semiconductor of 2015), by 2029 just the mobile segment will integrate over 300 elements, between application processors and graphical processor units (GPUs) (ITRS, 2016). Therefore, the MPSoC will improve the performance through the parallelism, software flexibility through the heterogeneity and power reduction through less external hardware requirements.

In the recent past, the Internet was mostly used as a means of collecting information and communications. Progressively it evolved into a commercial instrument, where the users could book services, acquire goods, pay bills and so on. Then, different types of cameras and sensors began to be connected to the Internet resulting in novel uses and applications. At present the Internet of Things allows objects to be sensed and controlled remotely across existing network infrastructure, creating opportunities for more direct integration between the physical world and computer-based systems and resulting in improved efficiency, accuracy, and economic benefit.

As the list of elements that can be connected to the Internet keeps on increasing a new term has been proposed: The Internet of Everything (IoE). The term IoE expands on the concept of the "Internet of Things" in that it connects not just physical devices but quite literally everything by getting them all on the network (CHANDHOK, 2014). IoE works to connect more devices to the network, stretching out the edges of the network and expanding the roster of what can be connected. IoE has a major play in all industries, from retail to telecommunications to banking and financial services. However, placing all this personal information on the web or accessible via the web poses a severe challenge for security (KOMAR; EDELEV; KOUCHERYAVY, 2016). Almost every day we can hear news of hackers stealing valuable information, and it is imperative that appropriate measures are taken to prevent these problems, but despite this more and more people are willing to "venture" in the IoE since the benefits offered by the many capabilities provided by the IoE are overwhelming. Power consumption, electromagnetic radiation (EM) or hot spots Nowadays, Systems-on-Chip already is an object of attacks, and Side Channel Attack (SCA) is one of the most used techniques (KARRI et al., 2001). This type of attack employs features of the target system that reveals indirect information (leakage) about some secret or important data. This attack can be made physically through specialized instrumentation coupled directly to the device, extracting thermal (HUTTER; SCHMIDT, 2014), power (KOCHER; JAFFE; JUN, 1999; GEBOTYS; GEBOTYS, 2003; MASOOMI; MASOUMI; AHMADIAN, 2010; ORS et al., 2004) or electromagnetic (GANDOLFI; MOURTEL; OLIVIER, 2001) information. The collected information can be used to infer cryptographic keys, source code of proprietary software, digital certificates and other sensitive information (BAYON et al., 2012) (MORADI; MISCHKE; PAAR, 2013). New attacks have explored increasingly timing, access patterns, scheduling and faults to implement SCAs. These characteristics are not physical but logical from architectural behavior. This thesis defines this particular type of SCA as a subcategory called Architectural Channel Attack (ACA). Attacks that targets the behavior features are more suitable and effective for complex hardware systems, like SoCs and MPSoCs. The main reasons are:

- ACAs do not demand high specialized instrumentation;

- ACAs has no need to access the target device directly;

- High parallelism running on MPSoCs adds a significant noise for the physical measurements, such as power, EM, etc.;

- More structural complexity represent more potential leakage sources.

Cache memory is the most explored resource of SoCs for attacks, where timing, access pattern or trace are examples of leakage sources (BOGDANOV et al., 2010). Most cache attacks take advantage of the fact that the cache miss and cache hit are keydependent events with some cryptographic systems (SEPULVEDA et al., 2015). First cache attack proposals retrieved the key of different ciphers implementations, such as Data Encryption Standard (DES), RSA or Advanced Encryption Standard (AES) (KOCHER, 1996) (KELSEY et al., 1998) (TSUNOO et al., 2003) (BERNSTEIN, 2005) (OSVIK; SHAMIR; TROMER, 2006). Trace-based attacks are not considered in the scope of this research because they require a great level of information of the system, considered not possible (BOGDANOV et al., 2010). Therefore, we aimed access-based and timing-based cache attacks.

Regarding access-based attack, it infers the memory positions accessed during a cryptographic cipher operation by the time to access the data. One of the most efficient techniques is the Prime+Probe, proposed by Osvik et al. (OSVIK; SHAMIR; TROMER, 2006). In the same work, Osvik introduced the Evict+Flush and an asynchronous approach. The works of (XINJIE et al., 2008) (YOUNIS et al., 2015) (LIU et al., 2015) (OREN et al., 2015) optimized the access-based technique by Osvik or applied in different computational environments.

A timing-based attack observes the total execution time of a cryptographic cipher operation. The number of misses and hits of the cache result in a difference between latency responses. The timing attack proposed by Bernstein (BERNSTEIN, 2005) is a generic timing-based attack. The works of (NEVE; SEIFERT; WANG, 2006) (WEISS; HEINZ; STUMPF, 2012; WEISS et al., 2014) (SPREITZER; PLOS, 2013) (SPREITZER; GéRARD, 2014) (IRAZOQUI et al., 2014) optimized the timing-based technique of Bernstein. Then, some authors, like (BONNEAU; MIRONOV, 2006) and (BOGDANOV et al., 2010), proposed an optimization of the timing attack by manipulating the input data to provoke cache hits. This method is called collision timing attack. Bogdanov (BOGDANOV et al., 2010) presented a differential collision attack that explores the collisions generated by pairs of encryptions in sequence.

All the methods mentioned above was performed remotely to attack servers or remote computers. These attacks had to consider the target computer system and communication behavior besides the SoC architecture. Hence, the accuracy of the attack is compromised, due to communication and system interferences. Moreover, these attacks on MPSoC based devices face much more challenges, due to novel architectures features. One feature is the secure zone (SEPULVEDA; FLOREZ; GOGNIAT, 2015) (SEPUL-VEDA et al., 2014), where it is not possible to run a spy application in the victim CPU. The attack of Osvik uses the spy process strategy. Another architecture feature is the

usage of specific application IPs in the system. These specialized hardware functions are shared among several processors. Then, its behavior becomes not exclusive from the target process. For instance, a shared IP responsible for the network interface could increase the timing noise of remote protocols, like the Secure Sockets Layer (SSL) used by Bernstein's and Bogdanov's attacks. This work presents for the first time Architectural Channel Attacks implemented entirely inside the chip improving the attacks efficiency and decreasing data storage requirements.

Regarding attacks running inside the system, previous works considered that traffic patterns from Network-on-Chips (NoCs) could be exploited inside the MPSoC (YAO; SUH, 2012) (WASSEL et al., 2014) (SEPULVEDA et al., 2015). They mention that the NoC could leak information through the latency or throughput of the transfers. This ACA was called NoC timing attack. Each work also proposed a protection mechanism designed in the NoC architecture. Therefore, these authors did a remarkable contribution to the field of hardware security, pointing out the vulnerabilities and protection potentials of the NoC.

However, the state-of-the-art of ACAs did not comprehended attacks performed entirely inside the SoC or MPSoC, only describing the possibility of internal vulnerabilities. This research project has investigated the main ACAs related to cache and NoC inside MPSoCs to understand its feasibility and propose new threats. As a consequence, chapter six presents four developed attacks that breaks the AES cryptography. The first is the Hourglass, an adaptation of the timing-based attack from Bernstein, combined with a NoC timing attack. Then, the second and third are Firecracker and Arrow attacks, inspired in the Prime+Probe attack from Osvik integrated to a NoC timing attack. The fourth is Earthquake attack; that implements a differential collision attack with NoC timing attack.

The knowledge of MPSoCs vulnerabilities became possible to propose a security mechanisms. Chapter seven presents a secure enhanced NoC architecture, the Gossip NoC. This NoC targets sufficient protection with minimum area and performance penalties.

In summary, the present thesis sustains that MPSoCs, as the promising platform for future systems, have critical vulnerabilities in the shared cache and NoC, which can be worst if both are combined. Moreover, this thesis enforces that structures inside the NoC can implement some MPSoC security, and more research around this area should be addressed. Therefore, this research aims to deeply study ACAs in NoC-based MPSoCs, to develop and present with practical experiments MPSoCs vulnerabilities; and to show that the NoC can perform protection mechanisms.

#### 1.1 Motivation

Our project has technical, scientific and socio-economic relevance. Security in computer systems is a growing concern of society and the widespread use of SoCs in several electronic applications, such as smartphones and tablets, makes this issue even more critical.

The technical and scientific relevance rely on the fact that security is a key topic on enabling the electronics evolution. This subject is a target of recent studies of several research groups. Moreover, ACA has recently been proposed as a feasible attack, which leads to the fact that most devices are vulnerable. Our work in this topic will contribute to the scientific community with the first deep study of ACA implemented in MPSoCs and NoC-based protections. It is expected that the results of this project could be adopted by the national and international industry.

The socio-economic relevance stems from the importance of information security issue for national sovereignty, for businesses and citizens. A Recent article published in the portal Computer World, entitled "the Brazilian information security market has reached the significant milestone of US \$ 1 billion investment", evidence such relevance.

# 1.2 The Thesis

The architecture behavior of shared cache and network-on-chip, isolated or combined, can reveal secrets of MPSoCs through Architectural Channel Attacks (ACAs); though protection mechanisms implemented in the NoC has the potential to avoid it through traffic management.

# **1.3 Objectives**

The general thesis objective is to study ACAs in NoC-based MPSoCs, to develop and present with practical experiments MPSoCs vulnerabilities; and to show that the NoC can perform protections mechanisms. The following items are specific goals to achieve the general objective:

- To review the literature and identify potential threads for NoC-based MPSoCs;

- to develop an environment to run experiments and collect results;

- To adapt and perform state-of-the-art attacks on an MPSoC;

- To develop new attacks in NoC-based MPSoCs;

- To propose security mechanisms inside NoC architecture;

- To implement, characterize and validate the proposals under the attacks;

- To analyze results and present the final considerations.

#### 1.4 Methodology

Four parts comprehend the methodology of the present thesis work. The first one referred to the research on Architecture Channel Attacks. The second part investigated protection strategies implemented in the NoC architecture. The third one was the development of an experimental environment to evaluate attacks and countermeasures. The final part evaluated the attacks and the protection mechanisms, resulting in a comparative analysis of the vulnerabilities and hardware security.

The ACA exploration started with a review of the literature where commonly cache memories were the primary target of logical attacks in complex computational systems. Another valuable information found in published works was that the NoC had become a potential source of leakage to attack MPSoC architectures (NoC timing attacks). Then, the NoC timing attack was analyzed to develop a complete workflow on how to perform such attack. At the same time, the understanding of the techniques from the state-of-the-art did culminate in four new attacks proposals.

The knowledge of the MPSoC vulnerabilities made possible to develop and evaluate countermeasures against most dangerous MPSoCs attacks. To be aligned with the thesis, the protection mechanism proposed was a NoC architecture, aiming a low area and power solution. It resulted in the Gossip NoC.

An MPSoC platform was developed to evaluate with a significant level of confidence the attacks and some countermeasures (the Gossip and others from literature). The environment runs entirely in hardware in an FPGA. It was developed an external software also to support compilation, boot sequence and execution interface.

Finally, the last step comprised all experiments to validate and extract metrics of the proposals. Besides, it was performed a comparison of state-of-the-art and the propos-

als. The analysis of the security mechanisms had shown the potential of the NoC as the leading actor in MPSoC security.

#### 1.5 Structure of the Thesis

The present thesis is divided into eight chapters plus the conclusion and appendix. The chapter two describes the basic concepts required to understand the main topics of the thesis. It organizes the concepts in three fields: i) hardware security; ii) cryptographic engineering; and iii) Multi-processors Systems-on-Chips. Then, chapter three and four presents the state-of-the-art, where the first chapter focus on the architectural attacks, and the second on the countermeasures. Both chapters show works that explored vulnerabilities and protections in the cache and in the NoC of complex hardware systems. Chapter five introduces a study on the theme of the NoC timing attack. This type of attack was already cited by different authors ((YAO; SUH, 2012) (WASSEL et al., 2014) (SEPUL-VEDA et al., 2016) (SEPULVEDA et al., 2015) and (STEFAN; GOOSSENS, 2011)), but no detailed analysis and study has been performed yet. This chapter provides an overview of the technique and defines a threat model and methodology, to enable the replication of such technique. Some concerns about the attack are also presented and evaluated. After understanding the NoC timing attack, it is presented in chapter six the developed attacks of this thesis. The attacks focus on three side channel approaches: i) timing-based leakage; ii) access-based leakage; and iii) collision-based leakage. Chapter seven presents the secure enhanced NoC proposed. The architecture and functionality of Gossip NoC are explained in details. Different attacks and countermeasures are evaluated in chapter eight. The experiments were developed in a real MPSoC architecture running on an FPGA. The thesis ends with the conclusion chapter. The appendix presents the software development environment developed for the experiments with the real MPSoC, called MPSoC Glass.

# **2 BASIC CONCEPTS**

This chapter presents the basic concepts regarding the field of the thesis. It comprises: i) security in hardware systems; ii) cryptographic engineering and iii) Multi-Processors Systems-on-Chips (MPSoCs). Security implemented in hardware is a recent approach. The principal motivations to embedded such mechanisms are presented. Regarding cryptographic engineering, several encryption technologies have allowed applications and devices to provide the suitable level of security. Considerations on performance and protection have driven such area. We present in details one of the most used encryption, the Advanced Encryption System (AES). The last part of this chapter introduces the Multi-Processors Systems-on-Chips. They are the architecture evolution of the Systemon-Chip (SoC) concept. MPSoCs assemble several processing elements besides peripherals, specific purpose IPs, memories, and interconnection. Hence, his parallel nature achieves high performance, energy efficiency, and software flexibility.

## 2.1 Hardware Security

To implement security mechanisms directly in hardware is a recent trend. The primary motivations regard integrated circuit counterfeiting, secure cryptography (authentication, key storage, and generation, etc.), hardware Trojans, and Side Channel Attacks (SCA).

IC Counterfeiting: Fake or pirate chips have become a relevant issue for the integrated circuit industry. The counterfeiting and piracy for G20 nations were \$923 billion to \$1.13 trillion in 2013, and it was estimated \$1.9 to \$2.81 trillion in 2022 according to the International Chamber of Commerce (ICC) (ICC, ). Current methods to detect counterfeit are performed during the test of the IC. However, it may not be effective against non-conventional types (e.g. cloned, overproduced, and tampered devices) (GUIN; DIMASE; TEHRANIPOOR, 2014). Recently, a different approach has been proposed, the application of Physically Unclonable Functions (PUF). The PUF uses manufacture variability to build a structure that responds with uniqueness for each chip. Each PUF receives a challenge as input, and outputs a unique response (BOSSUET; TORRES, 2017), providing a fingerprint for each chip. Then, the authenticity of the piece can be checked.

Secure Cryptography Besides the counterfeit problem, PUFs can solve the major concerns regarding authentication and secret key generation (SUH; DEVADAS, 2007). However, PUF is not the most recommended solution for this case. Given a challenge to a PUF, the response is always the same, but some errors may happen. The algorithm used to correct and check such response is computation intense, and it can be prohibitive for designs, whose application requires at run-time such correctness. Another approach has been established as the suitable solution, the authenticated encryption. This method performs the cryptography of huge blocks of data, generating the ciphertext and its respective tag. The tag has a correspondence with the encrypted data, being possible to authenticate the encryption. Six different authenticated encryption modes (namely OCB 2.0, Key Wrap, CCM, EAX, Encrypt-then-MAC (EtM), and GCM) have been standardized in ISO/IEC 19772:2009 (ISO/IEC, ). So far, the most used authenticated encryption is the GCM (Galois Counter Mode). At the moment, a competition called CAESAR (Competition for Authenticated Encryption: Security, Applicability, and Robustness) aims to define a new standard, which will be implementable by software or hardware (MAIMUT; REYHAN-ITABAR, 2014).

Hardware Trojans Hardware Trojans are malicious hardware elements inserted during IC manufacturing. Since the majority of ICs today have its manufacturing outsourced, this threat has appeared, and it has increased at a fast rate. There are already reports of trojans inserted in military equipment (ADEE, 2008). Trojans can change the functionality of an IC and affect the primary objective of the device, or even disable some function (TEHRANIPOOR; WANG, 2012). Another source of Trojan is the Intellectual Property component, which is a third-party hardware used to add some functionality to the project. Conventional test methods for ICs are unable to detect such undesirable elements because it can only check the expected functionality of the developed design (unless it is a soft-IP). A possible solution is to analyze the traces of current (or other physical features) to verify differences caused by the trojan. This technique is similar to the attack known as Side Channel Attack, that collects information through behavior tips.

Side Channel Attacks Attacks that uses leakage information from an implemented target hardware are known as Side-channel Attacks. It was first proposed in 1996 by (KOCHER, 1996), and since then, this technique has been used to extract cryptographic key material of encryption algorithms running on microprocessors, DSPs, FPGAs, ASICs and high-

performance CPUs (KOCHER; JAFFE; JUN, 1999; GEBOTYS; GEBOTYS, 2003; MA-SOOMI; MASOUMI; AHMADIAN, 2010; ORS et al., 2004; TSUNOO et al., 2003). Countermeasures in hardware include noise insertion, out-of-order memory access, data scrambling. However, most recent attacks have been exploring logical leakages, such as the timing behavior. Solutions by software have been proposed to avoid logical threats, like random allocation of processes in memory, out-of-order execution, dummy logic insertion, etc. The Side Channel Attacks is the main topic of this thesis. Thus next section details this subject, and proposes a new classification for the logical SCAs.

# 2.1.1 Side Channel Attacks

A public threat in cryptographic engineering is side channel analysis, or Side-Channel Attacks (SCAs) (BOSSUET; TORRES, 2017). SCAs are widely used as passive attacks because they make it possible to retrieve secret information (such as secret keys) with relatively few measurements and sometimes to use the inexpensive equipment. SCAs are non-invasive attacks, which means that the external agent only observes the device in normal operation without causing any physical harm. It can use information from sensors of power consumption, time delay or electromagnetic radiation. Typical targets of side-channel attacks are security ICs used in embedded devices or smart cards. Since these designs are specific purpose ICs, they are easier to analyze. In general, it is a simple device running a single process at a low to moderate clock frequency with direct access to the side-channel of interest and with (precise) control over synchronization and measurements. Examples of SCA techniques are:

- Power Analysis (PA) (GEBOTYS; GEBOTYS, 2003)(ORS et al., 2004);

- Differential Power Analysis (DPA) (KOCHER; JAFFE; JUN, 1999)(MASOOMI; MASOUMI; AHMADIAN, 2010);

- Electromagnetic Analysis (GANDOLFI; MOURTEL; OLIVIER, 2001);

- Temperature and Heat-fault Attacks (HUTTER; SCHMIDT, 2014); and

- Fault-based Attacks (KARRI et al., 2001).

Recently, some authors proposed the observation of the logical behavior from the ICs instead of the physical, since system actions lead to similar vulnerabilities. Firstly, the victims of these logical attacks were the System-on-Chips (SoCs), whose complex architecture created several sources of leakages. Commonly, most vulnerabilities remain

in the shared resources, optimized features, and increased functionality (TIRI, 2007). Examples of logical SCAs are:

- CPU Timing Attacks (TSUNOO et al., 2003)(ANDRYSCO et al., 2015);

- Cache Timing Attacks (KOCHER, 1996)(BERNSTEIN, 2005)(NEVE; SEIFERT; WANG, 2006)(PERCIVAL, 2005).

- Collision Cache Attacks (BONNEAU; MIRONOV, 2006)(BOGDANOV et al., 2010); and

- Access-based Attacks (OSVIK; SHAMIR; TROMER, 2006) (BENGER et al., 2014) (ZHANG et al., 2014) (IRAZOQUI et al., ) (GULLASCH; BANGERTER; KRENN, 2011) (YAROM; FALKNER, 2014).

The strategy of sharing resources aims to reduce the amount of hardware needed to implement a particular functionality, but it also creates opportunities to attackers. The main elements shared inside any SoC are the memories and the communication infrastructure. MPSoCs architectures follow the same concept, but on a more complex scale. Thus, it is expected that more source of leakages will be available for the attackers. MPSoCs have two primary shared resources, the memories, and the Network-on-Chip. Memory attacks already are a well-known SCAs. Recently, Networks-on-Chip attacks have been cited by (SEPULVEDA et al., 2012; SEPULVEDA et al., 2015), which considered draining, extraction of data and denial-of-service. It was proven that communication behavior could reveal patterns during application execution, which can be used to figure out sensitive information. NoCs are entering in the list of vulnerable components inside complex hardware systems. Therefore, attacks and countermeasures have to be investigated.

#### 2.1.2 Proposed SCA Classification

Side Channel Attacks comprise a great variety of techniques. As described before, the main difference between each SCA is the leakage source. The leakage source defines the type of victim, the methodology employed, and the equipment required. The majority of SCAs explores physical features of devices. Application specific integrated circuits (ASICs) are the typical target of such attacks. However, the demand for more flexibility, performance, and less power has been increasing. As a consequence, complex hardware architectures have been proposed. This increase in complexity has brought challenges regarding the physical-based attacks, but opportunities to logical-based ones. Therefore, since there are already several physical-based SCAs, and there is a potential emerging of several new logical-based SCAs, this thesis proposes an SCA classification. The proposed classification divide the attacks into two sub-categories by the leakage nature, physical and architecture. Table 2.1 organizes the current known SCAs according to the new subcategories.

| Side Channel Attacks          |                   | Target    |       |     |      |

|-------------------------------|-------------------|-----------|-------|-----|------|

| Sub-Category                  | Leakage Source    | Processor | Cache | NoC | ASIC |

|                               | Power             | X         |       |     | Х    |

|                               | Diferential Power | X         |       |     | Х    |

| Physical Channel Attacks      | Electromagnetic   | X         |       |     | Х    |

|                               | Temperature       | X         |       |     | Х    |

|                               | Fault             | X         | Х     |     | Х    |

|                               | Timing            | X         | X     | 0   | Х    |

| Architectural Channel Attacks | Collision         |           | Х     | 0   |      |

|                               | Access            |           | Х     | 0   |      |

Table 2.1: Proposed Side Channel Attacks Classification

The Xs presented in table 2.1 refers to the attacks described in the state-of-the-art. The Os are the contribution of this thesis in the state-of-the-art.

## 2.2 Cryptographic Engineering

The cryptographic engineering becomes a valuable tool for current technology. The increase of device integration brought all personal information to the digital world. As a result, these sensitive data has become a target of attacks. Therefore, different cryptographic algorithms have been used to protect and maintain users privacy. Different algorithms can be employed, depending on the characteristics of the target application, hardware support, and relevance of the information. The most popular solution is the Advanced Encryption Standard (DAEMEN; RIJMEN, 2002), introduced in 2001 by Vincent Rijmen e Joan Daemen in a competition of NIST (National Institute of Standards and Technology). Another great cipher is the RSA (RIVEST; SHAMIR; ADLEMAN, 1978). Due to hardware cost, RSA is used more frequently where it requires higher security, like bank terminals. Other cryptographic algorithms have been used in commercial applications, but considering the popularity, AES is the target study case of this thesis.

#### 2.2.1 Advanced Encryption Standard - AES

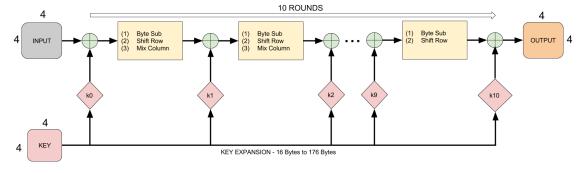

Advanced Encryption Standard is the preferred cryptography in many (mainly commercial) applications. This symmetric encryption operates inputs of 128 bits and keys of 128, 192 or 256 bits. This cipher algorithm uses iterations, called rounds, to perform a series of linked operations. In the case of a key of 128 bits, it is completed in 10 rounds. These activities refer to a substitution-permutation network because it replaces inputs by specific outputs and then shuffles the bits.

#### 2.2.1.1 Encryption Process

The input is a plaintext of 128 bits organized as a block of 16 bytes, represented as  $Plaintext \rightarrow P_i$ , where  $0 \le i \le 15$ . AES arranges this block as a matrix of four columns and four rows:

$$Plaintext = \begin{bmatrix} x_0 & x_1 & x_2 & x_3 \\ x_4 & x_5 & x_6 & x_7 \\ x_8 & x_9 & x_{10} & x_{11} \\ x_{12} & x_{13} & x_{14} & x_{15} \end{bmatrix}$$

The same structure is applied to the key, for example, a 16 byte key is represented as  $Key \rightarrow K_i$ , where  $0 \le i \le 15$ :

$$Key = \begin{bmatrix} k_0 & x_1 & k_2 & k_3 \\ k_4 & x_5 & k_6 & k_7 \\ k_8 & x_9 & k_{10} & k_{11} \\ k_{12} & k_{13} & k_{14} & k_{15} \end{bmatrix}$$

Before starting the encryption, it is performed the key expansion, which transforms the key in several keys to be used for each round, called subkeys. This process can be represented as  $expanded(K_i) \rightarrow k_i^{round}$ , where  $0 \le i \le 15$  and  $0 \le round \le 10$ . Figure 2.1 shows this process. Then, four operations are executed at each round, with an exception on the last one (figure 2.1):

• AddRoundKey: The 16 bytes of the plaintext or intermediate state (x) are considered as 128 bits and are XORed to the 128 bits of the subkey  $(k^{round})$ . If this is the last round, then the output is the ciphertext. Otherwise, the resulting 128 bits are

interpreted as 16-bytes and continue with the following operations.

- SubBytes: The 16 input bytes are substituted according to a fixed table (S-box) given in design. The result is a new matrix of four rows and four columns.

- ShiftRows: Each of the four rows of the matrix is shifted to the left, in a circular manner (no data lost).

- MixColumns: Each column of four bytes is now transformed using a unique mathematical function. This function takes as input the four bytes of one column and outputs four entirely new bytes, which replace the original column. The result is another new matrix consisting of 16 new bytes. It should be noted that this step is not performed in the last round.

All these four operations can be represented as an iterative set of equations. Each equation presented at 2.1 represents the computation of each byte (of all 16 bytes) in the intermediate value. These intermediate bytes are iterated through these equations for ten rounds to accomplish the 128 AES algorithm. To calculate each part, the intermediate value from the current round is used as an index of the S-Box table, represented as the S. After changing its value, a circular shift operation is performed, where the number besides the S represents the amount of shift (01 is one shift left, 02 is two shift left, and so on). When everything is ready, one can compute the AddRoundKey operation from the next round to be ready for the next iteration. Considering this algorithm, before start with these equations the inputs must perform an AddRoundKey in advance.

Figure 2.1: AES-128 encryption diagram, representing the main operations executed over the iterative process of ten rounds.

$$\begin{split} &(x_{0}^{r+1}) \leftarrow 01.S[x_{0}^{r}] \oplus 01.S[x_{5}^{r}] \oplus 02.S[x_{10}^{r}] \oplus 03.S[x_{15}^{r}] \oplus k_{0}^{r+1} \\ &(x_{1}^{r+1}) \leftarrow 01.S[x_{0}^{r}] \oplus 02.S[x_{5}^{r}] \oplus 03.S[x_{10}^{r}] \oplus 01.S[x_{15}^{r}] \oplus k_{1}^{r+1} \\ &(x_{2}^{r+1}) \leftarrow 02.S[x_{0}^{r}] \oplus 03.S[x_{5}^{r}] \oplus 01.S[x_{10}^{r}] \oplus 01.S[x_{15}^{r}] \oplus k_{2}^{r+1} \\ &(x_{3}^{r+1}) \leftarrow 03.S[x_{0}^{r}] \oplus 01.S[x_{5}^{r}] \oplus 01.S[x_{10}^{r}] \oplus 02.S[x_{15}^{r}] \oplus k_{3}^{r+1} \\ &(x_{4}^{r+1}) \leftarrow 01.S[x_{1}^{r}] \oplus 01.S[x_{6}^{r}] \oplus 02.S[x_{11}^{r}] \oplus 03.S[x_{12}^{r}] \oplus k_{4}^{r+1} \\ &(x_{5}^{r+1}) \leftarrow 01.S[x_{1}^{r}] \oplus 01.S[x_{6}^{r}] \oplus 02.S[x_{11}^{r}] \oplus 01.S[x_{12}^{r}] \oplus k_{5}^{r+1} \\ &(x_{5}^{r+1}) \leftarrow 01.S[x_{1}^{r}] \oplus 02.S[x_{6}^{r}] \oplus 01.S[x_{11}^{r}] \oplus 01.S[x_{12}^{r}] \oplus k_{5}^{r+1} \\ &(x_{7}^{r+1}) \leftarrow 03.S[x_{1}^{r}] \oplus 01.S[x_{6}^{r}] \oplus 01.S[x_{11}^{r}] \oplus 02.S[x_{12}^{r}] \oplus k_{7}^{r+1} \\ &(x_{7}^{r+1}) \leftarrow 03.S[x_{1}^{r}] \oplus 01.S[x_{7}^{r}] \oplus 02.S[x_{8}^{r}] \oplus 03.S[x_{13}^{r}] \oplus k_{7}^{r+1} \\ &(x_{7}^{r+1}) \leftarrow 01.S[x_{2}^{r}] \oplus 01.S[x_{7}^{r}] \oplus 02.S[x_{8}^{r}] \oplus 03.S[x_{13}^{r}] \oplus k_{7}^{r+1} \\ &(x_{10}^{r+1}) \leftarrow 03.S[x_{1}^{r}] \oplus 01.S[x_{7}^{r}] \oplus 01.S[x_{8}^{r}] \oplus 01.S[x_{13}^{r}] \oplus k_{7}^{r+1} \\ &(x_{11}^{r+1}) \leftarrow 03.S[x_{2}^{r}] \oplus 01.S[x_{7}^{r}] \oplus 01.S[x_{8}^{r}] \oplus 01.S[x_{13}^{r}] \oplus k_{1}^{r+1} \\ &(x_{11}^{r+1}) \leftarrow 03.S[x_{2}^{r}] \oplus 01.S[x_{7}^{r}] \oplus 01.S[x_{8}^{r}] \oplus 01.S[x_{13}^{r}] \oplus k_{1}^{r+1} \\ &(x_{11}^{r+1}) \leftarrow 03.S[x_{2}^{r}] \oplus 01.S[x_{7}^{r}] \oplus 01.S[x_{8}^{r}] \oplus 02.S[x_{13}^{r}] \oplus k_{1}^{r+1} \\ &(x_{11}^{r+1}) \leftarrow 01.S[x_{3}^{r}] \oplus 01.S[x_{4}^{r}] \oplus 02.S[x_{9}^{r}] \oplus 03.S[x_{14}^{r}] \oplus k_{12}^{r+1} \\ &(x_{13}^{r+1}) \leftarrow 01.S[x_{3}^{r}] \oplus 01.S[x_{4}^{r}] \oplus 02.S[x_{9}^{r}] \oplus 01.S[x_{14}^{r}] \oplus k_{12}^{r+1} \\ &(x_{13}^{r+1}) \leftarrow 03.S[x_{3}^{r}] \oplus 01.S[x_{4}^{r}] \oplus 01.S[x_{9}^{r}] \oplus 01.S[x_{14}^{r}] \oplus k_{13}^{r+1} \\ &(x_{15}^{r+1}) \leftarrow 03.S[x_{3}^{r}] \oplus 01.S[x_{1}^{r}] \oplus 01.S[x_{6}^{r}] \oplus 02.S[x_{11}^{r}] \oplus k_{13}^{r+1} \\ &(x_{15}^{r+1}) \leftarrow 03.S[x_{3}^{r}] \oplus 01.S[x_{1}^{r}] \oplus 01.S[x_{6}^{r}] \oplus 02.S[x_{11}^{r}] \oplus k_{15}^{r+1} \\ &(x_{15}^{r+1}) \leftarrow 03.S[x_{3}^{r}] \oplus 01.S[x_{$$

### 2.2.1.2 Decryption Process

The decryption process follows the same algorithm. However, each step has to be made on the contrary. The expansion of the key remains the same. Then, the ciphertext (the input of this process) goes through the AddRoundKey step, but the first sum with the last part of the key (opposite way). The MixColumn and the ShiftRow also perform its operations in opposite way. In the end, the process outputs the plaintext recovered.

#### 2.2.2 Performance-oriented AES

All operations performed by AES can be implemented using just logical and arithmetic operations. However, to obtain better performance, the cipher can be optimized for software implementations using a table with the operations pre-computed, as presented in (DAEMEN; RIJMEN, 2002). The pre-computed operations comprise the execution of SubBytes, ShiftRows and MixColumns for all possibilities (entries of 0 to 255), resulting in four tables of 1 kB, called the T-tables ( $T_0$ ,  $T_1$ ,  $T_2$  and  $T_3$ ). There is one more table ( $T_4$ ) for the last round that does not use the MixColumns operation.

The performance-oriented AES has two main phases. The first phase generates the subkeys by key expansion  $(expansion(K) \rightarrow k^{round})$ . Each subkey is used in the AddRoundKey step to provide the next round input matrix. Each byte of this input matrix is related to an index of the T-tables, where its content represents all operations performed for such byte. As a consequence, the output of the T-tables consulting are XORed resulting in a new output matrix, that can be represented as an intermediate state as follows  $x_i^{round}$ , where  $0 \le i \le 15$  and  $0 \le round \le 9$ . In summary, each intermediate state is used for the next round computation, which executes a XOR with the next round subkey (AddRoundKey operation) and the accessed T-tables values (SubBytes, ShiftRows and MixColumns operations) generating the next intermediate state. This mathematical iterated operation can be observed in 2.2.

$$(x_0^{r+1}, x_1^{r+1}, x_2^{r+1}, x_3^{r+1}) \leftarrow T_0[x_0^r] \oplus T_1[x_5^r] \oplus T_2[x_{10}^r] \oplus T_3[x_{15}^r] \oplus k_0^{r+1} (x_4^{r+1}, x_5^{r+1}, x_6^{r+1}, x_7^{r+1}) \leftarrow T_0[x_4^r] \oplus T_1[x_9^r] \oplus T_2[x_{14}^r] \oplus T_3[x_3^r] \oplus k_1^{r+1} (x_8^{r+1}, x_9^{r+1}, x_{10}^{r+1}, x_{11}^{r+1}) \leftarrow T_0[x_8^r] \oplus T_1[x_{13}^r] \oplus T_2[x_2^r] \oplus T_3[x_7^r] \oplus k_2^{r+1} (x_{12}^{r+1}, x_{13}^{r+1}, x_{14}^{r+1}, x_{15}^{r+1}) \leftarrow T_0[x_{12}^r] \oplus T_1[x_1^r] \oplus T_2[x_6^r] \oplus T_3[x_{11}^r] \oplus k_3^{r+1}$$

$$(2.2)$$

The last round is computed by repeating the equation 2.2 with r = 9, except that  $T_0, ..., T_3$  is replaced by  $T_4$ . The resulting  $x_i^{10}$  is the ciphertext.

#### 2.2.3 Crypto-libraries

In this section, we also analyze the commercial implementations of AES in software. Three widely used crypto libraries are described, namely OpenSSL (PROJECT, ), PolarSSL (POLARSSL, ), and Libgcrypt (LIBGCRYPT, ). All these AES solutions use the performance oriented approach. However, each one differs in the last round. Also, some of them do already contain methods to reduce or nullify cache-based side channel leakage. OpenSSL: It performs the last round using a table  $T_4$ , where the S-box and the ShiftRow are previously computed.

PolarSSL: PolarSSL executes the last round using an S-Box table. It provides more security than OpenSSL since the granularity of such table is in bytes not words. The computation effort increases a little, mainly to perform the ShiftRow operation.

Libgcrypt: This library calculates the S-Box values used in the last round during the encryption. The timing leakage generated by cache access can be mitigated since there is no table, but a high computation effort is inserted. Depending on the sensitivity of the attacker, this methodology could not be secure.

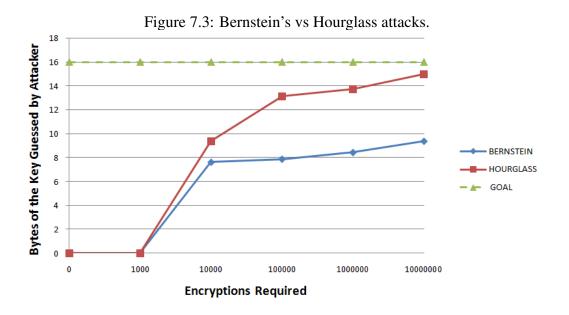

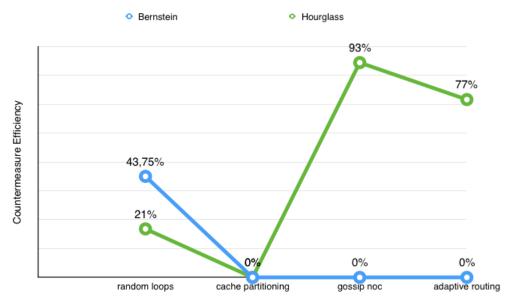

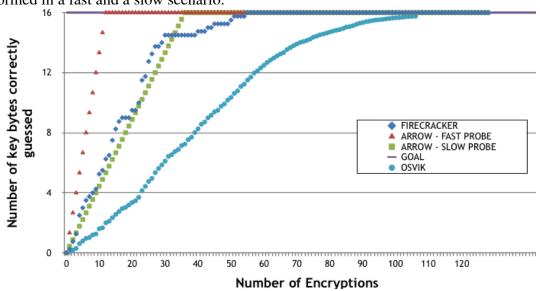

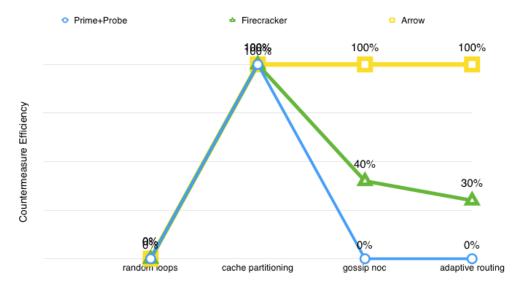

## 2.3 Multi-processors Systems-on-Chip