## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

Maurício Banaszeski da Silva

# PROJETO DE DIPLOMAÇÃO

# RUÍDO RTS EM OSCILADORES EM ANEL

Porto Alegre 2009

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

# RUÍDO RTS EM OSCILADORES EM ANEL

Projeto de Diplomação apresentado ao Departamento de Engenharia Elétrica da Universidade Federal do Rio Grande do Sul, como parte dos requisitos para Graduação em Engenharia Elétrica.

ORIENTADOR: Gilson Inácio Wirth

Porto Alegre 2009

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL ESCOLA DE ENGENHARIA DEPARTAMENTO DE ENGENHARIA ELÉTRICA

### MAURÍCIO BANASZESKI DA SILVA

## RUÍDO RTS EM OSCILADORES EM ANEL

Este projeto foi julgado adequado para fazer jus aos créditos da Disciplina de "Projeto de Diplomação", do Departamento de Engenharia Elétrica e aprovado em sua forma final pelo Orientador e pela Banca Examinadora.

| Orientador:                              |

|------------------------------------------|

| Prof. Gilson Inácio Wirth, UFRGS         |

| Formação Universitaet Dortmund, Alemanha |

Banca Examinadora:

Prof. Dr. Altamiro Amadeu Susin, UFRGS

Doutor pelo Institut National Polytechnique - Grenoble, França

Prof. Dr. Marcelo Soares Lubaszewski, UFRGS

Doutor pelo Institut National Polytechnique - Grenoble, França

# **DEDICATÓRIA**

Dedico este trabalho aos meus pais e irmã, em especial pela dedicação e apoio em todos os momentos difíceis.

### **AGRADECIMENTOS**

Primeiramente, gostaria de agradecer aos meus pais e irmã pelo apoio incondicional dado, sem qual seria extremamente difícil a jornada ao longo desses cinco anos.

Gostaria de expressar minha gratidão para com todos professores da Engenharia Elétrica desta Universidade pelo conhecimento passado e pelo apoio. Gostaria de agradecer ao Professor Gilson I. Wirth pela confiança depositada como orientador desse projeto, como orientador da minha bolsa de iniciação científica e principalmente por todo incentivo dado ao curso de Engenharia Elétrica.

#### **RESUMO**

Nesse trabalho foram estudados os efeitos da captura e emissão de portadores em armadilhas (traps) situadas na interface do silício com o dióxido de silício, chamado RTS (Random Telegraph Signal). Será apresentado um breve estudo teórico da física que envolve a captura emissão de portadores e do impacto das traps na corrente de dreno  $I_{DS}$ . Após, a teoria demonstrada será utilizada na análise e simulação de osciladores em anel single-ended. Por fim, conclusões a respeito do ruído causado pelo efeito RTS, nos transistores do circuito oscilador, serão feitas.

Palavras-chaves: Random Telegraph Signal. Armadilhas de Interface. Variabilidade. Confiabilidade. Ruído. Oscilador em Anel e MOSFETs.

#### **ABSTRACT**

In this work was studied the effects of carriers capture and emission by traps located at the silicon and silicon dioxide interface, called RTS (Random Telegraph Signal). Will be presented a brief theoretical study of the physics behind carrier capture and emission and its impacts on drain current  $I_{DS}$ . The theory presented will be utilized in the analysis and simulation of single-ended ring oscillators. After all, the conclusions of the RTS noise in the ring oscillator transistors will be done.

Keywords: Random Telegraph Signal. Interface Traps. Variability. Reliability. Noise. Ring Oscillator and MOSFETs.

# **SUMÁRIO**

| 1 INTRODUÇAO                                             | 12 |

|----------------------------------------------------------|----|

| 2 OSCILADOR EM ANEL                                      |    |

| 2.1 Princípio básico de funcionamento                    | 14 |

| 2.2 Ajuste de frequência                                 |    |

| 2.3 Aplicações                                           |    |

| 2.4 Jitter                                               |    |

| 2.5 Buffer de Saída                                      | 21 |

| 2 INTERFACE TRAP                                         | 23 |

| 2.1 Modelo da Interface Trap                             |    |

| 2.2 Análise do Impacto                                   | 27 |

| 3 SIMULAÇÃÔ                                              |    |

| 3.1 O Simulador                                          | 31 |

| 3.2 Dimensionamento                                      | 32 |

| 3.3 Cálculo de RTS                                       | 33 |

| 3.4 Uma simples aproximação                              | 36 |

| 3.5 Script                                               | 38 |

| 3.6 Resultados para diferentes simulações                | 43 |

| 3.6.1 Oscilador de três estágios                         | 43 |

| 3.6.2 Oscilador de cinco estágios                        | 44 |

| 3.6.3 Oscilador de sete estágios                         | 45 |

| 3.6.4 Análise dos resultados                             | 46 |

| 4 CONCLUSÕES E TRABALHOS FUTUROS                         | 48 |

| REFERÊNCIAS                                              | 49 |

| APÊNDICE: ARQUIVOS UTILIZADOS PELO SCRIPT PARA SIMULAÇÃO | 51 |

| Netlist utilizado                                        | 51 |

| Netlist criado                                           | 52 |

| Script                                                   | 52 |

# LISTA DE ILUSTRAÇÕES

| Figura 1 Esquematico logico de um oscilador em anel                                   | 14     |

|---------------------------------------------------------------------------------------|--------|

| Figura 2 Tensão nos diferentes estágios do oscilador                                  | 15     |

| Figura 3 Representação dos sinais de entrada e saída em uma porta inversora (Rabaey,  |        |

|                                                                                       |        |

| Figura 4 Inserção de capacitância na saída dos inversores.                            |        |

| Figura 5 Ilustração do period-jitter                                                  | 18     |

| Figura 6 Ilustração do cycle-to-cycle jitter.                                         | 19     |

| Figura 7 Circuito para estudo do impacto do jitter na performance, adaptado de (Rabae | y      |

| 2003)                                                                                 |        |

| Figura 8 Representação do phase jitter (McNeill, 1994).                               | 20     |

| Figura 9 Oscilador em anel e buffer de saída (McNeill, 2009)                          | 22     |

| Figura 10 Variações discretas na corrente devido ao RTS.(Simoen, 1992)                |        |

| Figura 11 Localização dos estados de energia dos interfacial traps                    |        |

| Figura 12 Ligações incompletas na superfície do silício (Pierret, 1996)               | 25     |

| Figura 13 Band bending causado pela aplicação de um potêncial no gate do transitor    |        |

| Figura 14 Mudança na quantidade de portadores na interface e em Et-Ef devido a muda   | ınça   |

| em Vg. (Martinez, 2005)                                                               | 27     |

| Figura 15 Desenho esquemático da camada de inversão de um transistor MOSFET pert      | urbada |

| por um trap. Adaptado de (Wirth, 2005)                                                | 29     |

| Figura 16 Exemplo de um netlist do HSpice e seu respectivo esquemático elétrico       | 31     |

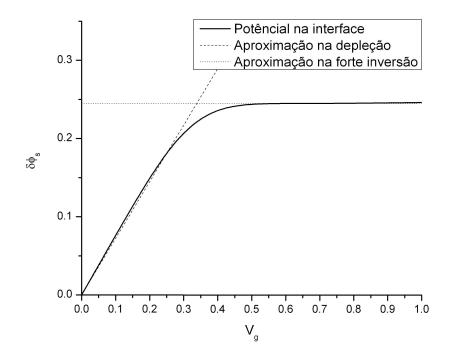

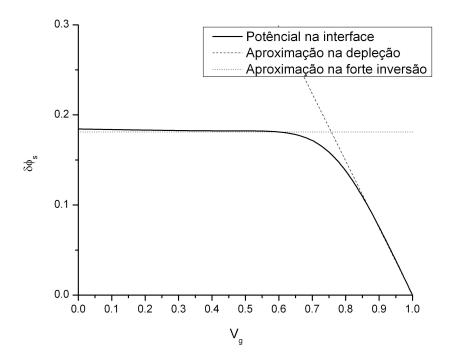

| Figura 17 Variação de tensão na interface do NMOS em função de Vg                     | 33     |

| Figura 18 Variação da tensão na interface do PMOS em função de Vg                     | 34     |

| Figura 19 Formato de saída gerado pelo HSpice                                         |        |

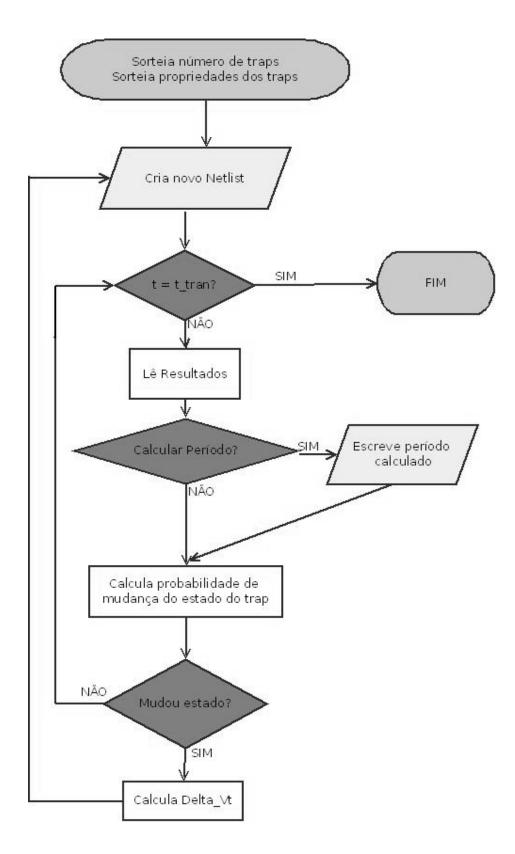

| Figura 20 Fluxograma simplificado do script criado                                    | 40     |

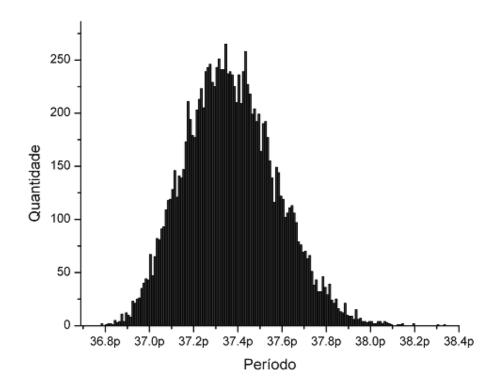

| Figura 21 Distribuição dos períodos medidos.                                          |        |

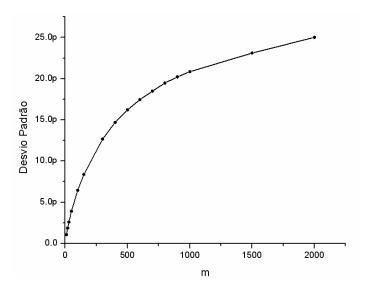

| Figura 22 Desvio padrão em função de m períodos transcorridos.                        | 42     |

## LISTA DE TABELAS

| Tabela 1 Resultados do circuito dimensionado.                          | 32 |

|------------------------------------------------------------------------|----|

| Tabela 2 Variação na tensão limiar devido a um trap                    | 36 |

| Tabela 3 Número de traps sorteados                                     |    |

| Tabela 4 Resultados da simulações de melhor e pior caso                | 37 |

| Tabela 5 Resultados estatísticos da simulação do script                | 41 |

| Tabela 6 Probabilidade de falha.                                       |    |

| Tabela 7 Resultados para várias simulações do oscilador de 3 estágios  | 44 |

| Tabela 8 Resultados para o oscilador de 5 estágios                     | 44 |

| Tabela 9 Simulação de pior e melhor caso para oscilador de 5 estágios  | 45 |

| Tabela 10 Resultados para o oscilador de 7 estágios                    | 45 |

| Tabela 11 Probabilidade de falha para oscilador de 7 estágios          |    |

| Tabela 12 Simulação de pior e melhor caso para oscilador de 7 estágios |    |

| Tabela 13 Desvio do máximo encontrado e do pior-caso.                  |    |

### LISTA DE ABREVIATURAS

L: Length (Comprimento)

MOSFET: Metal Oxide Field Effect Transistor

PLL: Phase Locked Loop

RTS: Random Telegraph Signal

ULSI: Ultra Large Scale Integration

VLSI: Very Large Scale Integration

VCO: Voltage Controlled Oscilator

W: Width (Largura)

### 1 INTRODUÇÃO

Novos avanços na miniaturização de transistores MOSFETs para dimensões nanométricas permitiram circuitos mais rápidos, que consomem menor potência e permitiram o aumento no nível de integração dos transistores, possibilitando no início da década de 80 o desenvolvimento de circuitos com centenas de milhares de transistores (VLSI - Very Large Scale Integration). Em 1986 a primeira memória RAM de 1 Megabit foi introduzida contendo mais de 1 milhão de transistores. Em 2005 foi ultrapassada a marca de 1 bilhão de transistores em um único chip, dando inicio a era do ULSI (Ultra Large Scale Integration).

Com a diminuição no tamanho dos transistores cada vez mais a não idealidade do comportamento dos transistores, assim como, a variabilidade no processo de fabricação teve que ser considerada nos projetos de circuitos integrados. Projetistas tiveram que fazer uso de ferramentas de simulação mais poderosas, que utilizassem equações mais precisas ao descrever o comportamento não ideal do transistor e que utilizassem "corners" para considerar a variabilidade no processo. Apesar dos problemas encontrados ao diminuir o tamanho do transistor, a sua miniaturização se mostra inevitável para o aumento na complexidade dos circuitos assim como na sua capacidade de armazenamento e velocidade.

Porém, quando a miniaturização dos MOSFETs passou para dimensões submicrométricas, com áreas menores que  $1\mu m^2$ , novas fontes de variações, além das variações de processo (variações estáticas), passaram a comprometer a performance e a confiabilidade dos circuitos. As variações passaram a ser uma função do tempo, ou seja, variações dinâmicas que modificam as propriedades do transistor com o passar do tempo, tais como NBTI ( Negative Temperature Instability), HCI (Hot Carrier Injection) e RTS (Random Telegraph Signal). Essas variações significam que parâmetros dos transistores podem sofrer modificações enquanto o circuito é utilizado e para que esse efeito não leve o circuito à falhas projetistas vêm utilizando "guard bands" nos projetos de circuitos digitais, ou seja, utilizam uma margem de segurança para que as variações que ocorrerem nos parâmetros dos transistores não levem o circuito à falha. Porém essas margens de segurança são muito pessimistas, levando em conta casos extremos encontrado na caracterização, e esse pessimismo ao considerar o atraso de uma célula digital acaba sendo um desperdício de área e de potência no circuito.

Com as motivações de projetar circuitos imunes a falhas, diminuir as "guard bands" e fabricar transistores mais confiáveis surgiram nos últimos anos muitos trabalhos nessa área, os quais buscam medir, modelar e explicar os efeitos que causam estas variações.

Este trabalho terá como meta analisar o modelo existente do efeito de Random Telegraph Signal. Primeiramente será demonstrada uma análise teórica do modelo e após o modelo será utilizado na simulação e análise de jitter em osciladores em anel.

#### 2 OSCILADOR EM ANEL

#### 2.1 PRINCÍPIO BÁSICO DE FUNCIONAMENTO

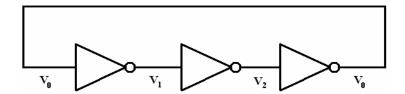

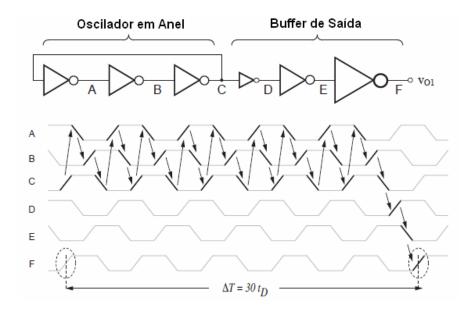

Osciladores em anel são exemplos de circuitos astáveis. Um circuito astável é um circuito que não possui um estado estável e sua saída oscila entre dois estados quase-estáveis com um período determinado pela tecnologia, pela topologia e pelos parâmetros utilizados no design e na fabricação do circuito oscilador. Osciladores em anel single-ended, como o que será utilizado neste trabalho, são dispositivos compostos por um número impar de inversores encadeados de maneira com que a saída do ultimo inversor é à entrada do primeiro (Figura 1).

Figura 1 Esquemático lógico de um oscilador em anel.

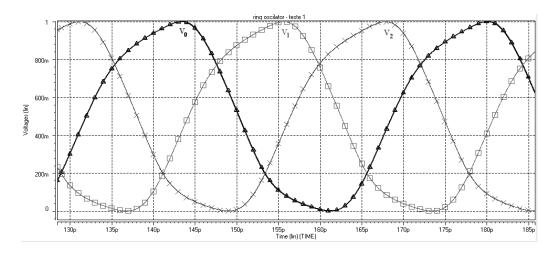

Devido ao número impar de inversões o circuito não tem um ponto de operação estável fazendo-o com que oscile, Figura 2. O período T da oscilação é dado pelo tempo de propagação do sinal por todos inversores ou como mostrado na fórmula abaixo (Rabaey, 2003).

$$T = 2 \times t_p \times N \tag{1}$$

Sendo  $t_p$  o tempo de propagação de um único inversor e N o número de inversores encadeados.

Figura 2 Tensão nos diferentes estágios do oscilador.

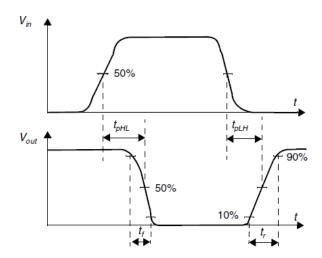

O tempo de propagação  $t_p$  de uma porta lógica define o quão rápida é sua resposta a uma mudança no sinal de sua(s) entrada(s), expressando o atraso no sinal ao passar pela porta lógica. O tempo de propagação é medido entre os pontos que representam 50% do sinal de entrada e saída, como mostrado na Figura 3, para o caso de uma porta inversora.

Figura 3 Representação dos sinais de entrada e saída em uma porta inversora (Rabaey, 2003).

Como a porta lógica apresenta tempos de respostas diferentes para sinais que estão aumentando de tensão ou diminuindo de tensão, na sua entrada, duas definições de tempo de

propagação são necessárias. O  $t_{pLH}$  define a resposta para uma transição de saída positiva (sinal transiciona de um nível lógico baixo para um nível lógico alto), enquanto o  $t_{pHL}$  define a resposta para uma transição de saída negativa (sinal transiciona de um nível lógico alto para um nível lógico baixo). Logo o tempo de propagação  $t_p$ , em contraste com  $t_{pLH}$  e  $t_{pHL}$ , é uma propriedade simbólica, não tendo sentido físico, e sendo empregada para a comparação entre diferentes design e tecnologias. Sendo  $t_p$  dado pela equação 2 (Rabaey, 2003).

$$t_p = \frac{t_{pLH} + t_{pHL}}{2} \tag{2}$$

#### 2.2 AJUSTE DE FREQUÊNCIA

Existem diversos métodos para controlar a frequência de operação de osciladores em anel. Os comumente utilizados são: mudança no número de inversores encadeados, mudança na tensão de alimentação, variação na capacitância de saída dos inversores e mudança na capacidade de corrente dos inversores.

Como pode ser visto na equação 1, o período de oscilação é diretamente proporcional a variação no número de estágios inversores, um aumento no número de estágios inversores resulta em aumento no período, consequentemente, diminuição da frequência de operação.

A mudança da tensão de operação dos inversores é comumente utilizado em Voltage Controlled Oscillators (VCOs) presentes no núcleo de PLLs, o aumento da tenção resulta no aumento da frequência e a diminuição da tensão resulta na diminuição da frequência de oscilação. A desvantagem deste método está quando há necessidade da utilização de tensões muito baixas para atingir a frequência de operação desejada, pois o uso de tensões muito baixas, deixa o circuito mais susceptível a ruídos presentes nas tensões de alimentação.

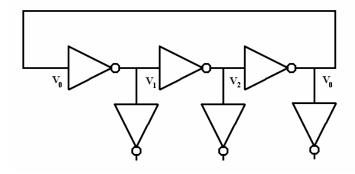

Outro método bastante utilizado é a variação da capacitância na saída dos estágios inversores, o aumento de capacitância pode ser conseguido inserindo inversores de acordo

com a figura 4, com um aumento na capacitância de saída dos inversores, o tempo de propagação  $t_p$  irá aumentar, e assim, irá diminuir a frequência de operação.

Figura 4 Inserção de capacitância na saída dos inversores.

Por fim, a capacidade de o transistor passar corrente pode ser mudada, um aumento na largura W do transistor aumenta a capacidade de corrente do transistor, diminuindo  $t_p$  e assim, aumenta a frequência de operação do oscilador, por consequência, uma diminuição em W tem efeito inverso na capacidade de corrente, assim, diminuindo a frequência de oscilação. A variação no comprimento L do canal do transistor tem comportamento inverso a variação de W, ou seja aumentando-se L diminui-se a capacidade de corrente e aumenta-se  $t_p$ . Tal comportamento pode ser provado ao analisar a fórmula  $I_{DS} \approx \frac{W}{L} K'_n (V_{gs} - V_t) V_d$ .

#### 2.3 APLICAÇÕES

Osciladores em anel são largamente utilizados em núcleos de phase-locked-loops (McNeill, 2009); para recuperação do clock, recuperação de dado, sínteses de frequência e sincronização do clock; para geração de clock dentro do chip (Rabaey, 2003); e como estruturas de teste incorporadas ao silício para monitorar as características e as variabilidades no processo dos transistores MOSFETs (Bhushan, 2006).

#### 2.4 JITTER

A análise da performance de um circuito digital é expressa pelo período do clock, ou frequência de clock. O valor de um período de clock para uma dada tecnologia e design é dado por inúmeros fatores como o tempo de propagação do sinal através da lógica combinacional, o tempo que leva o dado para entrar ou sair dos registradores e a incerteza no tempo de chegada do sinal de clock, a qual esse trabalho se destinará.

Em um oscilador ideal o espaçamento entre as transições é constante, ou seja, tem período e freqüência constantes. Porém na prática esses espaçamentos são variáveis devido ao ruído presente no oscilador. Essa incerteza no período de um oscilador em anel, ou clock é conhecida como jitter. Existem três principais tipos de jitter: period jitter, cycle-to-cycle jitter e long-term jitter (Tektronix, 2005).

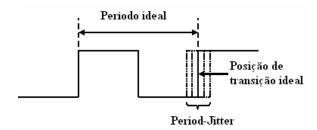

Period-jitter é dado pelo desvio na transição de saída do clock relativo à posição de transição ideal, podendo tanto ocorrer antes ou depois da posição ideal. Figura 5 ilustra medição do period-jitter.

Figura 5 Ilustração do period-jitter.

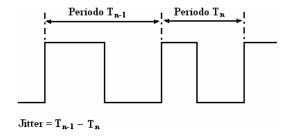

Cycle-to-cycle jitter é dado pela mudança na transição de saída do clock com relação à posição da transição do ciclo anterior, como mostrado na Figura 6.

Figura 6 Ilustração do cycle-to-cycle jitter.

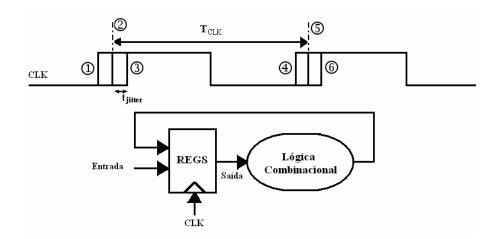

Grandes cycle-to-cycle jitters impactam diretamente na performance de sistemas sequenciais, podendo levar os sistemas à falha. Analisando a Figura 7 nota-se que idealmente o período do clock começa em 2 e termina em 5 tendo um período nominal de  $T_{CLK}$ , ainda analisando a figura constata-se que o cenário de pior caso acontece quando o período nominal começa atrasado em 3 e termina adiantado em 4.

Nesse cenário de pior caso para que o sistema, mostrado na Figura 7, não venha a falhar deve-se cumprir a equação mostrada abaixo:

$$T_{CLK} - 2t_{iitter} \ge t_{c-a} + t_{logica} + t_{setup}$$

ou  $T_{CLK} \ge t_{c-a} + t_{logica} + t_{setup} + 2t_{iitter}$  (3)

Sendo  $t_{c-q}$  o atraso do registrador para que a entrada apareça na saída, no momento em que há transição do clock,  $t_{setup}$  é o tempo de setup do registrador, ou melhor, o tempo que a entrada deve estar estável antes da transição do clock e  $t_{logica}$  é o atraso devido à lógica combinacional.

Figura 7 Circuito para estudo do impacto do jitter na performance, adaptado de (Rabaey 2003).

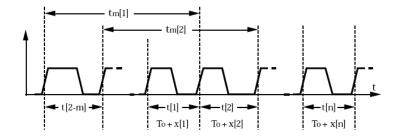

Long-term jitter, também conhecido como phase jitter, mede a máxima mudança na transição de saída do clock com relação à posição ideal do clock após um número grande de transições. Na medida long-term do jitter ocorre o acúmulo de variabilidade porque qualquer incerteza nas primeiras transições afeta todas as próximas transições, logo o efeito persiste indefinidamente e a incerteza total após um certo tempo decorrido é igual à soma de todas incertezas associadas a cada transição. O que torna essa media dependente do tempo medido, como mostrado na Figura 8.

Figura 8 Representação do phase jitter (McNeill, 2009).

Assim o jitter  $\sigma_{\Delta T}$  no intervalo de tempo transcorrido  $\Delta t = mT_0$  é apenas a soma dos jitters nos m períodos transcorridos. De acordo com a Figura 8 e com (McNeill, 2009) podemos representar  $t_m[n]$ , para m períodos transcorridos, como a equação que segue abaixo:

$$t_m[n] = \sum_{i=n-m+1}^{n} t[i]$$

(4)

Sendo, uma vez que a média de x[n] é igual a zero, a expectativa ou média de  $t_m[n]$  é igual a:

$$E\{t_m[n]\} = mT_0 \tag{5}$$

E usando um pouco de matemática mostrada em (McNeill, 2009) se chega à equação abaixo que relaciona a variância de  $t_m[n]$  com a auto-correlação  $R_{xx}$  de x[n].

$$\sigma^{2}(m) = \sum_{i=-m}^{m} (m - |i|) R_{xx}[i]$$

(6)

Este tipo de jitter impacta dramaticamente nas aplicações que envolvem comunicação serial de dados de alta velocidade, pois essas necessitam de um clock bem sincronizado com o dado recebido.

#### 2.5 BUFFER DE SAÍDA

Um projeto de osciladores deve conter meios pelo quais o sinal do oscilador será levado do núcleo do oscilador para o restante do circuito, que utiliza a forma de onda do oscilador, para isso são utilizados buffers. Como mostrado na figura abaixo, as portas A, B e C formam o núcleo do oscilador e as portas D, E e F formam o estagio de saída simplificado.

Figura 9 Oscilador em anel e buffer de saída (McNeill, 2009).

Qualquer buffer de saída irá adicionar jitter ao já existente na forma de onda do oscilador em anel, porém na maioria dos casos, o jitter adicionado fora do anel não é um problema considerável, para o cálculo de long-term jitter. O exemplo da figura 8 mostra o jitter medido durante um período  $\Delta T$  com uma média equivalente a 30 vezes o tempo de propagação de uma porta. As transições destacadas mostram a propagação da primeira até a ultima transição que ocorrem no período  $\Delta T$ . Como pode ser visto na figura, cada estágio no oscilador tem múltiplas oportunidades para adicionar jitter na forma de onda, porém, quando o sinal está fora do anel cada estagio de buffer terá apenas uma oportunidade de contribuir com o jitter. Assim tornando predominante o jitter produzido no anel, e tornando o jitter produzido nos buffers como efeito secundário no cálculo de long-term jitter (McNeill, 2009). Porém na análise de period-jitter e cycle-to-cycle jitter o estágio de buffer e clock gating representam importantes fontes de jitter em cicuitos digitais.

#### 2 INTERFACE TRAP

#### 2.1 MODELO DA INTERFACE TRAP

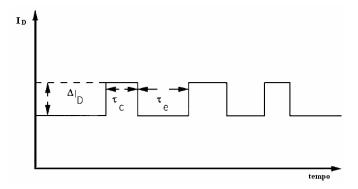

Interface Trap é o mecanismo predominantemente responsável pelo ruído de baixa freqüência em transistores MOSFETs com áreas diminutas, abaixo 1um², interface trap é responsável pelo aprisionamento e emissão de elétrons na interface do silício com o óxido de silício, Si-SiO2. A captura e emissão de um único portador causada por um único trap leva a mudanças discretas na corrente de dreno Ids, fenômeno conhecido como Random Telegraph Signal (RTS) (Simoen, 1992; Brusamarello, 2009; Wirth, 2005, Kirton, 1989), Figura 10.

Figura 10 Variações discretas na corrente devido ao RTS.(Simoen, 1992)

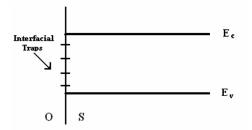

Interfacial traps, também conhecidos como estados de superfície ou estados de interface, são estados permitidos de energia, situados na banda proibida, ou band gap, encontrados na vizinhança da superfície do material, no qual podem ser encontrado portadores (Pierret, 1996), como mostrado na figura abaixo.

Figura 11 Localização dos estados de energia dos interfacial traps.

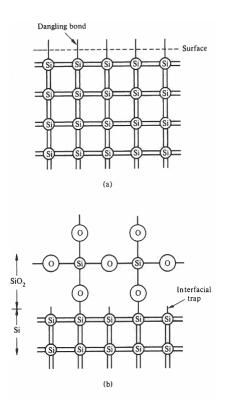

Embora modelos que detalhem o comportamento elétrico das traps existam, a origem física das traps não foi totalmente explicada (Pierret, 1996). Porém, dados experimentais mostram que primariamente as interface traps surgem de ligações incompletas, ou chamadas de "dangling-bond", na superfície do semicondutor. Quando o silício é interrompido ao longo de um plano para formar uma superfície, uma das quatro ligações do átomo de silício fica "suspensa" como mostrado na Figura 12a. Durante o processo de oxidação a maioria das ligações são completadas com o óxido de silício, mas algumas são deixadas incompletas, assim formando as interface traps, como mostra Figura 12b. (Pierret, 1996)

Figura 12 Ligações incompletas na superfície do silício (Pierret, 1996). a) Antes da oxidação. b) Após a oxidação ( número relativo de traps exagerado)

A partir do conceito, dado anteriormente, sobre os estados de energia do trap, pode-se fazer uso da função de Fermi-Dirac:

$$f(E) = \frac{1}{1 + e^{\frac{(E - E_F)}{KT}}}$$

(7)

fazendo a substituição de E pela energia do trap  $E_T$ , para encontrar a probabilidade de ocupação de um trap por um portador,. Após o uso de dados experimentais presentes em (Kirton, 1989) e conceitos teóricos, pode-se chegar às equações de probabilidade de ocupação e de probabilidade de desocupação do trap dado por (Brusamarello, 2009).

$$\Pr^{(i)}(0 \to 1)dt = \frac{dt}{10^{p_i} [1 + \exp(-q_i)]} = \frac{dt}{\tau_c^{(i)}}$$

(8)

$$\Pr^{(i)}(1 \to 0)dt = \frac{dt}{10^{p_i}[1 + \exp(q_i)]} = \frac{dt}{\tau_e^{(i)}}$$

(9)

Sendo  $\Pr^{(i)}(0 \to 1)$  e  $\Pr^{(i)}(1 \to 0)$ , respectivamente, as probabilidades de captura e emissão de portadores livres pelo trap i,  $q_i = {}^{(E_T - E_F)} /_{KT}$  sendo  $E_T$  a energia do trap i,  $E_F$  a energia de Fermi,  $E_F$  a constante de Boltzmann e  $E_T$  a temperatura em graus Kelvins.  $E_T$  de acordo com (Kirton, 1989) é uma variável aleatória uniformemente distribuída e  $E_T$  e são, respectivamente, os tempos de captura e emissão de portadores pelo trap.

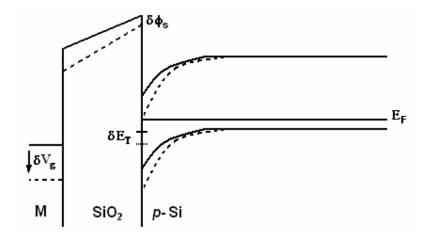

A dependência de  $\tau_c$  e  $\tau_e$  com a tensão no gate do transistor  $V_{gs}$  pode ser explicada a partir da teoria de band bending, no qual a tensão  $V_g$  altera o potencial na interface Si-SiO2 mantendo a energia de Fermi, que é uma propriedade do material, constante, como mostrado na Figura 13.

Figura 13 Band bending causado pela aplicação de um potencial no gate do transistor.

Logo, a mudança na energia do trap pode ser dada pela equação abaixo.

$$\delta E_T \approx \delta \phi_s \tag{10}$$

Porém, como pode ser visto em várias referências (Kirton, 1989; Lukyanchikova, 2000; Martinez, 2005) o tempo de captura varia em proporções muito maiores das que é dada pela variação da energia do trap  $\delta E_T$ . Essa diferença é explicada, ao considerarmos o tempo de captura  $\tau_c$  como sendo dependente da concentração de portadores na interface. Pois, caso a

concentração de portadores tender a zero espera-se que o tempo de captura dos portadores  $\tau_c$  tenda a infinito.

Finalmente, pode-se expressar a variação de  $\tau_c$  e  $\tau_e$  devido a variação em  $V_g$ , como mostrado na equação abaixo, sendo  $n_s$  a concentração de portadores na interface.

$$\frac{\tau_c(V_{g,2})}{\tau_c(V_{g,1})} = \frac{n_s(V_{g,1})}{n_s(V_{g,2})} \cdot \frac{(1 + e^{\phi_{TF}(V_{g,1})})}{(1 + e^{\phi_{TF}(V_{g,2})})}$$

(11)

$$\tau_{e}(\delta V_{g}) = (1 + e^{E_{T} - E_{F} + \delta \phi_{S}})$$

$$\tag{12}$$

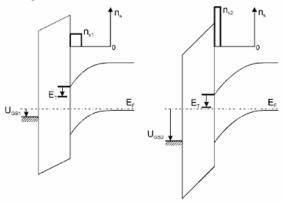

A figura abaixo, ilustra as mudanças em  $n_s$  e  $E_T-E_F$  devido a mudança em  $V_g$  (mostrado na figura como Ugs).

Figura 14 Mudança na quantidade de portadores na interface e em Et-Ef devido a mudança em Vg. (Martinez, 2005)

#### 2.2 ANÁLISE DO IMPACTO

Para analisar os efeitos na corrente de dreno de um transistor dado por um único trap, parte-se da fórmula de  $I_{DS}$  para um MOSFET, de acordo com (Pierret, 1996):

$$I_{DS} = W_{eff} \cdot \mu_n(y) Q_n(y) \frac{d\phi}{dy}$$

(13)

Sendo  $Q_n(y)$ , a densidade de carga na camada de inversão em função da posição y no canal, dado por  $Q_n(y) \cong C_O(V_g - V_T - \phi(y))$  sendo  $\phi(y)$  o potencial na posição y.

A partir da equação de  $Q_n(y)$  podemos representar  $I_{DS}$  em função da densidade de portadores  $N_c(y)$ , resultando em:

$$I_{DS} = W_{eff} \cdot \mu_n(y) \cdot qN_c(y) \cdot \frac{d\phi}{dy}$$

(14)

E sendo  $\mu_n(y)$  é a mobilidade dos portadores, podendo ser representada, de acordo com (Pierret, 1996), como independente de y e dada por:

$$\overline{\mu}_n \approx \frac{\mu_0}{1 + \theta(V_g - V_T)} \tag{15}$$

Analisando a dependência da mobilidade e da densidade de portadores em função de  $V_{g,eff}=(V_g-V_T)$  fica claro a dependência de  $I_{DS}$  em  $V_{g,eff}$ . Resolvendo-se a equação 5, para um dispositivo de canal longo, tem-se para pequenas tensões de dreno Vd:

$$I_{DS} = q \cdot \frac{W_{eff}}{L_{eff}} \cdot \overline{\mu}_n(V_{g,eff}) \cdot N_c(V_{g,eff}) \cdot V_D$$

(16)

e tem-se para a região de saturação:

$$I_{DS} = q \cdot \frac{W_{eff}}{L_{eff}} \cdot \overline{\mu}_n(V_{g,eff}) \cdot N_c(V_{g,eff}) \cdot V_{g,eff}$$

(17)

Quando há ocupação de um trap por um portador os três principais efeitos no transistor são:

1) O canal de condução contará com um portador a menos para a condução da corrente, e a densidade de portadores  $N_c$  irá variar de acordo com (Wirth, 2005)

$$\frac{\delta N_c}{\delta N_{tr}} = \frac{q^2 / K_T \cdot N_c(y)}{C_{OV} + C_{tr} + C_{dr} + q^2 / K_T \cdot N_c(y)}$$

$$\tag{18}$$

sendo  $C_{ii}$  a capacitância da interface trap e  $C_{d}$  a capacitância da junção pn.

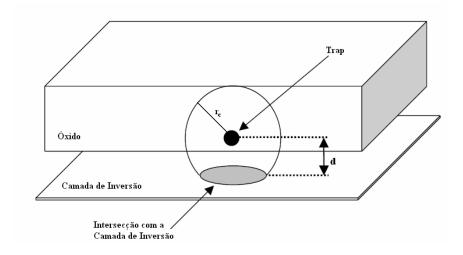

2) A carga do trap terá forte influência na mobilidade local  $\mu_n(y)$  próxima ao trap, influência que se dá devido a ação do fenômeno conhecido como Coulomb-scattering, no qual a carga do trap ocupado reage com a carga dos portadores, fazendo com que os portadores

desviem de suas trajetórias e assim diminuindo a velocidade média e por conseqüência a mobilidade. A mudança na mobilidade pode ser dada pela equação apresentada por (Wirth, 2005):

$$\frac{\delta\mu}{\delta\mu(y)} = \frac{\pi r_i^2}{WL} \tag{19}$$

Sendo  $\pi r_i^2$  a área perturbada pelo trap e  $r_i$  dado por  $r_i = \sqrt{r_c^2 + d^2}$ , como mostrado na figura a seguir.

Figura 15 Desenho esquemático da camada de inversão de um transistor MOSFET perturbada por um trap. Adaptado de (Wirth, 2005).

3) A carga do trap ocupado no óxido irá aumentar a tensão de threshold do transistor, diminuindo  $V_{g,eff}$ , já que os portadores para transistores tipo n são elétrons (carga negativa) e para tipo p são buracos (carga positiva) essa carga irá se opor à tensão no gate necessária a formação do canal de condução, assim alterando a tensão limiar, ou tensão de threshold, conforme a equação abaixo.

$$\delta V_T = \frac{q}{W_{eff} \cdot L_{eff} \cdot C_o} \tag{20}$$

Sendo  $C_o = \frac{K_s \mathcal{E}_0}{x_0}$ ,  $K_s = 3.9$  para o óxido de silício,  $\mathcal{E}_0$  a permissividade do vácuo e  $x_0$  a profundidade do óxido.

Por fim, as referencias (Wirth, 2005; Brusamarello, 2009; Alexander, 2005) comprovam a possibilidade de fazer a aproximação dos principais efeitos dos traps como sendo variações na tensão limiar  $V_T$ . De acordo com (Brusamarello 2009) o efeito de um trap ocupado na interface pode ser aproximado pela equação abaixo.

$$\delta V_T = \frac{q}{W_{eff} \cdot L_{eff} \cdot C_o} \cdot \alpha(x l_i)$$

(21)

Sendo  $\alpha(xl_i)$  função da posição  $xl_i$  do trap no comprimento do canal e função do formato considerado do canal (constante, linear ou exponencial), dada por:

$$\alpha(xl_i) = \begin{cases} k_c & \text{constante} \\ k_l \cdot \frac{xl_i}{Leff} + c_l & \text{linear} \\ \exp(k_e \cdot \frac{xl_i}{Leff}) + c_e & \text{exponencial} \end{cases}$$

(22)

### 3 SIMULAÇÃO

#### 3.1 O SIMULADOR

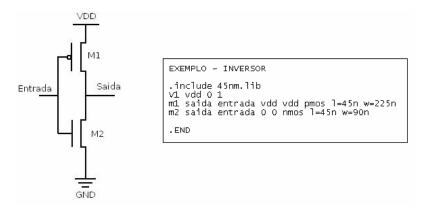

Para a realização das simulações que buscam analisar os efeitos das interface traps em osciladores em anel, foi utilizado o simulador de circuitos elétricos HSpice da Synopsys. Esta escolha se deve ao fato do programa ser largamente utilizado e aceito na comunidade acadêmica e na indústria, devido a sua alta precisão de cálculo e ao uso de equações precisas que descrevam o comportamento do transistor.

Para realização das simulações o HSpice necessita de um arquivo de entrada comumente chamado de Netlist. Esse arquivo contém a descrição do circuito a ser simulado em uma linguagem SPICE própria. Nessa descrição devem conter: a tecnologia dos transistores utilizados, tensões de VDD e GND, descrição dos transistores, as ligações dos circuitos, parâmetros para realização de medidas e etc. A Figura 16 demonstra um exemplo de Netlist de um inversor CMOS e seu respectivo esquemático elétrico.

Figura 16 Exemplo de um netlist do HSpice e seu respectivo esquemático elétrico.

#### 3.2 DIMENSIONAMENTO

A primeira simulação efetuada foi para dimensionar a largura. Wp dos transistores PMOS dos inversores para que o tempo de atraso de subida  $t_r$  seja igual ao tempo de atraso de descida  $t_f$ . Assim o duty cycle do oscilador será igual a 50%, ou seja, o tempo que o sinal ficará em nível lógico alto será igual ao tempo que o sinal ficará em nível lógico baixo. O Inversor utilizado neste trabalho utiliza a tecnologia CMOS de 45 nanômetros da Predective Technology Model (PTM) (Cao, 2007), foi escolhida a utilização desta tecnologia por se tratar de uma tecnologia estado-da-arte, ou seja, uma tecnologia nova que recentemente entrou no mercado industrial.

Para a realização do dimensionamento foi fixada a largura Wn dos transistores NMOS em duas vezes o tamanho do comprimento mínimo do canal L de 45 nanômetros, ou seja, Wn igual a 90 nanômetros. Fazendo-se o uso da opção OPTMISE do HSpice, pode-se encontrar o Wp ideal para  $t_r$  igual a  $t_f$ , essa opção varia o parâmetro Wp até que um valor que satisfaça a condição descrita seja encontrado. Os resultado de Wp foi utilizado em um novo Netlist, desta vez, simulando um oscilador em anel com 3 estágios, para comprovação do dimensionamento otimizado de Wp, os resultados da simulação são dados pela tabela 1.

Tabela 1 Resultados do circuito dimensionado.

| Wp    | 225nm      |  |  |

|-------|------------|--|--|

| $t_r$ | 6.1360E-12 |  |  |

| $t_f$ | 6.1001E-12 |  |  |

| TH    | 1.0892E-11 |  |  |

| TL    | 9.2145E-12 |  |  |

#### 3.3 CÁLCULO DE RTS

Para análise do impacto das interface traps foram feitas simulações para o cálculo dos tempos de captura e emissão em função da tensão na entrada do inversor, conforme foi apresentada na seção 2.1. Primeiramente foi simulado a variação da tensão na interface  $\delta\phi_s$  dos transistores NMOS e PMOS em função de  $V_g$ . A simulação foi feita no Hspice utilizando-se um novo Netlist, os resultados são mostrados nas figuras abaixo.

Figura 17 Variação de tensão na interface do NMOS em função de Vg.

Figura 18 Variação da tensão na interface do PMOS em função de Vg.

A seguir, para se fazer uso da variação da tensão superficial dos transistores em função da tensão na entrada do inversor, foram calculadas as aproximações mostradas na Figura 17 e na Figura 18, tendo como resultados as equações 23 e 24.

$$\delta\phi_{s,NMOS} = \begin{cases} \frac{V_g}{1.38129} &, V_g \le 0.34\\ 0.245 &, V_g > 0.34 \end{cases}$$

(23)

$$\delta\phi_{s,PMOS} = \begin{cases} \frac{V_g}{1.34192} , & V_g \le 0.6\\ 0.18113 , & V_g > 0.6 \end{cases}$$

(24)

Após, de acordo com a equação 11, é necessário conhecer as variações na concentração de portadores na interface SiO2, para isso, foi feita à consideração que a variação na concentração de portadores na interface segue a mesma proporção da variação da carga no canal de inversão, ou seja:

$$\frac{n_s(V_{g,2})}{n_s(V_{g,1})} \approx \frac{Q_{inv}(V_{g,2})}{Q_{inv}(V_{g,1})}$$

(25)

A carga no canal de inversão foi encontrada simulando o netlist, dado no Anexo 4, no HSpice. Os resultados mostraram uma variação quase linear de Qinv com Vg e as aproximações utilizadas são dadas abaixo:

$$\overline{n}_{s,NMOS}(V_g) = \frac{Q_{inv}(V_g)}{Q_{inv}(V_g = 1)} = V_g \cdot 0.96372 + 0.03628$$

(26)

$$\overline{n}_{s,PMOS}(V_g) = \frac{Q_{inv}(V_g)}{Q_{inv}(V_g = 0)} = -V_g \cdot 0.96396 + 1$$

(27)

Por fim, as equações utilizadas que regem o comportamento de  $au_c$  e  $au_e$  em função de  $V_g$  são dadas por:

$$\tau_{c,NMOS} = \left( \frac{1}{n_{s,NMOS}} \right) \cdot 10^{-p} \cdot \left( 1 + e^{-(\Delta E_{TF} - \delta \phi_{s,NMOS})} \right) \tag{28}$$

$$\tau_{e,NMOS} = 10^{-p} \cdot (1 + e^{(\Delta E_{TF} - \delta \phi_{S}, NMOS)})$$

(29)

$$\tau_{c,PMOS} = (\sqrt{n_{s,PMOS}}) \cdot 10^{-p} \cdot (1 + e^{-(\Delta E_{TF} + \delta \phi_{s,PMOS})})$$

(30)

$$\tau_{e,PMOS} = 10^{-p} \cdot (1 + e^{(\Delta E_{TF} + \delta \phi_S, PMOS)})$$

(31)

Sendo p, como já dito anteriormente, uma propriedade do trap, cujos valores possíveis são uniformemente distribuídos  $p_1 \le p \le p_2$ . Para que o efeito de um trap seja visível na janela de tempo que ocorreu a observação p1 e p2 devem ter valor tal que a probabilidade de ocorrer uma captura ou emissão de um portador no intervalo de tempo observado seja próxima de 1. Neste trabalho será utilizada a premissa de que todos os traps existentes são observáveis e possuem p uniformemente distribuído entre 8 e 12.

De acordo com a equação 21 o impacto de um trap ocupado nos parâmetros do transistor pode ser modelado como uma variação na tensão de threshold dada pelo efeito eletrostático da carga no óxido multiplicado por um fator experimental, que considera as

variações na mobilidade e na concentração de portadores. Analisando a referencia (Alexander, 2005) que compara os efeitos de um trap na corrente de dreno considerando apenas o efeito eletrostático com os efeitos considerando também a mudança na mobilidade e no número de portadores, chegou-se a conclusão que a constante  $K_c$  é igual a 3, para o caso de  $\alpha(xl_i) = K_c$ , dado na equação 22. Logo, para calcular o efeito de um trap ocupado na interface foi utilizada a equação à abaixo, e os dados utilizados e calculados estão presentes na Tabela 2:

$$\Delta V_{t} = 3 \cdot \frac{q}{L_{eff} \cdot W_{eff} \cdot C_{OX}}$$

(32)

|                | •               |         | •               |

|----------------|-----------------|---------|-----------------|

| Transitor tipo | Parâmetro       | Valor   | $\Delta V_{_T}$ |

| n              | $L_{\it eff}$   | 17.5nm  | 10.95mV         |

|                | $W_{n,e\!f\!f}$ | 81nm    | 10.93111        |

| p              | $L_{\it eff}$   | 17.5nm  | 4.35mV          |

|                | $W_{n,eff}$     | 202.5nm | 4.33III V       |

Tabela 2 Variação na tensão limiar devido a um trap.

#### 3.4 UMA SIMPLES APROXIMAÇÃO

Como já mencionado anteriormente neste trabalho será feita a análise da presença de interface traps nos transistores de um oscilador em anel. Para uma comparação com resultados posteriores duas simples simulações foram feitas, uma considerando nenhum trap ocupado em todo tempo de simulação do circuito e outra considerando todos os traps ocupados no tempo de simulação. Para os resultados dessas simulações foram dados os nomes de melhor-caso e pior-caso, respectivamente.

Para todas as simulações presentes nesse trabalho será utilizado um oscilador em anel single-ended, Figura 1, feito a partir da tecnologia CMOS 45nm PTM (Cao, 2007). Os seguintes dados já mencionados anteriormente foram utilizados para essa simulação:

$$Wn = 90nm$$

$Wp = 225nm$

Estágios = 3

Primeiramente foram sorteados a partir da distribuição de Poisson os números de traps existente em cada transistor, tendo como médias os valores extrapolados da tabela presente em (Wirth, 2005). Os valores sorteados são mostrados na Tabela 3.

Tabela 3 Número de traps sorteados.

| Transistor | Valor       | Estágio | N° de Traps |

|------------|-------------|---------|-------------|

| Tipo       | Extrapolado |         |             |

|            |             | 0       | 3           |

| n          | 2           | 1       | 4           |

|            |             | 2       | 3           |

|            |             | 0       | 5           |

| p          | 3           | 1       | 4           |

|            |             | 2       | 6           |

Os resultados das duas simulações são mostrados a seguir:

Tabela 4 Resultados da simulações de melhor e pior caso.

| Simulação       | Período    |  |  |

|-----------------|------------|--|--|

| Melhor Caso     | 3.6709E-11 |  |  |

| Pior Caso       | 3.9140E-11 |  |  |

| Desvio de 6.62% |            |  |  |

#### 3.5 SCRIPT

Para realizar o estudo estatístico dos efeitos no período do oscilador devido à captura e emissão de portadores durante o tempo de simulação necessita-se do uso das equações de número 28 a 31, para que seja sorteado a cada instante de tempo, ou passo da simulação, se um trap foi ocupado ou deixou de ser ocupado. Assim modificando durante o tempo de simulação, caso haja modificação no estado do trap, a tensão limiar do transistor. Porém os simuladores Spice não possuem essa capacidade, logo, foi necessário o desenvolvimento de um script que suprisse essa deficiência do simulador Hspice.

Para o desenvolvimento do script optou-se pelo uso da linguagem Perl, pelos seguintes motivos: linguagem de código-aberto, não necessita de compilação, fácil de utilizar para leitura e gravação de arquivos e fácil uso de expressões regulares na procura ou substituições em strings e em arquivos.

Primeiramente o script faz o sorteio da quantidade de traps existente em cada transistor, como mostrado na seção 3.3, após é sorteado, utilizando distribuição uniforme, as propriedades  $p_i$ ,  $E_T - E_F$  e o estado inicial do trap, ou seja, ocupado ou desocupado, e é calculado os  $V_T$  dos transistores, como mostra equação 32, partindo dessas informações o script cria um arquivo de netlist do Hspice, e chama a execução do mesmo.

Após o fim da execução do Hspice, o script inicia a leitura do arquivo de saída gerado, Figura 19.

| time     | voltage<br>ent0 | voltage<br>ent1 | voltage<br>ent2 |

|----------|-----------------|-----------------|-----------------|

| 0.       | 68.3538m        | 500.0007m       | 991.7698m       |

| 1.00000f | 68.3422m        | 500.0462m       | 991.7624m       |

| 2.00000f | 68.3361m        | 500.0739m       | 991.7585m       |

| 3.00000f | 68.3304m        | 500.0995m       | 991.7547m       |

| 4.00000f | 68.3246m        | 500.1252m       | 991.7509m       |

| 5.00000f | 68.3046m        | 500.1996m       | 991.7501m       |

| 6.00000f | 68.2846m        | 500.2740m       | 991.7493m       |

Figura 19 Formato de saída gerado pelo HSpice.

Para cada passo simulado é lida a tensão nas entradas dos transistores e calculada à probabilidade de uma mudança no estado de cada um dos traps naquele instante, de acordo com a tensão aplicada, como é mostrado nas equações 28 a 31. Com base nas probabilidades calculadas é feito o sorteio se o trap sofreu ou não a mudança de estado, caso um ou mais traps sofreram mudança no seu estado um novo netlist é criado com os novos valores de  $V_T$  e com as informações das tensões iniciais dos transistores, as tensões iniciais são geradas a partir das tensões existentes nos transistores no momento da mudança de estado do trap. Com a criação de um novo netlist o HSpice é executado novamente repetindo-se o ciclo até que o número estipulado de períodos, configurado no script, tenha sido medido. O script também tem como função a medida do período de oscilação, escrevendo o resultado em um arquivo de saída.

O funcionamento mais detalhado pode ser visto no fluxograma presente na Figura 20 e, ou, na leitura do script presente no Apêndice.

Figura 20 Fluxograma simplificado do script criado.

O resultado obtido com o uso do script, para um oscilador com 3 estágios de inversores e número de traps presentes na Tabela 3, pode ser visto na Figura 21. Nessa simulação o script foi simulado para um número de períodos aproximadamente igual a 12000, os dados estatísticos podem ser vistos na Tabela 5.

Figura 21 Distribuição dos períodos medidos.

Tabela 5 Resultados estatísticos da simulação do script.

| Mínimo        | 3.6784E-11  |

|---------------|-------------|

| Máximo        | 3.8338E-11  |

| Média         | 3.7370E-11  |

| Desvio Padrão | 2.06329E-13 |

Analisando os dados da tabela acima se pode notar que para 12000 amostras de período, não foi possível encontrar a situação de pior caso expressada na seção 3.4, porém o melhor caso foi praticamente atingido. Com isso e com o dado presente na tabela logo se nota que a média não é equivalente à média entre o melhor caso e o pior caso. Outro ponto

interessante em se notar é que o desvio entre o valor mínimo e máximo foi de 4.2% enquanto na seção 3.4 foi de 6.62%.

Para analisar o impacto do jitter em comunicações seriais fez-se uso da equação 6, afim de calcular o phase-jitter. Foi calculado a incerteza, ou desvio padrão, do clock que existiria para cada m períodos transcorridos, como mostrado abaixo.

Figura 22 Desvio padrão em função de m períodos transcorridos.

Quando o oscilador é utilizado em núcleos de PLLs a incerteza existente em um tempo muito grande não é um sério problema uma vez que o PLL amarra a fase do oscilador, porém em escalas de tempo menores que a largura de banda do PLL o oscilador deve ter uma boa performance de phase-jitter (Mc Neill, 1999). Sendo essa performance importante no projeto de PLLs.

Pode-se dizer que se o clock, que deve estar sincronizado com os dados da transmissão serial, se desviar de meio período a transmissão irá falhar, ou seja, o receptor estará "pulando" dados ou repetindo o mesmo dado.

Com base nesse argumento foi calculada a probabilidade de falha em função de m. A probabilidade foi calculada levando em conta que o desvio do clock calculado segue uma distribuição normal com média zero, seção 2.4. De acordo com a equação abaixo, foi

calculada quantas vezes o valor de meio período representa do desvio padrão e utilizando isso com a tabela de distribuição normal é possível calcular a probabilidade de que o clock se desvie de mais de meio período no tempo transcorrido. Os dados calculados são dados na Tabela 6.

$$z = \frac{\frac{1}{2}T_{m\acute{e}dio}}{\sigma_m} \tag{33}$$

| Tabala | 6 Dre | shahili | ahahi | do fol | ha |

|--------|-------|---------|-------|--------|----|

| m    | σ        | Z        | Pr     |

|------|----------|----------|--------|

| 10   | 1.07E-12 | 1.75E+01 |        |

| 20   | 1.87E-12 | 9.97E+00 |        |

| 30   | 2.61E-12 | 7.16E+00 |        |

| 50   | 3.91E-12 | 4.78E+00 |        |

| 100  | 6.45E-12 | 2.90E+00 | 0.38%  |

| 150  | 8.38E-12 | 2.23E+00 | 2.58%  |

| 300  | 1.27E-11 | 1.47E+00 | 14.16% |

| 400  | 1.47E-11 | 1.27E+00 | 20.40% |

| 500  | 1.62E-11 | 1.15E+00 | 25.02% |

| 600  | 1.75E-11 | 1.07E+00 | 28.46% |

| 700  | 1.85E-11 | 1.01E+00 | 31.24% |

| 800  | 1.95E-11 | 9.59E-01 | 33.70% |

| 900  | 2.02E-11 | 9.24E-01 | 35.76% |

| 1000 | 2.08E-11 | 8.96E-01 | 36.82% |

| 1500 | 2.31E-11 | 8.08E-01 | 41.80% |

| 2000 | 2.50E-11 | 7.47E-01 | 45.32% |

### 3.6 RESULTADOS PARA DIFERENTES SIMULAÇÕES

### 3.6.1 Oscilador de três estágios

Fazendo-se algumas simulações do script para o mesmo circuito, oscilador em anel de três estágios. Sendo que para cada simulação novos números de traps e novos valores das propriedades dos traps foram sorteados. Os resultados alcançados são mostrados abaixo:

Tabela 7 Resultados para várias simulações do oscilador de 3 estágios.

|               | Simulação 1 | Simulação 2 | Simulação 3 | Simulação 4 | Simulação 5 | Simulação 6 |

|---------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Mínimo        | 3.6784E-11  | 3.6786E-11  | 3.6713E-11  | 3.6762E-11  | 3.6793E-11  | 3.6683E-11  |

| Média         | 3.7370E-11  | 3.7138E-11  | 3.7181E-11  | 3.7203E-11  | 3.7361E-11  | 3.6989E-11  |

| Máximo        | 3.8338E-11  | 3.7811E-11  | 3.7823E-11  | 3.7838E-11  | 3.8261E-11  | 3.7609E-11  |

| Desvio Padrão |             | 1.5009E-13  |             |             |             |             |

Simulação 7 Simulação 8 Simulação 9 Simulação 10 Simulação 11 3.6741E-11 3.6664E-11 3.6733E-11 3.6738E-11 3.7294E-11 3.7089E-11 3.7420E-11 3.7047E-11 3.7438E-11 3.8032E-11 3.7703E-11 3.8289E-11 3.7586E-11 3.8379E-11 2.0099E-13 1.6994E-13 2.4981E-13 1.3589E-13 2.5074E-13

Analisando a tabela acima, nota-se que, devido as diferentes quantidades de traps presentes nas simulações e aos diferentes tempos de emissão e captura, a média, o desvio padrão, o valor mínimo e máximo medido de cada simulação foi diferente. O desvio entre o maior e o menor valor máximo foi de mais de 2% as médias tiveram desvio de mais de 1.2%, os desvios padrões se desviaram de 72.66% e enquanto os valores mínimos permaneceram praticamente os mesmos se desviando de 0.33%.

# 3.6.2 Oscilador de cinco estágios

Tabela 8 Resultados para o oscilador de 5 estágios.

|               | Simulação 1 | Simulação 2 | Simulação 3 | Simulação 4 | Simulação 5 | Simulação 6 |

|---------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Mínimo        | 6.4274E-11  | 6.43165E-11 | 6.4309E-11  | 6.4499E-11  | 6.4404E-11  | 6.41941E-11 |

| Média         | 6.4765E-11  | 6.49771E-11 | 6.4859E-11  | 6.5224E-11  | 6.506E-11   | 6.44975E-11 |

| Máximo        | 6.5459E-11  | 6.57914E-11 | 6.5576E-11  | 6.6188E-11  | 6.5924E-11  | 6.49605E-11 |

| Desvio Padrão | 1.8545E-13  | 2.50154E-13 | 2.1775E-13  | 2.5715E-13  | 2.3953E-13  | 1.21229E-13 |

Simulação 7 Simulação 8 Simulação 9 Simulação 10 6.43059E-11 6.4314E-11 6.4513E-11 6.4378E-11 6.49266E-11 6.5042E-11 6.50513E-11 6.51085E-11 6.56851E-11 6.5892E-11 6.59205E-11 6.59383E-11 2.3719E-13 2.5159E-13 2.25599E-13 2.62914E-13

Analisando os dados pode-se dizer que o desvio entre o maior valor máximo e o menor valor mínimo foi de cerca de 3.1%, o desvio entre maior e menor máximo foi de 1.9%,

o desvio entre a maior e menor média foi de 1.12%, desvio do valor mínimo foi de 0.47% e a diferença entre o maior e menor desvio padrão foi de 124%.

Seguindo o mesmo raciocínio da secção 3.4 foi simulado o pior caso e o melhor caso, tendo o pior-caso todos os traps ocupados, existentes na simulação 10 da Tabela 8.

Tabela 9 Simulação de pior e melhor caso para oscilador de 5 estágios.

| Simulação       | Período    |  |  |

|-----------------|------------|--|--|

| Melhor Caso     | 6.4246E-11 |  |  |

| Pior Caso       | 6.7543E-11 |  |  |

| Desvio de 5.13% |            |  |  |

# 3.6.3 Oscilador de sete estágios

Para um oscilador de sete estágios e novamente fazendo algumas simulações com diferentes quantidades de traps e diferentes propriedades os resultados são dados a seguir:

Tabela 10 Resultados para o oscilador de 7 estágios.

|               | Simulação 1 | Simulação 2 | Simulação 3 | Simulação 4 | Simulação 5 | Simulação 6 |

|---------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Mínimo        |             |             |             |             |             | 9.03851E-11 |

| Média         | 9.14579E-11 | 9.14258E-11 | 9.12513E-11 | 9.1015E-11  | 9.07488E-11 | 9.13112E-11 |

| Máximo        |             |             |             |             |             | 9.23709E-11 |

| Desvio Padrão | 3.39563E-13 | 2.9041E-13  | 2.5537E-13  | 2.8031E-13  | 1.86589E-13 | 2.98881E-13 |

| Simulação 7 | Simulação 8 | Simulação 9 | Simulação 10 |

|-------------|-------------|-------------|--------------|

| 9.0247E-11  | 9.0427E-11  | 9.032E-11   | 9.02748E-11  |

| 9.1297E-11  | 9.1192E-11  | 9.1132E-11  | 9.09534E-11  |

|             |             |             | 9.16772E-11  |

| 2.8978E-13  | 2.7247E-13  | 2.6311E-13  | 2.33167E-13  |

Analisando os dados pode-se dizer que o desvio entre o maior valor máximo e o menor valor mínimo foi de cerca de 2.8%, o desvio entre maior e menor máximo foi de 1.4%, o desvio entre a maior e menor média foi de 0.78%, desvio do valor mínimo foi de 0.58% e o desvio entre o maior e menor desvio padrão foi de 82%.

Assim como calculado na Tabela 6, a Tabela 11 mostra a probabilidade de falha do oscilador da simulação 1. Pode-se notar probabilidade de falha foi semelhante a dada pelo oscilador de 3 estágios.

Tabela 11 Probabilidade de falha para oscilador de 7 estágios.

| m    | σ        | Z        | Pr     |

|------|----------|----------|--------|

| 10   | 1.97E-12 | 2.30E+01 |        |

| 20   | 3.50E-12 | 1.30E+01 |        |

| 30   | 4.89E-12 | 9.28E+00 |        |

| 50   | 7.37E-12 | 6.16E+00 |        |

| 100  | 1.22E-11 | 3.71E+00 | 0.02%  |

| 150  | 1.60E-11 | 2.84E+00 | 0.46%  |

| 200  | 1.95E-11 | 2.33E+00 | 1.98%  |

| 300  | 2.62E-11 | 1.73E+00 | 8.36%  |

| 400  | 3.13E-11 | 1.45E+00 | 14.70% |

| 500  | 3.55E-11 | 1.28E+00 | 20.06% |

| 600  | 3.89E-11 | 1.17E+00 | 24.20% |

| 700  | 4.22E-11 | 1.08E+00 | 28.02% |

| 800  | 4.51E-11 | 1.01E+00 | 31.24% |

| 900  | 4.75E-11 | 9.54E-01 | 34.22% |

| 1000 | 5.00E-11 | 9.07E-01 | 36.83% |

| 1250 | 5.45E-11 | 8.33E-01 | 40.66% |

| 1500 | 5.75E-11 | 7.89E-01 | 42.96% |

Simulando o pior-caso e o melhor-caso, tendo o pior-caso todos os traps ocupados, existentes na simulação 1 da Tabela 10, foi encontrado os seguintes resultados:

Tabela 12 Simulação de pior e melhor caso para oscilador de 7 estágios.

| Simulação      | Período    |  |  |

|----------------|------------|--|--|

| Melhor Caso    | 9.0144E-11 |  |  |

| Pior Caso      | 9.5248E-11 |  |  |

| Desvio de 5.6% |            |  |  |

### 3.6.4 Análise dos resultados

A análise estatística dos osciladores de três, cinco e sete estágios teve como período máximo encontrado de 3.8379E-11, 6.6188E-11 e 9.27025E-11 respectivamente. Entretanto

os valores máximos possíveis encontrados na simulação pior-caso foram de 3.9140E-11, 6.7543E-11 e 9.5948E-11para o mesmo número de traps da análise estatística. Como mostra a Tabela 13 quanto maior o número de estágios maior é a diferença entre o máximo encontrado com o uso do script e o pior caso possível. Esse aumento na diferença pode ser facilmente explicado pelo limitado número de períodos medido pelo script, foram de cerca de 2000 para cada simulação. Como a situação de pior-caso acontece quando todos os traps estão ocupados e assim permanecem por um longo período de tempo até que a oscilação se estabilize, conclui-se que a probabilidade de ocorrer à situação de pior-caso diminui quanto maior o número de traps. Logo, para um número maior de estágios é de se esperar um número total de traps maior e assim, uma probabilidade menor de se atingir a situação de pior-caso.

Tabela 13 Desvio do máximo encontrado e do pior-caso.

| N°<br>estágios | Máximo encontrado | Pior-Caso  | Desvio (%) |

|----------------|-------------------|------------|------------|

| 3              | 3.8379E-11        | 3.9140E-11 | 1.98       |

|                | 6.5938E-11        |            | 2.43       |

| 7              | 9.2703E-11        | 9.5248E-11 | 2.75       |

Também se pode notar que quanto maior o número de estágio menor será os desvios da média, dos valores mínimos e dos valores máximos.

# 4 CONCLUSÕES E TRABALHOS FUTUROS

A partir deste trabalho se verifica que o efeito RTS para a tecnologia de 45nm, afeta significativamente o desempenho de osciladores em anel. Nas análises temporais feitas o aumento de jitter foi significativo para circuitos de grande desempenho. Também se pôde observar que a caracterização dos osciladores utilizando como margem de segurança a incerteza dada pelos pior e melhor casos são um tanto quanto pessimistas, pois a probabilidade de ocorrência do pior caso é extremamente baixa, não sendo alcançada em nenhuma das simulações aqui apresentadas.

Na análise de phase jitter se verificou que o RTS contribuiu fortemente no aumento da incerteza da fase do oscilador com o tempo, sendo essencial sua consideração no projeto de PLLs para sincronização do clock.

Este trabalho ficou focado em um único método para controle de frequência do oscilador em anel, variando apenas seu número de estágios, para trabalhos futuros, um interessante tópico seria a comparação das técnicas de controle de frequência, tal como, inserção de capacitância e mudança na capacidade de corrente, para assim poder escolher um design com baixo impacto de RTS. Também seria interessante uma análise conjunta de clock buffers e ou clock gating na saídas do oscilador, já que podem ser fontes de ruído RTS significativas para circuitos digitais.

# REFERÊNCIAS

ALEXANDER, C. L. et al. Impact of Single Charge Trapping in Nano-MOSFETs—Electrostatics Versus Transport Effects. **IEEE Transactions on Nanotechnology**, v. 4, n. 3, mai. 2005.

BHUSHAN, M. et al. Ring Oscillators for CMOS Process Tuning and Variability Control. **IEEE Transactions on Semiconductors Manufacturing**, [S. l.], v. 19, n. 1, p 10-18, fev. 2006.

BRUSAMARELLO, L.; WIRTH, G. I.; DA SILVA, R. Statistical RTS model for digital circuits. **Microelectronics Reliability**, [S. 1.], v. 49. p 1064-1069, nov. 2009.

CAO Y, MCANDREW C. Mosfet modeling for 45 nm and beyond. In: Proc. IEEE/ACM Int. conference on Computer-aided design. Piscataway (NJ, USA): **IEEE Press**; 2007. p. 638–43.

KIRTON, M. J.; UREN, M. J.; Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frquency (1/f) noise. **Advances in Physics**, [S. l.], v. 38, n. 4, p 367-468, 1989.

LUKYANCHIKOVA, N.B. et al. Influence of the substrate voltage on the randomtelegraph signal parameters in submicron n-channelmetal-oxide-semiconductor field-effect transistors under a constant inversion charge density. **Applied Physics A,** [S. l.], v. 70, p 345-353, 2000.

MARTINEZ, F. et al. Oxide traps characterization of 45 nm MOS transistors by gate current R.T.S. noise measurements. **Microelectronic Engineering**, v. 80, p 54-57, 2005.

MCNEILL, J. A.; RICKETTS, D. S.; The Designer's Guide to Jitter in Ring Oscillators. New York: Springer, 2009. p 1-4; 29-30; 138-141. ISBN: 978-0-387-76526-6.

PIERRET, R. F. **Semiconductor Device Fundamental**. [S. 1.]: Addison Wesley Longman, 1996. p 42; 612-623; 662-667. ISBN-10: 0-201-54393-1.

RABAEY, J. M.; CHANDRAKSAN, A.; NICOLIC B. **Digital Integrated Circuits: a design perpesctive**. [S. 1.]: Prentice-Hall, 2003. p 32-33;501-502. ISBN-10: 0130909963.

SIMOEN, E. et al. Explaining the Amplitude of RTS Noise in Submicrometer MOSFET's. **IEEE Transactions on Electron Devices**, [S. l.], v. 39, n. 2. p 422-429, fev 1992.

TEKTRONIX. **Jitter Analysis:** A Brief guide to Jitter. 2005. p 1-6. Disponível em: <a href="http://www.tektronix.com/jitter">http://www.tektronix.com/jitter</a>. Acesso em: 3 out. 2009.

WIRTH, G. I Modeling of Statistical Low-Frequency Noise of Deep-Submicron MOSFETs. IEEE Transactions On Electron Devices, USA, v. 52, n. 7, p. 1576-1588, 2005.

# APÊNDICE:

Arquivos utilizados pelo script para simulação de RTS em osciladores em anel.

# APÊNDICE: ARQUIVOS UTILIZADOS PELO SCRIPT PARA SIMULAÇÃO

#### NETLIST UTILIZADO

Abaixo segue o exemplo de um Netlist utilizado pelo script para a simulação de um oscilador em anel de 3 estágios.

```

RING OSCILATOR - Teste 1

.include 45nm.lib

**** SUB CIRCUITO ****

** INV

.subckt inv inn inp out vdd

mp out inp vdd vdd pmos 1=45n w=225n

mn out inn 0 0 nmos 1=45n w=90n

.ends inv

**** ALIMENTAÇÃO ****

Va vcc 0 1

**** CIRCUITO ****

xinv0 entn0 entp0 ent1 vcc inv

xinv1 entn1 entp1 ent2 vcc inv

xinv2 entn2 entp2 ent0 vcc inv

**** INCLUIDO PELO SCRIPT ****

.include "rts_inc.sp"

**** SIMULAÇÃO ****

.tran 0.001ps 1500ps

**** MEDIDAS ****

.MEASURE TRAN osc_beg when V(ent1) 0.5 TD = 500p RISE = 1 .MEASURE TRAN osc_end when V(ent1) 0.5 TD = 500p RISE = 2

.MEASURE TRAN v_ent0 find V(ent0) at='osc_beg'

.MEASURE TRAN v_ent1 find V(ent1) at='osc_beg'

.MEASURE TRAN v_ent2 find v(ent2) at='osc_beg'

.measure period param=('osc_end-osc_beg')

.measure frequency param=('1/period')

.print tran v(ent0) v(ent1) v(ent2)

.end

```

### NETLIST CRIADO

Abaixo segue o exemplo do Netlist criado pelo script contendo as mudanças nas tensões de threshold e contendo as condições inicias do script.

```

**** RTS DELTA_Vth ****

VNmos0 ent0 entn0 '3*10.95m'

VNmos1 ent1 entn1 '4*10.95m'

VNmos2 ent2 entn2 '3*10.95m'

VPmos0 ent0 entp0 '-5*4.35m'

VPmos1 ent1 entp1 '-4*4.35m'

VPmos2 ent2 entp2 '-6*4.35m'

**** INITIAL CONDITIONS ****

.IC V(ent0)=6.8354E-02

.IC v(ent1)=5.0000E-01

.IC v(ent2)=9.9177E-01

```

#### **SCRIPT**

Abaixo segue script utilizado para a simulação de RTS em osciladores em anel, no exemplo o script está configurado para a simulação de 10 diferentes osciladores de 3 estágios.

```

#!/usr/bin/perl

use warnings;

use strict;

#use Math::Random;

#use lib qw(/home/mbs/TCC/Math/blib/lib/ ./);

use Math::Random qw(:all);

use POSIX;

for (my \$var = 0; \$var < 10; \$var++) {

my (@ntr_nmos, @ntr_pmos);

my (@trn, @trp);

my (@dn, @dp);

my (@pi_nmos, @pi_pmos);

my (@delta_E_nmos, @delta_E_pmos);

my (@pf, @nf, $filein);

######################

# Parametros do Circuito

#######################

my $n_stages=3;

my \$lmin = 17.5e-9;

my \$wmin = 80e-9;

```

```

my \$wpmos = 225e-9;

my \$wnmos = 90e-9;

my \$vdd = 1;

##########################

########################

# Parametros da Simulação

########################

my delta_t = 1e-13;

my t_{tran} = 100e-9;

##########################

##############################

# Parametros da Tecnologia

##########################

# charge of 1 electron

my q_charge = 1.602e-19;

my $Q = 2; # Si-SiO2

my tox_pmos = 1.1e-09;

my $tox_nmos = 1.1e-09;

my \$e0 = 8.854e-12;

my \$eox = 3.9*\$e0;

my $coxn = $eox/$tox_nmos;

my $coxp = $eox/$tox_pmos;

my \$alpha = 3;

my \ pi_max = 11;

my $pi_min = 9;

my delta_E = 0.56;

#########################

#########################

# Variaveis Globais

########################

my ($t, $lixo);

my \$guarda_t = 0;

my (@trn_ant, @trp_ant);

my $guarda_p;

my $guarda_p_ant = 0;

open(FH_saida, "> saida_$var.txt") or die("Could not create file:

saida.txt.");

for (my $i=0; $i < $n_stages; $i++) {

my $ntr lambda n=2*floor(($lmin*$wnmos)/($wmin*$lmin));

my $ntr_lambda_p=2*floor(($lmin*$wpmos)/($wmin*$lmin));

$ntr_nmos[$i]=random_poisson(1,$ntr_lambda_n);

print("\n$ntr_nmos[$i]\n");

$ntr_pmos[$i]=random_poisson(1,$ntr_lambda_p);

print FH_saida "NUMERO DE TRAPS - ESTAGIO $i : \t PMOS = $ntr_pmos[$i] \t

NMOS = $ntr_nmos[$i]\n";

# populate traps NMOS

```

```

my $initn_oc;

for (my \ j=0; \ j < ntr_nmos[\]; \ j++) {

t_{ij} = t

$pi_nmos[$i][$j] = random_uniform_integer(1, $pi_min, $pi_max);

$delta_E_nmos[$i][$j] = random_uniform(1, -$delta_E, $delta_E);

$initn_oc += $trn_ant[$i][$j];

\sinh[\$i][\$j] = \$alpha*(\$q\_charge/((\$wnmos*0.9)*\$lmin*\$coxn)); #*(1-

($xt/$tox_nmos));

}

# populate traps PMOS

my $initp_oc;

for (my \ \ j=0; \ \ j < ntr_pmos[\ i]; \ \ j++) {

strp_ant[si][sj] = (random_uniform(1, 0, 1)>0.5) ? (0) : (1);

$pi_pmos[$i][$j] = random_uniform_integer(1, $pi_min, $pi_max);

$delta_E_pmos[$i][$j] = random_uniform(1, -$delta_E, $delta_E);

$initp_oc += $trp_ant[$i][$j];

($xt/$tox_pmos));

print FH_saida "\tINICIALMENTES OCUPADOS: \t PMOS = $initp_oc \t NMOS =

$initn_oc\n";

print FH_saida "\tPi: \t PMOS = @{\$pi_pmos[\$i]}[0..\$ntr_pmos[\$i]-1] \t

NMOS = \{\{pi\_nmos[\{i\}]\} [0..\{ntr\_nmos[\{i-1]]\} n"\}\}

print FH_saida "\tDelta E \t PMOS =

@{\$delta_E_pmos[\$i]}[0..\$ntr_pmos[\$i]-1] \t NMOS =

\{ \text{delta}_E_n mos[\$i] \} [0..\$ntr_n mos[\$i]-1] \n";

cria_spice_include_file("condicao_inicial");

system("sudo hspice -i osc_rts.sp -o osc_rts.lis") == 0

or die("system falhou: $?");

while ($guarda_t < $t_tran) {</pre>

my $rline=0;

my $line_number = 0;

my $1;

open(FH_READ, "<osc_rts.lis") or die("Nao pode abrir arquivo

osc_rts.lis");

my (@dvt_n_gua, @dvt_p_gua, @v_gua);

my @file = <FH_READ>;

foreach $1 (@file) {

chomp($1);

my (@dvt_n, @dvt_p, @v);

if( $1 = ~/^x$/){}

$rline = 1;

elsif( $1 = ~/^y$/){

$rline = 0;

my $guarda_p_atual = $guarda_t + $guarda_p;

$guarda_t = $guarda_t + $t;

my $periodo = $guarda_p_atual - $guarda_p_ant;

$guarda_p_ant = $guarda_p_atual;

print FH_saida "$periodo\n";

print("Iniciando simulaçao t\: $guarda_t\n");

close(FH_READ);

cria_spice_include_file(\@dvt_n_gua, \@dvt_p_gua, \@v_gua);

system("sudo hspice -i osc_rts.sp -o osc_rts.lis") == 0

or die("system falhou: $?");

last:

```

```

\} elsif (($rline >= 1) && ($rline <=4)){

$rline++;

} elsif ($rline >4){

# time

voltage

voltage

voltage

500.0007m

991.7697m

# 0.

68.3538m

for (my $bloco = 0; $bloco < ceil($n_stages/4); $bloco++) {</pre>

my $ln = $line_number + 706*$bloco;

my $line = $file[$ln];

chomp($line);

=\sim s/m/e-3/q;

line = ~ s/u/e-6/g;

=  s/n/e-9/g;

line = ~ s/p/e-12/g;

le =  s/f/e-15/g;

my @temp = split(/ +/, $line);

my $lixo = shift(@temp);

t = shift(@temp);

push (@v, @temp[0..$#temp]);

my \$mudou_estado = 0;

for (my $i=0; $i < $n_stages; $i++) {

my $occ=0;

my $delta_vn = 0; my $delta_vp = 0;

my vs_n = (v[i]>0.34) ? (0.24505) : (v[i]/1.38129);

my v_p = (v_{ij} < 0.6)? (0.18113) : ((-v_{ij} + 1)/1.34192);

my $dq_nmos = $v[$i]*0.96372+0.03628;

my 4q_pmos = -v[i]*0.96396+1;

for (my \ j=0; \ j < ntr_nmos[\]; \ j++) {

trn[i][i] = trn_ant[i][i];

my  $tau_c = (1/$dq_nmos)*(10**-$pi_nmos[$i][$j])*(1+exp(-

($delta_E_nmos[$i][$j] - $vs_n)));

- $vs_n)));

my $pc = $delta_t/$tau_c;

my $pe = $delta_t/$tau_e;

trn[i][i] = (random_uniform(1, 0, 1) < pe) ? (0) : (1);

} else{

trn[i][i] = (random_uniform(1, 0, 1) < pc) ? (1) : (0);

if ($trn_ant[$i][$j] != $trn[$i][$j]) {

$mudou_estado = 1;

trn_ant[$i][$j] = trn[$i][$j];

$delta_vn= $delta_vn + ($trn[$i][$j])*($dn[$i][$j]);

for (my \ \ j=0; \ \ j < ntr_pmos[\ i]; \ \ j++) {

$trp[$i][$j] = $trp_ant[$i][$j];

my  tau_c = (1/$dq_pmos)*(10**-$pi_pmos[$i][$j])*(1+exp(-

($delta_E_pmos[$i][$j] + $vs_p)));

+ $vs_p)));

my $pc = $delta_t/$tau_c;

my $pe = $delta_t/$tau_e;

if(f(j) = 1){ \# tran i, trap j, occupied}

trp[i][i] = (random_uniform(1, 0, 1) < pe) ? (0) : (1);

```

```

}else{

trp[i][i] = (random_uniform(1, 0, 1) < pc) ? (1) : (0);

if ($trp_ant[$i][$j] != $trp[$i][$j]) {

$mudou_estado = 1;

$trp_ant[$i][$j] = $trp[$i][$j];

$delta_vp=$delta_vp+($trp[$i][$j])*($dp[$i][$j]);

push(@dvt_n, $delta_vn);

push(@dvt_p, $delta_vp);

@dvt_n_gua = @dvt_n;

Qdvt_p_gua = Qdvt_p;

@v_gua = @v;

if ($mudou_estado == 1) {

close(FH_READ);

my $guarda_p_atual = $guarda_t + $guarda_p;

$quarda_t += $t;

if ($guarda_t >= $guarda_p_atual) {

my $periodo = $guarda_p_atual - $guarda_p_ant;

$guarda_p_ant = $guarda_p_atual;

print FH_saida "$periodo\n";

}

print("Montando dados\nDelta_Vtn: @dvt_n\nDelta_Vtp:

@dvt_p\nCondiÃSões Iniciais: @v\nTempo relativo: $t\nTempo Absoluto:

$guarda_t\n");

cria_spice_include_file(\@dvt_n, \@dvt_p, \@v);

system("sudo hspice -i osc_rts.sp -o osc_rts.lis") == 0

or die("system falhou: $?");

last;

quarda_p = 1;

$line_number ++;

close(FH_saida);

sub cria_spice_include_file {

my $dvt_n = shift;

my $dvt_p = shift;

my $v_ic = shift;

if ($dvt_n eq "condicao_inicial") {

dvt_n = [0, 0, 0];

dvt_p = [0, 0, 0];

v_i = [6.8875E-02, 5.0000E-01, 9.9177E-01];

print ("Usando condições iniciais...\n");

}

open(FH, "> rts_inc.sp") or die("Could not create file: rts_inc.sp.");

print FH <<"NETLIST";</pre>

```

```

\*\*\*\ RTS DELTA_Vth \*\*\*

VNmos0 ent0 entn0 $$dvt_n[0]

VNmos1 ent1 entn1 $$dvt_n[1]

VNmos2 ent2 entn2 $$dvt_n[2]

VNmos3 ent3 entn3 $$dvt_n[3]

VNmos4 ent4 entn4 $$dvt_n[4]

VPmos0 ent0 entp0 -$$dvt_p[0]

VPmos1 ent1 entp1 -$$dvt_p[1]

VPmos2 ent2 entp2 -$$dvt_p[2]

VPmos3 ent3 entp3 -$$dvt_p[3]

VPmos4 ent4 entp4 -$$dvt_p[4]

\*\*\*\* INITIAL CONDITIONS \*\*\*

\.IC v(ent0) = \$\$v_ic[0]

\.IC v(ent1)=$$v_ic[1]

\.IC v(ent2)=$$v_ic[2]

\.IC v(ent3)=$$v_ic[3]

\.IC v(ent4) = \$\$v_ic[4]

NETLIST

close(FH);

}

```