UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

OSVALDO MARTINELLO JUNIOR

# **KL-Cuts: A New Approach for Logic Synthesis Targeting Multiple Output Blocks**

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Dr. Renato Perez Ribas Advisor

Prof. Dr. André Inácio Reis Co-advisor

Porto Alegre, October 2010

Martinello Junior, Osvaldo

KL-Cuts: A New Approach for Logic Synthesis Targeting Multiple Output Blocks / Osvaldo Martinello Junior. – Porto Alegre: PPGC da UFRGS, 2010.

85f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2010. Advisor: Renato Perez Ribas; Co-advisor: André Inácio Reis.

AIG. 2. Cut Enumeration. 3. KL-Cuts. 4. Logic Design.

Logic Synthesis. 6. Multiple Output Blocks. 7. Technology Mapping. I. Ribas, Renato Perez. II. Reis, André Inácio. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Flávio Rech Wagner Coordenador do PPGC: Prof. Álvaro Freitas Moreira Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"This is your life and it's ending one minute at a time." — CHUCK PALAHNIUK (FIGHT CLUB)

# ACKNOWLEDGMENTS

It is a pleasure to thank the many people who made this thesis possible.

I am grateful to my advisor, Renato Perez Ribas, for his time and for his sense of organization (which I lack). His understanding, encouraging and personal guidance have provided a good basis for the present thesis.

I would like also to express my gratitude to my co-advisor, André Inácio Reis. His wide knowledge and his logical way of thinking have been of great value for me.

I could not forget to thank my labmates, for supporting my work, for the stimulating discussions, for working together before deadlines, and for all the fun we have had in the last years.

To my oldest friends from Mato Grosso whose friendship molded me as I am, and to my friends who are next to me now with whom I have divided the latest cheer times, my sincere thank you.

I am especially thankful to my family: to my father Osvaldo Martinello, to my mother Cleci Maria Martinello and to my sisters Christine and Caroline. I have missed them a lot during this research time.

I owe my deepest gratitude to my girlfriend Bibiana Strohmayer Alves. Without her encouragement, understanding and love it would have been impossible for me to finish this work.

I need also to thank the ones that funded this period of research (besides my father). The company Nangate Inc under a Nangate/UFRGS research agreement, CNPq Brazilian funding agency through the National Program of Microelectronics (PNM), and the European Community's Seventh Framework Programme under grant 248538 - Synaptic. Without their investment this work would not be possible.

# CONTENTS

| LIST OF FIGURES       1         LIST OF TABLES       1         ABSTRACT       1         RESUMO       1         1 INTRODUCTION       1         1.1 Synthesis       1         1.2 Motivation       20         1.3 Objective       20         1.4 Thesis Organization       20         2.1 Boolean Function and Boolean Network       22         2.2 Equivalence Classes of Logic Functions       24         2.3 Data Structures       22         2.3.1 Directed Acyclic Graph       24         2.3.2 Forest of Trees       24   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABSTRACT       13         RESUMO       17         1       INTRODUCTION       19         1.1       Synthesis       19         1.2       Motivation       20         1.3       Objective       20         1.4       Thesis Organization       21         2       TECHNICAL BACKGROUND       22         2.1       Boolean Function and Boolean Network       22         2.2       Equivalence Classes of Logic Functions       22         2.3       Data Structures       22         2.3.1       Directed Acyclic Graph       24 |

| <b>RESUMO</b> 1 <b>1</b> INTRODUCTION       19 <b>1.1</b> Synthesis       19 <b>1.2</b> Motivation       20 <b>1.3</b> Objective       20 <b>1.4</b> Thesis Organization       20 <b>2 TECHNICAL BACKGROUND</b> 21 <b>2.1</b> Boolean Function and Boolean Network       22 <b>2.2</b> Equivalence Classes of Logic Functions       24 <b>2.3</b> Data Structures       25 <b>2.3.1</b> Directed Acyclic Graph       26                                                                                                       |

| 1       INTRODUCTION       19         1.1       Synthesis       19         1.2       Motivation       20         1.3       Objective       20         1.4       Thesis Organization       20         2       TECHNICAL BACKGROUND       21         2.1       Boolean Function and Boolean Network       22         2.2       Equivalence Classes of Logic Functions       24         2.3       Data Structures       25         2.3.1       Directed Acyclic Graph       24                                                   |

| 1.1Synthesis191.2Motivation201.3Objective201.4Thesis Organization202TECHNICAL BACKGROUND202.1Boolean Function and Boolean Network202.2Equivalence Classes of Logic Functions202.3Data Structures202.3.1Directed Acyclic Graph20                                                                                                                                                                                                                                                                                               |

| 2.1Boolean Function and Boolean Network222.2Equivalence Classes of Logic Functions242.3Data Structures252.3.1Directed Acyclic Graph24                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.3.2       And-Inverter Graph       20         2.3.3       And-Inverter Graph       20         2.3.4       Binary Decision Diagram       21         2.4       Dag Nodes and Tree Nodes       22         2.5       K-Feasible Cuts       22         2.6       Library       30         2.7       Technology Mapping       30         2.7.1       Decomposition       30         2.7.2       Pattern Matching       3         2.7.3       Covering       3                                                                     |

| 3STATE OF THE ART333.1Technology Mapping333.2DAG-Aware AIG rewriting343.3Using Signatures on Cut Computation373.4Factor Cuts333.4.1Complete Cut Factorization333.4.2Partial Cut Factorization34                                                                                                                                                                                                                                                                                                                               |

| 3.5<br>3.6                                                                                                  | <b>TEMPLATE Boolean Matching MethodArea Flow Covering</b>                                                                                                                                                                   | 39<br>42                                     |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| <ul> <li>4 K</li> <li>4.1</li> <li>4.1.1</li> <li>4.2</li> <li>4.3</li> <li>4.3.1</li> <li>4.3.2</li> </ul> | XL-FEASIBLE CUTS         L-Feasible Backcuts         Factor Backcuts         KL-Cuts Generation Algorithm         Unbounded KL-Cuts         KL-Cuts with unbounded K         KL-Cuts with unbounded L                       | 45<br>45<br>46<br>47<br>49<br>50<br>51       |

| <b>5 A</b><br><b>5.1</b><br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br><b>5.2</b><br><b>5.3</b>                    | PPLICATIONS OF KL-CUTS         Technology Mapping         Greedy Covering         Area Flow Covering for Multiple Outputs         Matching         Partitioning         Regularity Extraction         Peephole Optimization | 53<br>53<br>54<br>58<br>61<br>61<br>62       |

| 6 R<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                                | <b>ESULTS L-Feasible Backcuts KL-Cuts Covering Algoritms</b> Greedy Covering         Area Flow Covering for Multiple Output         Multiple Output Matching         Partitioning                                           | 63<br>63<br>64<br>65<br>67<br>69<br>70<br>70 |

| 7 C                                                                                                         | ONCLUSIONS AND FUTURE WORK                                                                                                                                                                                                  | 73                                           |

| A A<br>L<br>A.1<br>A.2                                                                                      | ERENCES<br>PPENDIX <kl-cuts: abordagem="" nova="" para="" síntese<br="" uma="">ÓGICA UTILIZANDO BLOCOS COM MÚLTIPLAS SAÍDAS&gt;<br/>Introdução</kl-cuts:>                                                                   | 75<br>79<br>79<br>80                         |

| A.2.1<br>A.3                                                                                                | Aplicações                                                                                                                                                                                                                  | 80<br>84                                     |

# LIST OF ABBREVIATIONS AND ACRONYMS

- AIG And-Inverter Graph

- BDD Binary Decision Diagram

- CAD Computer-Aided Design

- DAG Directed Acyclic Graph

- DFM Design for Manufacturing

- EDA Electronic Design Automation

- FPGA Field-Programmable Gate Array

- HDL Hardware Description Language

- IPO In-Place Optimization

- LUT Lookup Table

- MFFC Maximum Fanout-Free Cone

- OTR Odd-level Transistor Replacement

- PI Primary Input

- PO Primary Output

- RTL Register Transfer Level

- TSBDD Terminal-Suppressed Binary Decision Diagram

- VHDL VHSIC Hardware Description Language

- VHSIC Very High Speed Integrated Circuits

# **LIST OF FIGURES**

| Figure 2.1:    | A truth table representation of a function.                                                    | 24 |

|----------------|------------------------------------------------------------------------------------------------|----|

| Figure 2.2:    | A Boolean network.                                                                             | 24 |

| Figure 2.3:    | A directed acyclic graph example                                                               | 26 |

| Figure 2.4:    | A forest of trees.                                                                             | 27 |

| Figure 2.5:    | An and-inverter graph.                                                                         | 27 |

| Figure 2.6:    | An example of a BDD                                                                            | 28 |

| Figure 2.7:    | AIG illustrating dag and tree nodes.                                                           | 28 |

| Figure 3.1:    | Different AIG structures for function $f = a * b * c.$                                         | 36 |

| Figure 3.2:    | Two cases of AIG rewriting of a node                                                           | 36 |

| Figure 3.3:    | Naive approach for computing $R[f]_P$                                                          | 40 |

| Figure 3.4:    | A generic view of a truth table                                                                | 40 |

| Figure 3.5:    | Reducing search space by cutting non-maximal branches                                          | 41 |

| Figure 3.6:    | Reducing search space by using symmetry.                                                       | 42 |

| Figure 4.1:    | AIG demonstrating backcut factorization.                                                       | 46 |

| Figure 4.2:    | Pseudo-code for <i>KL</i> -cuts calculation                                                    | 48 |

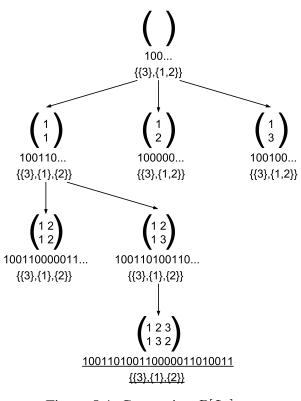

| Figure 4.3:    | AIG illustrating covering.                                                                     | 49 |

| Figure 4.4:    | Pseudo-code for KL-cuts with unbounded K computation                                           | 50 |

| Figure 4.5:    | AIG exemplifying KL-cuts with unbounded $K$                                                    | 51 |

| Figure 4.6:    | Pseudo-code for $KL$ -cuts with unbounded $L$ computation                                      | 52 |

| Figure 5.1:    | An AIG to illustrate the multiple output area flow algorithm                                   | 57 |

| Figure 5.2:    | An AIG with a loop formed by <i>KL</i> -cuts                                                   | 58 |

| Figure 5.3:    | A truth table representation of a set of functions $L_1$                                       | 60 |

| Figure 5.4:    | Computing $R[L_1]_{PP}$                                                                        | 61 |

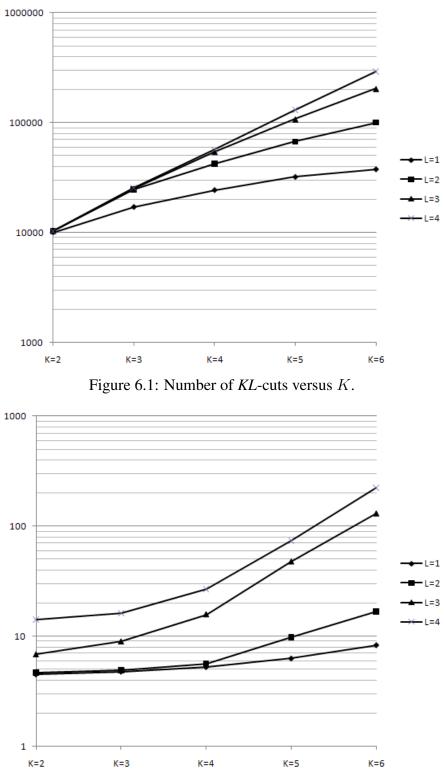

| Figure 6.1:    | Number of <i>KL</i> -cuts versus $K$                                                           | 65 |

| Figure 6.2:    | Time taken to compute KL-cuts versus $K$                                                       | 65 |

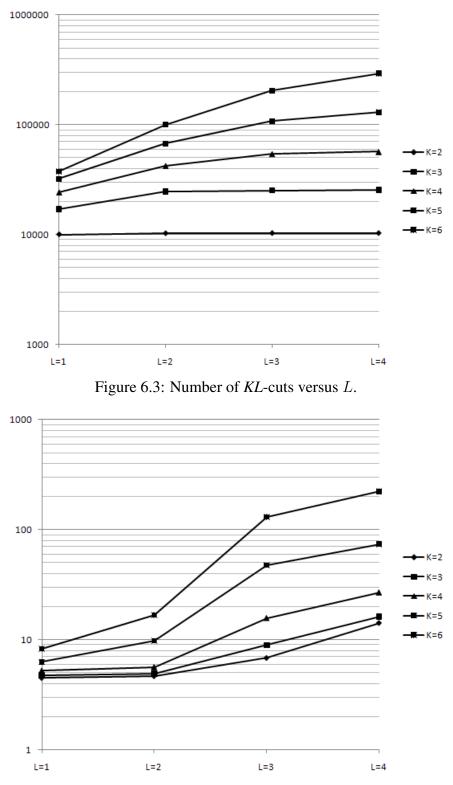

| Figure 6.3:    | Number of KL-cuts versus $L$                                                                   | 66 |

| Figure 6.4:    | Time taken to compute <i>KL</i> -cuts versus <i>L</i>                                          | 66 |

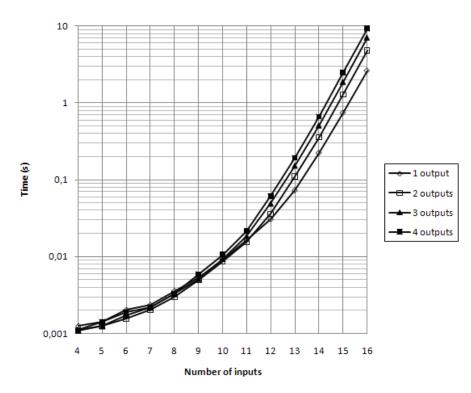

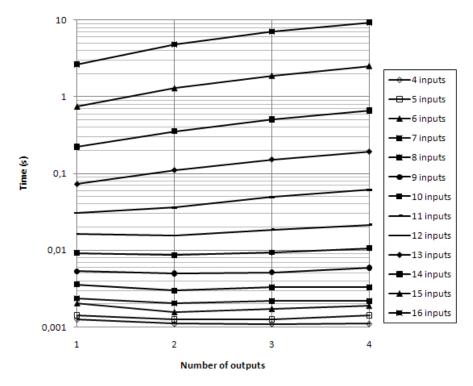

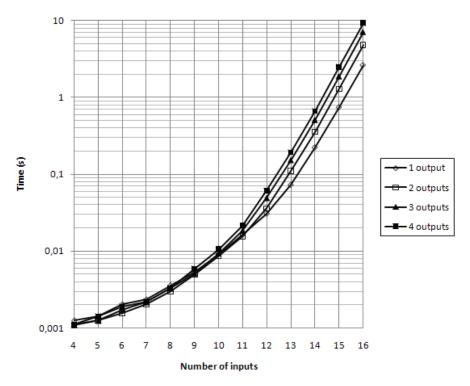

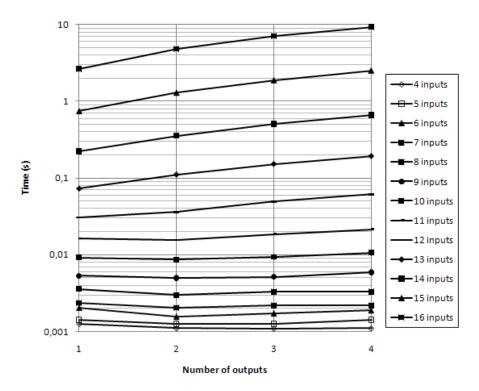

| Figure 6.5:    | Execution time of matching algorithm varying the number of inputs                              | 71 |

| Figure 6.6:    | Execution time of matching algorithm varying the number of outputs.                            | 71 |

| Figure A.1:    | Tempo de execução de algoritmo de identificação de padrões var-<br>iando o número de entradas. | 84 |

| Figure A.2:    | Tempo de execução de algoritmo de identificação de padrões var-                                | 04 |

| 1 15010 1 1.2. | iando o número de saídas.                                                                      | 85 |

# LIST OF TABLES

| Table 2.1:<br>Table 2.2: | Number of equivalence classes under various equivalence relations<br>An example of <i>K</i> -feasible cuts computation                        | 25<br>29 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Table 3.1:               | Effect of iterations in area flow.                                                                                                            | 43       |

| Table 4.1:               | An example of <i>L</i> -feasible backcuts computation                                                                                         | 47       |

| Table 5.1:<br>Table 5.2: | Effect of iterations in multiple output area flow, using only mode 1<br>Effect of iterations in multiple output area flow, using all modes of | 56       |

|                          | operation.                                                                                                                                    | 56       |

| Table 5.3:               | Area flow according to different modes of computing fanout                                                                                    | 56       |

| Table 6.1:               | Benchmark information.                                                                                                                        | 63       |

| Table 6.2:               | Comparison between <i>L</i> -backcut enumeration and factor <i>L</i> -backcut enumeration.                                                    | 64       |

| Table 6.3:               | Comparison between KL-cuts enumeration and factor KL-cuts enu-                                                                                | (7       |

| Table 6.4:               | meration                                                                                                                                      | 67<br>68 |

| Table 6.5:               | Greedy bottom-up covering using <i>KL</i> -cuts.                                                                                              | 68       |

| Table 6.6:               | Greedy bottom-up covering using <i>KL</i> -cuts                                                                                               | 69       |

| Table 6.7:               | Covering using the area flow for multiple outputs algorithm.                                                                                  | 70       |

| Table 6.8:               | Comparison between a covering with factor trees and a covering with                                                                           | 70       |

| 10010 0.0.               | KL-cuts with unbounded $K$                                                                                                                    | 72       |

| Table A.1:               | Cobertura para LUTs de uma saída usando ABC e fluxo de área                                                                                   | 81       |

| Table A.2:               | Cobertura gulosa usando cortes- <i>KL</i>                                                                                                     | 82       |

| Table A.3:               | Mapeamento de fluxo de área para múltiplas saídas                                                                                             | 83       |

|                          |                                                                                                                                               |          |

# ABSTRACT

This thesis introduces the concept of KL-feasible cuts, which allows controlling both the number K of inputs and the number L of outputs in a circuit region. The design of a digital circuit can roughly be divided in two phases: logic synthesis and physical synthesis. Within logic synthesis, one of the main steps is the technology mapping. Traditionally, the technology mapping process only handles single output functions, in order to construct circuits. The objective of this method is to explore the use of multiple output blocks on technology mapping. To provide scalability, the concept of factor cuts is extended to KL-cuts. Algorithms for enumerating these cuts and also for enumerating some subsets of cuts with some special characteristics are presented and results are shown. As examples of practical applications, different covering algorithms are proposed. The greedy algorithm is a simple alternative and produces good results in area, but it is too restrictive, as it is not practical in timing oriented mapping. The other covering algorithm presented is an extension to the area flow algorithm and allows cuts with multiple outputs to be used while making possible the control of some other costs. A Boolean matching algorithm that is able to handle multiple output blocks is also described, which permits the use of a standard cell library with more than one output on technology mapping. The results show the viability and usefulness of the method.

**Keywords:** AIG, Cut Enumeration, KL-Cuts, Logic Design, Logic Synthesis, Multiple Output Blocks, Technology Mapping.

#### KL-Cuts: Uma Nova Abordagem para Síntese Lógica Utilizando Blocos com Múltiplas Saídas

## RESUMO

Esta dissertação introduz o conceito de cortes KL, o que permite controlar tanto o número K de entradas como o número L de saídas em uma região de um circuito. O projeto de um circuito digital pode ser dividido em duas fases: síntese lógica e síntese física. Dentro de síntese lógica, um dos principais passos é o mapeamento tecnológico. Tradicionalmente, o processo de mapeamento tecnológico somente lida com funções de saída única, para a construção de circuitos. O objetivo deste método é explorar o uso de blocos de múltiplas saídas no mapeamento tecnológico. Para prover escalabilidade, o conceito de fatoração de cortes é estendido para os cortes KL. Algoritmos para enumerar esses cortes e também para enumerar alguns subconjuntos de cortes com características específicas são apresentados e os resultados são mostrados. Como exemplos de aplicações práticas, diferentes algoritmos de cobertura são propostos. O algoritmo guloso é uma alternativa simples e produz bons resultados em área, mas é muito restritivo, pois não é factível em mapeamento orientado à atraso. Outro algoritmo de cobertura apresentado é uma extensão do algoritmo de fluxo de área e permite a utilização de cortes com várias saídas, mantendo possível a consideração de outros custos. Um algoritmo de correspondência Booleana que é capaz de lidar com blocos com múltiplas saídas também é descrito. Isso permite a utilização de uma biblioteca padrão com células com mais de uma saída no mapeamento tecnológico. Os resultados mostram a viabilidade e utilidade do método.

**Palavras-chave:** AIG, Blocos com Múltiplas Saídas, Enumeração de Cortes, KL-Cuts, Mapeamento Tecnológico, Projeto Lógico, Síntese Lógica.

# 1 INTRODUCTION

Technologies based on digital integrated circuits have major impact on society, being present on virtually every knowledge area. The advances in the field of conception of integrated circuits make possible the aggregation of an increasingly large number of components on a same device. This high integration scale imposes new challenges to the synthesis process. In order to deal with constant changes in the design rules, and to increase productivity, the automation of this process through the use of EDA (Electronic Design Automation) tools plays a crucial role.

Usually the design methodologies are classified as custom and semicustom design (MICHELI, 1994). In the former methodology, both functional and physical designs are handcrafted, requiring hard skilled designers and a great effort in order to fine-tune features of the circuit. This methodology has, therefore, a high cost, which may be compensated by a high quality design. Semicustom design consists in establishing design restrictions, such as limiting the number of primitives, which limit the ability of optimization of a circuit. This reduction on the solution space makes easier the development of CAD (Computer-Aided Design) tools for design and optimizations, reducing the time-to-market of a design. Currently the number of semicustom designs outnumbers custom design.

## 1.1 Synthesis

The goal of the circuit synthesis is to transform a higher abstraction level description of a circuit into a more detailed model, such as a geometrical model. The whole synthesis process is often broken into three major steps: architectural synthesis, logic synthesis and physical synthesis (MICHELI, 1994). The architectural synthesis, often called high-level synthesis, consists of transforming a behavioral description of a system — usually represented in an HDL (Hardware Description Language), such as VHDL or Verilog, or even in a higher abstraction level language, such as SystemC — into a structural view, which describes the organization of the system, mainly described in RTL (Register Transfer Level).

The next step is the logic synthesis, whose role is to translate a logic description of a circuit into a network of interconnected cells of a given technology. It is typically divided in three phases: technology independent optimizations, technology mapping and technology dependent optimizations. The first one applies some transformations that do not depend on the technology, but depend on the chosen mapping algorithm. These transformations can be structural or Boolean. Then the technology mapping phase binds the circuit with the technology, by mapping portions of the circuit to a cell implemented in the target technology. After that, more optimizations are applied to the mapped circuit, such as cell resizing or logic duplication. These are called technology dependent optimizations.

The physical synthesis, or geometrical level synthesis, physically distributes the cells and performs its interconnections. The final product is a layout of the circuit that implements the initial behavioral description of the system.

## **1.2** Motivation

Some recent advances on logic synthesis are based on And-Inverter Graphs (AIGs), for scalability reasons (LING; ZHU; BROWN, 2008; MISHCHENKO; BRAYTON, 2006). Part of these advances is based on the concept of *K*-feasible cuts (CONG; WU; DING, 1999; PAN; LIN, 1998), including algorithms for re-synthesis based on AIG rewriting (MISHCHENKO; CHATTERJEE; BRAYTON, 2006). Scalability is obtained by keeping the value of *K* small so that logic functions can be manipulated as vectors of integers. For instance, in (MISHCHENKO; BRAYTON; CHATTERJEE, 2008) scalability is achieved by using functions of 16 or less inputs represented as binary truth-tables.

Algorithms for efficient cut computation are well known for single output cuts. Particularly, algorithms for exhaustive computation of K-feasible cuts were introduced by Cong (CONG; WU; DING, 1999) and Pan (PAN; LIN, 1998). Chatterjee (CHATTER-JEE; MISHCHENKO; BRAYTON, 2006) introduced the concept of factor cuts, where exhaustive enumeration is avoided by making a separation between dag nodes and tree nodes in the AIG. The computation of factor cuts enables to work with cuts up to 16 inputs, which is not possible with the previous algorithms of exhaustive enumeration. All these algorithms for cut enumeration are only able to take the number K of inputs into account, not contemplating the benefits of multiple output reasoning. For example, in technology mapping using K feasible cuts, logic duplication may occur during the step of covering, which is likely a problem on a design flow.

Even though current technologies do support blocks with more than one output, such as FPGAs (HUTTON et al., 2004; COSOROABA; RIVOALLON, 2006), the entire flow is currently oriented to single output blocks, and a combination step is added in the end to try to take advantage of these multiple output elements.

## 1.3 Objective

The objective of this thesis is to introduce the idea of controlling the number of outputs L in K-feasible cuts. This way, by enumerating KL-cuts, we are able to deal directly with multiple output blocks throughout the logic synthesis process. Applications of KL-cuts may include peephole optimization (WERBER; RAUTENBACH; SZEGEDY, 2007), regularity extraction (ROSIELLO et al., 2007) and technology mapping. The use of KL-feasible cuts in peephole optimization is justified as an arbitrary portion of the circuit, potentially having multiple outputs, can be exchanged by another one by taking into account all signals which it affects at once. Its use in regularity extraction can be justified as many regular (logic) patterns are composed of multiple output circuits. This is especially true for arithmetic circuits, e.g. full adder and half adder library cells. Technology mapping aiming dual output blocks is already a reality (HUTTON et al., 2004; COSOROABA; RIVOALLON, 2006), and multiple output blocks should be explored, even on a standard cell flow.

### **1.4 Thesis Organization**

The remaining of this thesis is organized as follows.

- Section 2: *Technical Background* Provides the reader with all basic and consolidated knowledge that is needed to understand the concepts presented in this work.

- **Section 3:** *State of the Art* Traces an evolutionary line over the technology mapping, and describes some recent works that are connected to the work presented in this document.

- Section 4: *KL-Feasible Cuts* Describes the main contribution of this work, which is the concept of *KL*-cuts, along with some algorithms for its enumeration. It also discusses some properties of specific types of *KL*-cuts.

- **Section 5:** *Applications of KL-Cuts* Shows a number of proposed applications for *KL*-cuts. Some of them are defined in this thesis, including mapping algorithms and a Boolean matching, and are discussed in detail. Others are just discussed more generally as possible applications, like peephole optimizations and regularity extraction.

- **Section 6:** *Results* Presents and discusses results of several experiments. These results are cross referenced throughout the text, so the reader can check this section while reading the other sections of this document.

- Section 7: *Conclusions and Future Work* Presents some conclusions, summarizes the contributions of this work, and discusses some possible future work.

# 2 TECHNICAL BACKGROUND

This section provides a review of the basics needed to understand the concepts introduced by this work. The idea of Boolean functions and Boolean networks is illustrated, and the classification of an equation into equivalence classes is explained. It explains as well how functions can be represented using different data structures. Then a manner to enumerate ways of breaking these data structures into smaller and more easily treatable ones is discussed. This is followed by a succinct revision on cell libraries and technology mapping.

#### 2.1 Boolean Function and Boolean Network

The *Boolean set* is defined as  $B = \{0, 1\}$ , whose elements can be interpreted as logic values. Usually the 0 value means *false* and the 1 value means *true*. An *n*-dimensional Boolean set  $B^n$  is composed by all distinct Boolean vectors with length *n*. For example,  $B^0 = \emptyset$ ,  $B^1 = \{0, 1\}$ ,  $B^2 = \{00, 01, 10, 11\}$ ,  $B^3 = \{000, 001, 010, 011, 100, 101, 1100, 111\}$  *et cetera*. This way, the set  $B^n$  has  $2^n$  elements.

A *Boolean function*  $f : B^n \mapsto B$  is a function that relates every element of its domain  $B^n$  into one element of its co-domain (or image) B, i.e. each Boolean vector of length n is associated by a Boolean function either to 0 or to 1.

Boolean variables are variables in the Boolean space, i.e. they can assume values of B. A Boolean function of the form  $f : B^n \mapsto B$  is a function of n variables, and each vector of  $B^n$  being an input vector defines the value of every Boolean variable. As each one of the  $2^n$  vectors corresponds to one of the two values 0 or 1, there are  $2^{2^n}$  different Boolean functions of n variables.

A very common representation of a Boolean function is a *truth table*. An example of truth table can be seen in Figure 2.1. Each variable is assigned to a position of the input vector, and the last column is the output value of the function for that input vector.

There are three basic Boolean operations, AND (\*), OR (+) and NOT (!), which can be applied to Boolean values of Boolean functions. The AND and OR operations are binary operations, since they have two operands. The AND function evaluates to (or returns) 1 when all of its operands are 1, and evaluates to 0 otherwise. The OR function returns 0 when all of its operands are 0, and returns 1 otherwise. The NOT function is a unary operation, it has only one operand. When the operand is 0 the NOT function, also called inversion operation, returns 1 and vice-versa.

A *Boolean expression* is a representation of a Boolean function, and it is characterized by a particular association of Boolean variables and Boolean operations. Although an expression represents exactly one function, a function can be represented by an infinite number of different expressions. As an example, equations 2.1 and 2.2 are two possible

| a | b | с | f |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

Figure 2.1: A truth table representation of a function.

representations of the function f depicted in figure 2.1.

$$f = (!c + (a * b)) \tag{2.1}$$

$$f = (!a*!b*!c) + (!a*b*!c) + (a*!b*!c) + (a*b)$$

(2.2)

Boolean operations can also be represented graphically as nodes in a graph. This way, Boolean expressions can be viewed as graphs, potentially sharing signals between them. This graphical representation of a set of Boolean functions is called a *Boolean network*. An example of a Boolean network is shown in figure 2.2.

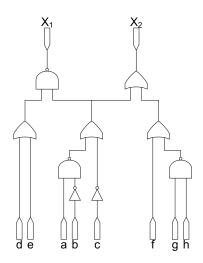

Figure 2.2: A Boolean network.

## 2.2 Equivalence Classes of Logic Functions

Consider the three following operations over the function f:

- **op1:** Negation of some variables in f.

- **op2:** Permutation of some variables in f.

- **op3:** Negation of f.

If a function g can be derived from f by a combination of these three operations, then the function g is NPN-equivalent to f. The set of functions that are NPN-equivalent to the function f forms an NPN-equivalence class  $[f]_{NPN}$ , of which f is a representative function. Similarly, the functions that are obtained by applying operations **op1** and **op2** in f are NP-equivalent to f, and form an NP-equivalence class  $[f]_{NP}$ . If only operation **op2** is considered, then a P-equivalence class  $[f]_P$  is defined.

For example, let us define the functions  $f_1 = a+b$ ,  $f_2 = !a+b$ ,  $f_3 = !(a+!b)$ ,  $f_4 = a+!b$ . Functions  $f_2$  and  $f_4$  belong to the same P-equivalence class. Functions  $f_1$ ,  $f_2$  and  $f_4$  are of the same NP-equivalence class. Finally, all of these functions belong to the same NPN-equivalence class.

|                       | 0 | 1 | 2  | 3   | 4     |

|-----------------------|---|---|----|-----|-------|

| All functions         | 2 | 4 | 16 | 256 | 65536 |

| P-equivalence class   | 2 | 4 | 12 | 80  | 3984  |

| NP-equivalence class  | 2 | 3 | 6  | 22  | 402   |

| NPN-equivalence class | 1 | 2 | 4  | 14  | 222   |

Table 2.1: Number of equivalence classes under various equivalence relations (SASAO, 1999).

Table 2.1 shows the number of different equivalence classes up to n = 4. When n is sufficiently large, the number of equivalence classes can be approximated as follows:

The number of P-equivalence classes is

$$\frac{2^{2^n}}{n!}$$

. (2.3)

The number of NP-equivalence classes is

$$\frac{2^{2^n}}{2^n \times n!}$$

. (2.4)

The number of NPN-equivalence classes is

$$\frac{2^{2^n}}{2^{n+1} \times n!}$$

. (2.5)

To categorize functions into equivalence classes is useful in the matching phase of a technology mapping. The task of the matching phase is to find sub-functions that are equivalent to one of those in the target library. As the objective is to cover the subject graph with black boxes connecting each other, the permutation operation is free. Hence the P-equivalence class is useful for any technology mapping. Moreover if the logic style used is dual rail, when all functions are generated both direct and complemented, then the negation operation is also free, so the NPN-equivalence class is the most useful.

#### **2.3 Data Structures**

A logic circuit or Boolean network may be represented by a variety of data structures. Each of them is more or less appropriate to a specific manipulation, having its particular strengths and weaknesses. An appropriate data structure is a key element to an efficient computation.

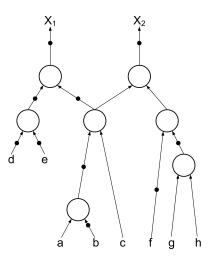

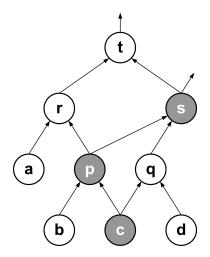

#### 2.3.1 Directed Acyclic Graph

Graphs of operators are widely used data structures to represent the combinational part of circuits. A *Directed Acyclic Graph* (DAG)  $\mathcal{G} = (V(\mathcal{G}), E(\mathcal{G}))$  is a directed graph and has no directed cycles. A node in the graph  $v \in V(\mathcal{G})$  represents a logic function, such as AND or OR, a *primary input* (PI) or a *primary output* (PO). The set of directed edges  $e \in E(\mathcal{G})$  arriving in the node v, iedge(v), represent the inputs of v. The set of edges leaving from v, oedge(v), represent the outputs of v. The *fanout* of v is defined as |oedge(v)|. If  $\forall v \in V(\mathcal{G})$ ,  $|iedge(v)| \leq K$ , then the DAG is *K-bounded*. An example of DAG can be seen in figure 2.3, it represents the same Boolean network of figure 2.2.

Figure 2.3: A directed acyclic graph example.

A DAG is a direct translation of a Boolean network into a data structure. It represents the circuit in an integrated way, but algorithms that perform technology mapping directly over DAGs tend to suffer of scalability problems.

#### 2.3.2 Forest of Trees

A tree is a particular case of DAG, in which  $\forall v \in V(\mathcal{G})$ , |oedge(v)| = 1. In other words, the fanout of every node is equal to one. In order to be able to represent any circuit as a forest of trees, every logic function that has a fanout larger than one will originate a new tree. This partitioning of the graph reduces the complexity of the subsequent technology mapping, at the cost of reducing the space of solutions, thus producing a mapping of inferior quality. A forest of trees representing the same Boolean function as before is depicted in figure 2.4.

Breaking a DAG into a forest of trees can greatly reduce the computational cost of the technology mapping process. Algorithms that achieve optimum results both in area and timing in polynomial time exist, but the optimality is only guaranteed for each tree individually. Hence, the use of trees on technology mapping can severely restrict the quality of the results.

#### 2.3.3 And-Inverter Graph

An And-Inverter Graph (AIG),  $\mathcal{G}$ , is a specific type of DAG. Each node  $v \in V(\mathcal{G})$  has either 0 or 2 incoming edges, hence it is 2-bounded. Nodes that have no incoming edges are primary inputs, and nodes having 2 inputs are AND nodes. Each edge can be complemented or not, denoting the inversion operation. Some nodes are marked as

Figure 2.4: A forest of trees.

primary outputs (PO). An AIG of the same Boolean network of figure 2.2 is shown in figure 2.5.

Figure 2.5: An and-inverter graph.

An AIG is a restricted DAG, though the problems of using it in technology mapping are reduced by the regularity and simplicity of its structure.

#### 2.3.4 Binary Decision Diagram

Graphs of operators are structural representations of circuits, as they have as starting point the description of a circuit as interconnected logic operations. Another way of representing the logical behavior of a circuit is to represent directly the logic functions of each output of the circuit. A logic function is characterized by its truth table, which relates every possible input vector into an output value. Storing directly the truth table of a function is not efficient because, for a logic function having n input variables, the table has  $2^n$  values. A more compact representation is the BDD.

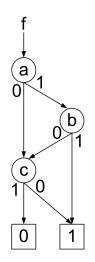

Binary Decision Diagrams (BDDs) are graph representations of Boolean functions (BRYANT, 1986). A BDD is a DAG with two terminal nodes, called 0-terminal and 1-terminal. Each non-terminal node has an index to identify an input variable of the Boolean function and has two outgoing edges, the 0-edge and the 1-edge. A BDD is represented in Figure 2.6. It represents the same function f from the truth table in Figure 2.1.

Figure 2.6: An example of a BDD.

#### 2.4 Dag Nodes and Tree Nodes

A *dag node* is defined as a node with fanout larger than one. The nodes that are not dag ones are *tree nodes*. The set of all dag nodes in a graph  $\mathcal{G}$  is represented by  $\mathcal{F}$ , and the set of tree nodes by  $\mathcal{T}$ .

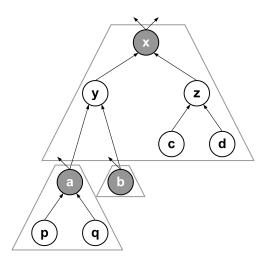

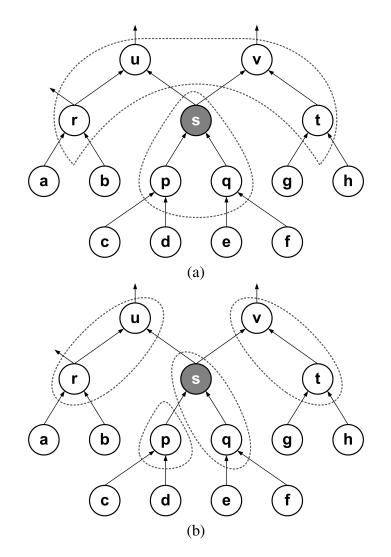

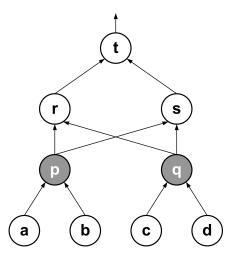

A sub-graph of  $\mathcal{G}$ ,  $\mathcal{G}_{\mathcal{T}}$ , induced by the nodes in  $\mathcal{T}$  is a forest of trees. The root node of a tree in  $\mathcal{G}_{\mathcal{T}}$  is either an input of a dag node or a PO. Consider a sub-graph  $\mathcal{T}_n$  induced by a dag node n and the trees in  $\mathcal{G}_{\mathcal{T}}$  that are inputs to it.  $\mathcal{T}_n$  is a *factor tree*. In addition, when the root node of a tree in  $\mathcal{G}_{\mathcal{T}}$  is a PO, the tree itself is also a factor tree. This way, each node n in  $\mathcal{G}$  is contained in a single factor tree. In Figure 2.7, the dag nodes are shaded, and its factor trees are delimited.

Figure 2.7: AIG illustrating dag and tree nodes (CHATTERJEE; MISHCHENKO; BRAYTON, 2006). Nodes p, q, b, c and d are primary inputs. Node x is a primary output.

A leaf of a factor tree that is not a PI has dag nodes as its inputs. A factor tree along with the dag nodes that are inputs of its leaves is called a factor leaf-DAG. In Figure 2.7, the factor leaf-DAG for the node x is its factor tree in conjunction with the nodes a and b.

### 2.5 K-Feasible Cuts

A K-feasible cut of a node n defines a subgraph, more specifically a logic cone, rooted in n, having no more than K inputs. In other words it defines a region in the graph that represents the logic function of n, using at most K variables. It is a useful tool in technology mapping, especially when targeting FPGAs, which are composed of LUTs that can implement any logic function up to a fixed number of inputs.

Formally, a *cut* of a node n is a set of nodes c such that every path between a PI and n contains a node in c. If a cut  $c_1$  is a subset of a cut  $c_2$ , then  $c_1$  dominates  $c_2$ . A cut is *irredundant* if it is not dominated by another cut. A *K-feasible cut* is an irredundant cut containing K or lesser nodes (PAN; LIN, 1998; CONG; WU; DING, 1999). The region defined by a *K*-feasible cut is composed by all nodes contained in a path between a node in c and the node n, including n and excluding the nodes of c.

The nature of the algorithm for enumeration of cuts is combinatorial. The combination of two cuts, where each cut is a set of nodes, is simply the union of these two sets. As each node has a set of cuts associated to it, it is of interest to define an operation that combines cuts as a Cartesian product between two sets of cuts. Notice that the simple combination of two *K*-feasible cuts does not guarantee that the resulting cut is *K*-feasible. Therefore the proposed combination operation should remove any cut that is not *K*-feasible.

Let A and B to be two sets of cuts. Let the auxiliary operation  $\bowtie$  to be:

$$A \bowtie B = \{a \cup b | a \in A, b \in B, |a \cup b| \le K\}$$

$$(2.6)$$

Let  $\Phi_{\mathcal{K}}(n)$  to be the set of *K*-feasible cuts of  $n \in \mathcal{G}$ , and if *n* is an AND node, let  $n_1$  and  $n_2$  to be its inputs. Then,  $\Phi_{\mathcal{K}}(n)$  is defined recursively as follows:

$$\Phi_{\mathcal{K}}(n) = \begin{cases} \{\{n\}\} &: n \text{ is a PI} \\ \{\{n\}\} \cup (\Phi_{\mathcal{K}}(n_1) \bowtie \Phi_{\mathcal{K}}(n_2)) &: \text{ otherwise} \end{cases}$$

(2.7)

The  $\bowtie$  operation can also easily remove the redundant cuts, by comparing the cuts with one another, and possibly by making use of signatures (explained in section 3.3).

Table 2.2 illustrates the computation of K-feasible cuts. The AIG being computed is the one of figure 2.7, and the value of K is kept unlimited for the sake of the example. Notice that each node has one cut composed only by itself (called the *trivial cut*) in addition to all combinations of its fanin nodes' cuts.

Table 2.2: An example of *K*-feasible cuts computation.

| Node | K-feasible cuts                                     |

|------|-----------------------------------------------------|

| p    | $\{p\}$                                             |

| q    | $\{q\}$                                             |

| a    | $\{a\}, \{p,q\}$                                    |

| b    | $\{b\}$                                             |

| y    | $\{y\}, \{a, b\}, \{b, p, q\}$                      |

| c    | $\{c\}$                                             |

| d    | $\{d\}$                                             |

| z    | $\{z\},\{c,d\}$                                     |

| x    | $\{x\}, \{y, z\}, \{c, d, y\}, \{a, b, z\},$        |

|      | $\{a, b, c, d\}, \{b, p, q, z\}, \{b, c, d, p, q\}$ |

## 2.6 Library

A *cell library* is a finite set of primitive logic gates, including combinational, sequential (e.g. flip-flops) and interface (e.g. drivers) elements. Here we focus on combinational cells, which are implementations of Boolean functions. This may seem too restrictive, but practical approaches of technology mapping usually deal only with the combinational portion of the circuit.

Traditionally, technology mapping algorithms rely on static pre-characterized libraries. Each cell of the library is fully characterized through exhaustive simulations, resulting in accurate information about the behavior of the cell concerning timing, power consumption and its physical area. This way, the technology mapping algorithms are restricted to use these cells in the mapping process. This approach is known as *library-based* mapping.

The quality of the final circuit is increased as the library becomes richer, i.e. a larger cell variety, both in number of functions implemented and in different flavors of each logic function (VUJKOVIC; SECHEN, 2002). However the number of different P-equivalence classes, or even NPN-equivalence classes, grows exponentially with the number of inputs. Further, the processes of electrical characterization and layout generation are extremely computing demanding, making the creation of an exhaustive library, even for a number of inputs not so large, unfeasible (SECHEN et al., 2003).

As an alternative to this duality — either to have a rich library but at a high development cost, or to have a restricted library at expense of the final quality — lies the concept of *library-free* technology mapping. The main idea is that the library is not fully designed and characterized prior to the mapping, but it is defined by means of rules, e.g. the maximum number of inputs, or the maximum number of series transistors. This reduces drastically the cost of maintaining such a large library. However, as the cells are not characterized, not even laid out, the technology mapping does not dispose of sufficient information to choose which cells to use. Thus estimation methods for each piece of information required by the mapping must be provided. These estimation methods must be fast, in order to be able to treat many cells in a short time, and accurate, in order to not mislead the mapping process. Also, once the mapper has chosen which cells must be used, they need to be properly generated, and as the variety of cells is potentially large, an automatic layout generator may be required.

## 2.7 Technology Mapping

*Technology mapping*, also known as technology binding, transforms a logic network independent from a technology into gates implemented in a technology library (HAS-SOUN; SASAO, 2002). It can be decomposed in three phases: *decomposition*, *pattern matching* and *covering*.

#### 2.7.1 Decomposition

The decomposition process transforms the initial representation of the circuit into a more simple and restricted one, in order to aid the technology mapping algorithm. For example, it applies the same structural transformations in the graph representations of cells, if structural matching is used, or it breaks the graph into trees, if the technology mapping was designed to map only these data structures. This new representation, called the *subject graph* depends strongly on the future mapping strategy.

One of the tasks of the decomposition phase is to assure that each node of the subject

graph does have at least one match against the library, considering the technology mapping to be used. If this can be achieved, then at least one successful covering is guaranteed to exist.

#### 2.7.2 Pattern Matching

Once the data structure is constructed, the pattern matcher finds a set of matches between nodes on the circuit and a predefined library. This means being able to determine whether a portion of the subject graph can be implemented by a cell in the library. Matching algorithms can be classified into two major groups: structural matching and Boolean matching (MICHELI, 1994).

*Structural matching* relies on the identification of common patterns. For this reason, both the subject graph and the library cells must be decomposed in the same way, so the matching process can be reduced to a graph isomorphism testing. The cells in the library may have more than one representation in the subject graph format, hence more than one representation must be maintained. Even though the problem of determining isomorphism between two graphs may be intractable, considering the size of the subgraphs used in technology mapping the computational time can be neglected.

*Boolean matching* relies on the identification of Boolean functions of the same equivalence class. This approach is less restrictive than structural matching, because a same function can be represented by many different graphs. It usually performs the matching using BDDs by trying different variable orderings, until a matching is found. Boolean matching is computationally more expensive than structural matching, but can lead to better results.

#### 2.7.3 Covering

The final step, the covering, chooses a subset of the matches such that the entire network is covered and optimizing some objective function. This function is often the total area, the largest delay, the power consumption, or a composition of these.

More formally, the result of a covering is a set of cells, which have input and output signals, such that:

- Every node of the subject graph is covered by at least one cell.

- Each signal that is input of a cell is an output of another cell.

- Every cell has at least one output used by another cell as an input.

The quality of the mapping will depend significantly on the quality of the subject graph composed in the first stage of the mapping. The best algorithm executed over a poor subject graph may produce a worse result than an average mapping over a good graph. This problem is known as *structural biasing*.

As the technology mapping is a step that transforms every cell in the network, it has a major impact on the final circuit characteristics.

# **3 STATE OF THE ART**

This section starts with a review of the evolution of technology mapping, both librarybased and library-free. After that, a collection of works that are related to the research presented in this thesis is summarized.

## 3.1 Technology Mapping

The first methods for automatic synthesis of digital circuits had no specific algorithms for technology mapping. The synthesis process was restricted to applying a set of rules over a structure that represents the circuit, seeking some kind of optimization. The main approaches of synthesis based on rules were presented in the 1980s, by Darringer (1981) and Gregory (1988). This kind of methodology performs local optimizations, trying to reduce the cost of a region of the circuit. However, not all local optimizations lead towards global optimizations, given a particular objective function. As alternatives to the rules based system, new algorithmic solutions have emerged in order to perform the technology mapping of circuits using heuristics or even exact algorithms.

The first technology mapping algorithm, called DAGON, was proposed by Keutzer (1987). He noted a similarity between technology mapping and the tasks of a compiler. The pattern matching between sub-graphs of a circuit representation and cells of a library is a similar problem as to identify patterns between intermediate representations of a computer program and a given set of machine instructions. The subject graph used is a binary tree represented in the form of a string, and this description was consistent with the input format of the compiling engine. The structural matching and the initial representation of the circuit restrict the search space to be explored by mapping, affecting the quality of the mapped circuit. Moreover, the algorithm requires all isomorphic matches to be stored in each node of the tree, until the end of covering step. This precluded the use of very large libraries, when the number of patterns found is usually higher. It also required greater storage capacity and more time to find a solution.

In the same year, Detjens (1987) proposed the first method that actually used trees as the subject graph. In addition to this innovation, Detjens proposed the insertion of pairs of inverters in the graph. This increases the possibility of identifying new patterns in the graph (graph isomorphism), increasing the solution space. However to take advantage of this increased search space, it is necessary to create several decompositions for each element of the library. Thus, the use of a large library becomes unfeasible.

Some years later, Mailhot (1993) presented the first technology mapping algorithm that used an approach of functional verification to identify patterns. Like previous algorithms (KEUTZER, 1987; DETJENS et al., 1987), the initial DAG is partitioned into a forest of trees. However, the comparison between the sub-trees and the cells of the library

is performed by using BDDs. Since BDDs are a canonical form of representing Boolean functions, finding matches did not depend anymore on the structure of these sub-trees. However, this Boolean approach was computationally expensive, leading to limitations similar to previous approaches.

The dynamic reorganization proposed by Lehman (1995) was another alternative to minimize the dependence on the initial graph representation. In this algorithm, the decomposition phase is integrated with the pattern matching. Graphs functionally equivalent but structurally different are associated with each node of the graph, increasing the search space in order to find better solutions. Consequently, by storing many decompositions per node, the graph grows rapidly, making it impractical for large circuits.

Kukimoto (1998) proposed a method in which the mapping is executed directly over a DAG representation, and ensures optimum result in terms of speed, regardless of the initial decomposition of the graph. However, it is necessary to emphasize that the delay model, for which the optimal solution is guaranteed, ignores the load of the cell, taking into account only its propagation delay. This means that it requires a post-processing step to ensure the proper sizing of the logic cells.

Stok (1999) proposed the algorithm called *wavefront*, which is similar to Lehman's approach, but solving the scalability problem. Like Kukimoto's method, the circuit is represented by a DAG and the delay model is independent of the cell's load. To prevent the DAG to increase exponentially with the insertion of different representations for each node, the stages of decomposition, pattern matching and covering are executed concurrently in a "sliding window", called wavefront, which is tunable in terms of logic depth. This heuristic algorithm has performed well compared to its predecessors.

The state-of-the-art in library-based technology mapping is presented by Chatterjee (2006). It brings together a series of techniques used in logic synthesis, integrated and well calibrated to the benefit of the technology mapping. The essence of the mapping algorithm is the same of Kukimoto's method. The main differences are in the pattern matching, which is a Boolean matching, and in the data structure, which is an AIG. This algorithm was incorporated into an academic tool, called ABC (Berkeley Logic Synthesis and Verification Group, 2010).

In parallel with the evolution of library-based algorithms, methods based on virtual libraries have also been proposed. The first one was presented by Berkelaar (1988), and like the first methods for technology mapping, it partitions the circuit into logic cones, but does not use trees to represent them. Expressions of sums-of-products and product-of-sums are represented as graphs, using a prefixed notation. Traversing these graphs from outputs to inputs, they are partitioned into logic cells. This happens every time that a certain portion of the graph reaches a limit imposed by a set of constraints that defined the virtual library. The biggest problem with this approach is that it is a greedy algorithm. As the cuts are made top-down, the logic depth of what is below is unknown. So, it is not possible to guarantee a solution with minimum logic depth or with minimum number of cells.

Abouzeid (1993) proposed a new approach to generating cells, motivated by the possibility of using a large number of logic cells. In this method, the initial DAG is also partitioned into trees, but these are n-ary trees, as each node can have n child nodes. The representation as an n-ary tree decreases the dependence on the initial graph, allowing change of structure in a given set of nodes. Based on this representation, cuts are made each time a node that exceeds any of the restrictions is found. Although the cuts are generated from inputs to outputs, they are made in a greedy way, not contemplating logic depth minimization.

Liem (1992) proposed a method based on a strategy called constructive matching. Unlike previous approaches that considered only maximum values for chains of transistors, this method considered the number of inputs and logic depth of a cell. These two additional restrictions are imposed to ease post-mapping stages, because the used cells are smaller. This also restricts the number of possible matchings, reducing the complexity of the problem. One problem is the algorithm dependence on the initial structure of the circuit, considering that the circuit is represented by binary trees. Another problem is the storage of the matchings up until the covering, which also precluded the method for mapping large circuits.

The method presented by Reis (1999) proposes a different approach in library-free. The representation of each logic cone is made by a special type of BDD, called Terminal-Suppressed Binary Decision Diagram (TSBDD). An interesting property of this structure is the direct association of the arcs of the BDD to transistors. However, this representation faces the same problems of representation by trees. The major contribution of this method was the use of dynamic reordering on the initial representation of the circuit.

Later on, Jiang (2001) proposed the Odd-level Transistor Replacement (OTR) method. This method works directly on a graph representing the electrical diagram at transistor level of a circuit, so it depends on an already mapped structure. The goal of the algorithm is to select which gates can be collapsed in order to achieve a better performance. Like most of the methods, it also depends strongly on the initial decomposition of the circuit.

A latter strategy for mapping based on virtual libraries, and using trees as a subject description, was presented by Correia (2004), originating the ELIS tool. This method uses n-ary trees to represent the cones of a logic circuit. The main advantage of this algorithm is that it considers several decompositions of sub-trees dynamically (at a low computational cost), leading to a minimum coverage using dynamic programming. The major limitation comes from the use of by trees, which prevent a broader view of the circuit.

Marques (2007) proposes the VIRMA algorithm. VIRMA performs the mapping over a DAG, aiming the reduction the circuit delay. The library uses a maximum number of series transistor, but considering the lower bound (SCHNEIDER et al., 2005) in a topologically non-complementary implementation of CMOS cells. It also uses a sliding window to reduce the complexity, and achieves a reasonable scalability comparing to its predecessors.

All methods discussed above have limitations imposed by how they address the problem of technology mapping. In general, the application of heuristics is necessary to ensure the tractability of the problem. As an example of heuristic, the mapping for minimum area in a DAG is NP-complete, but if the DAG is partitioned into trees and each tree mapped independently, optimum coverings for each tree can be found in linear time. Regarding a mapping for minimal delay, it can be achieved on a DAG mapping depending on the delay model. However, it should be noted that these models are not precise enough to ensure proper sizing of the circuit. Thus, a further step of sizing is necessary. There are methods that try to solve the problem of mapping and sizing simultaneously. The algorithm proposed by Karandikar (2004) is an example of it. It finds good results in polynomial time using more sophisticated delay models associated to some heuristics.

## **3.2 DAG-Aware AIG rewriting**

AIG rewriting is a greedy algorithm for minimizing the number of nodes of an AIG. It iteratively selects subgraphs and replaces them with pre-computed logically equivalent subgraphs.

The algorithm needs a hash table of pre-computed graphs, for all functions with up to a certain number of inputs inputs. The authors used functions with up to four inputs. So, first of all, a series of AIG subgraphs are computed for every one of the 222 different NPN-equivalence classes with up to four inputs.

Once the hash table is set up, the algorithm traverses the AIG in topological order, from inputs to outputs. For each node, all 4-feasible cuts are enumerated. Each 4-feasible cut is matched with the pre-computed graphs from the hash-table. Cuts that reduce the number of nodes without increasing the height of the region, or cuts that add shared nodes are sought. After trying all available subgraphs for a node, the one that leads to the greatest improvement replaces the original cut.

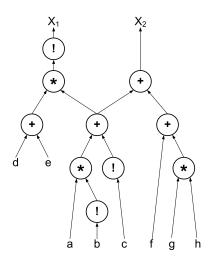

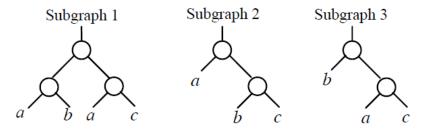

Figure 3.1: Different AIG structures for function f = a \* b \* c (MISHCHENKO; CHATTERJEE; BRAYTON, 2006).

Figure 3.2: Two cases of AIG rewriting of a node (MISHCHENKO; CHATTERJEE; BRAYTON, 2006).

An example follows. Figure 3.1 shows three AIG representations of the function f = a \* b \* c, which were pre-computed and stored in a hash-table. Figure 3.2 contains two examples of AIG rewriting. In the upper example subgraph 1 was detected and replaced by subgraph 2, causing a reduction of one node. The lower example shows, besides the marked cut, two more nodes that are already elsewhere on the graph. In this case, subgraph 2 is detected and replaced by subgraph 1, a seemingly useless subgraph since it

is redundant. However the sharing of nodes caused this replacement to reduce one node in the graph.

After the entire AIG is traversed, a second type of AIG rewriting takes place, called refactoring. This algorithm has a heuristic that chooses one large cut for each AIG node. Refactoring a cut is performed by extracting the Boolean function of the cut and running an equation factorization algorithm, which is converted back to an AIG representation, possibly replacing the original cut. The change is accepted if there is a reduction of the number of nodes.

A third step consists in balancing the AIG structure. The authors suggest a script that traverses the structure 10 times, as follows: *b*, *rw*, *rf*, *b*, *rw*, *rwz*, *b*, *rfz*, *rwz*, *b*. In the abbreviated form, *b* stands for balancing, *rw/rf* stand for AIG rewriting and refactoring, and *rfz/rwz* is the same, but with zero improvement replacements permitted.

The authors claim that this approach leads to a reduction of area in the order of 10% and 5% gains in delay, while the runtime is reduced by a factor ranging between 7 and  $\sim$ 1000, when comparing with certain scripts of MVSIS (MVSIS Group, 2010) and SIS (SENTOVICH et al., 1992).

## **3.3** Using Signatures on Cut Computation

The use of signatures on cut computation has been proposed by Mishchenko (2007). Its use speeds up the process, and does not affect the final result.

A signature, sign(c), of a cut c is an M-bit integer. It is suggested by the authors to use M as the number of bits that compose a word of the target processor. Every node  $n \in c$  has an ID. The signature is computed by bitwise OR operations, for each node contained on the cut, as seen on equation 3.1.

$$sign(c) = \underset{n \in c}{\operatorname{OR}} 2^{(\operatorname{ID}(n) \operatorname{mod} M)}$$

(3.1)

Testing cut properties is much faster with signatures than testing the actual cuts. Although the use of signatures cannot avoid completely the computation over the real cuts, they are able to reduce it drastically.

If cuts  $c_1$  and  $c_2$  are equal then  $sign(c_1) = sign(c_2)$ . Hence if the signatures are different, so are the cuts. If the signatures are equal, then the cuts must be tested for equality.

If a cut  $c_1$  dominates a cut  $c_2$  then all the 1s in  $sign(c_1)$  are contained in  $sign(c_2)$ . This way, if  $sign(c_1) \operatorname{AND} sign(c_2) \neq sign(c_1)$  then  $c_1$  does not dominate  $c_2$ . Otherwise, the cuts must be tested for dominance.

If  $c_1 \bowtie c_2$  is a *K*-feasible cut then  $|sign(c_1) \operatorname{OR} sign(c_2)| \le K$ . Here |s| denotes the number of 1s on the binary representation of *s*. So, if  $|sign(c_1) \operatorname{OR} sign(c_2)| > K$  then  $c_1 \bowtie c_2$  is not *K*-feasible, otherwise its *K*-feasibility must be tested.

An example follows. Let M = 8. Cut  $c_1$ , having the nodes with ids 32, 68 and 69 would have  $sign(c_1) = 00110001$ . A second cut  $c_2$  with nodes having ids 32, 68 and 70 would have  $sign(c_2) = 01010001$ . It can be inferred that neither  $c_1$  dominates  $c_2$  nor  $c_2$  dominates  $c_1$ , without having to actually compare the cuts. If  $c_3$  is a cut composed by nodes having ids 36, 64 and 69, then  $sign(c_3) = sign(c_1) = 00110001$ . However  $c_1 \neq c_3$ , which shows that the comparison of the cuts is sometimes necessary.

## **3.4** Factor Cuts

Factor cuts (CHATTERJEE; MISHCHENKO; BRAYTON, 2006) are a collection of *K*-feasible cuts, grouped in two categories, *local cuts* and *global cuts*. The definition of these groups can vary according to the factorization scheme. However, the idea is to construct these two sets of cuts in order to be able to expand them generating a (possibly complete) set of *K*-feasible cuts. Observe that in this context the term factorization has a distinct meaning from factorization of Boolean equations.

In short, factor cuts allow algorithms that were conceived to use *K*-feasible cuts to work without the need of enumerating all cuts of every node. Only factor cuts need to be computed, and further calculation can be executed on-the-fly as more cuts are needed.

The expansion process can be explained as follows. Let c to be a global cut of a node n, and let  $c_i$  to be a local cut of a node i belonging to c. If e is a cut defined as  $e = \bigcup_i c_i$ , and e is K-feasible, then e is a *1-step expansion* of n. The set of cuts obtained expanding the cut c is defined as 1-step(c).

$$1-\text{step}(c) = \{e | e \text{ is a } 1-\text{step expansion of } c\}$$

(3.2)

In Figure 2.7, expanding the node a in the global cut  $\{a, b, z\}$  by its local cut  $\{p, q\}$ , we get the cut  $\{p, q, b, z\}$ , which is therefore a 1-step expansion of  $\{a, b, z\}$ .

### 3.4.1 Complete Cut Factorization

When using *complete factorization*, the local cuts are the *tree cuts*, and the global cuts are the *reduced cuts*. The complete factorization has an interesting property: any K-feasible cut can be generated by 1-step expansion.

### 3.4.1.1 Tree Cuts

The tree cuts of n are cuts only involving nodes within its factor tree.

Let  $\Phi_{\mathcal{KT}}(n)$  be the set of tree cuts of a node *n*. Define the auxiliary function  $\Phi^{\dagger}_{\mathcal{KT}}(n)$  as follows:

$$\Phi_{\mathcal{KT}}^{\dagger}(n) = \begin{cases} \emptyset & : n \in \mathcal{F} \\ \Phi_{\mathcal{KT}}(n) & : \text{ otherwise} \end{cases}$$

(3.3)

Then,  $\Phi_{\mathcal{KT}}(n)$  is defined by:

$$\Phi_{\mathcal{KT}}(n) = \begin{cases} \{\{n\}\} &: n \text{ is a PI} \\ \{\{n\}\} \cup (\Phi_{\mathcal{KT}}^{\dagger}(n_1) \bowtie \Phi_{\mathcal{KT}}^{\dagger}(n_2)) &: \text{ otherwise} \end{cases}$$

(3.4)

So,  $\Phi_{\mathcal{KT}}(n)$  is the subset of  $\Phi_{\mathcal{K}}(n)$  that is composed only of nodes from the factor tree of n.

For example, in Figure 2.7,  $\Phi_{\mathcal{KT}}(x) = \{\{x\}, \{y, z\}, \{y, c, d\}\}.$

#### 3.4.1.2 Reduced Cuts

The set of reduced cuts of a node n,  $\Phi_{\mathcal{KR}}(n)$ , is defined as:

$$\Phi_{\mathcal{KR}}(n) = \begin{cases} \{\{n\}\} &: n \text{ is a PI} \\ \{\{n\}\} \cup ((\Phi_{\mathcal{KR}}(n_1) \bowtie \Phi_{\mathcal{KR}}(n_2)) \setminus \Phi_{\mathcal{KT}}(n)) &: \text{ otherwise} \end{cases}$$

(3.5)

The formula of  $\Phi_{\mathcal{KR}}(n)$  is very similar to  $\Phi_{\mathcal{K}}(n)$ , except that the tree cuts of n are recursively removed. Because of that  $\Phi_{\mathcal{KR}}(n)$  is much smaller than  $\Phi_{\mathcal{K}}(n)$ .

In Figure 2.7,  $\Phi_{\mathcal{KR}}(x) = \{\{x\}, \{a, b, z\}\}.$

#### 3.4.2 Partial Cut Factorization

The *partial factorization* scheme does not allow the generation of a complete set of *K*-feasible cuts by 1-step expansion as the complete factorization scheme does, although it is much faster and in practice produces good results. For partial factorization, the local cuts are the *leaf-dag cuts*, and the global cuts are the *dag cuts*.

#### 3.4.2.1 Leaf-dag Cuts

The leaf-dag cuts of a node n are cuts only involving nodes of its factor leaf-DAG.

Let  $\Phi_{\mathcal{KL}}(n)$  be the set of leaf-dag cuts of a node *n*. Define the auxiliary function  $\Phi^{\dagger}_{\mathcal{KL}}(n)$  as follows:

$$\Phi_{\mathcal{K}\mathcal{L}}^{\dagger}(n) = \begin{cases} \{\{n\}\} & : n \in \mathcal{F} \\ \Phi_{\mathcal{K}\mathcal{L}}(n) & : \text{ otherwise} \end{cases}$$

(3.6)

Then,  $\Phi_{\mathcal{KL}}(n)$  is defined by:

$$\Phi_{\mathcal{KL}}(n) = \begin{cases} \{\{n\}\} &: n \text{ is a PI} \\ \{\{n\}\} \cup (\Phi_{\mathcal{KL}}^{\dagger}(n_1) \bowtie \Phi_{\mathcal{KL}}^{\dagger}(n_2)) &: \text{ otherwise} \end{cases}$$

(3.7)

Leaf-dag cuts are conceptually similar to the tree cuts. The difference lies at the fact that leaf-dag cuts include also the dag nodes that are inputs to the factor tree of n.

For example, in Figure 2.7,  $\Phi_{\mathcal{KL}}(x) = \{\{x\}, \{y, z\}, \{a, b, z\}, \{y, c, d\}, \{a, b, c, d\}\}$ . Notice that  $\{a, b, z\}$  and  $\{a, b, c, d\}$  are not tree cuts of x.

#### 3.4.2.2 Dag Cuts

Let  $\Phi_{\mathcal{KD}}(n)$  define the set of dag cuts of the node *n*:

$$\Phi_{\mathcal{KD}}(n) = \begin{cases} \{\{n\}\} & : n \text{ is a PI} \\ (\Phi_{\mathcal{KD}}(n_1) \bowtie \Phi_{\mathcal{KD}}(n_2)) & : n \in \mathcal{T} \\ \{\{n\}\} \cup (\Phi_{\mathcal{KD}}(n_1) \bowtie \Phi_{\mathcal{KD}}(n_2)) & : \text{ otherwise} \end{cases}$$

(3.8)

This way,  $\Phi_{\mathcal{KD}}(n)$  will only contain dag nodes and primary inputs. The number of dag cuts is much smaller than reduced cuts, but still allows us to capture much of the reconvergence in the network.

In Figure 2.7,  $\Phi_{\mathcal{KD}}(x) = \{\{x\}, \{a, b, c, d\}, \{p, q, b, c, d\}\}.$

## 3.5 TEMPLATE Boolean Matching Method

The TEMPLATE system (TEchnology Mapping PLATform) (HINSBERGER; KOLLA, 1998) is a method for Boolean matching of functions, which tries to find whether functions belong to the same equivalence class.

The method is based on the definition of a canonical representative function R[f] for each equivalence class [f]. Thus, the matching of a function against a library can be performed as follows: first the canonical representative function is computed for each function in the library; then the representative for the target function is computed and a direct comparison takes place, if  $R[f_1] = R[f_2]$  then  $f_1$  is a match of  $f_2$ .

A function is defined by its truth table, which can be represented as a bit string. When looking at a bit string as an unsigned integer representation, there is an inherent ordering.

This way, the two functions can be compared and classified as larger, smaller or equal by comparing the integers formed by their bit string representations.

So the representative function R[f] of [f] can be defined as the largest function in [f], as said in equation 3.9.

$$R[f] = \max_{g \in [f]} g \tag{3.9}$$

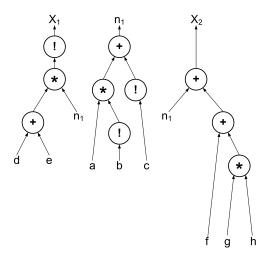

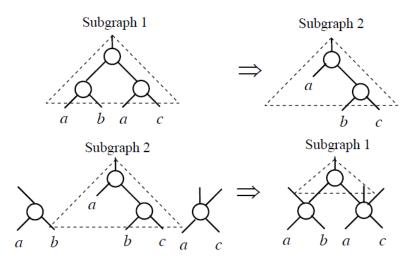

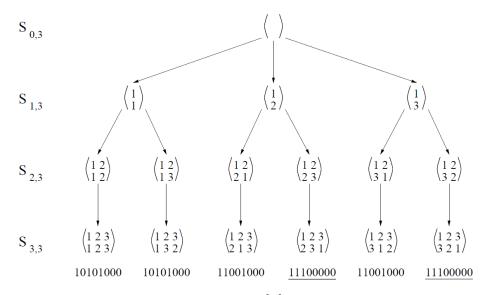

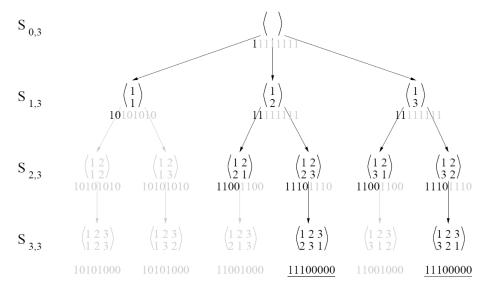

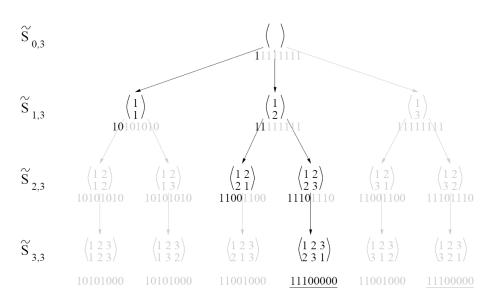

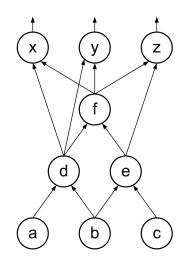

The most intuitive way of finding R[f] would be trying all operations allowed in the target equivalence class. For example, figure 3.3 shows functions of three variables obtained by all possible permutations of the inputs, hence considering a P-equivalence class, in the format of a tree. In the figure, the variables are represented by the numbers 1, 2 and 3. Each node contains a variable ordering assigned. In the  $S_{0,3}$  line there is no ordering assigned to any variable, in the line  $S_{1,3}$  the first variable is assigned, and so on.

Figure 3.3: Naive approach for computing  $R[f]_P$  (HINSBERGER; KOLLA, 1998).

One interesting property can be visualized with the help of figure 3.4. If the variable ordering is defined up to the k-th variable, no matter the ordering of the subsequent variables, the first  $2^k$  lines of the truth table are already defined. This is because every variable having an index larger than k has an equal value (zero) on these first  $2^k$  lines.

| $x_n \dots x_{k+1}$ | $ x_k \dots x_1 $ | $\int f(x_1 \dots x_n)$ |

|---------------------|-------------------|-------------------------|

|                     | 00                | $T_0$                   |

| 0                   | :                 | ÷                       |

|                     | 11                | $T_{2^{k}-1}$           |

| 01                  | 00                | $T_{2^k}$               |

| ÷                   | :                 | :                       |

| 11                  | 11                | $T_{2^{n}-1}$           |

Figure 3.4: A generic view of a truth table.

With this property in mind, at each node of the tree some of the first values of the function can be evaluated. As the most significant bits play a more important role on

determining relations of equality and ordering, some branches of the tree are already known not to produce the largest integer, hence some branches are not computed any further. Following the same example, figure 3.5 shows a reduction on the computation of  $R[f]_P$  when comparing to 3.3. This way the computation of the whole tree is avoided, by not reaching the not maximal leaves.

Figure 3.5: Reducing search space by cutting non-maximal branches (HINSBERGER; KOLLA, 1998).

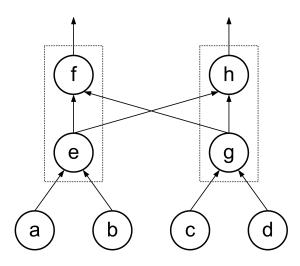

Although reduction is achieved by cutting branches, every branch producing a maximal integer is still reached, even though only one could provide the correct representative. To reduce even further the computational effort, information of variable symmetry can be used. Two variables a and b of a function f are symmetrical when they can be exchanged without changing the result of the function. More formally, if f(a, b) = f(b, a) then a and b are symmetrical. The set of variables that are symmetrical between them defines a symmetry class.

From the definition of variable symmetry, it is deductible that not every variable should be tested in every position, but only one variable of each symmetry class. This is because if the only difference between two branches is that the position of two symmetric variables is exchanged, then these two branches produce the same integers in their leaves. The same example now is shown in figure 3.6, but taking advantage of the fact that variables 2 and 3 are symmetrical.

The authors also define a generalization for the NPN-equivalence class case. Instead of considering only permutations, the tree is constructed by also considering inversions in the variables. This covers the NP-equivalence class. But as the tree is constructed twice, one for the direct function and another for the inverted function, the NPN-equivalence class case is covered.

The authors claim that this algorithm is able to manage about  $10^6$  functions per second, using an HP 735/125. The tests were executed over the 1989 MCNC benchmark circuits, and they did not provide the average size of the cuts, which is the average number of inputs of the functions treated.

Other authors (DEBNATH; SASAO, 2004) have improved this method to make it faster. The difference on this latter approach is that the entire set of possible negations and permutations is pre-computed and stored in a hash-table. According to the authors,

Figure 3.6: Reducing search space by using symmetry (HINSBERGER; KOLLA, 1998).

once this hash-table is computed, the matching phase presents a speed-up of two orders of magnitude, at expense of using much more memory. Hash-tables for functions with up to seven variables consume 140 megabytes of memory.

## **3.6 Area Flow Covering**