# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### ALÉCIO PEDRO DELAZARI BINOTTO

# A Dynamic Scheduling Runtime and Tuning System for Heterogeneous Multi and Many-Core Desktop Platforms

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Computer Science

Prof. Dr. Carlos Eduardo Pereira Supervisor

Prof. Dr. Dieter W. Fellner Cosupervisor

#### CIP - CATALOGING-IN-PUBLICATION

Binotto, Alécio Pedro Delazari

A Dynamic Scheduling Runtime and Tuning System for Heterogeneous Multi and Many-Core Desktop Platforms / Alécio Pedro Delazari Binotto. – Porto Alegre: PPGC da UFRGS, 2011.

129 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR-RS, 2011. Supervisor: Carlos Eduardo Pereira; Cosupervisor: Dieter W. Fellner.

1. High-performance computing. 2. Scheduling. 3. Dynamic load-balancing. 4. Heterogenous systems. 5. Graphics processors. 6. Solvers for systems of linear equations. I. Pereira, Carlos Eduardo. II. Fellner, Dieter W.. III. Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Pró-Reitor de Coordenação Acadêmica: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Aldo Bolten Lucion

Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PPGC: Prof. Álvaro Freitas Moreira

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

## **ACKNOWLEDGEMENTS**

The development of this binational doctoral thesis was composed of studies at the Federal University of Rio Grande do Sul, in Brazil, along 2 years and 2 months, and of studies at the Technische Universität Darmstadt and the Fraunhofer Institute for Visual Computing Research, in Germany, along 2 years and 10 months. It has been a significant research and personal challenge and it is one of the most important steps on my career. To reach this goal, a set of personal, technical, and financial support were needed, which without any of them I could not have developed this work.

I would like to begin with my parents, Mercedes and Jurandyr. They were the personal support to reach motivation and equilibrium on the most difficult moments. They have encouraged my studies from the very beginning. I express here my deepest respect, proud, and gratitude for their dedication and the many years of constant support, care, and friendship. This is for you. Without you, I would have never reached this way and the courage of exploring new frontiers. This gratitude is also extended to all of my family.

I am also grateful to Maria Clara for her encouragement on the beginning of this journey, specially on deciding to go to Germany, and also for the last year.

The other pillar is my main advisor: Prof. Carlos Eduardo Pereira. Carlos believed on my potential, accepting me as a PhD student. There is no bad time for Carlos and he became a friend spontaneously. He has the ability to discuss and to propose several ideas to constructively improve the work, inserting me on a variety of multidisciplinary research projects (I am sure this is a plus on my career). He was the one that believed and advocated for my applied (and not just academic) doctoral thesis. With Carlos, I have learned a lot, mainly to not concentrate just in one point/topic, but to open the eyes to complementary and innovative stuff, combining engineering and informatics. He was also decisive on acquiring the binational degree.

I had also the same feeling with Prof. Dieter Fellner. In our first meeting, he presented me several other ways to go and to question the work regarding the usability of the thesis' result. I will never forget when he challenged that the solutions have to serve for a long period of time and not just till the end of the PhD course. Additionally, I would like to thank Prof. André Stork and Gino Brunetti, whom accepted me on my stay in Germany. André offered me several possibilities of industry projets to experimentally validate the developed methods and put them in practice. This makes a difference at the end, André.

I wish to thank Dr. Arjan Kuijper, who I learned a lot the way of writing scientific texts and to emphasize the importance of the research. Acquiring skills of technical writing helped to clearly identify the contributions of this research for conference and journal committees, leading to constructive external evaluation and scientific publications. He also helped on finding shortcuts for the binational degree.

I also thank Daniel Weber, who I shared the office room during my stay in Germany.

He was important on choosing a case study for this work and to discuss mainly mathematical stuff I should learn. Without his support, I would have taken more time to understand concepts of linear algebra. At the same time, I thank my students Christian Daniel and Bernardo Pedras for the dedication on implementing some of the ideas I had in mind. Together, we have published interesting ideas. Besides, I would like to thank Profa. Judith Kelner, Prof. Cláudio Geyer, and Prof. Philippe Navaux for the considerations made at the thesis qualification. I also thank all my former colleagues at the Fraunhofer IGD-A2 group and Gabriele Knö $\beta$  for the administrative support.

The last pillar, but not less important, was the funding I received during this period. I thank CETA, where I worked on the beginning and enabled my first contact with Fraunhofer Institutes, and mainly DAAD - Deutsche Akademischer Austausch Dienst, the Programme  $Al\beta$ an and Fraunhofer IGD for the scholarships during my stay in Germany. In addition, I would like to thank Prof. Valter Roesler and Carlos for the scholarship on the way back to Brazil to conclude the thesis.

I want to say a big "thank you" to all of my friends! I should not forget to mention Angela Seip-Butz, who was a very important friend that I will definitely keep over the time. She was a lovely support for bad and good times and also to introduce typical things of Germany. If I know the real Germany, I know by her hints. In addition, I thank Roberto, Rafael, Jerome, Gilberto, Ulysses, Jorge, Gonçalo, Valéria, Régis, and Frithjof for important moments.

Finally, my gratitude to God for keeping me every time healthy during this journey.

# **CONTENTS**

| ACRO                                                                                   | DNYMS                                                                                                                                                                                             | 9                                                  |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| LIST                                                                                   | OF FIGURES                                                                                                                                                                                        | 11                                                 |

| LIST                                                                                   | OF TABLES                                                                                                                                                                                         | 13                                                 |

| LIST                                                                                   | OF ALGORITHMS                                                                                                                                                                                     | 15                                                 |

| ABST                                                                                   | TRACT                                                                                                                                                                                             | 17                                                 |

| RESU                                                                                   | JMO                                                                                                                                                                                               | 19                                                 |

| 1 IN<br>1.1<br>1.2<br>1.3                                                              | Contributions                                                                                                                                                                                     | 21<br>25<br>25<br>27                               |

| 2 TI<br>2.1.1<br>2.1.2<br>2.2<br>2.2.1<br>2.2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.5 | Multi-core CPUs Hardware characteristics Software functionalities  Many-core GPUs Hardware characteristics Software functionalities Processors' Trends Managing Heterogeneous Execution Platforms | 29<br>30<br>31<br>33<br>35<br>38<br>39<br>41<br>43 |

| 3 S <sup>3</sup> 3.1 3.2 3.3 3.4 3.5 3.6 3.6.1                                         | Distributed Processing on Multi-core Platforms                                                                                                                                                    | 45<br>46<br>47<br>48<br>49<br>50<br>50             |

| 3.6.2                                                                                  | Closing remarks                                                                                                                                                                                   | 51                                                 |

| 4 1        | THE SM@F        | RTCONFIG SYSTEM                                                                                                                            | 53  |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1        | <b>Platform</b> | Independent Programming Model                                                                                                              | 54  |

| 4.2        | Profiler a      | nd Database (DB)                                                                                                                           | 56  |

| 4.3        | Dynamic         | Scheduler                                                                                                                                  | 57  |

| 4.3.1      | First As        | signment Phase - FAP                                                                                                                       | 58  |

| 4.3.2      | Runtime         | e Assignment Phase - RAP                                                                                                                   | 61  |

| 4.4        | Chapter I       | Remarks: gaining performance with a load-balancing approach                                                                                | 63  |

| 5 <i>A</i> | APPLICATI       | ON: ITERATIVE SOLVERS FOR SLES APPLIED TO A                                                                                                |     |

| F          | REAL-TIME       | 3D CFD SIMULATION                                                                                                                          | 65  |

| 5.1        | Introduct       | ion to Iterative Solvers for SLEs                                                                                                          | 66  |

| 5.1.1      | The Sys         | stem of Linear Equations                                                                                                                   | 66  |

| 5.1.2      |                 | e methods for solving sparse SLEs                                                                                                          | 68  |

| 5.2        |                 | Vork on Solvers for SLEs using the CPU and the GPU                                                                                         | 70  |

| 5.3        | Implemen        | nting Iterative Solvers on the GPU platform                                                                                                | 71  |

| 5.3.1      | Four Co         | oncerns to be Met Towards an Efficient GPU Implementation                                                                                  | 72  |

| 5.3.2      | The Mat         | trix-vector Multiplication on the GPU                                                                                                      | 73  |

| 5.4        |                 | Remarks: gaining performance with a GPU approach                                                                                           | 76  |

| 6 E        | XPERIME         | NTAL VALIDATION & PERFORMANCE ANALYSIS                                                                                                     | 77  |

| 6.1        |                 | nce of the Iterative Solvers over the CPU-GPU Platform                                                                                     | 78  |

| 6.2        |                 | nce Analysis of the Sm@rtConfig Runtime System                                                                                             | 83  |

| 6.3        |                 | Remarks: gaining performance with the proposed system                                                                                      | 87  |

|            | •               |                                                                                                                                            |     |

|            |                 | ION                                                                                                                                        | 89  |

| 7.1        |                 | esearch                                                                                                                                    | 91  |

| 7.2        | Closing R       | demarks                                                                                                                                    | 92  |

| REF        | ERENCES         |                                                                                                                                            | 93  |

| APP        | ENDIX A         | USING THE SYSTEM IN CODE EXAMPLES                                                                                                          | 103 |

| <b>A.1</b> | CUDA Im         | plementation of the Main Modules Used by the Solvers                                                                                       | 103 |

| <b>A.2</b> | Example         | of Using the Sm@rtConfig System                                                                                                            | 110 |

| APP        | ENDIX B         | HANDLING DYNAMIC SCHEDULING OVER A CPU-GPU PLATFORM USING AN ASPECT-ORIENTED APPROACH                                                      | 113 |

| APP        | ENDIX C         | UM SISTEMA DE ESCALONAMENTO DI-<br>NÂMICO E TUNING EM TEMPO DE EXECUÇÃO PARA<br>PLATAFORMAS DESKTOP HETEROGÊNEAS DE MÚLTI-<br>PLOS NÚCLEOS | 110 |

| <b>C.1</b> | Ohietivos       |                                                                                                                                            |     |

| C.2        |                 | ições                                                                                                                                      |     |

| APP        | ENDIX D         | PUBLICATIONS AND ACADEMIC ACTIVITIES                                                                                                       | 123 |

| ΔΡΡ        | ENDIX F         | SUPERVISING ACTIVITIES                                                                                                                     | 125 |

|            |                 | Thesis                                                                                                                                     |     |

|            |                 | Work                                                                                                                                       |     |

|            |                 | AUTHOR'S CURRICULUM VITAE                                                                                                                  |     |

|            |                 |                                                                                                                                            |     |

# **ACRONYMS**

| ARBB Array Building Block |

|---------------------------|

|---------------------------|

API Application Program Interface

ASIC Application Specific Integrated Circuit

CFD Computational Fluid Dynamics

CG Conjugate Gradient

CPU Central Processing Unit

Ct C for Throughput Computing

CTM Close To Metal

CUDA Compute Unified Device Architecture

FAP First Assignment Phase

FIFO First In First Out

FPGA Field-Programmable Gate Array

GPGPU General Purpose Computation Using Graphics Hardware

**GPU** Graphics Processing Unit

HT Hyper Threading

MIMD Multiple Instruction Multiple Data

NFR Non-Functional Requirements

OpenCL Open Computing Language

PC Personal Computer

PCI Peripheral Component Interconnect

PTX Parallel Thread Execution

PU Processing Unit

RAP Runtime Assignment Phase

SDK Software Development Kit

SIMD Single Instruction Multiple Data

SLE System of Linear Equations

TBB Threading Building Blocks

UA Unit of Allocation

UML Unified Modeling Language

# **LIST OF FIGURES**

| tion with real-time geometry modification                                                                                                                                                                                                                                                           | e<br>-<br>-<br>. 24 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| correlation to application's needs                                                                                                                                                                                                                                                                  |                     |

| Figure 2.2: 6-core CPU from the Intel company (SCHROUT, 2010) Figure 2.3: The GPU as a co-processor of the CPU                                                                                                                                                                                      |                     |

| Figure 2.3: The GPU as a co-processor of the CPU                                                                                                                                                                                                                                                    |                     |

| Figure 2.4: CPU (from Intel) versus GPU (from Nvidia and AMD) performance                                                                                                                                                                                                                           |                     |

| growth                                                                                                                                                                                                                                                                                              |                     |

| Figure 2.5: Data transfer bandwidth comparison between CPU and GPU and their memory accesses - partially based on (GÖDDEKE, 2010)                                                                                                                                                                   | r                   |

| Figure 2.6: CUDA's grid, block, and thread organization - extracted from (NVIDI                                                                                                                                                                                                                     |                     |

| 2010a)                                                                                                                                                                                                                                                                                              | . 37                |

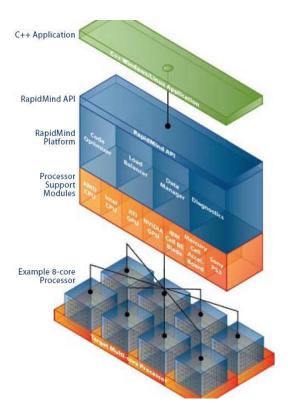

| Figure 2.7: RapidMind platform overview - extracted from the web site rapid-mind.net, which is no longer available                                                                                                                                                                                  | -                   |

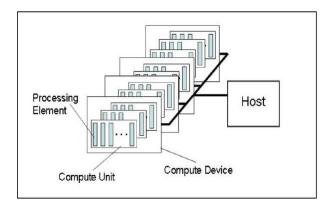

| Figure 2.8: OpenCL execution platform organization - extracted from (STONE GOHARA; SHI, 2010)                                                                                                                                                                                                       | ;                   |

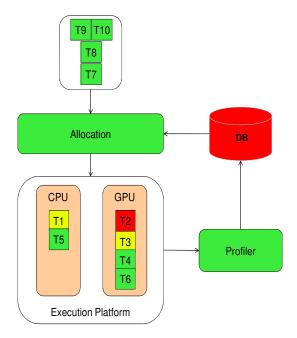

| Figure 4.1: Overview of the proposed system                                                                                                                                                                                                                                                         | . 54                |

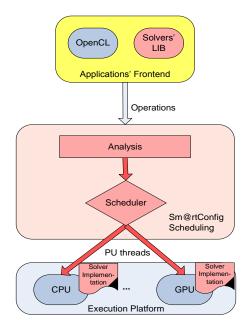

| Figure 4.2: The frontend interface design                                                                                                                                                                                                                                                           |                     |

| Figure 4.3: Performance history database: ID represents the task (number of unknowns for the SLE case study), type represents double or float, and time_Host and time_PU stores the last task execution time using the                                                                              | -<br>1              |

| CPU and the PU clock time                                                                                                                                                                                                                                                                           |                     |

| Figure 4.4: Dynamic arrival of new tasks at system execution time (green: tasks to be executed; yellow: tasks in execution; red: executed tasks)                                                                                                                                                    | S                   |

| Figure 5.1: The CFD workflow                                                                                                                                                                                                                                                                        | . 65                |

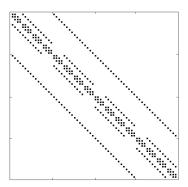

| Figure 5.2: Sparsity pattern of a finite difference discretization in three dimension                                                                                                                                                                                                               |                     |

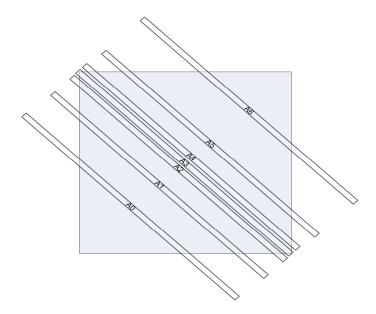

| Figure 5.3: Representation by seven linear vectors (A0-A6) of the resulting ma-                                                                                                                                                                                                                     |                     |

| trix from a regular grid                                                                                                                                                                                                                                                                            |                     |

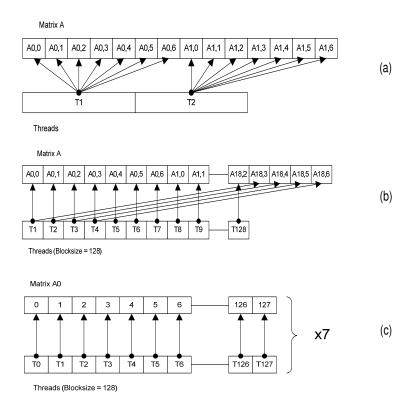

| Figure 5.4: Enabling memory coalescing access: (a) simple loading, where different threads access different addresses; (b)improved loading, where coalesced access is partially achieved; (c) final loading strategy, where the starting address for each block will be aligned to a multiple of 12 | e<br>e              |

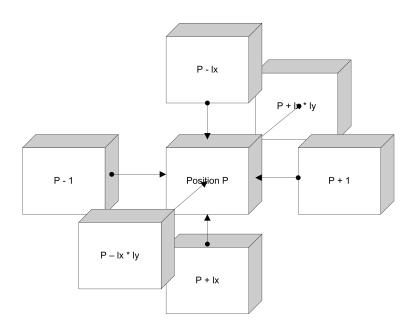

| Figure 5.5: | Stencil representation: relative positions of the Control Volumes                                                                                                                                                                                                                                                                                                                                                          | 75 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

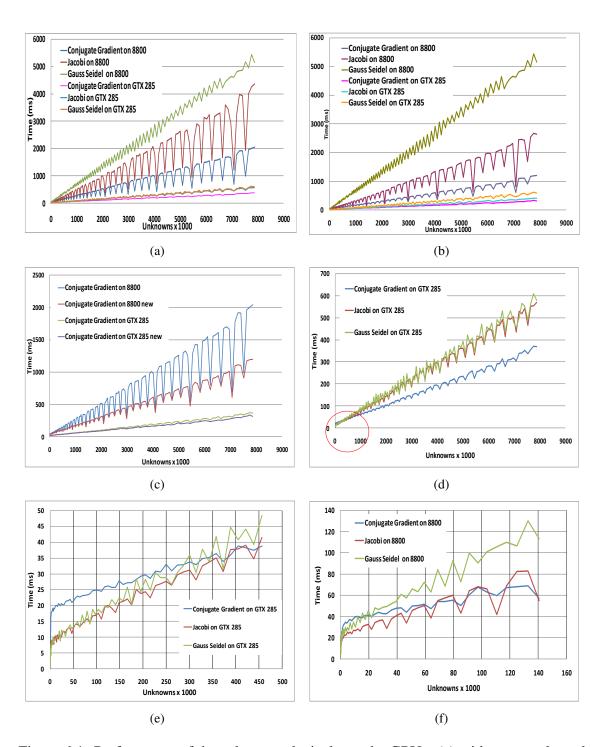

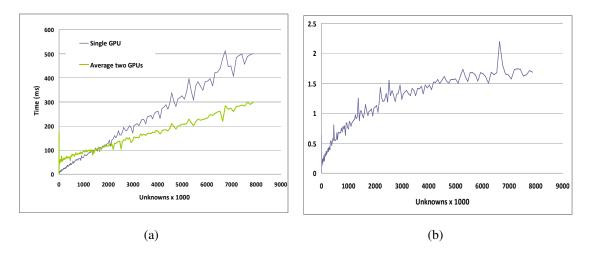

| Figure 6.1: | Performance of the solvers exclusively on the GPUs: (a) without a coalesced access strategy; (b) with the <i>new approach</i> ; (c) the Conjugate Gradient solver with and without the proposed approach; (d) on the GTX285 with the proposed approach; (e) break-even point on the GTX285 with the proposed approach (zoom of the red circle area of (d)); (f) break-even point on the 8800GT with the proposed approach. | 79 |

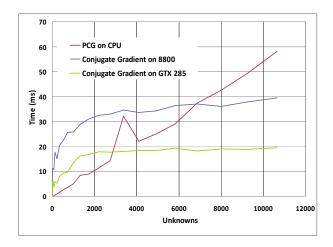

| Figure 6.2: | Performance break-even point on CPU and GPU                                                                                                                                                                                                                                                                                                                                                                                | 80 |

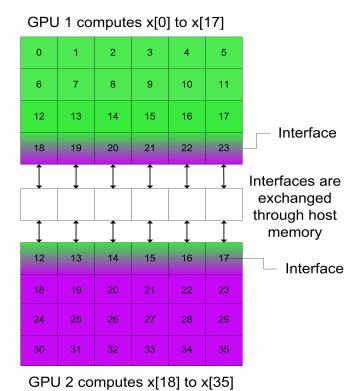

| Figure 6.3: | Using 2 GPUs for computing the stencil: data is divided in two sets with a redundant interface.                                                                                                                                                                                                                                                                                                                            | 81 |

| Figure 6.4: | Performance of the solvers using 2 GTX285 GPUs: (a) comparison                                                                                                                                                                                                                                                                                                                                                             | 01 |

| 118010 01   | with one GPU; (b) speedup using two GPUs                                                                                                                                                                                                                                                                                                                                                                                   | 82 |

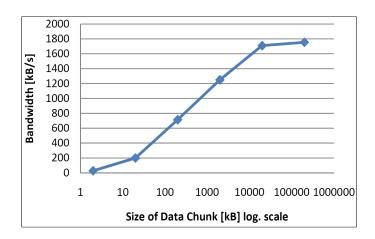

| Figure 6.5: | Real consumed bandwidth for the solvers                                                                                                                                                                                                                                                                                                                                                                                    | 83 |

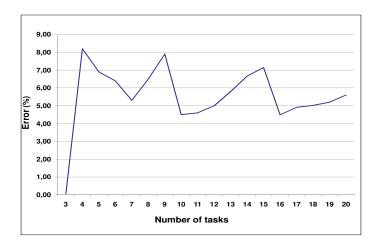

| Figure 6.6: | FAP heuristic accuracy                                                                                                                                                                                                                                                                                                                                                                                                     | 85 |

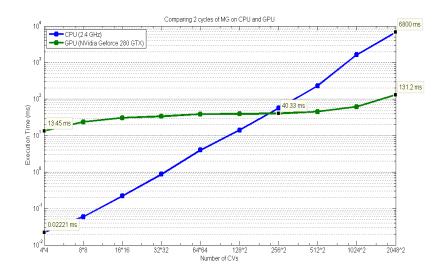

| Figure 6.7: | Performance comparison of the Multigrid (MG) solver over the CPU                                                                                                                                                                                                                                                                                                                                                           |    |

| _           | and the GPU (KELLER, 2009)                                                                                                                                                                                                                                                                                                                                                                                                 | 88 |

# **LIST OF TABLES**

| Table 6.1: | Domain sizes and execution costs of the tasks on the CPU and GPU       | 84 |

|------------|------------------------------------------------------------------------|----|

| Table 6.2: | Comparison of the FAP allocation heuristics: 0- assigned to the GPU,   |    |

|            | 1- assigned to the CPU                                                 | 84 |

| Table 6.3: | Overhead of the dynamic scheduling using Algorithm 2 and its gain      |    |

|            | in comparison to scheduling all tasks to the GPU                       | 85 |

| Table 6.4: | Comparison of the scheduling techniques for 24 tasks: overhead is      |    |

|            | the time to perform the scheduling; solve time is the execution time   |    |

|            | to compute the tasks; total time is the overhead plus solve time; and  |    |

|            | the error represents how worst is the total time of the techniques in  |    |

|            | comparison to the fastest solve time, which is the optimal solution    |    |

|            | without its overhead                                                   | 86 |

| Table 6.5: | Comparison of all techniques for 24 tasks in the FAP plus 42 tasks ar- |    |

|            | riving in the RAP: Algorithm 4 produced the best execution times for   |    |

|            | one CPU and one GPU, while Algorithm 2 did not perform well with       |    |

|            | reconfiguration. Algorithm 5 represents the generalization for several |    |

|            | PUs and achieved a better performance in comparison to scheduling      |    |

|            | all tasks to the GPU                                                   | 87 |

# LIST OF ALGORITHMS

| 1 | First Assignment Heuristic                                              | 58 |

|---|-------------------------------------------------------------------------|----|

| 2 | First Assignment with Swap Heuristic                                    | 59 |

| 3 | First Assignment Considering Performance Differences Heuristic          | 60 |

| 4 | First Assignment Considering Performance Differences and Swap Heuristic | 60 |

| 5 | Earliest First Termination - EFT                                        | 62 |

## **ABSTRACT**

A modern personal computer can be now considered as a one-node heterogeneous cluster that simultaneously processes several applications' tasks. It can be composed by asymmetric Processing Units (PUs), like the multi-core Central Processing Unit (CPU), the many-core Graphics Processing Units (GPUs) - which have become one of the main co-processors that contributed towards high performance computing - and other PUs. This way, a powerful heterogeneous execution platform is built on a desktop for data intensive calculations. In the perspective of this thesis, to improve the performance of applications and explore such heterogeneity, a workload distribution over the PUs plays a key role in such systems. This issue presents challenges since the execution cost of a task at a PU is non-deterministic and can be affected by a number of parameters not known a priori, like the *problem size domain* and the *precision* of the solution, among others.

Within this scope, this doctoral research introduces a *context-aware runtime and per-formance tuning system* based on a compromise between reducing the execution time of the applications - due to appropriate dynamic scheduling of high-level tasks - and the cost of computing such scheduling applied on a platform composed of CPU and GPUs. This approach combines a model for a *first scheduling* based on an off-line task performance profile benchmark with a *runtime model* that keeps track of the tasks' real execution time and efficiently schedules new instances of the high-level tasks dynamically over the CPU/GPU execution platform. For that, it is proposed a set of heuristics to schedule tasks over one CPU and one GPU and a generic and efficient scheduling strategy that considers several processing units.

The proposed approach is applied in a case study using a CPU-GPU execution platform for computing iterative solvers for Systems of Linear Equations using a stencil code specially designed to explore the characteristics of modern GPUs. The solution uses the number of unknowns as the main parameter for assignment decision. By scheduling tasks to the CPU and to the GPU, it is achieved a performance gain of 21.77% in comparison to the static assignment of all tasks to the GPU (which is done by current programming models, such as OpenCL and CUDA for Nvidia) with a scheduling error of only 0.25% compared to exhaustive search.

**Keywords:** High-performance computing, Scheduling, Dynamic load-balancing, Heterogenous systems, Graphics processors, Solvers for systems of linear equations.

# Um Sistema de Escalonamento Dinâmico e Tuning em Tempo de Execução para Plataformas Desktop Heterogêneas de Múltiplos Núcleos

## **RESUMO**

Atualmente, o computador pessoal (PC) moderno poder ser considerado como um *cluster* heterogênedo de um nodo, o qual processa simultâneamente inúmeras tarefas provenientes das aplicações. O PC pode ser composto por Unidades de Processamento (PUs) assimétricas, como a Unidade Central de Processamento (CPU), composta de múltiplos núcleos, a Unidade de Processamento Gráfico (GPU), composta por inúmeros núcleos e que tem sido um dos principais co-processadores que contribuiram para a computação de alto desempenho em PCs, entre outras. Neste sentido, uma plataforma de execução heterogênea é formada em um PC para efetuar cálculos intensivos em um grande número de dados. Na perspectiva desta tese, a distribuição da carga de trabalho de uma aplicação nas PUs é um fator importante para melhorar o desempenho das aplicações e explorar tal heterogeneidade. Esta questão apresenta desafios uma vez que o custo de execução de uma tarefa de alto nível em uma PU é não-determinístico e pode ser afetado por uma série de parâmetros não conhecidos a priori, como o *tamanho do domínio do problema* e a *precisão* da solução, entre outros.

Nesse escopo, esta pesquisa de doutorado apresenta um sistema sensível ao contexto e de adaptação em tempo de execução com base em um compromisso entre a redução do tempo de execução das aplicações - devido a um escalonamento dinâmico adequado de tarefas de alto nível - e o custo de computação do próprio escalonamento aplicados em uma plataforma composta de CPU e GPU. Esta abordagem combina um modelo para um primeiro escalonamento baseado em perfis de desempenho adquiridos em préprocessamento com um modelo online, o qual mantém o controle do tempo de execução real de novas tarefas e escalona dinâmicamente e de modo eficaz novas instâncias das tarefas de alto nível em uma plataforma de execução composta de CPU e de GPU. Para isso, é proposto um conjunto de heurísticas para escalonar tarefas em uma CPU e uma GPU e uma estratégia genérica e eficiente de escalonamento que considera várias unidades de processamento.

A abordagem proposta é aplicada em um estudo de caso utilizando uma plataforma de execução composta por CPU e GPU para computação de métodos iterativos focados na solução de Sistemas de Equações Lineares que se utilizam de um cálculo de *stencil* especialmente concebido para explorar as características das GPUs modernas. A solução utiliza o número de incógnitas como o principal parâmetro para a decisão de escalonamento. Ao escalonar tarefas para a CPU e para a GPU, um ganho de 21,77% em desempenho é obtido em comparação com o escalonamento estático de todas as tarefas para a GPU (o qual é utilizado por modelos de programação atuais, como OpenCL e CUDA para Nvidia) com um erro de escalonamento de apenas 0,25% em relação à combinação exaustiva.

**Palavras-chave:** Computação de alto desempenho, Escalonamento, Balanceamento de carga dinâmico, Sistemas heterogêneos, Processadores gráficos, Métodos para solução de sistemas de equações lineares.

### 1 INTRODUCTION

Modern industrial applications of *virtual engineering* commonly require high performance platforms to deal with distinct algorithms and massive calculations. Many of these applications - composed of scientific and engineering algorithms - require a powerful execution platform to perform simulation tasks with a minimum quality of performance. Hence, high performance platforms are a requisite for dealing appropriately with timing constraints towards the achievement of a *real-time* simulation for virtual engineering.

These requirements strongly indicate that a parallel architecture is a necessary approach to accelerate the computational time of such applications. Moreover, in order to obtain an additional performance gain, such systems could be parallel-based designed to benefit also from processing distribution and achieve their final goal with performance maximization.

Until the recent past, grid and cluster computing as well as conventional supercomputers were the options used as powerful execution platforms to deal with most of the scientific and engineering applications. Nowadays, with the recent development of low-cost parallel and "plug-and-play" hardware, the community can profit from an interesting powerful execution platform, locally in a Personal Computer (PC). The many-core Graphics Processing Unit (GPU) is a good example. It is one of the most well known computing unit of this type. It evolved from specific application hardware for Computer Graphics to a multiprocessor architecture for general purposes computation (OWENS et al., 2007). Its computational power showed up along the time to be used beyond graphics utilities and now can be applied in favor of mathematical computations, physical simulations, scientific calculations, among other general processing. This trend is called General Purpose processing using GPU (GPGPU) (GPGPU, 2010).

As another example in the market, the Cell Processor followed a similar way of evolution as the GPU, evolving from a game purpose to compute tasks of generic purpose (KIM, 2008). It was firstly designed and commercialized as an embedded processor into game consoles and at present, based on user needs, it is also offered as an accelerator card (coupling eight heterogeneous processors) that can be plugged over a PCI Express bus.

The Field Programmable Gate Arrays (FPGA) is another example that has become attractive over the years due to its flexibility, even though it is not a common hardware like the GPU or the Cell Processor - it is devoted for more experienced users (CHE et al., 2008). The hardware itself is configurable and one can configure a specific FPGA with a processor (including multiple cores), memory, and logic cells. All these blocks are embedded in a general routing structure (also reconfigurable) which allows their inter-

#### connections.

From these examples, it can be verified that several alternatives for configuration of execution platforms and application programming can be stated, aiming at better application performance. The resulting execution platform can, then, be viewed as a heterogeneous multi-core architecture, combining some concepts of cluster and grid, but on a unique node of a common desktop or of portable computers. In other words, the combination of these multiprocessor units can be considered as an asymmetric set of Processing Units (PUs) and it is intensified with the new generation of multi-core Central Processing Units (CPUs), which, over the last few years, became indeed more powerful and have turned into processors of multiple cores. Due to their ability to deliver higher system performance more efficiently than single-core processors, the trend towards a higher number of cores is now established and a performance gain can be obtained using parallelization over the cores as well. Additionally, but not less important, all of these PUs are offered for a reasonable market price and as commodity, powering a PC to serve as a type of *supercomputer*.

In this sense, such low-cost hybrid hardware architectures (CPU, GPU, Cell, FPGA, etc) are becoming attractive to compose adaptable execution platforms in a single personal computer, being an alternative to the supercomputers or even clusters. Moreover, as crucial as the hardware evolution, software applications must, at the same time, evolve and benefit from that offer of powerfulness. However, it is a challenge to perform simple programming and perform efficient resource utilization in high level over the computing units in order to enable applications to move between different architectures and automatically scale as new processor generations are introduced (MCCOOL, 2008).

Some tools for parallelization based on threads already consider workload distribution over the multiple cores of a CPU. The same applies for the interfaces (drivers) for GPU or Cell, managing internal parallelization and giving certain flexibility and control to the programmer. On the other hand, an automatic coarser-grained parallelization focused on a high level design of processing distribution over the available PUs is lacking. The task of distributing the computation in high level is made currently at programming time by the designer without considering the entire context of the platform in a specific time. This way, runtime conditions are commonly not taken into consideration in the processing distribution. Below, some limitations are listed of current approaches:

- They are oriented to a specific hardware, i.e., applications are hard-coded using the specific API of the target PU, avoiding the flexibility of executing the same application on other PU without recoding and recompilation.

- They perform the load-balancing of tasks between different PUs in an off-line and statically pre-designed way. This means that the programmer codes which components of the application will execute in which hardware. If the execution platform configuration is changed or there is presence of load-imbalance, an application recoding is necessary.

- They do not take into account the runtime execution conditions of the platform, assuming that the PUs are completely idle without processing third party applications.

- They assume that the execution platform must be composed by the specific PU in which the application was developed, otherwise the application will not execute (even in a worst performance using the CPU, for example).

- They assume that the programmer must know specificities of each target PU architecture. For example, the programmer must manage the data over the memory levels (cache) explicitly using the programming language.

- They force the programmer to think not only about the main goal of his application, but also in low-level details (focused on the PU architecture) to balance the processing and extract a good performance from the application. Such a task considerably increases the programming complexity.

The presented items open possibilities towards the creation of new strategies that overcome these limitations, from a new programming layer, that encapsulates the APIs of the processing units, to automatic strategies that assign application's tasks to the most appropriated computing unit at a given runtime condition and aiming at performance maximization. This doctoral dissertation concentrates on the last approach: it introduces a framework that automatically tunes specific applications and performs a workload distribution of the applications (tasks, algorithms, or even full applications that must run concurrently) by choosing a processing unit as the execution target hardware in order to better meet applications' time requirements, such as performance.

Challenging applications that could benefit from the framework to obtain performance gain are simulation models of physical phenomena, which must precisely reflect the reality. For that, a high performance computing environment is decisive to accelerate numerical computations utilized on the applications, like on Computational Fluid Dynamics (CFD) (LUKSCH, 2000; WANG; YU; MA, 2010) used as case study in this thesis. This is an area of fluid mechanics highly used to simulate the fluid flows that are everywhere in our lives, like liquids and gases. It uses numerical methods that demand large computations for solving, for example, the velocity field and local pressure of the wind on objects like planes and cars. For those cases, a big computational effort is required for processing the complex, and sometimes recursive, mathematical models, clearly leading to the need of techniques that can optimize both computation time and performance.

The demand of improving the performance of a CFD application also emerged within the scope of an applied research project, focused on the industrial prototyping for a leading automobile industry in Germany. In CFD industrial prototyping, commonly default flow simulation is used, while in later stages of product development the models become more geometrically detailed and precise (LUKSCH, 2000). In the case of this project, by using a cluster of several CPUs for a traditional flow simulation, based on Navier-Stokes equations (FERZIGER; PERIC, 2002), the average calculation time takes about 12 hours<sup>1</sup>. At the same time, the error in accuracy between the actual aerodynamic behavior and the subsequent real prototype is around 5 %. This means that the used CFD model brings precision to the engineers, who maybe could accept to trade precision over simulation time in early stages of product development.

Based on that scenario, the industry wants to potentially increase the flow simulation in terms of performance, inserting a new CFD phase on early stages of product development. This phase has the goal to produce a real-time flow simulation executed on the engineers' desktop, commonly composed of a CPU and a GPU. Such simulation could use a less accurate, but still precise enough, CFD method to achieve the real-time requirement

<sup>&</sup>lt;sup>1</sup>Due to a non-disclosure agreement with the automobile company, details about the cluster configuration or CFD and car models cannot be described.

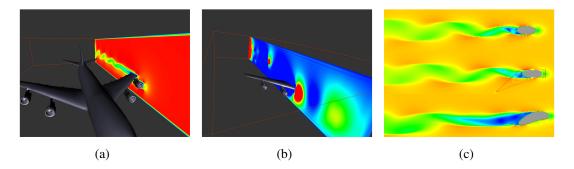

Figure 1.1: Real-time CFD Application: (a) velocity field and (b) pressure slice visualization of a 3D simulation; (c) a sequence of three time instances representing the velocity field visualization of a 2D simulation with real-time geometry modification

at the desktop. In this new phase, it is also desired that the engineer could interactively modify the geometry model to analyze its design over a virtual wind tunnel. This implies that the used models are not perfectly precise, but sufficiently accurate for early stages of product development. Additionally, it is desired that the engineer could simultaneously work with multiple simulations for visual comparison purposes.

This way, the main benefit of inserting this new phase is to reduce the number of times that precise CFD models (over accurate geometry models) need to be reevaluated in later stages of product development. Decreasing computation time without compromising the quality is clearly desired. For example, a 3D real-time CFD simulator with surface modification could be used to optimize a rough geometrical structure in early prototyping stages. As advantage, the number of times that accurate CFD models must be reevaluated in later stages of product development is expected to be significantly reduced, gaining time in the design process.

Based on these considerations, a 3D real-time CFD simulation was developed to be applied on the new proposed phase. The method is based on Stam (STAM, 1999), which presents an acceptable trade-off between accuracy and speed. In the method, it was identified that solving a System of Linear Equations (SLEs) used to compute the velocity and pressure, for example, was the most time expensive step on the workflow of the CFD method. Therewith, the performance of the solvers for SLEs were, then, improved in this thesis by using a new GPU-based strategy. Some examples of the developed CFD application are shown by Figure 1.1. Figure 1.1(a) depicts a slice of the developed 3D simulation that represents the velocity field visualization. Figure 1.1(b) shows the pressure visualization. And a real-time geometry modification is shown in Figure 1.1(c), where a 2D sequence of three images, i.e., three time instances represent the manipulation of an object's geometry.

But, the GPU-based solution was still static in terms of platform execution and configuration, and use the GPU or the CPU to compute the solvers. For real-time applications, efficiency with respect to both huge domain sizes and with small problems is important. Thus, a CPU-GPU platform dedicated to address these two different aspects is assumed to offer a better execution scenario than homogeneous ones.

Therefore, since this scenario does present a dynamic behavior (e.g., the domain size can vary, the execution platform is different over the desktops, the engineer can execute several simulations in parallel, etc), imposing thereby dynamic requirements to the ap-

plication, an static solution is no longer efficient. For such scenarios, the presence of strategies that dynamically adapt the application(s) to execute on a heterogeneous platform, like the CPU and the GPU with the requisite to obtain fast computational times using the resources in an efficient manner, is desirable. Following that line, dynamic and reconfigurable load-balancing computing (by means of a set of partitioning, allocation, and scheduling methods) is a potential paradigm for those scenarios. It can provide flexibility and improve efficiency, offering alternatives for programming an application on heterogeneous and multi-core architectures (FREITAS et al., 2008a).

#### 1.1 Goals

As already mentioned, desktop-based co-processors, like many-core GPUs, are nowadays a cost-effective alternative for those execution platforms that aim at better performance. Taking an example, Nvidia has presented its GPU GTX285 that provides a peak performance of 1062 Gflop/s for single precision and 89 Gflop/s for double precision (NVIDIA, 2010b).

As a consequence, heterogeneous platforms with several types of processing units act in essence as powerful asymmetric multi-core clusters and can handle multiple applications and tasks, like CFD and the tasks of solvers for SLEs. This is even intensified with the multi-core CPUs, like the Intel Core2Quad that provides around 100 Gflop/s (INTEL, 2010a). Therefore, *efficiently using all available resources from the heterogeneous execution platform* is a significant challenge to program applications.

In this direction, this thesis has the goal to provide methodologies, strategies and mechanisms that aggregates allocation and scheduling capabilities to tasks that must be executed by heterogeneous systems. By this means, the applications can be dynamically configured over the asymmetric architecture in order to use the most appropriate computational resources that can currently diminish the tasks' execution time.

In order to benefit from the powerfulness of all PUs, a strategy to distribute the application tasks onto such processing units is designed. The strategy lies on *dynamic scheduling*, instead of current static programming and scheduling model used by OpenCL (STONE; GOHARA; SHI, 2010) or, more specifically, by CUDA (NVIDIA, 2010b) for Nvidia GPUs (see also the work of Göddeke et al. (GÖDDEKE et al., 2009)). This need becomes even more essential when dealing with desktop applications that present timing constraints, like the real-time CFD application that partially motivated this work.

#### 1.2 Contributions

The topic "scheduling for hybrid multi-core platforms" has been identified as one important open problem by the recent ICT (Information and Communication Technologies) call for research proposals of the European Commission, named Framework Program 7 (COMMISSION, 2010), shortly FP7, and by the Roadmap on High-Performance Embedded Architecture and Compilation that drives the importance of several open problems in the area of computer science (DE BOSSCHERE et al., 2007). The references explicitly mention that the availability of multiple cores is a trend and will integrate up to 1000 billion devices by the year 2020. It indicates that these devices will provide orders of

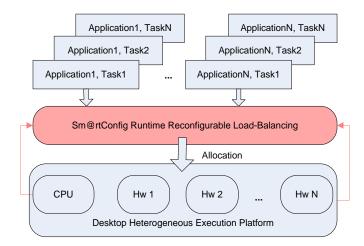

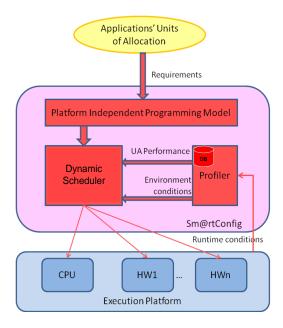

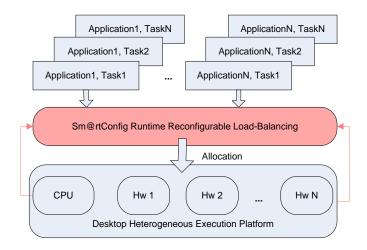

Figure 1.2: Sm@rtConfig system overview

magnitude for performance improvement only with much higher concurrency and with heterogeneous architectures tuned to specific application kernels. In addition, an analogous report made by the Council of Advisors on Science and Technology of the United States of America claims that performance gains due to improvements in algorithms have exceeded the performance gains due to increased processor speed (SCIENCE; TECHNOLOGY, 2010). The report also focuses on the need of system management tools for the next generation of high performance technologies, including research on hardware/software systems and in both systems software and applications software. Based on these statements, this thesis addresses punctually the assignment methods over heterogeneous platforms, specially composed of CPU and GPU.

Figure C.1 gives an overview of the thesis contributions, where the proposed framework is called Sm@rtConfig. Coupling the discovery of computing unit resources of the platform with the applications' characteristics, an analysis is performed to configure the tasks allocation balance over the available processing units. During runtime, the Sm@rtConfig profiles the performance of tasks feeding the balancer towards a possible new allocation if this procedure can promote a better performance.

This framework presents a new strategy to distribute the workload over the CPU and the GPU, being sufficient generic to consider other PUs coupled in a desktop. The dynamic assignment methods combine a *first assignment phase* for a set of *high-level tasks* (algorithms, for example) with a *runtime phase* that obtains real performance measurements of tasks, feeding a *performance database*. The first assignment is based on a preprocessing benchmark for acquiring basic computational times' samples of the tasks on each PU. This way, after the first assignment, the system considers the history presented on the database to perform further assignments for every task, maximizing the applications' performance with load-balance and minimal overhead.

In summary, the main contributions of this thesis are:

1. The development of a framework that comprises: (i) a *first assignment phase* of tasks, (ii) a runtime *profiler* that feeds a *timing performance database*, and (iii) the *runtime assignment phase* that performs dynamic assignments based on the performance history;

- 2. The development of a new strategy for storing and retrieving data, used by the tasks of SLEs' solvers, on the GPU memory hierarchy aiming memory coalescing and using the shared memory, with a performance gain compared to state-of-the-art works;

- 3. The analysis of the solvers' characteristics and their performance on a CPU-GPU platform, expressing the conditions where the solvers (tasks) obtain better execution performance (i.e., finding a so-called performance *break-even point* that indicates the best PU to be used) for performance tuning purposes;

- 4. The implementation and comparison of three different iterative methods to solve SLEs (Jacobi, Gauss-Seidel, and Conjugate Gradient) on the CPU and multiple GPUs, applied to a real-time CFD simulation with a geometry modification example.

All main parts of this thesis have been published in several conferences, which demonstrate the recognition of this work by the research community. Moreover, it indicates the relevance of the investigations carried out in the scope of this research. An initial study of virtual engineering was performed by Binotto et al. in 2006 (BINOTTO et al., 2006), followed by a study that used the GPU to enhance the performance of engineering based simulations (BINOTTO et al., 2006). Then, the basic concepts of this thesis were further published in 2008 (FREITAS et al., 2008a; BINOTTO et al., 2008), refined by a journal (BINOTTO et al., 2009) and a conference (BINOTTO et al., 2009) publication in 2009, being also applied to other case studies rather than CFD (FREITAS et al., 2008b; BINOTTO et al., 2008; FREITAS et al., 2009).

The solvers for SLEs tasks, used by the CFD application, were presented by Binotto, Pereira, and Fellner in 2010 (BINOTTO; PEREIRA; FELLNER, 2010) and further detailed in the same year (BINOTTO et al., 2010). The works described the execution over the heterogeneous platform composed by a CPU and a GPU, indicating the importance of a tuning system based on performance break-even points and of an efficient method to implement the solvers specifically for the GPU architecture. It is important to note that understanding the most efficient design and utilization of emerging multi-core systems is one of the most challenging questions and a flexible platform composed of the CPU and the GPU of different capabilities can be benefited by performance tuning strategies for switching over the PUs.

Furthermore, some of the assignment algorithms available on the framework were published by the author in 2010 as well (BINOTTO et al., 2010). To finalize, an article about the complete framework description - with additional infrastructure to support the whole dynamic scheduling and performance tuning system of high-level tasks for virtual engineering - was recently invited for extended publication in the special issue on Advanced Software Engineering in Industrial Automation of the journal Control Engineering Practice to be published by Elsevier in early 2012.

#### 1.3 Outline

The thesis is organized as follows:

Chapter 2 provides the necessary background information on theoretical concepts for

a clear understanding of the topics discussed in the subsequent chapters. It emphasizes the modern architectures of the many-core CPUs and multi-core GPUs, their respective programming models, and solutions that couple the CPU and the GPU aiming at a better performance.

Chapter 3 summarizes relevant state-of-the-art work. It includes a survey on the use of the GPU for computations of virtual engineering applications, concentrating on CFD cases and solvers for SLEs. It also describes in details distributed and heterogeneous platforms, based on CPU and GPU, aiming at application performance gain and systems that benefit from the workload distribution and dynamic assignment of tasks over the CPU and the GPU. A comparison between the main related work and the subject of this thesis is emphasized at the end of the chapter.

**Chapter 4** introduces the methodologies and strategies adopted by the Sm@rtConfig framework to manage the allocation and reconfiguration of tasks over the heterogeneous architecture. These strategies are mainly based on low complexity heuristic algorithms and have the goal to perform a load-balancing of tasks that are needed to be concurrently executed.

**Chapter 5** shows the CFD case study used to validate the proposed strategies, gives a mathematical introduction of the solvers for SLEs, and a method for implementing the solvers on the GPU, focusing on the loading data strategy that provides performance gains for the case study. It also describes the exploitation of the CPU and the GPU concurrently.

**Chapter 6** discusses the experimental results based on a performance analysis oriented to the heterogeneous platform approach, presenting the performance break-even points using this heterogeneous execution platform. The chapter explains the use of the proposed framework and its benefits.

**Chapter 7** closes the text with a conclusion of the presented work and the ongoing work to improve the framework functionalities. Finally, it signals directions on which further work can be conducted.

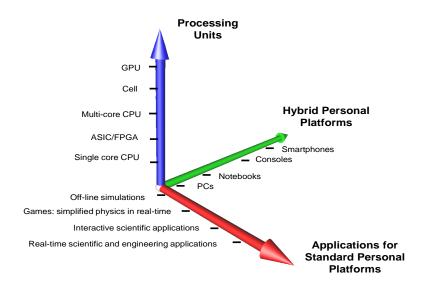

## 2 THEORETICAL BACKGROUND

With the recent development of consumable parallel and low-cost dedicated and generic purpose processors, several applications (including the virtual engineering applications) can be executed on "standard" personal computers or portable devices, like notebooks, with relatively good performance. It is an evolution on the microprocessor die, from single core devices to devices with multiple cores and parallel computational capabilities, being an alternative for high performance platforms. Figure 2.1 exemplifies, in the blue axis, the evolution of the processing units in terms of an increasing number of cores; in the green axis, the types of platforms that can be powered with hybrid processing units; and, on the red axis, the performance demand of applications and their evolution on personal platforms. The figure suggests a 3D relationship since processing units, applications, and platforms are highly evolving at the same time.

Figure 2.1: Relevant evolution of personal platforms and its processing units in correlation to application's needs

In addition, software libraries and runtime systems must also meet the programmers' and applications' needs for gaining performance, i.e., they must be implemented to explore the performance capabilities from that kind of hardware with multiple cores. In addition, it has to support the composition of heterogeneous processing units at the same

platform. Nevertheless, software techniques and strategies to explore modern multi-core and heterogeneous platforms are still under development, like the OpenCL (STONE; GOHARA; SHI, 2010) which is a framework for coding applications that execute across heterogeneous platforms.

This chapter presents the background information about the related hardware used in this research (CPU and GPU), their controlling APIs, and some approaches oriented to common programming over an execution platform composed of the heterogeneous hardware. Besides, a mathematical overview on the solvers for SLEs is given, since they are used as tasks of the virtual engineering case study. The background of the solvers helps on making clear how they were implemented for the CPU-GPU platform and the need to use the concepts presented on the developed framework.

#### 2.1 Multi-core CPUs

This section gives the necessary background information for the understanding of the modern multi-core CPUs. It describes the hardware fundamentals and current software functionalities, mainly from APIs and standard software tools, to explore the performance given by the parallel hardware technologies.

#### 2.1.1 Hardware characteristics

The main computational engine of modern computers, the CPU, is becoming highly parallelized. The sustained growth in transistor density (Moore's law) allows chip designers to put more and more processor cores on a single silicon die. Until 2004, consumers experienced an increase in performance through a steady growth in core clock frequency. Consequently, most commodity processors only included one processor core. Threads facilitate the concurrent programming and were commonly used in software programs to improve performance by splitting instructions into multiple streams so that multiple processors could act upon them.

As a first on-die indication of parallelization, the Hyper-Threading (HT) technology was produced by the company Intel and was one of the steps with the goal to bring parallelism at a single CPU in a higher program level (INTEL, 2010b). Emulating a dual-core processor, it provided thread-level parallelism, resulting in more efficient use of processor resources, higher processing throughput, and improved performance on multi-threaded software. The single processor supporting HT technology presented itself to the operating systems and applications as two virtual or logical processors and could work on two sets of tasks "simultaneously", use resources that otherwise would sit idle, and get more work done in the same amount of time. This was one of the first indicators oriented to multi-core.

In the last years, the community has seen only little increase in core clock frequency. The trend of the two major players (Intel and AMD) is to offer increased performance over symmetric multi-core commodity chips. Physical dual-core processors on one die have become a mainstream in desktop and mobile devices due to their ability to deliver high system performance for complex applications running at personal platforms. It is also more efficient on energy consumption, since, for example, two processors running on a half of frequency of one single core have the same computational power, but with

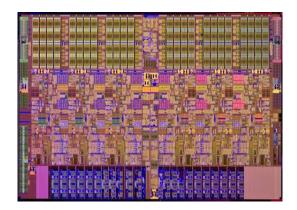

Figure 2.2: 6-core CPU from the Intel company (SCHROUT, 2010)

half of energy consumption.

In multi-core, application threads can be independently scheduled, dispatched, and processed by the available processors. In other words, multi-core processors enable true multitasking on the contrary of the old single-core systems where multitasking usually resulted in decreased performance as operations must wait to be processed in a queue. Thus, presently, on multi-core systems, each core has its own cache, providing the operational system with resources to handle compute-intensive tasks absolutely in parallel (MCCOOL, 2008).

The trend towards a higher number of cores is continuing strong with quad-core processors which are establishing an increasing presence across the market segments over a reasonable price, optimizing the trade-off between silicon material, performance, and energy efficiency. Figure 2.2 shows an example of the circuit of a six-core processor, the Intel's Nehalem Core i7 model.

Therefore, applications can obtain considerable performance gains using multi-core platforms. As an example, following the Amdahl's law, the amount of performance that can be gained depends on the characteristics of the application and states that a fraction of a program's execution time is infinitely parallelizable with minimal or no overhead, while the remaining part is sequential (AMDAHL, 1967). In a multi-core era, increasing core performance, even if it appears locally inefficient, can be globally efficient by reducing the idle time of the rest of the chip's resources, having a demand for global load-balancing "on the fly". Overall, performance gain should be viewed regarding the entire multi-core chip rather than punctually focused on one core or processor. The validity of this concept is intensified when dealing with heterogeneous processors (HILL; MARTY, 2008).

#### 2.1.2 Software functionalities

Although the computing community settled on the random-access machine model for serial computing early in the history of computer science, no single model for parallel computing has gained as wide acceptance (CORMEN et al., 2009). Probably, a major reason is the competitiveness where the vendors have not agreed on a single architectural model for parallel computers. With the advent of the multi-core technology, every new laptop and desktop machine tends to become a shared-memory parallel computer and the trend appears to be toward shared-memory multiprocessing, where each processor can

directly access any location of memory.

The OpenMP API is one of the most known tools utilized to obtain a performance gain via software parallelization, being processor independent (OPENMP, 2010). It is used to explicitly create multithreaded and shared memory parallelism where the user specifies the regions in the code that can be executed in parallel and can also specify necessary synchronization to ensure correct execution of the parallel regions. More concrete, programmers write their code in standard programming languages, like C++, and provide hints to the compiler via *pragmas* about which loops can be parallelized and how the execution of the loop should be distributed among the processors. At runtime, threads are forked for the parallel region and are typically executed in different virtual processors, sharing the same memory.

It became very attractive to programmers because they do not have to use a new programming language, just adapt the code with the key pragmas and the compiler does the job. Unfortunately, the pragmas may differ between compilers, although there is a standard subset which is generally used, but requires a compiler that supports it. In addition, using vendor extensions for better optimization (and targeting a specific machine) comes at the cost of portability. It can also be inefficient on large shared memory machines because of non-uniform memory access effects and makes distributed memory implementations problematic since there is no notion of locality.

Within the multi-core era, some new tools - developed usually by chip vendors - became available. Intel, for instance, developed the open source Threading Building Blocks (TBB) as a template for writing software that specifically takes advantage from multi-core processors. It offers a high-level task-based parallelism that abstracts the complexity and platform details for performance and scalability goals, treating the operations as tasks that are dynamically allocated to the individual cores by the runtime module (INTEL, 2010c). The company also developed the C for Throughput Computing (Ct), a commercial software package to ease the exploitation of its multi-core chips. Just very recently, the Ct turned into the Array Building Blocks (ARBB) to provide a generalized vector parallel programming solution that frees application developers from dependencies on particular low-level parallelism mechanisms or hardware architectures (INTEL, 2011). It is comprised of a combination of standard C++ library interface and powerful runtime system. It produces scalable, portable, and deterministic parallel implementations from high-level source description. The ARBB functionalities are more detailed in Subsection 2.3 because it is a merge from Ct and a vendor-independent runtime system for heterogeneous processing units.

Similar to the TBB, the AMD company offers a commercial tool oriented to multiprocessing, named CodeAnalyst, which is a set of tools to analyze software performance devoted to AMD microprocessors (AMD, 2010a). However, it is not dedicated to bring control for software developers about the multiple cores, but it is oriented for profiling the code to identify bottlenecks and opportunities for parallelization (shown to programmer by a visualization tool). AMD, which acquired the ATI GPU manufacturer, is also investing on an tool for heterogeneous platforms: the OpenCL.

Going to a solution that is independent from processor's vendors, Cilk is a set of programming language extensions for C developed by the MIT laboratory since 1994 and focusing on high performance computing (BLUMOFE et al., 1995). With the advent of multi-core architecture, the tool became commercial as a library supporting the C++

programming language. The commercial version was shipped to the market in the end of 2008 and focuses to maximize application performance on CPU multi-core processors (INTEL, 2010d).

As the other libraries cited before, Cilk enables the programmers to develop parallel applications retaining the serial methodologies for programming. The programmer just needs to write a Cilk property command before the function to be parallelized. The Cilk compiler and the runtime module deals automatically with threading parallelization to spawn and schedule threads to processing elements, delivering code to the operational system that manages and balances the execution over the multi-core CPU. The main commands are  $cilk_spawn$  (posed just before a call of a function to indicate that such function can be executed in parallel) and  $cilk_sync$  (for synchronization). Additionally, it presents the  $cilk_for$  to perform loop parallelization. Very recently, the company that commercialized Cilk was acquired by the Intel company.

## 2.2 Many-core GPUs

This section gives the necessary background information for the understanding of the modern many-core GPUs. It describes the complexity of the hardware architecture and the APIs, programming languages, and other software tools and functionalities that a programmer needs to use for developing an application that explores the parallel power of such a processing unit.

#### 2.2.1 Hardware characteristics

Originally, Graphics Processing Units (GPUs) were designed to accelerate graphics applications, having the game industry as the main demand. GPUs are programmable processors based on the scan and rasterization concept presented on the graphics pipeline, which is implemented in a parallel way. It is based on SIMD (Single-Instruction/Multiple-Data) architecture and its processors are composed by several parallel processing group units that implement the so-called flow-based computation pipeline (GPGPU, 2010).

In summary, in its root, the computer graphics application would "prepare and send" a list of vertices (together with their properties) from objects placed on a scenario to the GPU. The hardware will, then, be responsible to apply a set of programmable effects and generates, as a result, the pixel colors of the final image to be visualized. Additional information on such details of programmable graphics hardware history, modules, and functionality applied to computer graphics can be taken from the work of Krüger (KRÜGER, 2006).

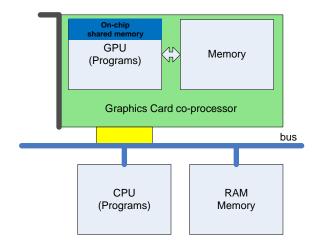

The approach of this research focuses on the performance of the GPU as a co-processor unit of the CPU for general calculations, i.e., the generic purpose of the GPU (OWENS et al., 2007). Figure 2.3 depicts the use of a graphics board as a device in a desktop with the CPU as a host. The CPU manages the execution of applications using the RAM memory and can transfer data to the memory of the co-processor using the bus. Once data is transferred to the device, the GPU programs are parallel executed and the final result can be transferred back to the CPU for further interventions.

This potential use of the GPU as a common parallel co-processor emerged during the last decade and made this PU evolving from being graphics-fixed functionality processors

Figure 2.3: The GPU as a co-processor of the CPU

to become very powerful programmable many-core data stream processors (SCHIWIETZ, 2008). That vision was mainly possible due to its parallel conception of having different groups of processors (multiprocessors) working in the same calculation in parallel, but operating on different input data. In other words, at a given clock cycle, each processor of a multiprocessor executes the same instruction, but operating on different data.

Based on that parallelization, the GPUs, along its growth of performance gain, reported better achievements in terms of performance than the ones from CPUs, since it offers an even higher number of parallel cores than the central unit. The Nvidia GPU vendor comments that the main reason behind such an evolution is that the GPU is compute-intensive oriented, supported by highly parallel computation and therefore is designed such that more transistors are devoted to data processing rather than data caching and flow control (NVIDIA, 2010a).

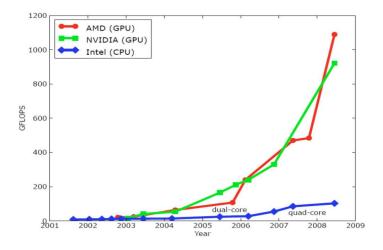

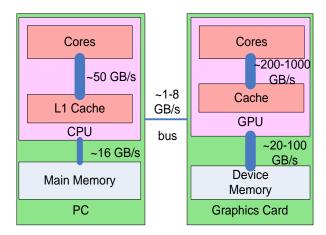

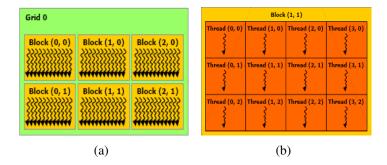

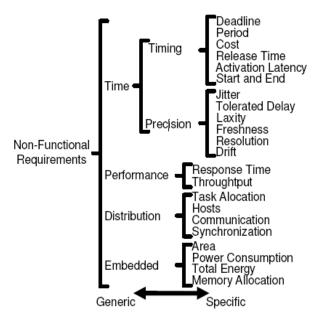

For example, there are 480 cores (2x30 multiprocessors, where each multiprocessor is composed of 8 processors) in the Nvidia GeForce GTX 295 model compared to 4 units of the quad-core CPU. A commonly used comparison about the evolution of GPUs is based on Moore's law. It is a prediction concept positing that the number of transistors placed on an affordable commercial chip doubles in every two years. However, the law seems to be not valid when it comes to the graphics hardware scenario, even when the number of transistors alone does not reflect a gain of performance since there are some overhead using GPUs, like data transmission. Figure 2.4 shows a comparison of the performance growth between CPUs and GPUs over the recent years, emphasizing the peak capacity. It represents the real local peak performance of the processors for floating point calculations.