## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

EDUARDO HENRIQUE MOLINA DA CRUZ

Dynamic Detection of the Communication Pattern in Shared Memory Environments for Thread Mapping

> Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Dr. Philippe O. A. Navaux Advisor

### **CIP – CATALOGING-IN-PUBLICATION**

Eduardo Henrique Molina da Cruz,

Dynamic Detection of the Communication Pattern in Shared Memory Environments for Thread Mapping /

Eduardo Henrique Molina da Cruz. – Porto Alegre: PPGC da UFRGS, 2012.

86 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2012. Advisor: Philippe O. A. Navaux.

Thread mapping.

Parallel computer architectures.

Shared memory.

Communication.

Cache memory.

Cache coherence protocols.

TLB. I. Navaux, Philippe O. A., II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Carlos Alexandre Netto Pró-Reitor de Coordenação Acadêmica: Prof. Rui Vicente Oppermann Pró-Reitora de Pós-Graduação: Prof. Aldo Bolten Lucion Diretor do Instituto de Informática: Prof. Prof. Luís da Cunha Lamb Coordenador do PPGC: Prof. Álvaro Freitas Moreira Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"I believe in intuition and inspiration. Imagination is more important than knowledge. For knowledge is limited, whereas imagination embraces the entire world, stimulating progress, giving birth to evolution. It is, strictly speaking, a real factor in scientific research." — ALBERT EINSTEIN

# AGRADECIMENTOS

Agradeço minha mãe por seu esforço e pelo apoio nessa jornada da Pós-Graduação, sendo que dedico este trabalho a ela. Também agradeço a meu pai, a quem pude aumentar o grau de contato agora que moramos mais próximos. Não esqueço também da importância do meu primo (que está mais para irmão) Gustavo, da minha tia Lourdes, meu tio Luiz, e de todos meus outros familiares. Relembro aqui também de meus grandes amigos Guilherme, Ramon, Christian e Igor, que, apesar da distância e falta de contato, são pessoas muito importantes em minha vida.

A meus amigos do GPPD, obrigado pelas dicas, discussões e, não menos importantes, momentos de descontração durante estes 2 anos de mestrado. Um agradecimento especial ao professor Navaux pela orientação e oportunidade que me ofereceu. Ressalto também os amigos que tiveram um contato mais próximo com este trabalho. O Marco pelos conselhos e puxões de orelha, o Matthias pela ajuda no desenvolvimento de algumas das propostas, e o Kassick pelo auxílio na correção.

Aos familiares e amigos que aqui não citei, obrigado por tudo.

# CONTENTS

| LIST                      | OF ABBREVIATIONS AND ACRONYMS                                                                                            | 9                    |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|

| LIST                      | OF FIGURES                                                                                                               | 11                   |

| LIST                      | OF TABLES                                                                                                                | 13                   |

| ABST                      | TRACT                                                                                                                    | 15                   |

| RESU                      | JMO                                                                                                                      | 17                   |

| 1 IN<br>1.1<br>1.2<br>1.3 | NTRODUCTION                                                                                                              | 19<br>19<br>20<br>21 |

| 2 T<br>2.1<br>2.2         | HREAD MAPPING       Properties of a thread mapping mechanism         Static thread mapping       Providential statements | 23<br>24<br>25       |

| 2.2.1                     | Static thread mapping based on simulation                                                                                | 26                   |

| 2.2.2                     | Static thread mapping based on dynamic binary analysis                                                                   | 28                   |

| 2.2.3                     | Static thread mapping based on hardware counters                                                                         | 28                   |

| 2.2.4                     | Static process mapping applied to message passing based applications                                                     | 28                   |

| 2.3                       | Dynamic thread mapping                                                                                                   | 29                   |

| 2.3.1                     | Dynamic thread mapping using hardware counters                                                                           | 29                   |

| 2.3.2                     | Dynamic data mapping applied to NUMA machines                                                                            | 30                   |

| 2.3.3                     | Dynamic process mapping applied to message passing based applications                                                    | 31                   |

| 2.4                       | Summary of the state-of-art                                                                                              | 31                   |

|                           | ROPOSED METHODS FOR DYNAMIC DETECTION OF THE COM-                                                                        | 33                   |

| 3.1                       | Exploiting Cache Coherence Protocols                                                                                     | 33                   |

| 3.1.1                     | Snoop Protocols                                                                                                          | 33                   |

| 3.1.2                     | Directory protocols                                                                                                      | 36                   |

| 3.1.3                     | Properties and procedures common to all cache coherence based mecha-<br>nisms                                            | 39                   |

| 3.2                       | Exploiting the Translation Lookaside Buffer                                                                              | 40                   |

| 3.2.1                     | Mechanism for Software-Managed TLBs                                                                                      | 41                   |

| 3.2.2                     | Mechanism for Hardware-Managed TLBs                                                                                      | 42                   |

| 3.3                       | Summary of the proposed methods                                                                                          | 43                   |

|       | VALUATION OF THE MECHANISMS FOR DYNAMIC DETECTION           |    |

|-------|-------------------------------------------------------------|----|

| 0     | F THE COMMUNICATION PATTERN                                 | 47 |

| 4.1   | Implementation inside the simulator                         | 47 |

| 4.2   | Thread mapping algorithm                                    | 48 |

| 4.3   | Platform                                                    | 50 |

| 4.3.1 | Simulated environment                                       | 50 |

| 4.3.2 | Real machine                                                | 50 |

| 4.4   | Validating the proposals using a microbenchmark             | 52 |

| 4.4.1 | Communication pattern                                       | 53 |

| 4.4.2 | Performance results                                         | 53 |

| 4.5   | Workload                                                    | 54 |

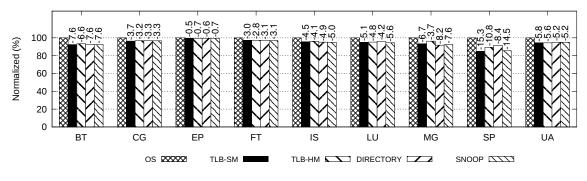

| 4.5.1 | Tools used to obtain the communication pattern baseline     | 54 |

| 4.5.2 | Communication pattern baseline                              | 56 |

| 5 R   | ESULTS                                                      | 59 |

| 5.1   | Communication Patterns                                      | 59 |

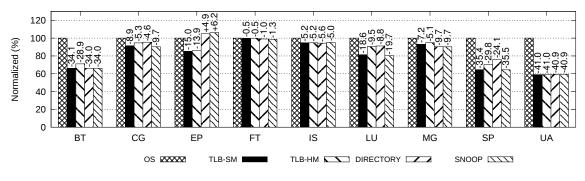

| 5.2   | Evaluating the Performance using Thread Mapping             | 63 |

| 5.3   | Overhead of the Mechanisms                                  | 67 |

| 5.3.1 | Cache coherence based mechanisms                            | 67 |

| 5.3.2 | TLB based mechanisms                                        | 67 |

| 6 C   | ONCLUSION AND FUTURE WORK                                   | 69 |

| REFE  | RENCES                                                      | 71 |

| 7 A   | PPENDIX - SUMMARY IN PORTUGUESE                             | 77 |

| 7.1   |                                                             | 77 |

| 7.2   | Mapeamento de Threads                                       | 78 |

| 7.3   | Propostas de mecanismos para mapeamento dinâmico de threads | 79 |

| 7.3.1 | Mecanismos baseados em coerência de cache                   | 79 |

| 7.3.2 | Mecanismos baseados em TLB                                  | 81 |

| 7.4   | Metodologia                                                 | 82 |

| 7.5   | Resultados                                                  | 83 |

| 7.5.1 | Padrões de comunicação                                      | 83 |

| 7.5.2 | Testes de desempenho                                        | 84 |

| 7.6   | Conclusão                                                   | 85 |

# LIST OF ABBREVIATIONS AND ACRONYMS

- SMP Symmetric Multi-Processor

- SMT Simultaneous Multithreading

- NUMA Non-Uniform Memory Access

- SIMD Single Instruction Multiple Data

- SPMD Single Program Multiple Data

- ISA Instruction Set Architecture

- I/O Input/Output

- MIPS Million Instructions per Second

- GPU Graphic Processing Unit

- NoC Network-on-Chip

- DBA Dynamic Binary Analysis

# **LIST OF FIGURES**

| Snoop based mechanism for private caches                                    | 34                                    |

|-----------------------------------------------------------------------------|---------------------------------------|

| Snoop based mechanism for shared caches                                     | 35                                    |

| Centralized directory based mechanism.                                      | 37                                    |

| Distributed directory based mechanism.                                      | 38                                    |

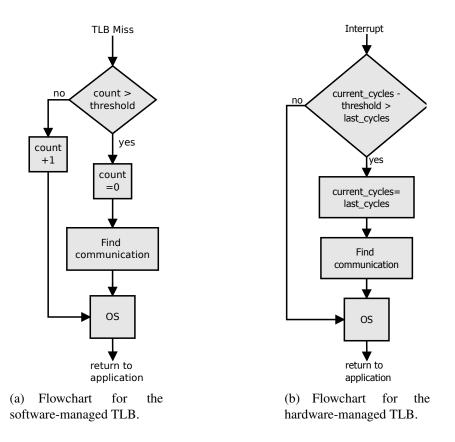

| Flowcharts for the proposed TLB based mechanisms                            | 41                                    |

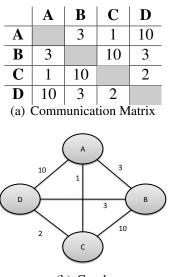

| Communication Matrix and the corresponding Communication Graph.             | 48                                    |

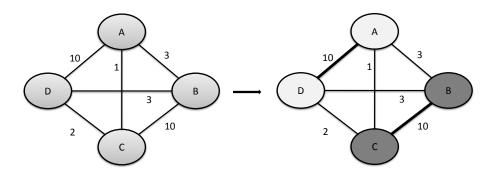

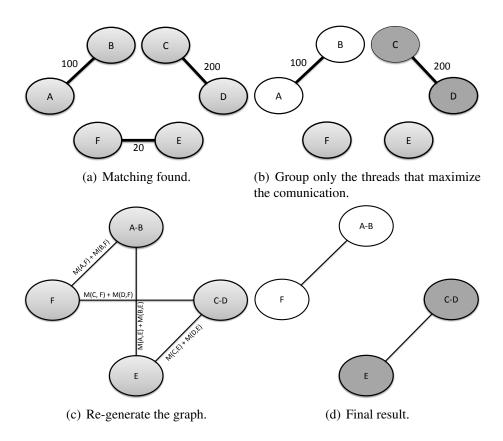

| The Matching Problem.                                                       | 49                                    |

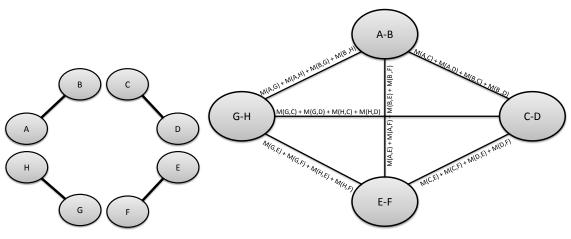

| Heuristic used to generate new communication graphs from previous           | -                                     |

| 0                                                                           | 50                                    |

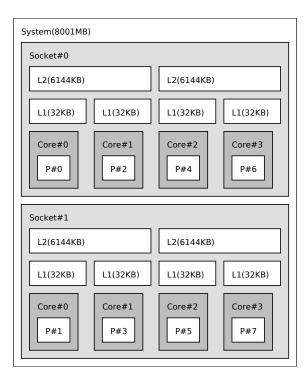

|                                                                             | 51                                    |

|                                                                             | 51                                    |

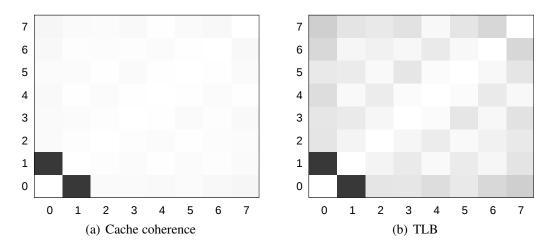

| •                                                                           | 52                                    |

| 1 1                                                                         | 54                                    |

| -                                                                           | 55                                    |

|                                                                             | 56                                    |

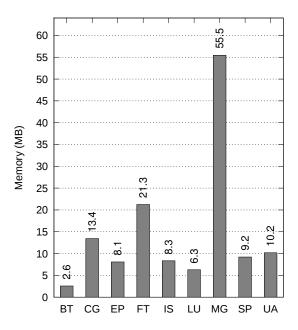

| Amount of memory shared by the threads of NPB                               | 57                                    |

| Amount of memory used by the applications of NPB                            | 57                                    |

| Number of accesses to the shared memory (5 million cycles time win-<br>dow) | 57                                    |

| Number of accesses to the shared memory (50 million cycles time window)     | 57                                    |

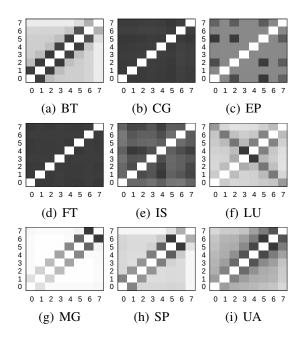

| Communication patterns of the applications from NPB discovered              |                                       |

| -                                                                           | 60                                    |

|                                                                             | 60                                    |

| •                                                                           | 00                                    |

| with the snoop coherence mechanism.                                         | 61                                    |

| Communication patterns of the applications from NPB discovered              |                                       |

| with the directory coherence mechanism (32kb L1 cache)                      | 61                                    |

| Communication patterns of the applications from NPB discovered              |                                       |

|                                                                             | 61                                    |

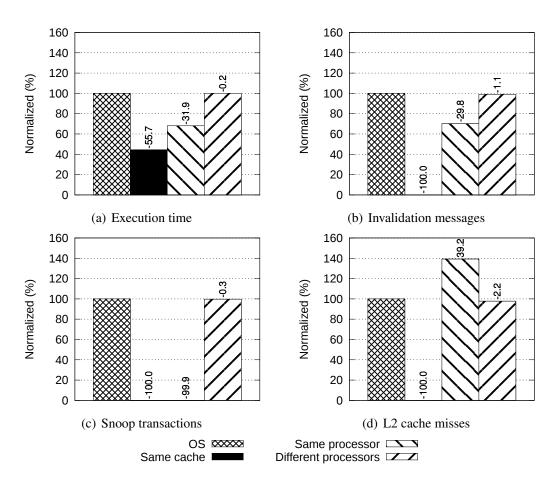

|                                                                             | 64                                    |

| 11                                                                          | 64                                    |

| 1                                                                           | 64                                    |

| Snoop transactions.                                                         | 64                                    |

|                                                                             | Centralized directory based mechanism |

# LIST OF TABLES

| Table 2.1: | Summary of the characteristics of current thread mapping mechanisms. | 31 |

|------------|----------------------------------------------------------------------|----|

| Table 3.1: | Examples of the snoop based mechanism for private caches             | 35 |

| Table 3.2: | Examples of the snoop based mechanism for shared caches              | 36 |

| Table 3.3: | Examples of the centralized directory based mechanism                | 37 |

| Table 3.4: | Examples of the distributed directory based mechanism.               | 39 |

| Table 3.5: | Comparison between the proposed mechanisms                           | 43 |

| Table 4.1: | Configuration of the caches using the original Simics modules        | 50 |

| Table 4.2: | Configuration of the caches using Ruby                               | 52 |

| Table 4.3: | Configuration of the caches of the real machine                      | 53 |

| Table 4.4: | Comparative between tools that can be used to detect the memory      |    |

|            | accesses                                                             | 56 |

| Table 5.1: | Mappings obtained by applying the thread mapping algorithm           | 62 |

| Table 5.2: | Execution time and number of invalidations, snoop transactions and   |    |

|            | L2 cache misses per second.                                          | 66 |

| Table 5.3: | Standard deviations for the performance experiments                  | 66 |

| Table 5.4: | Statistics for the software-managed TLB.                             | 67 |

|            |                                                                      |    |

# ABSTRACT

The threads of parallel applications cooperate in order to fulfill their tasks, thereby communication is performed among themselves. The communication latency between the cores in a multiprocessor architecture differs depending on the memory hierarchy and the interconnections. With the increase in the number of cores per chip and the number of threads per core, this difference between the communication latencies is increasing. Therefore, it is important to map the threads of parallel applications taking into account the communication between them.

In parallel applications based on the shared memory paradigm, the communication is implicit and occurs through accesses to shared variables, which makes difficult to detect the communication pattern between the threads. Traditional approaches use simulation to monitor the memory accesses performed by the application, requiring modifications to the source code and drastically increasing the overhead.

In this master thesis, we introduce two novel light-weight mechanisms to find the communication pattern of threads. The first mechanism makes use of the information about shared cache lines provided by cache coherence protocols. The second mechanism makes use of the Translation Lookaside Buffer (TLB) to detect which memory pages each core is accessing. Both our mechanisms rely entirely on hardware features, which makes the thread mapping transparent to the programmer and allows it to be performed dynamically by the operating system. Moreover, no time consuming task, such as simulation, is required.

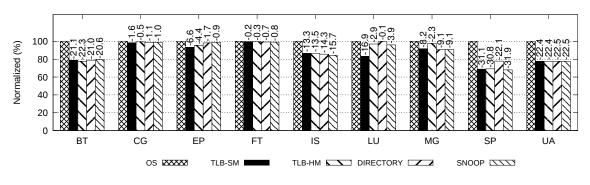

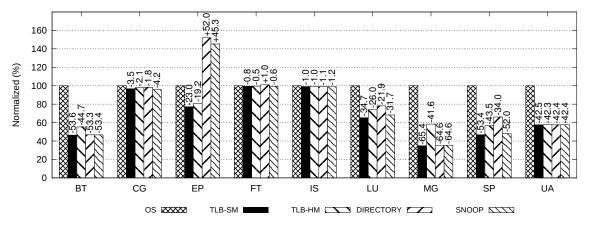

We evaluated our mechanisms with the NAS Parallel Benchmarks (NPB) and obtained accurate representations of the communication patterns. We generated thread mappings from the detected communication patterns using a mapping algorithm. Mapping is a NP-Hard problem. Therefore, in order to achieve a polynomial complexity, we designed a heuristic method based on the Edmonds graph matching algorithm. Running the applications with these mappings resulted in performance improvements of up to 15.3% compared to the original scheduler of the operating system. The number of cache misses, cache line invalidations and snoop transactions were reduced by up to 31.9%, 41% and 65.4%, respectively.

**Keywords:** Thread mapping, parallel computer architectures, shared memory, communication, cache memory, cache coherence protocols, TLB.

### Detecção Dinâmica do Padrão de Comunicação em Ambientes de Memória Compartilhada para o Mapeamento de Threads

## RESUMO

As *threads* de aplicações paralelas cooperam a fim de cumprir suas tarefas, dessa forma, comunicação é realizada entre elas. A latência de comunicação entre os núcleos em arquiteturas multiprocessadas diferem dependendo da hierarquia de memória e das interconexões. Com o aumento do número de núcleos por *chip* e número de *threads* por núcleo, esta diferença entre as latências de comunicação está aumentando. Portanto, é importante mapear as *threads* de aplicações paralelas levando em conta a comunicação entre elas.

Em aplicações paralelas baseadas no paradigma de memória compartilhada, a comunicação é implícita e ocorre através de acessos à variáveis compartilhadas, o que torna difícil a descoberta do padrão de comunicação entre as *threads*. Mecanismos tradicionais usam simulação para monitorar os acessos à memória realizados pela aplicação, requerendo modificações no código fonte e aumentando drasticamente a sobrecarga.

Nesta dissertação de mestrado, são introduzidos dois mecanismos inovadores com uma baixa sobrecarga para se detectar o padrão de comunicação entre *threads*. O primeiro mecanismo faz uso de informações sobre linhas compartilhadas de caches providas por protocolos de coerência de cache. O segundo mecanismo utiliza a *Translation Lookaside Buffer* (TLB) para detectar quais páginas de memória cada núcleo está acessando. Ambos os mecanismos dependem totalmente do *hardware*, o que torna o mapeamento de *threads* transparente aos programadores e permite que ele seja realizado dinamicamente pelo sistema operacional. Além disto, nenhuma tarefa de alta sobrecarga, como simulação, é requerida.

As propostas foram avaliadas com o *NAS Parallel Benchmarks* (NPB), obtendo representações precisas dos padrões de comunicação. Mapeamentos para as *threads* foram gerados utilizando os padrões de comunicação descobertos e um algoritmo de mapeamento. O problema do mapeamento é NP-Difícil. Portanto, de forma a se atingir uma complexidade polinomial, o algoritmo empregado é heurístico, baseado no algoritmo de emparelhamento de grafos de Edmonds. Executando as aplicações com o mapeamento resultou em um ganho de desempenho de até 15, 3%. O número de faltas na cache, invalidações em linhas de cache e transações de espionagem foram reduzidos em até 31, 9%, 41% e 65, 4%, respectivamente.

**Palavras-chave:** mapeamento de threads, arquiteturas paralelas de computadores, memória compartilhada, comunicação, memória cache, protocolos de coerência de cache, TLB.

# 1 INTRODUCTION

The performance of sequential computing is reaching its limits. The rate of increase of instruction level parallelism in superscalar architectures is reducing each year, and the number of pipeline stages became so high that it is difficult to break the execution in more steps to increase the operation frequency (SHALF; DOSANJH; MORRISON, 2011). Additionally, in the past few years, the power consumption of the processors started to play a big role on the design of new high performance architectures. Aggressive instruction speculation, out-of-order execution, as well as deep pipelines, require high amounts of energy. Therefore, high performance architectures focus on thread level parallelism, and are based on several processor cores executing in parallel. This makes the number of cores more relevant than the individual performance of each core.

As the industry relies on parallelism, the increase of the number of cores in multicore architectures is one of the adopted solutions. This makes the memory wall problem (HEN-NESSY; PATTERSON, 2007) more relevant, since more bandwidth between the cores and the main memory is required. Currently, memory hierarchies with several levels of cache memories are employed to overcome this issue. However, with the upcoming increase of the number of cores, it is expected an aggravation of the memory wall problem. Therefore, novel solutions are required to allow the performance to scale (COTEUS et al., 2011; TORRELLAS, 2009).

One of the main concerns regarding multicore architectures is the communication between threads (ZHAI et al., 2011). Communication implies in data movement among the cores, leading to performance loss and energy consumption (BORKAR; CHIEN, 2011). Therefore, it is important to research and develop mechanisms to optimize the communication. Some studies focus on hardware, suggesting new interconnections and network topologies (STEVENSON; CONN, 2011; AJIMA; SUMIMOTO; SHIMIZU, 2009), while others focus on software, to improve data locality (RIBEIRO et al., 2010). As the scope of the problem is wide, there are several ways to deal with it.

### **1.1** Scope of this research

In multicores architectures, some levels of the memory hierarchy are shared by more than one core, which causes the communication latency among the cores to be different. Additionally, in some architectures, there is more than one processor, in which each processor has several cores. This increases the number of levels of the memory hierarchy, since cores of the same processor communicate faster than cores of different processors. Future interconnections introduced by *Network-on-Chip* (NoC) (DE MICHELI; BENINI, 2006; FREITAS et al., 2007) are expected to increase the difference in the communication latencies among the cores. Several levels of memory hierarchy also impose a high over-

head on cache coherence protocols (CHISHTI; POWELL; VIJAYKUMAR, 2005), which are responsible to keep the data integrity among all the cache memories.

Thread mapping helps to improve performance by mapping the threads on cores according to some policy, such that the usage of the resources is optimized. By mapping the threads considering the amount of communication between them, the communication latency is reduced, since threads that communicate are mapped to nearby cores on the memory hierarchy. The overhead of cache coherence protocols is also reduced, because the number of cache-to-cache and invalidation transactions is thereby decreased (ALVES; FREITAS; NAVAUX, 2009).

The level of difficulty to map the threads depends on the parallel programming paradigm. When the paradigm is messaging passing (RODRIGUES et al., 2009), detecting the communication pattern is rather straightforward, and is accomplished by monitoring the origin and destination fields for each message. However, when the paradigm is shared memory, the communication between the threads is implicit and it happens every time a thread reads or writes data that has been previously accessed by other threads. Therefore, mapping shared memory based applications is much more challenging. Another factor that influences on the difficulty is if the mapping is made statically or dynamically. In static thread mapping, the information on the communication pattern is gathered by profiling the application in previous executions using controlled environments such as simulators. In dynamic thread mapping, the information on the communication pattern must be gathered while running the application, a much more difficult task.

It is important to take into account the viability of the proposed methods. For instance, architectures such as of the graphic processing units (GPU) provide high performance, but requires complex software (LIU; ZHANG; SHEN, 2009). Some mechanisms present high overhead steps of profiling, discouraging their usage (WANG; O'BOYLE, 2009). Other mechanisms require modifications on the source code of the applications, increasing the complexity of the programming (IBRAHIM, 2010). Such mechanisms also reduces the portability of the applications, since the modifications usually depend on the target architecture. Furthermore, relying on programmers is not desirable, because inexperienced programmers may insert wrong annotations.

#### **1.2** Proposal

In this master thesis, we propose two different mechanisms to dynamically detect the communication pattern among the threads of shared memory based applications. Both mechanisms allow the thread mapping to be performed dynamically by the operating system and do not require simulation or any changes to the source code of the applications. Our first proposed mechanism makes use of cache coherence protocols. It is based on two fundamental ideas. First, a cache line that is shared by more than one cache indicates that more than one core is accessing the same memory location, which represents a communication. Second, cache coherence protocols keep track of shared cache lines. By adding some minimal extra hardware to the original cache coherence system, we allow the hardware to count the number of memory accesses to shared cache lines.

Our second proposed mechanism to find the communication pattern consists of looking at the most recently accessed pages by each core. This was done by checking the content of the *Translation Lookaside Buffer (TLB)*, which is responsible to perform the translation of virtual addresses to physical addresses and is present in most architectures that support virtual memory. As there is one TLB per core, the communication pattern could be detected by searching all TLBs for matching entries. We developed mechanisms for both software-managed and hardware-managed TLBs, covering most of the current architectures.

## **1.3** Organization of the text

The text is organized as follows. Chapter 2 explains how thread mapping works and presents some related work. Chapter 3 shows our proposed mechanisms for dynamic detection of the communication pattern. Chapter 4 shows the methodology we adopted to evaluate our proposals. Chapter 5 contains the results of the experiments. Finally, Chapter 6 draws our conclusions and future work.

# 2 THREAD MAPPING

The basic goal of thread mapping is to optimize the usage of the available resources. When dealing with threads, the parallel programming paradigm used is shared memory, in which all the communication among the threads is performed by accesses to the memory. Therefore, memory is the main resource to be considered when mapping the threads of applications based on this paradigm. As multi-core architectures have memory hierarchies with several levels of cache memories, some cache lines may be present in more than one cache. These cache lines are said to be replicated, or shared. Keeping data integrity among all the caches is responsibility of cache coherence protocols (STALLINGS, 2006). To do this, cache coherence protocols store information about the state of each cache line, such as if the line is shared or modified. They also send messages through the interconnections to the caches when some data is requested or modified.

In snoop protocols (EGGERS; KATZ, 1989), the information about the state is kept by the caches and messages are exchanged between them. In directory protocols (AGAR-WAL et al., 1988), the directory is responsible to keep this information and to send the messages to the caches. However, in both snoop and directory protocols, the overhead generated by the messages sent through the interconnections is high. For instance, a common situation in shared-memory programs is to have one thread writing to an area of memory and another reading from the same area. If the cache coherence protocol is based on invalidation, such as MESI (STALLINGS, 2006), and the reader and writer do not share a cache, an invalidation message would be sent to the reader every time the writer writes the data. As a result, the reader would always receive a cache miss when reading, thereby requiring more coherence traffic on the interconnections, since the cache of the reader would have to retrieve the data from the cache of the writer on every access.

One way to reduce this overhead is by mapping the threads that communicate on cores that are close to each other in the memory hierarchy. In the previous example, no coherence traffic would be generated if the writer and reader shared a cache. It is important to note that write operations impact more on performance than read operations, as all writes to shared cache lines invalidate the corresponding lines on the other caches. Furthermore, memory accesses to data are more relevant than instruction fetches when mapping the threads. The reason is that write operations to data occur frequently, while write operations to instructions only occur when the operating system loads a program into memory.

As mentioned before, thread mapping reduces the cache misses generated by the invalidation messages. This type of cache miss is called invalidation miss. Other side effects are the reduction of capacity misses and replication misses. Capacity misses are cache misses that happen when data is accessed for the first time and was not already fetched from memory. In a shared cache, threads compete for cache lines and evict cache lines from each other (ZHOU; CHEN; ZHENG, 2009). By mapping threads that communicate to shared caches, this competition is reduced. Replication misses are cache misses that happen due to uncontrolled cache line replication. As stated in CHISHTI; POWELL; VI-JAYKUMAR (2005), uncontrolled replication leads to a virtual reduction of the effective size of the caches, as some of their space would be used to store the same cache lines. By mapping threads that communicate to cores that share a cache, the space wasted with replicated cache lines is minimized, leading to a reduction of the cache misses.

The mapping can also be applied to processes. Processes, contrary to threads, do not share memory among themselves by default. In order to communicate, the processes send and receive messages to each other. This parallel programming paradigm is called message passing (SEBESTA, 2009). The discovery of the communication pattern of message passing based applications is straightforward compared to shared memory based applications. This happens because the messages keep fields that explicitly identify the source and destination. We discuss some related work about message passing in Sections 2.2.4 and 2.3.3.

Regarding architectures with non-uniform memory access characteristics (NUMA), besides thread mapping, data mapping is also important (TERBOVEN et al., 2008; RIBEIRO et al., 2009). The data mapping is required in NUMA because the access latencies to the memory banks are different among the cores. The cores are divided into groups, in which each group is a NUMA node. Each NUMA node has its own memory banks. When a core access memory that is located on the same NUMA node, we call this type of access local access. When the core access memory located on other NUMA node, we call the access remote access. We discuss some related work about data mappings for NUMA architectures in Section 2.3.2.

The mapping techniques, in general, can be divided in two main groups: static and dynamic. Static mappings are based on information gathered before the execution of the applications. They require previous analysis of the behavior of the applications to generate a profile that will guide the mapping. This step to generate a profile usually is a time consuming task, requiring simulation or other tools, and relies on information provided by programmers and compilers. On the other hand, dynamic mappings are usually lightweight and do not require previous profiling of the applications. We discuss some related work about static and dynamic mapping in Sections 2.2 and 2.3, respectively.

### 2.1 Properties of a thread mapping mechanism

To be suitable for a real-world environment, a mechanism to find the communication pattern between threads should present some properties according to CRUZ; DIENER; NAVAUX (2012) and DIENER et al. (2010). Some of them are:

#### Detect communication pattern and dynamic behavior during execution - Many

previous approaches rely on finding the communication pattern in a phase before the actual execution of the workload, for example by using simulation or binary instrumentation. This is very time-consuming and potentially takes a lot of storage space to store intermediate data, such as memory traces. Furthermore, some applications change their behavior and the communication pattern during the execution. Therefore, the mechanism should be able to detect changes dynamically and thereby make dynamic mapping possible. Many previous approaches analyze the application over the whole execution time and provide a static mapping for the application. This leads to wrong results when the application exhibits dynamic behavior.

- Low impact on performance The mechanism should have a very low overhead in order not to interfere with the execution of the application. Some previous approaches permute the mapping of threads to cores periodically to observe changes in the cache statistics. As a remapping of threads has an overhead in terms of an increase of cache misses, this leads a noticeable decrease of performance and hence is less efficient.

- **Provide an accurate communication pattern –** The detection of the communication pattern should be as accurate as possible to allow a beneficial mapping to be performed. In the case of shared memory applications, this means that the observation should happen as directly as possible by monitoring the memory accesses. Approaches that use hardware counters, for example, only observe the applications behavior indirectly and provide a less accurate view of the communication between the threads.

- Avoid the false communication problem False communication can be temporal, as when two threads access the same address, but at different times during the execution. Another scenario of false communication is the classical false sharing problem, which is a spatial false communication, in which a cache line is present in more than one cache; however, the cores are accessing different addresses inside the cache line. Both scenarios should not be considered as communication.

- Independence from the implementation of the application To provide benefits to a wide number of applications, the mechanism should be transparent to the programmer and user and make as few assumptions about the applications as possible. This has two consequences. First, the mechanism should not depend on a particular parallelization API, such as OpenMP and Pthreads. Second, it should not require the programmer to modify the source code or link to additional libraries.

### 2.2 Static thread mapping

In this section, we discuss some related work about static mapping. To statically map an application, it must be executed inside controlled environments so that information about the communication pattern can be gathered. This information is used in future executions of the application to map their threads to the cores. There are three main types of controlled environments used to monitor the memory accesses of the applications: emulation, simulation and dynamic binary analysis (DBA).

Emulators are programs that implement some particular instruction set (ISA) entirely by software. They are able to run executable files for the targeted ISA, allowing them to be executed in any machine. Emulators focus on performance and only guarantee that the program output for a given input will be the same of the real machine. Some examples of emulators are Qemu (BELLARD, 2005) and Bochs (SHWARTSMAN; MIHOCKA, 2008). Qemu uses a technique called dynamic binary recompilation, which consists of translating the executable of the the targeted ISA to a binary code compatible to the host machine during runtime. Bochs is based on interpretation and hence is much slower than Qemu. To minimize the high overhead imposed by interpretation, Bochs implements a cache of decoded instructions. The first time an instruction is executed, the operands and the operation are stored in the cache. The future accesses to the same instruction use the information from the decoded cache.

Simulators are also programs that implement some particular instruction set (ISA) entirely by software. They are able to run executable files for the targeted ISA, allowing them to be executed in any machine. Simulators, besides generating the same output of the real machine, also focus on implementing the virtual machine so that the behavior will be similar to the real machine. One example of simulator is Simics (MAGNUSSON et al., 2002). Simics is a full system simulator that achieves a good trade-off between realistic simulation and performance. By doing so, Simics allows real benchmarks to be simulated with a reasonable accuracy compared to a real machine. It allows the simulation of latencies in some components, which makes it possible to simulate the memory hierarchy and pipeline stalls.

Dynamic binary analysis tools enable instrumentation of executable files so that their behavior can be analyzed while running the programs. Some examples of dynamic binary analysis tools are Valgrind (NETHERCOTE; SEWARD, 2007) and Pin (BACH et al., 2010). The feature of Valgrind that is most related to our work is the BBV generator. A Basic Block is a sequence of instructions that contains one entry and one exit points. A Basic Block Vector (BBV) is the set of all Basic Blocks of an application. The tools outputs the BBV of an application in a format compatible with the Simpoint simulator (HAMERLY et al., 2005). Simpoint performs simulation in small steps from different phases of the application. Then, it estimates the global behavior of the application by analyzing the BBV and the results given from each phase. This approach is based on the concept that the behavior of the applications are cyclic.

Valgrind also supports the instrumentation of multi-threaded applications. However, the thread execution is serialized, thereby the behavior of parallel applications is totally different from the original, as only one thread will be executing at a time. On the other hand, Pin does not impose serialization on multi-threaded applications. It provides synchronization primitives, such as locks, so that race conditions can be prevented. The synchronization primitives present high overhead and should be used with precaution. Private storage for each thread is provided by the thread local storage (TLS), which represents an efficient method to store data that must be unique to each thread. Furthermore, Pin has tools to help the analysis of programs based on the most used APIs, such as OpenMP (OPENMP, 2008) and Threading Building Blocks (REINDERS, 2007).

The tools presented in the previous paragraphs are controlled environments that can be used to detect the communication patterns of parallel applications. They demand a lot of computational resources, drastically increasing the overhead of current thread mapping approaches. In the rest of this section, we present some related work about thread mapping that use these controlled environments to gather information to map the threads of parallel applications.

#### 2.2.1 Static thread mapping based on simulation

In BARROW-WILLIAMS; FENSCH; MOORE (2009), a technique to collect the communication pattern between the threads of parallel applications based on shared memory is evaluated. Their method consists of two main steps: generation of memory access traces and the analyses of the traces. To perform the first step, they instrumented Simics to register all the memory accesses in files. The simulated ISA was the *x86*. To obtain more realistic results, a memory hierarchy was also simulated with Simics while generating the traces. The memory hierarchy had private L1 caches and one large shared L2 cache using

a coherence protocol. In the second step, the memory traces are analyzed to determine the communication pattern of the applications.

To consider an access to the memory as communication between the threads, the access should fulfill three criteria. The first one is that more than one thread must access the same address. The second criteria is that when one thread performs several consecutive writes to the same address, only the last access represents a communication. The third is that when one thread performs several consecutive reads to the same address, only the first access represents a communication. These last two criteria are necessary to ignore the memory access that occurred due to register number constraints. This happens when several consecutive operations must be performed in one variable, but the architecture does not provide enough registers to hold all the involved variables.

The authors categorize the memory accesses in three types: read-only, migratory and producer-consumer. Read-only accesses are the ones that only read accesses are performed after the initialization of the variable. Migratory accesses are represented by atomic read-write operations. Producer-consumer is a pattern that one data is written by one thread, the producer, and then is read by another thread, the consumer. However, as few memory accesses fulfill this definition, the authors used a less strict rule to consider a memory access as a producer-consumer. They extended the definition to allow an arbitrary number of producers, and to consider a thread as a consumer when the it reads the data for at least 50% of the performed writes.

The technique was evaluated using the *Splash-2* (WOO et al., 1995) and *Parsec* (BI-ENIA et al., 2008) benchmarks. These benchmarks were chosen because they cover different targets: *Splash-2* is more suitable to evaluate clusters, while *Parsec* is focused in multicore architectures. The analysis of the results showed that 1.5% of the read accesses represent communication. For the write accesses, 4.2% and 20.4%, respectively for *Splash-2* and *Parsec*, represent communication. As the main goal of the work was just to characterize the communication pattern, the authors did not ran any performance tests using the collected data.

The work described in DIENER et al. (2010) also uses Simics to discover the communication pattern of parallel applications. However, the authors used the collected information to map the threads to cores according to the amount of communication. They developed two algorithms to map the threads. The first one tries every possible mapping and selects the one that maximizes the amount communication between the threads. The problem of this approach is that the time complexity is exponential, hence it is viable only for small number of threads. The second algorithm is a greedy heuristic and presents polynomial time complexity. The applications were also executed using the original scheduling policy of the operating system.

The authors evaluated their proposal by mapping a subset of the *Splash-2* and *Parsec* benchmarks on the Intel Nehalem architecture. Performance was improved by up to 45% when compared to the native scheduler of the Linux operating system. Thread migration imposed by the Linux scheduler requires context switches, which increases the number of cache misses and leads to performance degradation when transferring the data to other caches (MOGUL; BORG, 1991). In CRUZ; ALVES; NAVAUX (2010), it is shown that, in some situations, thread migration can harm the performance more than any random thread mapping.

#### 2.2.2 Static thread mapping based on dynamic binary analysis

The work presented in BIENIA; KUMAR; LI (2008) uses the Pin tool to collect information about the applications. They analyze the communication pattern and the distribution of the instructions of the applications by their type. For the communication pattern, they evaluate the amount of memory shared by the threads, separating read-only data and data that suffered rewrites. Furthermore, they counted the number of accesses to regions of memory that are shared, both write and read accesses. The working set (TANEN-BAUM, 2007) of the applications were also taken into account. The size of the working set was estimated by making use of the cache miss rate, since the amount of cache misses is usually proportional to the size of the working set.

The results show that, even for small cache memories of 1mb, the miss rate is lower than 1.25% for the Parsec benchmark. To decrease the cache miss to almost 0%, the cache size was set to 128mb. This indicates that, despite the cache miss rate being proportional to the size of the working set, the scale is not direct. Another interesting result of the work was the ratio of write accesses to shared cache lines. This is an important measure because write operations performed to shared cache lines generate invalidation or update messages by cache coherence protocols. With the size of current last level caches, which are around 32mb, less than 6% of the memory accesses result in writes to shared cache lines. This number rises to around 7.5% when considering a 128mb cache size. As the goal of the paper was just to analyze the behavior of the applications, no performance tests were realized. However, these results suggest that obtaining performance improvements with thread mapping is challenging, since the amount of private data overwhelms the amount of shared data in current parallel applications.

#### 2.2.3 Static thread mapping based on hardware counters

Hardware counters present on current architectures may also be used to guide the static thread mapping. In OTT et al. (2008), hardware counters were employed in order to measure the quality of a specific thread mapping. The communication among the threads of the applications was not considered, since hardware counters present on current architectures do not provide this kind of information. Instead, they used the million instructions per second (MIPS) as metric. This metric indirectly estimates the quality of the mapping, since it is expected that the value of the MIPS to be higher for better mappings. Each application was executed with every possible mapping, and the one that outputs the highest MIPS was chosen.

To evaluate their proposal, they used their mechanism to map applications from the *Spec OMP* benchmark (SAITO et al., 2002). The authors claim that their method was able to find the best mapping for all the applications. However, they did not explain how they obtained the best mapping. Furthermore, the results are not conclusive and the manner they were presented lacks organization, which makes them difficult to be interpreted. Nevertheless, it is interesting that they used hardware counters, which requires less computational resources than simulation and dynamic binary analysis and could be implemented directly on the operating system scheduler.

#### 2.2.4 Static process mapping applied to message passing based applications

As already mentioned, the detection of the communication pattern of message passing based applications is straightforward compared to shared memory based applications. In RODRIGUES et al. (2009), a technique to statically map parallel applications based on the

Message Passing Interface (MPI) (MPI, 2009) is proposed. To detect the communication pattern, the authors created wrappers to the MPI primitives that monitors the source and destination fields of each message, as well as the amount of exchanged data between them. With these information, they generate a complete graph in which the vertices represent the processes and the edges the amount of communication.

To map the processes on the processing units they used a tool called *Scotch* (SCOTCH, 2010). *Scotch* requires as input two graphs: one to describe the application and other to describe the machine. The graph of the application is generated as explained in the above paragraph. In the graph of the machine, the vertices represent the processing units and the edges the bandwidth of the link that connects them, if there is one. *Scotch* maps the application graph to the machine graph by applying heuristic algorithms, most of them based on graph partitioning. The generated mapping tries to minimize the overhead imposed by the communication while keeping the load balancing. The bandwidth of the links of the target machines were measured using a ping-pong application, which just sends messages between all the processing units and reports the time took to transmit them.

They used the weather forecast program BRAMS (BRAMS, 2009) to evaluate their proposal. They obtained up to 9% of performance improvement, and a reduction of 20% on the time spent waiting for messages. The mapping also resulted in a reduction in the network traffic between the nodes of the cluster. One weak point of this work is that the only metric tested was the amount of exchanged data. As stated in CHEN et al. (2006), this metric is appropriate for applications in which the size of the messages far surpass the number of messages. On the other hand, if the message sizes are too small, the network latency dominates the transmission time, which makes the number of messages metric more suitable than the amount of data.

### 2.3 Dynamic thread mapping

In this section, we discuss some related work about dynamic mapping.

#### 2.3.1 Dynamic thread mapping using hardware counters

The works described at TAM; AZIMI; STUMM (2007a,b); AZIMI et al. (2009) show that hardware performance counters already present in current processors may be used to dynamically map parallel applications. They schedule threads by making use of hardware counters present in the Power5 processor. Four main steps are performed: monitoring, discovery of the communication pattern, thread clustering and migration. The monitoring step consists of checking the hardware counter that stores the amount of cycles that the core was stalled due to accesses to remote cache memories. When the stall time exceeds a certain threshold, the mapping mechanism is enabled. This threshold is employed to reduce the overhead.

When the mapping mechanism is enabled, the first procedure is to detect the communication pattern. This was accomplished by reading a hardware counter of the Power5 that stores the latest address that resulted in a remote cache access. A list of addresses is kept for each core. After some time, when the size of the lists are large enough, the thread clustering step is initiated. If the same address is present in more than one list, that means that this address is shared between the corresponding cores and is used for communication. Therefore, the thread clustering step consists of searching the lists of addresses of each core for matches. Finally, the threads migrate to cores so that the number of remote access is reduced.

Performance was increased by up to 7% and the number of memory accesses to remote cache memories was reduced by up to 70%. This work has three main disadvantages. The first is that the steps of discovering the communication pattern present high overhead, because it requires too much traps to the kernel. The thread clustering step is also expensive, but as it is not performed so frequently, it does not have a high impact. The second disadvantage is a result of the first one. As two of the steps have high overhead, the mapping mechanism is enabled occasionally, which reduces the accuracy of the results. The third disadvantage is that only the remote cache accesses are monitored, hence it is not possible to detect communication among all the threads.

In BROQUEDIS et al. (2010), a library called ForestGOMP is introduced. This library integrates into the OpenMP (OPENMP, 2008) runtime environment and gathers information about the different parallel sections of the applications from hardware performance counters. The library generates data and thread mappings for the regions of the application. As the library performs data mappings, it focus on NUMA architectures. The library tries to keep the threads that communicate nearby according to the memory hierarchy, as well as to place the memory pages in NUMA nodes close to the cores that access the page. As stated in TERBOVEN et al. (2008), Linux first-touch policy consists of mapping a page to the NUMA node of the core that first access the page, and is not efficient due to the different behavior of parallel applications in different phases of the program. ForesGOMP adds a next-touch policy, in which the pages migrate to the NUMA node of the next core that access the page. The library also supports the migration of individual pages.

They improved performance by up to 11.6% using the NAS parallel benchmarks. They also evaluated the performance with a benchmark called *Stream* (STREAM, 2011), which measures the memory bandwidth, obtaining up to 80% of improvement. This work has two disadvantages. The first one is that the hardware counters they used to guide the thread and data mapping only indirectly estimate the communication patterns. The second major problem is that their work is limited to OpenMP based applications. Applications based on other APIs, such as Intel TBB or Posix Threads, are not able to benefit from their library.

#### 2.3.2 Dynamic data mapping applied to NUMA machines

The ForestGOMP library (BROQUEDIS et al., 2010), introduced on the previous section (Section 2.3.1), already performs data mappings for NUMA machines. Another interesting work is described at AWASTHI et al. (2010). They have developed page migration mechanisms that uses the load balancing between the memory controllers and the rowbuffer hit rate as main metrics. The reason for optimizing the load balancing is straightforward, as it will cause a better distribution of the memory traffic across the NUMA nodes. Optimizing the row-buffer hit rates, on the other hand, is very interesting. If you have high row-buffer hit rates, it suggests that the same data is being re-used. It is not an accurate information because access to different pages may also result in a row-buffer hit, but, at least, a miss in the row-buffer only happens if a different page is accessed. As a result, the row-buffer hit rate indirectly estimates the amount of shared pages between the cores that are accessing a NUMA node.

Two page migrations mechanisms were developed. The first is called Adaptive First-Touch and consists of gathering statistics of the memory controller to map the data of the

| Method                                        | Detect commu-<br>nication pattern<br>and dynamic<br>behavior during<br>execution | Impact on per-<br>formance | Accuracy of the<br>communication<br>pattern | Avoid the false<br>communication<br>problem | Independent<br>from the imple-<br>mentation of the<br>application |

|-----------------------------------------------|----------------------------------------------------------------------------------|----------------------------|---------------------------------------------|---------------------------------------------|-------------------------------------------------------------------|

| Static, using simulation                      | No                                                                               | High                       | High                                        | Yes                                         | No                                                                |

| Static, using<br>DBA                          | No                                                                               | High                       | High                                        | Yes                                         | Yes                                                               |

| Static, using<br>hardware<br>counters         | No                                                                               | Low                        | Low                                         | No                                          | Yes                                                               |

| Dynamic,<br>using hard-<br>ware coun-<br>ters | Yes                                                                              | Low                        | Low                                         | No                                          | Yes                                                               |

Table 2.1: Summary of the characteristics of current thread mapping mechanisms.

application in future executions. However, this mechanism fails if the behavior changes among the different phases of the application. The second mechanism uses the same information, but allows dynamic page migration during the execution of the application. In their heuristic, a page must migrate when the row-buffer hit rate drops by 10%. They select the destination NUMA node considering the difference of the access latency between the source and destination NUMA nodes, as well as the row-buffer and the load of the destination memory controller.

Their mechanisms were implemented in the Simics simulator, leading to a performance improvement of up to 35%. The major problem of this work is that the information about the communication pattern between the threads, as well as which data each thread is using, is unreliable, since it is based only in the row-buffer hit rate. The page to be migrated is randomly chosen, and may lead to an increase on the number of remote accesses. Additionally, threads that access the same memory pages may be executed on different NUMA nodes, since they do not map threads that communicate on the same node. This also leads to an increase of the number of remote accesses.

#### 2.3.3 Dynamic process mapping applied to message passing based applications

In SONNEK et al. (2010), virtual machines running on clusters are migrated among the different nodes considering the amount of communication between them. They detect the communication between the virtual machines by monitoring the source and destination fields of the packets sent on the network. By dynamic migrating the virtual machines to nearby nodes of the cluster, they improved performance by up to 42% and reduced the network communication cost by up to 85%.

### 2.4 Summary of the state-of-art

In this chapter, we presented the state-of-art related to mapping techniques. Thread mapping, data mapping and process mapping mechanisms were evaluated. One first conclusion is that process mapping of parallel applications based on message passing are rather straightforward, at least from the point of view of the computer architecture. As the communication pattern is easily discovered by monitoring the source and destination of

the messages, the problem is reduced to determine which core will execute each process. This is more of a mathematical and combinatorial optimization problem than a computer architecture problem. On the other hand, thread mapping of parallel applications based on shared memory imposes a real challenge on computer architecture, since it is very difficult to accurately detect the communication pattern without requiring time consuming tasks such as profiling.

Table 2.1 summarizes the characteristics of current thread mapping mechanisms. We can categorize current thread mapping mechanisms in two groups: the mechanisms that impose high overhead, but generate an accurate communication pattern, and the mechanisms that are light-weight, but rely on indirect and unreliable information about the communication. To our knowledge, there is no solution that was able to accurately detect the communication pattern of shared memory based parallel applications with a low overhead. Our goal is to fulfill this gap. We developed mechanisms that dynamically generate accurate communication patterns with a low overhead for parallel applications based on shared memory. Our mechanisms also allow the thread mapping to be performed dynamically by the operating system during the execution of the applications. Furthermore, they do not depend on any particular parallel programming library or any kind of modifications to the source code of the applications.

# **3 PROPOSED METHODS FOR DYNAMIC DETECTION OF THE COMMUNICATION PATTERN**

In this chapter, we explain our proposed mechanisms for dynamic detection of the communication pattern. The proposals can be classified in two main categories: cache coherence based and TLB based. The communication can be analyzed by grouping different number of threads. To calculate the amount of communication between groups of threads of any size, the time and space complexity raises exponentially. Therefore, the communication was evaluated only between pairs of threads, generating a communication matrix. Although this may decrease the accuracy of the results, it reduces the complexity to  $\Theta(N^2)$ , where N is the number of threads, and allows a faster processing of the information.

### 3.1 Exploiting Cache Coherence Protocols

Cache coherence protocols are responsible for keeping data integrity in architectures where more than one cache memory is present, as is common in multicore and multiprocessor environments. These protocols keep information about whether a line is private or shared between two or more caches. This can be exploited in order to estimate the amount of communication between the threads, since an access to a line shared by two or more caches represents a communication. Small modifications to the protocols and the hardware are required to identify communication patterns. We used the MESI protocol (STALLINGS, 2006) as base for our cache coherence based mechanisms, and they can be adapted to work with any protocol, such as MOESI.

In MESI based protocols, an invalidation message is sent when a write is performed in a shared or invalid cache line. However, no message is sent when a read is performed in a shared cache line. Hence, we detect the communication when the cache lines are invalidated. Nevertheless, read transactions are considered when an invalidation message arrives, because cache lines are invalidated regardless of their state. This decision was taken considering that write operations have a greater impact on performance than read operations (CHISHTI; POWELL; VIJAYKUMAR, 2005).

There are two main types of cache coherence protocols: snoop and directory. We propose modifications to both snoop and directory protocols in the rest of the section. The examples and figures were based on a machine which consists of four cores.

#### 3.1.1 Snoop Protocols

In this section, we explain how to detect the communication pattern in snoop protocols. In these protocols, each cache is responsible for keeping the state of its cache lines.

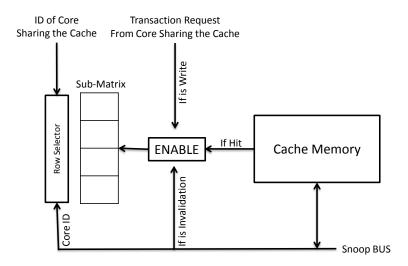

Figure 3.1: Snoop based mechanism for private caches.

Since snoop protocols usually do not keep any information about which caches are sharing each line, the coherence messages are broadcasted to all caches (EGGERS; KATZ, 1989). Snoop protocols can be used with caches that are private to one core and with caches that are shared between two or more cores. We propose different mechanisms for private and shared caches.

#### 3.1.1.1 Mechanism for Private Caches

Our first approach to detect the communication pattern in snoop protocols is appropriate for private cache memories. We add a matrix to each cache to store the communication corresponding to the core that is connected to the cache, therefore the matrix consists of only one column. The number of rows of this matrix is equal to the total number of cores in the system. From now on, we will call this matrix *sub-matrix*, since it is part of the communication matrix. The procedure to obtain the communication matrix is explained in Section 3.1.3.1. In order to identify which cores are communicating, the id of the core that sent the coherence message is also required. To provide this information, the id of the core must be sent along with the message. This scheme is not suitable for shared caches, since we do not know which of the cores that share the cache have accessed each line.

Figure 3.1 shows how the mechanism works. Table 3.1 presents some examples, considering that all transactions happens on the same cache line. In the Table, the letters M, E, S and I represent the coherence state. When a write is performed in a shared cache line, as in Example 1, we send the invalidation message along with the id of the core that sent the message in the snoop bus. Those caches that invalidate a line in response to this message increment their sub-matrix by one in the cell whose row is the core id from the snoop bus. The same happens when a write is performed in an invalid cache line, as in Example 2. Example 3 illustrates how read transactions are taken into account when an invalidation arrives.

The space required to store each sub-matrix is  $P \cdot C$ , where P is the number of processing cores of the machine and C is the size of each cell of the sub-matrix in bytes. As there are P caches, the total space used to store the matrices is  $P^2 \cdot C$  bytes.

| Ex. | Core 0<br>Cache 0 | Core 1<br>Cache 1 | Core 2<br>Cache 2 | Core 3<br>Cache 3 | Action                                                                                   |

|-----|-------------------|-------------------|-------------------|-------------------|------------------------------------------------------------------------------------------|

| 1   | S                 | Ι                 | S                 | S                 | Core 0 Writes<br>Cache 0 sends invalidation                                              |

|     | М                 | Ι                 | Ι                 | Ι                 | Cache 2 updates its sub-matrix in cell 0-0<br>Cache 3 updates its sub-matrix in cell 0-0 |

| 2   | Ι                 | Е                 | Ι                 | Ι                 | Core 0 Writes<br>Cache 0 sends invalidation                                              |

|     | М                 | Ι                 | Ι                 | Ι                 | Cache 1 updates its sub-matrix in cell 0-0                                               |

|     | Ι                 | Ι                 | Ι                 | Ι                 | Core 0 Reads                                                                             |

|     | Е                 | Ι                 | Ι                 | Ι                 | Core 2 Reads                                                                             |

| 3   | S                 | Ι                 | S                 | Ι                 | Core 3 Writes<br>Cache 3 sends invalidation                                              |

|     | Ι                 | Ι                 | Ι                 | М                 | Cache 0 updates its sub-matrix in cell 3-0<br>Cache 2 updates its sub-matrix in cell 3-0 |

Table 3.1: Examples of the snoop based mechanism for private caches.

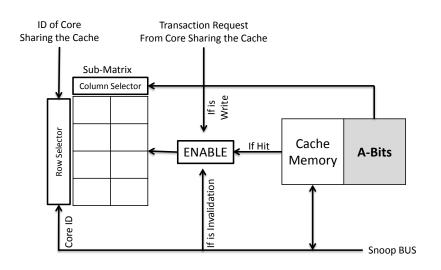

Figure 3.2: Snoop based mechanism for shared caches.

#### 3.1.1.2 Mechanism for Shared Caches

The previous protocol (Section 3.1.1.1) requires small modifications to the hardware, but only works for private caches. Its constraint is that it does not determine which core accessed a given cache line when there is more than one core sharing a cache. The protocol described in this section overcomes this issue, but requires more modifications to the original hardware.

To make it possible to use the mechanism with shared caches, we add one access bit (A-Bit) per core sharing a cache to every cache line. These access bits show which of the cores sharing a cache accessed a cache line. We add a sub-matrix to each cache to store the amount of communication correspoding to the cores that are sharing the cache. The number of rows of the sub-matrix is equal to the total number of cores, and the number of columns is equal to the number of cores sharing the cache.

Figure 3.2 shows how the mechanism works, considering that there are 2 cores sharing each cache. Therefore, 2 A-Bits are added to each cache line, and each sub-matrix has 2 columns. Table 3.2 present examples of the operation of the mechanism.  $C_x$  is the coherence state of cache x and  $A_x$  is the Access Bit corresponding to core x. It is important to

| Ex. | Core 0-1<br>Cache 0 |    | Core 2-3<br>Cache 1 |    |    | Action |                                                                                                              |

|-----|---------------------|----|---------------------|----|----|--------|--------------------------------------------------------------------------------------------------------------|

|     | C0                  | A0 | A1                  | C1 | A2 | A3     |                                                                                                              |

| 1   | Ι                   | 0  | 0                   | Ι  | 0  | 0      | Core 0 Reads<br>Cache 0 Sets A0                                                                              |

|     | Е                   | 1  | 0                   | Ι  | 0  | 0      |                                                                                                              |

| 2   | E                   | 1  | 0                   | Ι  | 0  | 0      | Core 1 Writes<br>Cache 0 Sets A1<br>Cache 0 updates its sub-matrix in cell 1-0                               |

|     | М                   | 1  | 1                   | Ι  | 0  | 0      |                                                                                                              |

| 3   | S                   | 1  | 0                   | S  | 0  | 1      | Core 1 Writes<br>Cache 0 Sets A1<br>Cache 0 updates its sub-matrix in cell 1-0<br>Cache 0 sends invalidation |

|     | М                   | 1  | 1                   | Ι  | 0  | 0      | Cache 1 updates its sub-matrix in cell 1-1                                                                   |

| 4   | S                   | 1  | 0                   | S  | 1  | 1      | Core 1 Writes<br>Cache 0 Sets A1<br>Cache 0 updates its sub-matrix in cell 1-0<br>Cache 0 sends invalidation |

|     | М                   | 1  | 1                   | Ι  | 0  | 0      | Cache 1 updates its sub-matrix in cells 1-0 and 1-1                                                          |

Table 3.2: Examples of the snoop based mechanism for shared caches.

mention that  $A_2$  and  $A_3$  point to columns 0 and 1 of the sub-matrix, since each sub-matrix only stores the communication corresponding to the cores that share them.

When a memory request arrives on the cache, the cache sets the A-Bit corresponding to the core that initiated the transaction on the requested cache line, as in Example 1. If a write hit occurs, the sub-matrix of the accessed cache is incremented in the cells whose row is the id of the core sharing the cache that initiated the transaction, and columns where the A-Bits are set (Example 2). This is done in order to detect the communication among the cores that share the cache. Besides, if the write hit happens in a shared cache line, an invalidation message is broadcasted along with the id of the core that initiated the transaction. Those caches that invalidate a line in response to this message increment their sub-matrix by one in the cells whose row is the core id from snoop bus, and columns where the A-Bits are set, as depicted in Example 3. It is important to note that, when more than 1 A-Bit is set, more than one cell is updated, as in Example 4. The invalidation is also broadcasted along with the id of the core when a write is performed in an invalid cache line.

The space required to store each sub-matrix is  $P \cdot S \cdot C$ , where P is the number of cores of the machine, S is the number of cores sharing the cache and C is the size of each cell of the sub-matrix in bytes. The overhead of the A-Bits for each cache is  $\frac{B \cdot S}{L}$  bits, where B is the size of the cache in bytes, L is the size of each cache line in bytes, and S is the number of cores sharing the cache. As there are  $\frac{P}{S}$  caches, the total space used to store the matrices is  $P^2 \cdot C$  bytes and the total space required for the A-Bits is  $\frac{B \cdot P}{L}$  bits. Since one byte contains 8 bits, the space complexity is  $P^2 \cdot C + \frac{B \cdot P}{8 \cdot L}$  bytes.

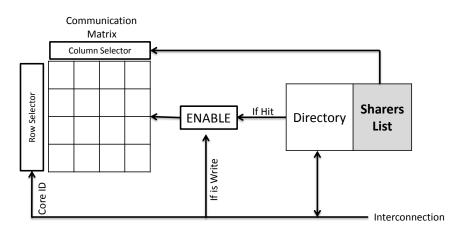

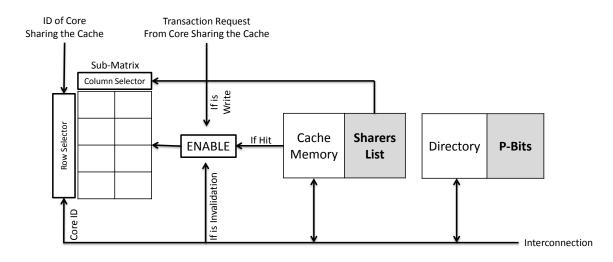

#### 3.1.2 Directory protocols

In this section, we explain how to detect the communication pattern using directory cache coherence protocols. In directory protocols, the directory stores the state of the cache lines of all caches and also keeps track of which caches contain each line. This can be seen in the Example 1 of Table 3.3. Coherence messages are sent only to the caches

Figure 3.3: Centralized directory based mechanism.

| Table 3.3: Examples of the cent | alized directory based mechanism. |

|---------------------------------|-----------------------------------|

|---------------------------------|-----------------------------------|

| Ex.   | Core 0  | Core 1  | Core 2  | Core 3  |           | Dire      | ctory |            | Action                                                                                                                                |

|-------|---------|---------|---------|---------|-----------|-----------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 2.1.4 | Cache 0 | Cache 1 | Cache 2 | Cache 3 | <b>S0</b> | <b>S1</b> | S2    | <b>S</b> 3 |                                                                                                                                       |

|       | Ι       | Ι       | Ι       | Ι       | 0         | 0         | 0     | 0          | Core 0 Reads<br>Directory sets Exclusive to Cache 0                                                                                   |

| 1     | Ε       | Ι       | Ι       | Ι       | 1         | 0         | 0     | 0          | Core 2 Reads<br>Directory sets Shared to Cache 2<br>Directory sets Shared to Cache 0                                                  |

|       | S       | Ι       | S       | Ι       | 1         | 0         | 1     | 0          |                                                                                                                                       |

| 2     | S       | Ι       | S       | Ι       | 1         | 0         | 1     | 0          | Core 1 Writes<br>Directory sends invalidation to Caches 0 and 2<br>Directory updates its sub-matrix in cells 1-0 and 1-2              |

|       | Ι       | М       | Ι       | Ι       | 0         | 1         | 0     | 0          |                                                                                                                                       |

| 3     | S       | S       | S       | Ι       | 1         | 1         | 1     | 0          | Core 1 Writes<br>Directory sends invalidation to Caches 0 and 2<br>Directory updates its communication matrix in cells<br>1-0 and 1-2 |

|       | Ι       | М       | Ι       | Ι       | 0         | 1         | 0     | 0          |                                                                                                                                       |

that contain the corresponding line, hence there is no need for broadcasts (AGARWAL et al., 1988). We will refer to the structure that keeps the caches that share a line as *sharers list*. Likewise, we will call the caches that are sharing a given cache line as a *sharer* of the line.