# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### **RODRIGO POSSAMAI BASTOS**

# Design of a Soft-Error Robust Microprocessor

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Dr. Ricardo Augusto da Luz Reis Advisor

## CIP - CATALOGAÇÃO NA PUBLICAÇÃO

#### Bastos, Rodrigo Possamai

Design of a Soft-Error Robust Microprocessor / Rodrigo Possamai Bastos – Porto Alegre: Programa de Pós-Graduação em Computação, 2006.

120 f.:il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação. Porto Alegre, BR – RS, 2006. Advisor: Ricardo Augusto da Luz Reis.

Fault-tolerant microprocessor.

Soft Errors.

SET. 4. SEU.

Integrated circuit design.

Reis, Ricardo Augusto da Luz.

Título.

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. José Carlos Ferraz Hennemann Vice-Reitor: Prof. Pedro Cezar Dutra Fonseca

Pró-Reitora de Pós-Graduação: Profa. Valquíria Linck Bassani Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do PPGC: Prof. Carlos Alberto Heuser

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

# **CONTENTS**

| LIST           | OF ABBREVIATIONS                                                      | 7  |

|----------------|-----------------------------------------------------------------------|----|

| LIST           | OF FIGURES                                                            | 9  |

| LIST           | OF TABLES                                                             | 11 |

| ABS            | TRACT                                                                 | 13 |

| RESU           | UMO                                                                   | 15 |

| 1 IN           | ITRODUCTION                                                           | 17 |

| 2 A            | RADIATION-INDUCED FAULT MODEL                                         | 21 |

| 2.1            | The Basic Radiation-Induced Effects on Integrated Circuits            | 21 |

| 2.1.1          | Occurrence Rate of Radiation-Induced Effects                          | 23 |

| 2.1.2          | Modeling of Radiation-Induced Effects                                 |    |

| 3 S            | OFT ERROR MITIGATION TECHNIQUES                                       | 31 |

| 3.1            | Triple Modular Redundancy (TMR)                                       | 32 |

| 3.1.1          | Area and Performance Analysis                                         |    |

| 3.2            | Time Redundancy (TR) + Code Word State Preserving (CWSP)              |    |

| 3.2.1          | Area Analysis                                                         |    |

| 3.2.2          | Performance Analysis                                                  | 37 |

| 4 D            | ESIGN OF A ROBUST MICROPROCESSOR                                      | 39 |

| 4.1            | The Target Microprocessor                                             | 40 |

|                | Fault-Tolerant Circuit Design                                         |    |

| 4.3            | Integrated Circuit Design Flow                                        | 45 |

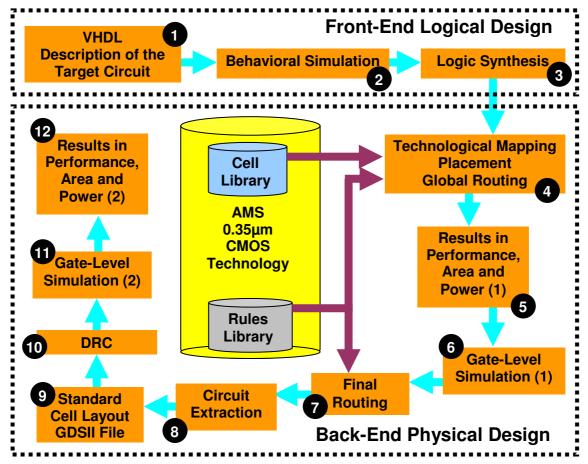

| 4.3.1          | The Developed Design Flow                                             | 46 |

| 4.4            | Front-End Logical Design                                              |    |

| 4.4.1          | Non-Protected Version or Susceptible to Direct and Indirect SEUs      |    |

| 4.4.2          | TMR Version or Robust to Direct SEUs                                  |    |

| 4.4.3          | TMR+TR+CWSP Version or Robust to Direct and Indirect SEUs             |    |

|                | Back-End Physical Design                                              |    |

|                | Some Fault-Tolerant Circuit Characteristics                           |    |

| 4.6.1          | The Maximum Width of SETs                                             |    |

| 4.6.2<br>4.6.3 | Multiple SEUs  SETs on the Elements of the Fault-Tolerance Mechanisms |    |

| 4.6.4          | Other Remarks                                                         |    |

| T.U.T          | Ouici iviiiuivi                                                       |    |

|                                                                                | ESIGN VERIFICATION SIMULATION OF A ROBUST OPROCESSOR                                                                                                                                                                                         | 69       |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5.1                                                                            | Types of Design Verification Simulation                                                                                                                                                                                                      | 70       |

| 5.1.1                                                                          | The Developed Types of Design Verification Simulations                                                                                                                                                                                       |          |

| 5.2                                                                            | Modeling of System for Simulation                                                                                                                                                                                                            |          |

| 5.2.1                                                                          | Functional Behavior of the Modeled System                                                                                                                                                                                                    |          |

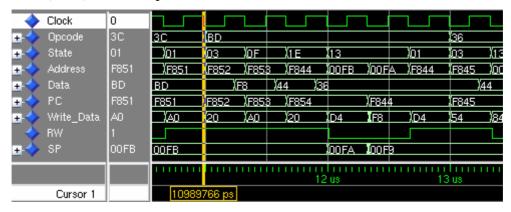

| 5.3                                                                            | Functional Testing by Simulation                                                                                                                                                                                                             |          |

| 5.3.1                                                                          | Benchmark Design                                                                                                                                                                                                                             |          |

| 5.3.2                                                                          | Benchmark Analysis                                                                                                                                                                                                                           |          |

| 5.3.3                                                                          | Benchmark Simulation Characteristics                                                                                                                                                                                                         | 76       |

| 5.3.4                                                                          | Required Processing Time                                                                                                                                                                                                                     | 76       |

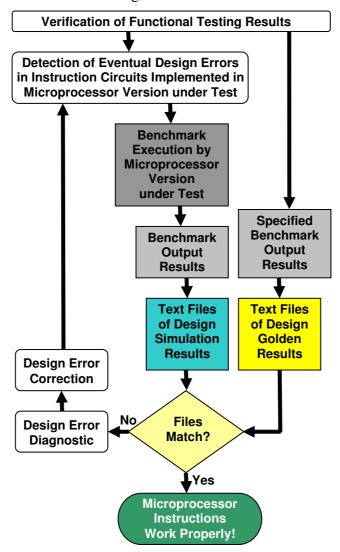

| 5.3.5                                                                          | Verification of Functional Testing Results                                                                                                                                                                                                   | 76       |

| 5.4                                                                            | Fault Injection by Simulation                                                                                                                                                                                                                | 78       |

| 5.4.1                                                                          | Instants of the SET Injection                                                                                                                                                                                                                | 79       |

| 5.4.2                                                                          | Widths of Injected SETs                                                                                                                                                                                                                      | 79       |

| 5.4.3                                                                          | Target Circuit Nodes for the SET Injection                                                                                                                                                                                                   | 80       |

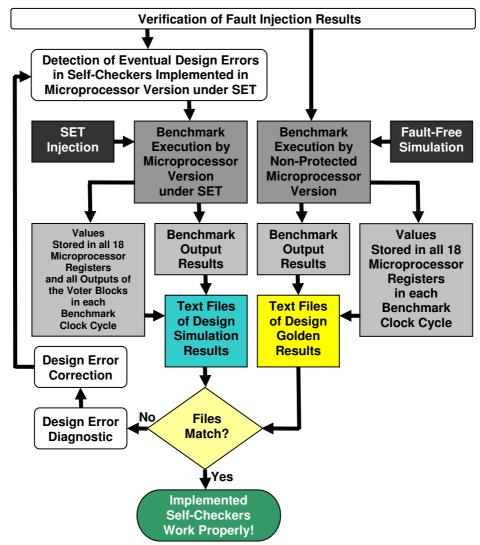

| 5.4.4                                                                          | Verification of Fault Injection Results                                                                                                                                                                                                      |          |

| 5.4.5                                                                          | Some Remarks about Fault Coverage of On-Line Self-Checkers                                                                                                                                                                                   | 84       |

| 6 D                                                                            | ESIGN RESULTS OF A ROBUST MICROPROCESSOR                                                                                                                                                                                                     | 85       |

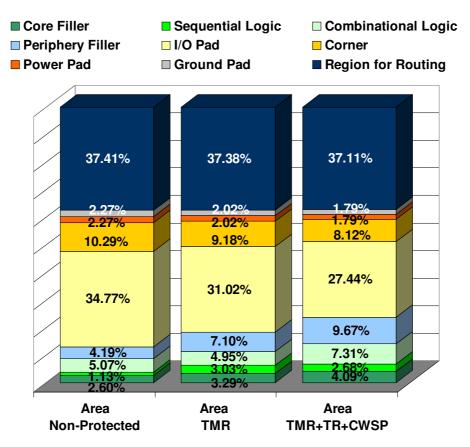

| 6.1                                                                            | Area Analysis                                                                                                                                                                                                                                | 85       |

| 6.1.1                                                                          | Floorplan Characteristics                                                                                                                                                                                                                    | 85       |

|                                                                                | 2 10 01 p 1 m 1 0 1 m 2 m 2 m 2 m 2 m 2 m 2 m 2 m 2 m 2 m                                                                                                                                                                                    |          |

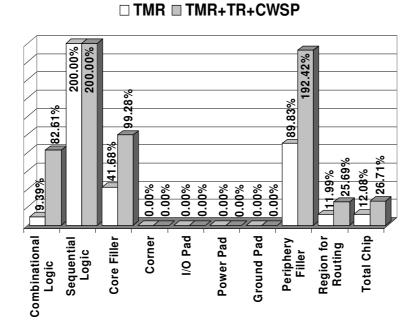

| 6.1.2                                                                          | About Standard Logic Cells and Other Types of Cells                                                                                                                                                                                          |          |

|                                                                                | <u> </u>                                                                                                                                                                                                                                     | 88       |

| 6.1.2                                                                          | About Standard Logic Cells and Other Types of Cells                                                                                                                                                                                          | 88<br>91 |

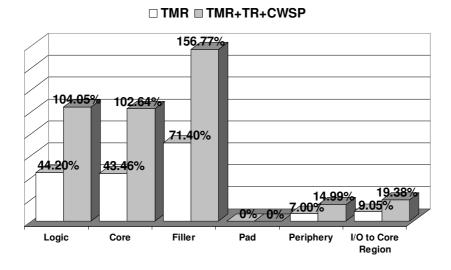

| 6.1.2<br>6.1.3                                                                 | About Standard Logic Cells and Other Types of Cells Costs in Area against Robustness                                                                                                                                                         |          |

| 6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                               | About Standard Logic Cells and Other Types of Cells                                                                                                                                                                                          |          |

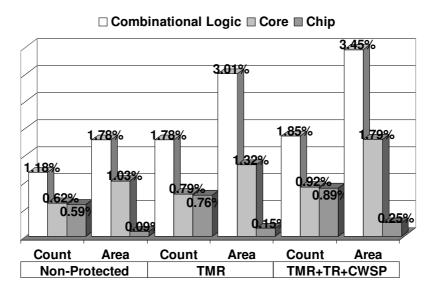

| 6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                               | About Standard Logic Cells and Other Types of Cells                                                                                                                                                                                          |          |

| 6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br><b>6.2</b><br>6.2.1                        | About Standard Logic Cells and Other Types of Cells                                                                                                                                                                                          |          |

| 6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br><b>6.2</b><br>6.2.1                        | About Standard Logic Cells and Other Types of Cells  Costs in Area against Robustness  Clock-Tree Elements  Routing Issues  Performance Analysis  Costs in Performance against Robustness                                                    |          |

| 6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br><b>6.2</b><br>6.2.1<br><b>6.3</b>          | About Standard Logic Cells and Other Types of Cells  Costs in Area against Robustness  Clock-Tree Elements  Routing Issues  Performance Analysis  Costs in Performance against Robustness  Power Analysis                                    |          |

| 6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br><b>6.2</b><br>6.2.1<br><b>6.3</b><br>6.3.1 | About Standard Logic Cells and Other Types of Cells  Costs in Area against Robustness  Clock-Tree Elements  Routing Issues  Performance Analysis  Costs in Performance against Robustness  Power Analysis  Costs in Power against Robustness |          |

### LIST OF ABBREVIATIONS

ASIC Application Specific Integrated Circuit

BIST Built-in Self-Test

CAD Computer-Aided Design

CIF Caltech Intermediate Form

CMOS Complementary Metal-Oxide-Semiconductor

CPU Central Processor Unit

CTLF Compiled Timing Library Format

CWSP Code Word State Preserving

DD Displacement Damage

DEF Design Exchange Format

DRC Design Rule Check

EDA Electronic Design Automation

EDAC Error Detection and Correction FPGA Field Programmable Gate Array

GDSII Graphical Design System II

HC Hamming Code

HCMOS High-density Complementary Metal-Oxide-Semiconductor

HDL Hardware Description Language

IC Integrated Circuit

IP Intellectual Property

LEF Library Exchange Format

LVS Layout Versus Schematic

MBU Multiple Bit Upset

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

PKS Cadence Physically Knowledgeable Synthesis

PPGC Programa de Pós-Graduação em Computação

PWM Pulse Width Modulation

RAM Random Access Memory

ROM Read Only Memory

RSPF Reduced Standard Parasitic Format

RT Register Transfer

SDF Standard Delay Format

SE Soft Error

SE P&R Cadence Silicon Ensemble Place-and-Route

SEB Single Event Burnout

SEE Single Event Effect

SEGR Single Event Gate Rupture

SEL Single Event Latchup

SER Soft Error Rate

SET Single Event Transient

SEU Single Event Upset

SHE Single Hard Error

SOC System-on-Chip

SOI Silicon-on-Insulator

SRAM Static Random Access Memory

TCL Tool Command Language

TID Total Ionizing Dose

TLF Timing Library Format

TCF Toggle Count Format

VCD Value Change Dump

TR Time Redundancy

TMR Triple Modular Redundancy

UFRGS Universidade Federal do Rio Grande do Sul

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VLSI Very Large Scale Integration

# **LIST OF FIGURES**

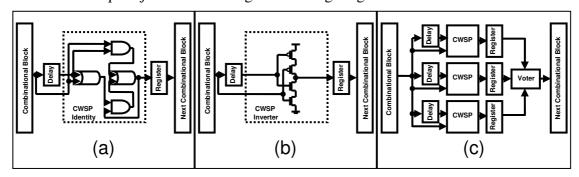

| Figure 1.1: A TR+CWSP mitigation scheme by standard gates (a) and by non-standa | .rd  |

|---------------------------------------------------------------------------------|------|

| gates (b). In (c), the TMR+TR+CWSP mitigation scheme that was used              | . 20 |

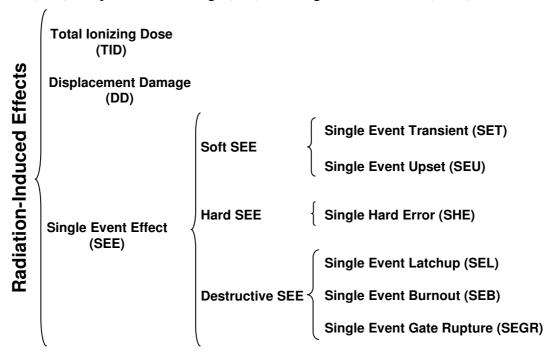

| Figure 2.1: Main radiation-induced effects on integrated circuits               |      |

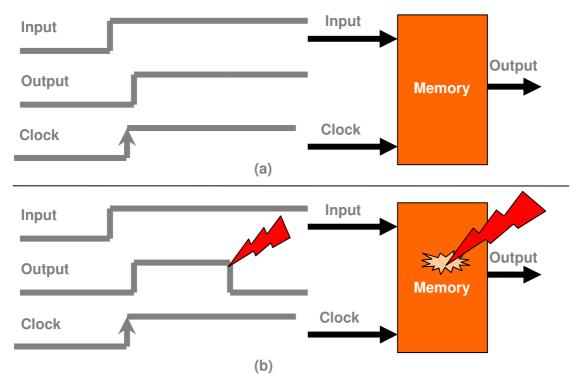

| Figure 2.2: The timing behavior of a memory cell without SE (a) and with SE (b) | . 26 |

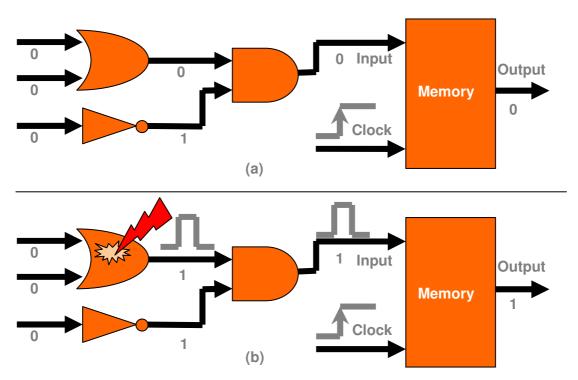

| Figure 2.3: A combinational circuit without SETs (a) and with a SET (b)         | . 27 |

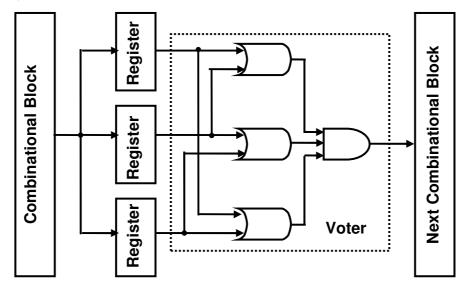

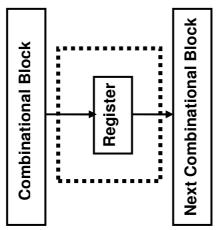

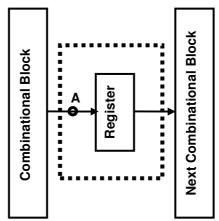

| Figure 3.1: Block diagram of the TMR scheme for a 1-bit register                | . 33 |

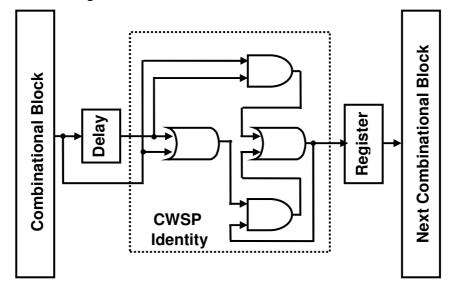

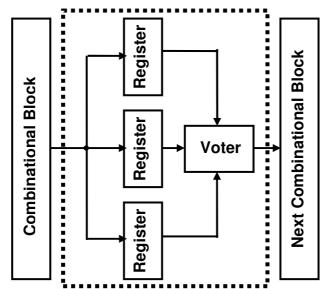

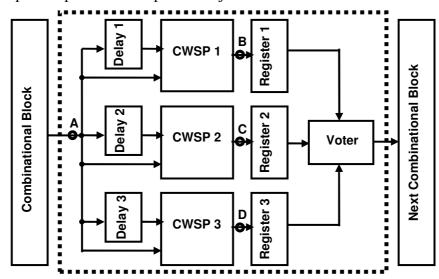

| Figure 3.2: Block diagram of the TR+CWSP scheme for a 1-bit register            |      |

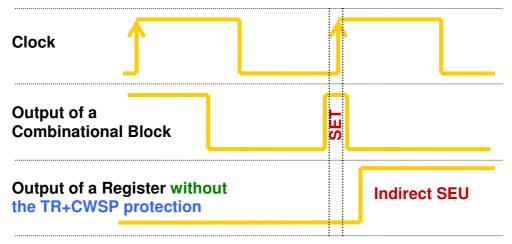

| Figure 3.3: Timing behavior of a system without the TR+CWSP protection          | . 34 |

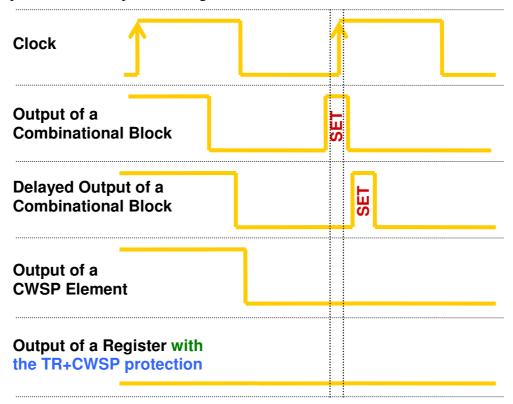

| Figure 3.4: Timing behavior of a system with the TR+CWSP protection             | . 35 |

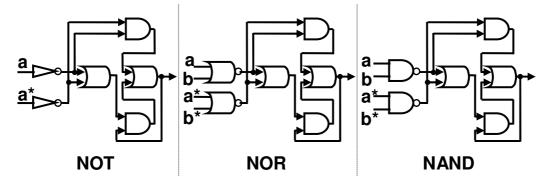

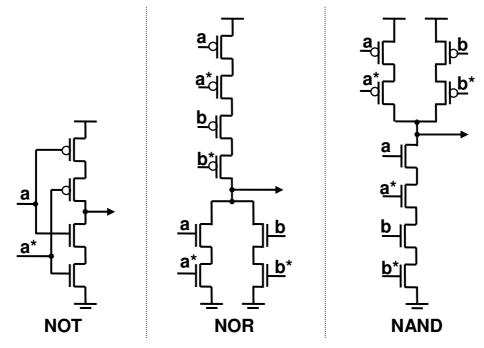

| Figure 3.5: CWSP logic elements (NICOLAIDIS, 1999)                              | . 36 |

| Figure 3.6: CWSP logic gates (NICOLAIDIS, 1999)                                 | . 36 |

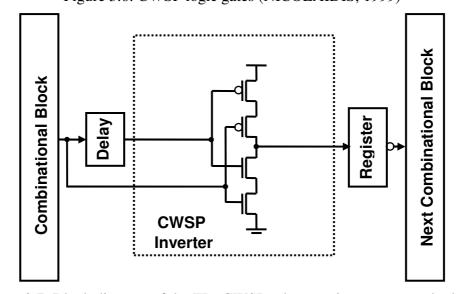

| Figure 3.7: Block diagram of the TR+CWSP scheme using a non-standard gate       | . 36 |

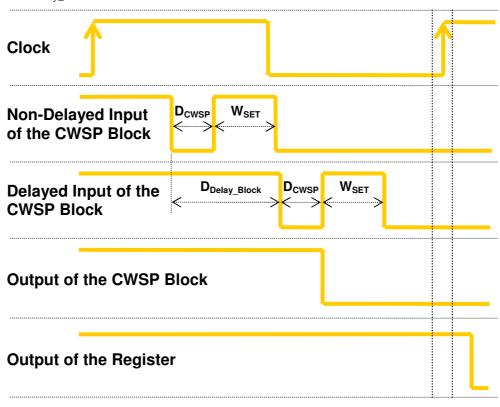

| Figure 3.8: Functional characteristics of the TR+CWSP scheme                    | . 37 |

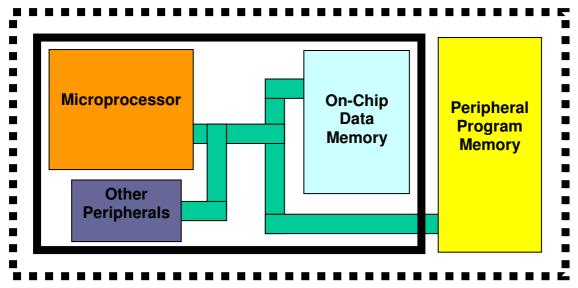

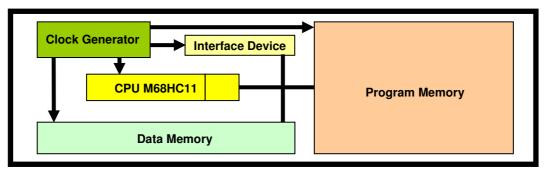

| Figure 4.1: Illustration of a typical microcontrolled system                    | . 41 |

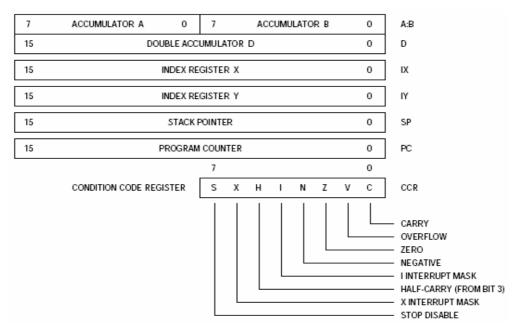

| Figure 4.2: CPU registers visible to the programmer (FREESCALE, 2003)           | . 42 |

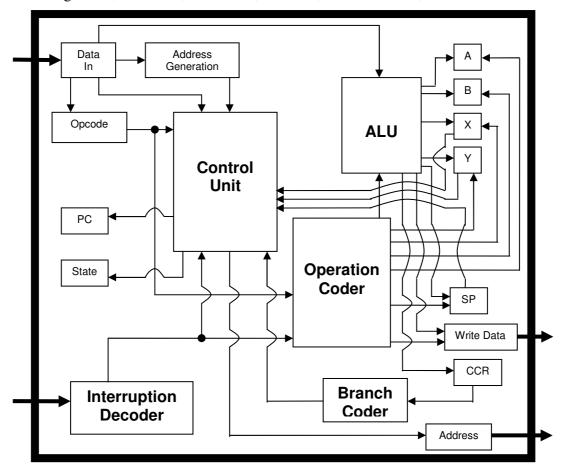

| Figure 4.3: Main functional blocks of the M68HC11 architecture                  | . 43 |

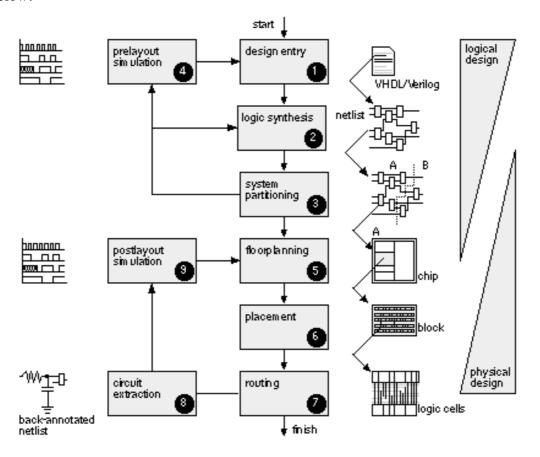

| Figure 4.4: A typical IC design flow (SMITH, 1997)                              | . 45 |

| Figure 4.5: The developed design flow                                           |      |

| Figure 4.6: A process from the original VHDL description                        | . 49 |

| Figure 4.7: Combinational and Register blocks in the Non-Protected version      | . 49 |

| Figure 4.8: A VHDL process purely sequential                                    | . 50 |

| Figure 4.9: VHDL process purely sequential with the new interconnection signal  | . 50 |

| Figure 4.10: A VHDL process purely combinational                                | . 50 |

| Figure 4.11: The unique reusable parameterized VHDL component for all registers | . 51 |

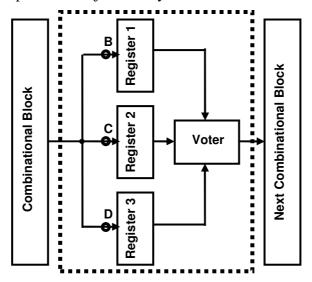

| Figure 4.12: Combinational and Register blocks in the TMR version               | . 52 |

| Figure 4.13: Voter component                                                    |      |

| Figure 4.14: Package of the fault-tolerance mechanisms (1)                      | . 53 |

| Figure 4.15: TMR parameterized component for each one of the registers (part 1) | . 53 |

| Figure 4.16: TMR parameterized component for each one of the registers (part 2) | . 54 |

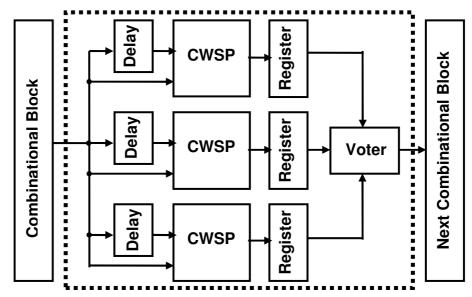

| Figure 4.17: Combinational and Register blocks in the TMR+TR+CWSP version       | . 55 |

| Figure 4.18: CWSP block component                                               | . 55 |

| Figure 4.19: Delay block component                                              | . 56 |

| Figure 4.20: Package of the fault-tolerance mechanisms (2) (part 1)             | . 56 |

| Figure 4.21: Package of the fault-tolerance mechanisms (2) (part 2)             |      |

| Figure 4.22: TMR+TR+CWSP component for each one of the registers (part 1)       |      |

| Figure 4.23: TMR+TR+CWSP component for each one of the registers (part 2)       |      |

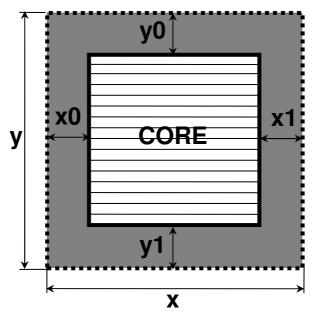

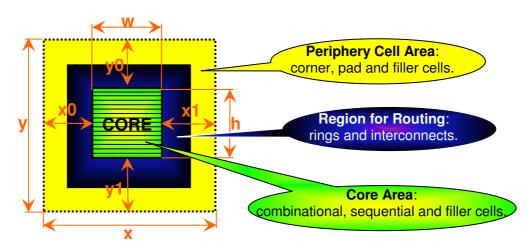

| Figure 4.24: Initial floorplan parameters for the three microprocessor versions |      |

| Figure 5.1: Diagram of the system modeled as a testbench in VHDL                | . 73 |

| Figure 5.2: Execution of the JSR instruction by simulation                             | . 74 |

|----------------------------------------------------------------------------------------|------|

| Figure 5.3: Verification process of functional testing simulation results              | . 77 |

| Figure 5.4: Target circuit nodes in the Non-Protected version                          | . 80 |

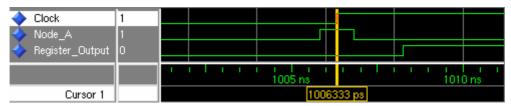

| Figure 5.5: SET injected on the Non-Protected microprocessor version                   | . 80 |

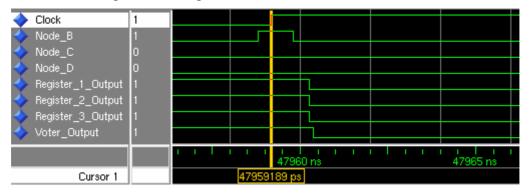

| Figure 5.6: Target circuit nodes in the TMR version                                    |      |

| Figure 5.7: SET injected on the TMR microprocessor version                             | . 81 |

| Figure 5.8: Target circuit nodes in the TMR+TR+CWSP version                            | . 82 |

| Figure 5.9: SET injected on the TMR+TR+CWSP microprocessor version                     |      |

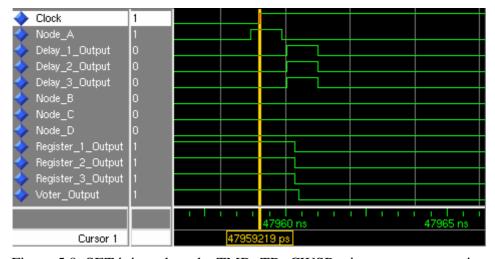

| Figure 5.10: Verification process of fault injection simulation results                | . 83 |

| Figure 6.1: Core and chip areas                                                        | . 86 |

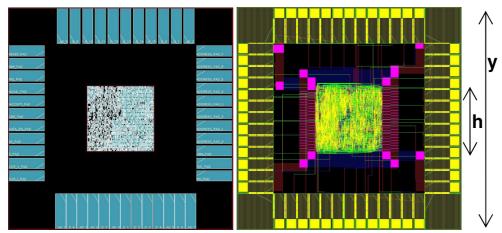

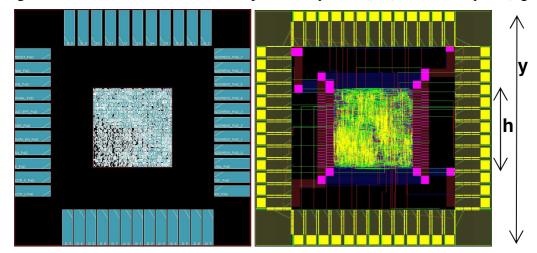

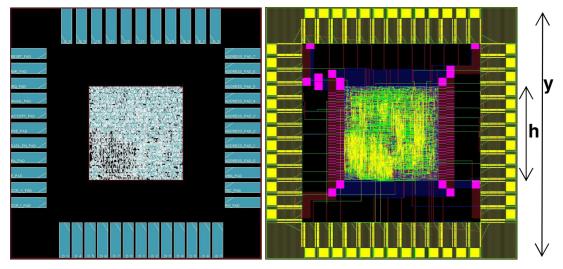

| Figure 6.2: Non-Protected IC version: preliminary view (left) and final layout (right) | . 87 |

| Figure 6.3: TMR IC version: preliminary view (left) and final layout (right)           |      |

| Figure 6.4: TMR+TR+CWSP IC version: preliminary view (left) and final layout (rig      | ght) |

|                                                                                        |      |

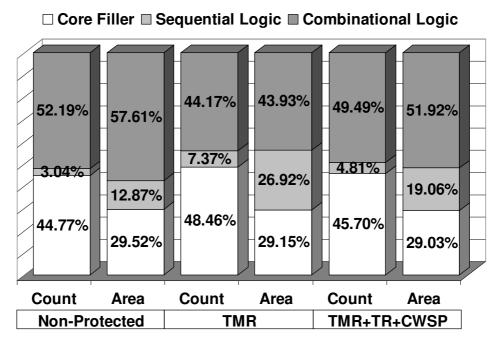

| Figure 6.5: Core utilization                                                           | . 89 |

| Figure 6.6: Chip area utilization                                                      | . 90 |

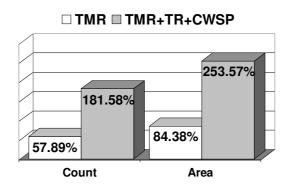

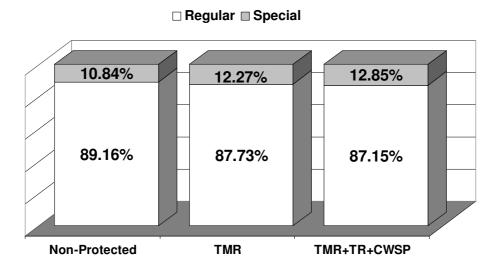

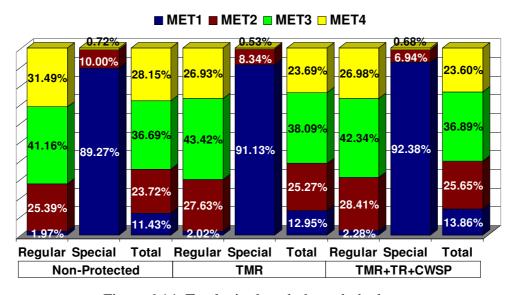

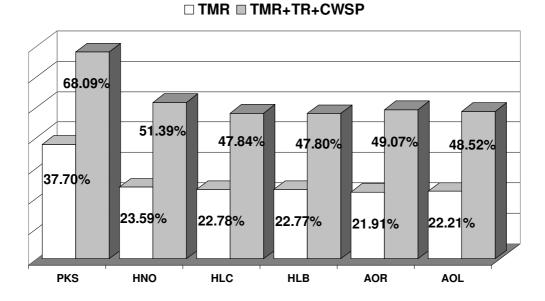

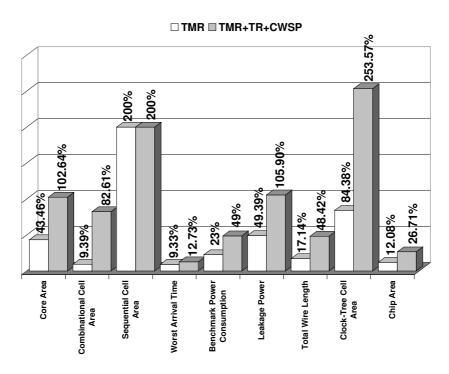

| Figure 6.7: Percent increase in number of cells at chip areas (1)                      | . 91 |

| Figure 6.8: Percent increase in chip areas (1)                                         | . 91 |

| Figure 6.9: Percent increase in number of cells at chip areas (2)                      | . 92 |

| Figure 6.10: Percent increase in chip areas (2)                                        | . 92 |

| Figure 6.11: Clock-tree element ratios to total combinational, core or chip elements   |      |

| Figure 6.12: Percent increase in clock-tree elements                                   | . 94 |

| Figure 6.13: Total wire length through the regular and special wires                   | . 96 |

| Figure 6.14: Total wire length through the layers                                      | . 96 |

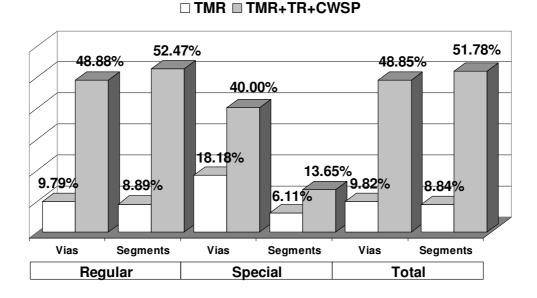

| Figure 6.15: Percent increase in wire lengths                                          | . 97 |

| Figure 6.16: Percent increase in vias and segments                                     | . 97 |

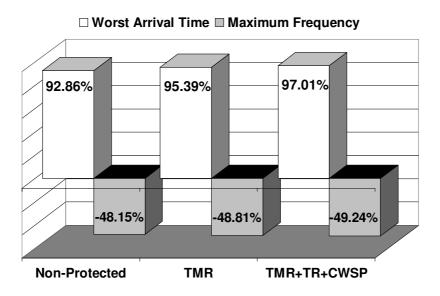

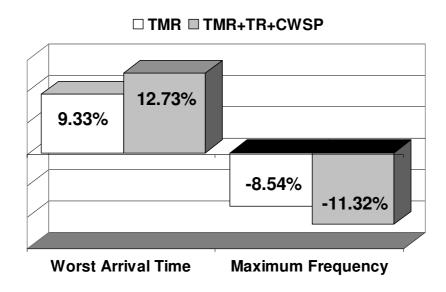

| Figure 6.17: Circuit-extraction information contribution at the worst arrival time     | . 98 |

| Figure 6.18: Timing degradation                                                        | . 99 |

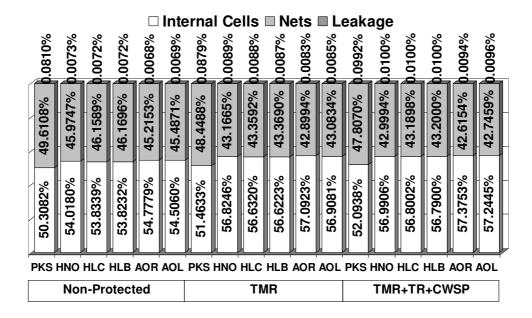

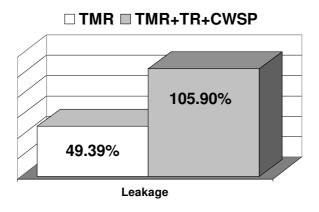

| Figure 6.19: Total power through its components                                        | 102  |

| Figure 6.20: Percent increase in static power                                          |      |

| Figure 6.21: Percent increase in dynamic power                                         | 103  |

| Figure 6.22: Percent increase in total power                                           |      |

| Figure 7.1: Correlation among design results                                           | 106  |

# **LIST OF TABLES**

| Table 4.1: The developed design flow (part 1)                               | 59  |

|-----------------------------------------------------------------------------|-----|

| Table 4.2: The developed design flow (part 2)                               | 62  |

| Table 4.3: The developed design flow (part 3)                               | 64  |

| Table 5.1: Toggle coverage of the benchmarks on the microprocessor versions | 75  |

| Table 5.2: Clock cycles of the benchmarks                                   | 76  |

| Table 5.3: All functional testing simulation approaches                     | 78  |

| Table 5.4: All fault injection simulation approaches                        | 84  |

| Table 6.1: Floorplan characteristics                                        | 86  |

| Table 6.2: About standard logic cells and other types of cells (1)          | 88  |

| Table 6.3: About standard logic cells and other types of cells (2)          | 89  |

| Table 6.4: Clock-tree elements                                              | 93  |

| Table 6.5: Routing issues                                                   | 95  |

| Table 6.6: Timing analysis results                                          | 98  |

| Table 6.7: Power results                                                    | 101 |

### **ABSTRACT**

The advance of the IC technologies raises important issues related to the reliability and robustness of electronic systems. The transistor scale by shrinking its geometry, the voltage reduction, the lesser capacitances and therefore smaller currents and charges to supply the circuits, besides the higher clock frequencies, have made the IC more vulnerable to faults, especially those faults caused by electrical noise or radiation-induced effects.

The radiation-induced effects known as Soft Single Event Effects (Soft SEEs) can be classified into: direct Single Event Upsets (SEUs) at nodes of storage elements that result in bit flips; and Single Event Transient (SET) pulses at any circuit node. Especially SETs on combinational circuits might propagate itself up to the storage elements and might be captured. These erroneous storages can be also called indirect SEUs. Faults like SETs and SEUs can provoke errors in functional operations of an IC. The known Soft Errors (SEs) are characterized by values stored wrongly on memory elements during the use of the IC. They can make serious consequences in IC applications due to their non-permanent and non-recurring nature. By these reasons, protection mechanisms to avoid SEs by using fault-tolerance techniques, at least in one abstraction level of the design, are currently fundamental to improve the reliability of systems.

In this dissertation work, a fault-tolerant IC version of a mass-produced 8-bit microprocessor from the M68HC11 family was designed. It is able to tolerate SETs and SEUs. Based on the Triple Modular Redundancy (TMR) and Time Redundancy (TR) fault-tolerance techniques, a protection scheme was designed and implemented at high level in the target microprocessor by using only standard logic gates. The designed scheme preserves the standard-architecture characteristics in such way that the reusability of microprocessor applications is guaranteed. A typical IC design flow was developed by means of commercial CAD tools. Functional testing and fault injection simulations through benchmark executions were performed as a design verification testing. Furthermore, fault-tolerant IC design issues and results in area, performance and power were compared with a non-protected microprocessor version. The core area increased by 102.64 % to protect the target circuit against SETs and SEUs. The performance was degraded in 12.73 % and the power consumption grew around 49 % for a set of benchmarks. The resulting area of the robust chip was approximately 5.707 mm<sup>2</sup>.

**Keywords:** fault-tolerant microprocessor, Soft Errors, SET, SEU, integrated circuit design.

## Projeto de um Microprocessador Robusto a Soft Errors

#### **RESUMO**

O avanço das tecnologias de circuitos integrados (CIs) levanta importantes questões relacionadas à confiabilidade e à robustez de sistemas eletrônicos. A diminuição da geometria dos transistores, a redução dos níveis de tensão, as menores capacitâncias e portanto menores correntes e cargas para alimentar os circuitos, além das freqüências de relógio elevadas, têm tornado os CIs mais vulneráveis a falhas, especialmente àquelas causadas por ruído elétrico ou por efeitos induzidos pela radiação.

Os efeitos induzidos pela radiação conhecidos como Soft Single Event Effects (Soft SEEs) podem ser classificados em: Single Event Upsets (SEUs) diretos em nós de elementos de armazenagem que resultam em inversões de bits; e pulsos transientes Single Event Transients (SETs) em qualquer nó do circuito. Especialmente SETs em circuitos combinacionais podem se propagar até os elementos de armazenagem e podem ser capturados. Estas errôneas armazenagens podem também serem chamadas de SEUs indiretos. Falhas como SETs e SEUs podem provocar erros em operações funcionais de um CI. Os conhecidos Soft Errors (SEs) são caracterizados por valores armazenados erradamente em elementos de memória durante o uso do CI. SEs podem produzir sérias conseqüências em aplicações de CIs devido à sua natureza não permanente e não recorrente. Por essas razões, mecanismos de proteção para evitar SEs através de técnicas de tolerância a falhas, no mínimo em um nível de abstração do projeto, são atualmente fundamentais para melhorar a confiabilidade de sistemas.

Neste trabalho de dissertação, uma versão tolerante a falhas de um microprocessador 8-bits de produção em massa da família M68HC11 foi projetada. A arquitetura é capaz de tolerar SETs e SEUs. Baseado nas técnicas de Redundância Modular Tripla (TMR) e Redundância no Tempo (TR), um esquema de proteção foi projetado e implementado em alto nível no microprocessador alvo usando apenas portas lógicas padrões. O esquema projetado preserva as características da arquitetura padrão de tal forma que a reusabilidade das aplicações do microprocessador é garantida. Um típico fluxo de projeto de circuitos integrados foi desenvolvido através de ferramentas de CAD comerciais. Testes funcionais e injeções de falhas através da simulação de execuções de benchmarks foram realizados como um teste de verificação do projeto. Além disto, detalhes do projeto do circuito integrado tolerante a falhas e resultados em área, performance e potência foram comparados com uma versão não protegida do microprocessador. A área do core aumentou 102,64 % para proteger o circuito alvo contra SETs e SEUs. A performance foi degrada em 12,73 % e o consumo de potência cresceu cerca de 49 % para um conjunto de benchmarks. A área resultante do chip robusto foi aproximadamente 5,707 mm<sup>2</sup>.

**Palavras-Chave:** microprocessador tolerante a falhas, Soft Errors, SET, SEU, projeto de circuito integrado.

#### 1 INTRODUCTION

The constant technology evolution on the electronic circuitry has already been allowing the manufacture of integrated circuits (ICs) using semiconductors built with nanometer-scale features that near of the physics limits. Indeed, nowadays some popular microchips can be already called nanochips (HUTCHESON, 2004).

If on one hand, the evolutions allow expressive innovations on the engineering of designs optimized in area, performance and power and thus enabling the building of more sophisticated and complex electronic systems. On the other hand, the increasing importance, which ICs have been placing in many spheres of life activities, obliges them to perform their functional tasks within higher levels of safety and correctness. It is even more required in perturbed environments, where ICs are potentially more susceptible to errors.

In fact, the advance of the IC technologies has raised important issues related to the reliability and robustness of the electronic systems. The transistor scale by shrinking its geometry, the voltage reduction, the lesser capacitances and therefore smaller currents and charges to supply the circuits, besides the greater clock frequencies, have made the ICs more vulnerable to faults, especially those faults caused by electrical noise or radiation-induced effects. These scaling and technology issues of the Very Deep Submicron (VDSM) ICs reduce significantly their noise margins and thus their reliabilities regarding various internal or external sources of upset (LIMA, 2003-b; KASTENSMIDT; CARRO; REIS, 2006).

About radiation, the physics explains as the process of emitting radiant energy in the form of waves or particles. The Soft Single Event Effects (Soft SEEs) are caused specially by alpha particles (released by radioactive impurities) and, more importantly, cosmic rays (neutrons) hitting on the silicon chips and transferring charge to the circuit nodes with enough energy able to perturb its storage elements (BORKAR, 2005). These effects are classified in accord to the localization of the attacked node on the IC: direct upsets at nodes of storage elements causing alteration in their information as bit flips can be called direct Single Event Upsets (SEUs) (MASSENGILL et al, 2000); transient voltage fluctuations at any circuit node due to radiation-induced particles as well electrical noise are characterized as Single Event Transients (SETs) (KRISHNAMOHAN, MAHAPATRA, 2004). Especially SETs on combinational circuits are modeled like transient pulses that might propagate up to the storage elements and might be captured. It basically depends on the delays of the combinational network gates, on the widths of the created pulses and if these pulses meet the set-up and hold time requirements of the memory elements at a clock transition for storing. These erroneous storages can be also called **indirect SEUs**.

Faults like SETs and SEUs may provoke errors in functional operations of an IC. The known **Soft Errors** (**SEs**) are characterized by values stored wrongly on memory elements during the use of the IC and not due to design errors, fabrication defects or permanent physical failures. They can make serious consequences in IC applications as a result of their non-permanent and non-recurring nature (SHIVAKUMAR et al, 2002; KARNIK; HAZUCHA; PATEL, 2004). The increase in Soft Error Rates (SERs) on ICs has been a great source of concern for researchers in the last years. Some techniques have been developed to decrease the SER on ICs. Alpha particle flux has been gradually reduced by the use of purified materials. Fabrication process improvements in the 0.18 um technology generation made the low-energy (lesser than 1 MeV) neutron SER negligible. Even though such techniques have reduced the SER, the high-energy (1 MeV to 1000 MeV) neutrons often dominate it in advanced CMOS logic (TOSAKA et al, 1998). Experiments, which replicate the sea level conditions for energies from 10 to 500 MeV, showed that the SER per bit of SRAMs in 0.25 µm, 0.18 µm, 0.13 µm and 90 nm technologies increases by 8% per generation (HAZUCHA et al, 2003). In addition, the situation is worse for ICs operating at flight altitudes or in space due to the even higher energies of the particles from there (LIMA, 2003-b). Years ago, studies related to the fault tolerance in semiconductor devices had larger developments especially for space and physics applications. Unlike today at which the concern is also focused at the debilities of circuits on terrestrial applications like servers and many embedded systems that usually have a large amount of embedded memory elements. By all these reasons, protection mechanisms to avoid SEs by using fault-tolerance techniques, at least in one abstraction level of the design, are currently fundamental. It improves the reliability and guarantees the correct operation of the systems. Several commercial microprocessors from AMD, Freescale, IBM, Intel and Sun are real implementations of robust systems by using detection and recovery techniques (IYER et al, 2005).

The current system complexities, the usual time-to-market and the project budget constraints have led designers to investigate fault-tolerance techniques and design flows more versatile. Reusable Intellectual Property (IP) cores developed at the higher abstraction levels of design, like the Register Transfer (RT) level, support engineers to faster cope with even more complex requirements such as System-On-Chips (SOCs). The reusability of hardware IPs and also software applications avoids redesigning and redeveloping the same features repeatedly and thus saves effort (i.e., development cost) and design time (HERRERA et al, 1999). Furthermore, the industry of EDA tools or CAD environments in the last years has been making easier and quicker the development of IC designs. Starting from higher design levels, EDA tools are able to provide very accurate estimated results of the IC design for a preliminary evaluation. On the other hand, making robust a system by using any fault-tolerance mechanism inherently involves additional overheads. There are many fault-tolerance techniques with different characteristics aiming different design levels, each one can be better adapted to a distinct design purpose. Therefore, a carefully preliminary analysis of the robustness features applied to the target system is mandatory before starting the design of the robust system. Moreover, a preliminary evaluation of the design costs before the IC manufacture is also fundamental through estimated IC design results such as in area, performance and power consumption.

Some requirements for the fault-tolerance implementation may implicate undesired modifications at standard characteristics of a system, especially when the target is the reusability of systems based on standard architectures like commercial microprocessors.

For instance, some typical fault-tolerance techniques require additional clock networks for fault detection and extra clock cycles for fault correction. In addition to the inherent cost of the fault-tolerance mechanisms, some consequences, which may be undesired, are the necessity for other clock signals and extra clock-tree implementations besides unexpected overheads at the execution time of its software applications. To save design time and development cost in a robust IC design, the chosen fault-tolerance techniques usually are desired not only to guarantee the reliability and reusability of their existing hardware and software applications. They are also desired to be easily or at least applicable at the target design level (for example, at the RT level) and that they adapt themselves to commercial standard cores.

Commercial microcontrollers like Freescale M68HC11, Intel 8051 and Microchip PIC are commonly mass-produced for electronic systems or embedded systems. Such systems have a wide range of applications in instrumentation, automation, control, telecommunication or even domestic appliances. These microcontrollers and their microprocessors are also largely used as cores or parts of SOCs. As these commercial circuits are consolidated in the market because they are simple and cheap, there are many systems and applications based on them. The utilization of these circuits allows the reusability of those already existing systems and applications. Consequently, design time and development costs can be saved. Typically, these commercial circuits are not prepared to operate under hostile environments. On the other hand, as circuits based on the new technology generations are more vulnerable to SEs. Thus, in the new manufactures, such commercial circuits trend to require some embedded fault-tolerance mechanism to guarantee their functionalities (i.e., to ensure the circuit reliability).

Another issue is that many commercial microprocessor systems such as some AMD, IBM and Intel architectures (LIMA et al, 2000-a, 2000-b; COTA et al, 2001; IYER et al, 2005) generally are protected against direct SEUs but not usually against indirect SEUs. The most commonly used mechanisms against SEs in modern processor are based on parity and Error Detection and Correction (EDAC) codes (IYER et al, 2005). Such techniques are essentially focused on protecting memory arrays and they usually do not mitigate indirect SEUs. Nevertheless, the scaling and technology issues tend to require protections against such faults too (SHIVAKUMAR et al, 2002). By this reason, many fault-tolerance techniques dedicated to mitigate indirect SEUs have been currently developed like those in (NICOLAIDIS, 1999; ANGHEL; NICOLAIDIS, 2000-a; KRISHNAMOHAN, MAHAPATRA, 2004; ZHANG; SHANBHAG, 2005).

The purpose of this dissertation work is to make robust to Soft SEEs or Soft Errors a commercial digital circuit, such as the 8-bit microprocessor from the microcontroller family M68HC11 (FREESCALE, 2002), for a future IC manufacture. In order to save design time, some initial design constraints were established. The fault-tolerant circuit design should be developed at high level like the RT level. The implemented fault-tolerance techniques should not use multiple clock networks. For any application, the techniques should preserve the total number of clock cycles, even so under a fault occurrence. Such initial constraints keep the standard-architecture characteristics and thus the reusability of microprocessor applications. In addition, they save development cost.

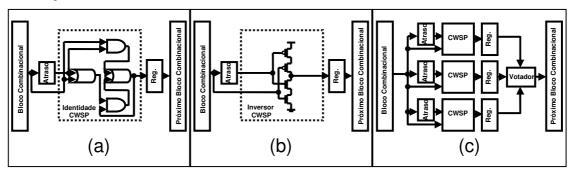

SETs on combinational circuits of the microprocessor, which can potentially cause indirect SEUs, are mitigated by using a Time Redundancy (TR) technique. The work in (NICOLAIDIS, 1999) suggests but does not implement a TR approach based on a special element called Code Word State Preserving (CWSP) like that from Figure 1.1

(a). Another work (ANGHEL; ALEXANDRESCU; NICOLAIDIS, 2000-b) evaluates this approach in area and performance by using simple test circuits, like adders and multipliers, and non-standard gates, such as that from Figure 1.1 (b), to implement the CWSP elements. In (LAZZARI; ANGHEL; REIS, 2005), the same evaluation is made for two microprocessors, MIPS and 8051, but a special automatic layout generator implements the non-standard gates that characterize the CWSP elements. In order to mitigate direct SEUs, in (LAZZARI; ANGHEL; REIS, 2005) a Triple Modular Redundancy (TMR) version that requires three clock signals was also implemented. In the present dissertation work was implemented a simpler and faster alternative to design by using only standard gates, like that from Figure 1.1 (a), and without an extra layout tool like that presented in (LAZZARI; ANGHEL; REIS, 2005). The defined initial design constraints are met through this alternative. The goal was to evaluate the costs in area, performance and also power and other design results of this fault-tolerance approach in the target microprocessor. In addition, the TR+CWSP elements and microprocessor registers were protected in accord to Figure 1.1 (c) by using a TMR version that require just one clock signal for mitigating direct SEUs.

Figure 1.1: A TR+CWSP mitigation scheme by standard gates (a) and by non-standard gates (b). In (c), the TMR+TR+CWSP mitigation scheme that was used

The present dissertation is organized by chapters in the following way. Chapter 2 characterizes the target faults on integrated circuits by means of a radiation-induced fault model. Chapter 3 presents an overview about usual soft error mitigation techniques and details concerning the techniques implemented in the target microprocessor of this work. Chapter 4 introduces the target microprocessor to be protected and emphasizes the strategies applied in the robust microprocessor design. Furthermore, it shows the design steps from the microprocessor RT-level descriptions up to the GDSII stream files that are used to specify the physical design characteristics in an IC manufacture process. Chapter 5 presents the design verification simulation methods performed with the implemented microprocessor models in order to avoid design errors. In chapter 6, microprocessor design results by means of the circuit area, performance, power and other resulting information are analyzed. Some final remarks, conclusions and future works are discussed in chapter 7.

### 2 A RADIATION-INDUCED FAULT MODEL

Noxious effects on integrated circuits caused by internal or external sources of upset have been increasing due to the current scaling and technology trends. The direct consequences of these trends are smaller noise margins and thus circuits more vulnerable to external effects, like charged particles from different sources of radiation, as well to internal or external electrical noise. If a charge disturbance on a circuit node is smaller than the noise margin, the circuit will continue to operate properly. Otherwise, the disturbed voltage may be interpreted as the opposite logic state and the circuit will malfunction (KARNIK; HAZUCHA; PATEL, 2004).

Many different sorts of particles are found in environments where integrated circuits usually work. In space, particles from cosmic rays consist mostly of protons, but also of helium, oxygen and other ions (TOSAKA et al, 1998). At atmospheric and ground levels, alpha particles released by radioactive impurities in the device materials and mainly terrestrial cosmic rays in the form of high-energy neutrons are the major contributors for perturbations on circuit nodes (TOSAKA et al, 1998; BAUMANN; SMITH, 2000; BAUMANN, 2001; LERAY et al, 2004; BORKAR, 2005). Even so neutrons do not have electrical charges, their effects occur through nuclear collisions that give rise to charged particles. When such particles interact with the silicon atoms, they create a direct ionization in the semiconductor device causing transient currents that are able to make faults on the circuits. The amount of ionization and the current surge in a given semiconductor device are directly proportional to the energy lost by the radiation particles (KARNIK; HAZUCHA; PATEL, 2004; LIMA, 2003-b).

The type and the flux of hadrons like neutrons, protons and pions exhibit strong altitude and latitude dependence (NORMAND, 1996-a; CONSTANTINESCU, 2005). At sea level, the neutron flux is several hundred times lower than at aircraft altitudes. For instance, the neutron flux at 12 km (~40000 ft) altitude is around 300 times higher than at sea level and at 20 km (~60000 ft) it has its maximum peak. For this reason, integrated circuits operating at aircraft altitudes are more susceptible to faults induced by such particles than at ground level (NORMAND, 1996-b; GRANLUND; GRANBOM; OLSSON, 2003).

#### 2.1 The Basic Radiation-Induced Effects on Integrated Circuits

The radiation-induced effects by means of their charged particles can cause different serious consequences on semiconductor circuits. Energetic particles incident on a solid lose their energy to ionizing and non-ionizing processes as they travel through a given material. The result of this energy loss is the production of electron-hole pairs (ionization) and displaced atoms (displacement damage) (SROUR; MARSHALL; MARSHALL, 2003). Especially three classes of these effects (Figure 2.1) are deeply

explored by researchers due to their random natures and occurrence rates: Total Ionizing Dose (TID), Displacement Damage (DD) and Single Event Effects (SEEs).

Figure 2.1: Main radiation-induced effects on integrated circuits

**Total Ionizing Dose** (**TID**) is due to long-term degradation of electronic circuits as a result of the cumulative energy deposited in some materials used by ICs. In space environment, significant sources of TID include trapped electrons, trapped protons and solar protons. Its effects include parametric failures or variations in device parameters like leakage current, threshold voltage, timing changes, etc (LABEL et al, 2000). These effects usually take a long time to occur, but they are permanent and can induce functional failures to ICs as putting out of use some of their functional blocks.

**Displacement Damage (DD)** is non-ionizing radiation effect that often has similar long-term degradation characteristics like TID. This effect leads to the degradation of material and device properties and is a consequence of the incident particles that displace atoms. The resulting defects give rise to new energy levels that alter the materials and devices in their electrical and optical properties. The effectiveness of radiation-induced DD depends basically on the defect rate and on the time exposure. Prime sources of DD include trapped protons, solar protons, neutrons, and in a lesser extent, trapped electrons (LABEL et al, 2000; SROUR; MARSHALL; MARSHALL, 2003).

Single Event Effects (SEEs) are due to transient physical faults such as single ions that impact on the circuit sensitive area. Sometimes, these events can deposit sufficient energy in the device that give rise to current pulses able to disturb the correct functionality of the system. Significant sources of SEEs include trapped protons, solar protons, neutrons and heavy ions from galactic cosmic rays. SEEs faults are composed by three distinct categories, depending on the consequences of the involved current pulse (LIMA, 2000-c; O'BRYAN et al, 1998):

• **Soft SEE**: during the operation of a device, a transient current pulse or a bit flip in its circuit can cause errors in its functionalities. Due to their non-permanent

and non-recurring nature, these physical failures were called **Soft Errors** (**SEs**) (KARNIK; HAZUCHA; PATEL, 2004). They disappear when the system is reset or a data is rewritten in the memory. By this reason they can also be considered as intermittent events. Such errors are entirely device specific and are better categorized by their impacts on the device (LABEL et al, 2000). When a radiation-induced particle hits a node of a circuit, a Single Event Transient (SET) pulse can be created with enough energy to switch the node to a different voltage level. Indeed, SETs are characterized as transient voltage fluctuations on circuit nodes. They can be caused by radiation-induced particles as well electrical noise like noisy power supply, crosstalk noise, electromagnetic interference (EMI), radiation from lightning, etc (ZIEGLER et al, 1996; CALIN; VARGAS; NICOLAIDIS, 1995; MAHESHWARI; KOREN; BURLESON, 2003; KRISHNAMOHAN, MAHAPATRA, 2004). In a digital device, a direct Single Event Upset (SEU) occur when a storage element is directly affected by a SET in such way that it causes an undesired change on the memorized information as a bit flip (MASSENGILL et al, 2000). A SET pulse can be generated on a combinational logic circuit. Depending on the delay of the combinational gates and on the width of the pulse, it also can propagate up to the output of the combinational logic block. If the storage element succeeds to capture this undesired pulse, an **indirect SEU** is characterized;

- **Hard SEE**: hard errors are permanent functional effects to the device. An event of **Single Hard Error (SHE)** causes an undesired permanent change to a circuit node. A common example would be a stuck bit in a memory element (LABEL et al, 2000);

- Destructive SEE: events that can cause permanent physical destruction of the circuit. A Single Event Latchup (SEL) is the most common Destructive SEE. It is a potential destructive condition involving parasitic transistors on which currents might exceed their maximums specified. These parasitic transistors in the circuit can be activated by spurious currents, like those from radiation-induced effects. It would create a short between internal circuit nodes that may destroy the device by thermal effect, unless the power supply is removed. A Single Event Burnout (SEB) is a highly localized destructive burnout of the drain-source in a MOSFET. On the other hand, a Single Event Gate Rupture (SEGR) is the destructive burnout of a gate insulator in a MOSFET (LABEL et al, 2000).

#### 2.1.1 Occurrence Rate of Radiation-Induced Effects

The SEE rates are not described as Mean-Time-To-Failure (MTTF). If an SEE rate is one per five years, it may happen at any time during that five year period with nearly equal probability. Otherwise, cumulative effects, such as TID or DD, the MTTF numbers are useful. The time-to-failure is the amount of operation time until the device has encountered enough degradation to cause failure (LABEL et al, 1996).

The high relevance of such effects can be supported by recent and frequent researches. At least since 1998, NASA's researchers have annually published at IEEE conference experimental results about the susceptibility of commercial and emerging technology devices to TID, DD and SEEs (O'BRYAN et al, 1998; COCHRAN et al, 2005; O'BRYAN et al, 2005).

This large concern, especially with the Soft Error (SE) occurrences on ICs, has resulted in a lot of researches for measuring, estimating and evaluating the **Soft Error Rate (SER)** of semiconductor devices. Many works characterize and evaluate the SE effects on ICs like those in (HARBOE-SORENSEN; SUND, 1992; VELAZCO; KAROUI; CHAPUIS, 1992; NORMAND et al, 1994; TOSAKA et al, 1998; ZIEGLER et al, 1998; BAUMANN, 2001; HOWARD et al, 2001; LIMA et al, 2001-a, 2001-b, 2002-a, 2002-b; DODD et al, 2002; MAIZ et al, 2003; KARNIK; HAZUCHA; PATEL, 2004; LERAY et al, 2004; LAMBERT et al, 2004; CONSTANTINESCU, 2005; SAGGESE et al, 2005).

Some real examples about SE evidence on ICs at ground level were discussed in (NORMAND, 1996-b). The computer system ACPMAPS at Fermilab is a very large system of individual computers, which when joined together, it contains about 160 Gbits of DRAM memory. This system is protected only by parity mechanisms. In a monitorial experiment, it had 2.5 upsets per day or a SER of  $0.7 \cdot 10^{-12}$  upset/(bit·hour). Another case, 58 off-the-shelf Nite Hawk computers were monitored. Each computer is constituted by 1 Gbits of DRAM protected by EDAC codes. On the average, each machine showed around one upset per month (assigned as 624 hours), which was equivalent to a SER of  $1.6 \cdot 10^{-12}$  upset/(bit·hour).

Additionally, there is a set of other works related to the SE effects on ICs at ground, atmospheric and space levels (NORMAND; BAKER, 1993; LABEL et al, 1996; NORMAND, 1996-a; BARTH, 1997; LABEL et al, 2000; NORMAND, 2001). Others show the SER increase in the new technology generations of ICs due to the scaling and technology trends (HAZUCHA el al, 2003; GRANLUND; GRANBOM; OLSSON, 2003; BORKAR, 2005).

#### 2.1.2 Modeling of Radiation-Induced Effects

The radiation-induced effects on an integrated circuit can be modeled at different abstraction levels of the circuit design. In accord to (ABRAMOVICI; BREUER; FRIEDMAN, 1990; SMITH, 1997; WAGNER, 2004), the usual design levels from the lowest to the highest are classified into:

- **Real circuit level**, the circuit prototypes or the circuit fabricated by physical materials from a fabrication technology;

- Electrical level, the circuit layout mask at a geometric axis or the circuit models

based on transistors, resistors, capacitors and inductors at a structural axis. Some

authors consider the layout mask issues as part of the labeled physical level,

even so such label is also used for the real circuit level. In addition, others define

switch level as transistors modeled discretely and transistor level as transistors

characterized by non-linear models;

- **Logical level**, the circuit models at a structural axis based on flip-flops, latches and logic gates, besides library cells at a geometric axis. EDA tools usually label the model of logic gates as **gate level**;

- Micro-architectural level or the well-known Register Transfer (RT) level, the

circuit models at a structural axis based on registers, multiplexers, operators like

adders, subtracters, multipliers and dividers, besides macro cells at a geometric

axis. Some authors label this level as behavioral level or even functional level

in accord to the delay model that is used;

- **Algorithmic level**, circuit models at a structural axis based on hardware modules. Modules, cores, plans of power, ground and clock at a geometric axis;

- **Systemic level**, circuit models at a structural axis based on processors, memories and other peripherals. Components and boards at a geometric axis.

As defined in chapter 1, the goal in this work is to make robust against radiation-induced effects a digital system such as a Central Processor Unit (CPU). A digital system denotes a complex digital circuit. The complexity of a circuit is related to the abstraction level required to describe its operation in a meaningful way (ABRAMOVICI; BREUER; FRIEDMAN, 1990). Typically, highest abstraction levels are used to design complex circuits because they provide a better management for designers. In this way, digital system designs usually require high-level abstraction resources like the VHDL, in which the lowest abstraction level that designers can deal with is the logical level.

At the abstraction logical level of a digital circuit, a further distinction can be made between combinational and sequential circuits. Unlike a combinational circuit, whose output logic values depend only on its present input values, a sequential circuit can also remember past values and hence it processes sequences of logic values (ABRAMOVICI; BREUER; FRIEDMAN, 1990).

In such circuit design abstraction, the radiation-induced effects feasible to be treated are those in which their tolerance mechanisms are able to be implemented at least at the logical level. The Soft and Hard SEEs are feasible. However, Destructive SEEs, TI and DD are typically treated at lower abstraction levels.

As emphasized in chapter 1, this work focuses on the Soft SEE on ICs. The serious effect of such physical fault can be modeled at the logical level as a bit flip. As seen in the last sections, it is an undesired change on the memorized information of storage elements or in other words a Soft Error (SE). At the logical level of an IC, storage elements are sequential circuits or memory cells such as flip-flops or latches.

This problem of Soft SEEs on ICs can be summarized based on the traditional definitions of fault, error and failure for a computer system (LAPRIE, 1998). The transient current pulse caused by a source of upset on a combinational or sequential circuit is a system **fault**, the bit flip on the memory cell is a system **error** and the reading of wrong values stored in the register is a system **failure**.

From the Soft SEEs, the sequential elements (memory cells) can be affected by direct or indirect Single Event Upsets (SEUs). In following sections, such effects and their characteristics are modeled and discussed.

#### 2.1.2.1 Direct SEUs

A direct SEU is modeled as a logic perturbation or a direct logic inversion on a bit memorized by a sequential element. To illustrate such fault at the logical level, firstly the ideal timing behavior of a memory cell such as a positive edge-triggered flip-flop is shown in Figure 2.2 (a). After, Figure 2.2 (b) shows the timing behavior of the memory under a direct SEU.

Note in Figure 2.2 (a) that the memory input is switched from 0 to 1 at an instant before the clock event. This instant need respect the set-up time, thus such switch can not occur within a set-up time before the clock event. In the same way, the memory

input need be kept on that value (value 1) at least a hold time after the clock event. Thus, the memory output switches logically from 0 to 1 and such value 1 is kept in the memory.

On the other hand, in Figure 2.2 (b), a direct SEU makes an inversion from 1 to 0 at the memory output (i.e., a SE) without any input or clock event. Note that the SE might be transient if new events occur. The memory output will be kept on 0 until new input switch (respecting the set-up and hold time requirements) or even until new SEU.

Figure 2.2: The timing behavior of a memory cell without SE (a) and with SE (b)

#### 2.1.2.2 Indirect SEUs

An indirect SEU is due to a Single Event Transient (SET) modeled as a rectangular transient pulse that occurs on a combinational circuit and propagates itself up to a sequential element.

To illustrate such fault at the logical level, initially the ideal behavior of a sequential element (flip-flop) and a combinational circuit by means of its logic gates are presented in Figure 2.3 (a). After in Figure 2.3 (b), the fault is characterized.

Observe in Figure 2.3 (a) that the combinational circuit processes properly the values 0 at its three inputs. In addition, the sequential element memorizes appropriately the value 0 from the resulting combinational circuit output.

On the other hand, in Figure 2.3 (b), a SET occurs on a gate of the combinational circuit. The SET succeeds in propagating up to the output of the combinational circuit that is temporarily switched to 1. It hypothetically occurs at an instant and lasts enough time to meet the requirements of the set-up and hold times. Thus the undesired value 1 is memorized as an indirect SEU and a SE is characterized.

Figure 2.3: A combinational circuit without SETs (a) and with a SET (b)

#### 2.1.2.3 *SET Issues*

A SET on a combinational circuit does not always give rise to an indirect SEU, it may not cause any unfavorable consequence to the IC. Such masking effect can be due to one of the following factors (SHIVAKUMAR et al, 2002):

- **Logical Masking**: a SET does not propagate up to output of the combinational circuit because makes some combinational logical operation that masks it;

- **Electrical Masking**: a SET is sufficiently attenuated due to the electrical properties of gates in the propagation path. In fact, if the duration of a SET pulse is larger than the propagation time (logic transition time) of a gate, it typically should not be attenuated. However, when a SET width is lesser than the propagation time of a gate, it starts to be slight attenuated and usually when it is lesser than half of the propagation time, it is sufficiently attenuated (NICOLAIDIS, 1999);

- Latching-Window Masking: a SET reaches the input of a sequential element, however does not meet the time window such as the set-up and hold times, which is required for the circuit latching a value at the clock event.

Such three masking phenomena provide the combinational circuits a form of natural resistance to SEs (SHIVAKUMAR et al, 2002). Past research has shown that combinational logic is much less susceptible to allow SEs than memory elements (LIDÉN et al, 1994; GAISLER, 1997). The memories always were considered most vulnerable to SEs due to their spatial density and the amount of information that they store (MAHESHWARI; KOREN; BURLESON, 2003). However, in the current decade as a result of the current nanometer technologies and the consequent high complexity of the integrated circuits, the SER arisen in combinational circuits shall become as relevant as the SER in sequential elements. In the work (SHIVAKUMAR et al, 2002) were analyzed the trends in the SER for SRAM cells, latches and combinational circuits. It

predicts that by 2011 the SER arisen in combinational circuits will be comparable to that of unprotected memory elements.

The timing nature of a SET pulse generated on a circuit, especially on the combinational parts, depends on the energy of the perturbation event, on the employed physical technology and on the design topology of the circuit. The work (ANGHEL; NICOLAIDIS, 2000-a) generically presumes the duration of a typical SET pulse at few hundreds of picoseconds. Currently, such order of SET width is common for micrometer (channel length above 0.1  $\mu$ m) nearly nanometer (below 0.1  $\mu$ m) technologies. It can be easily found in many related experiments and works discussed in dedicated conferences such as the (SEE SYMPOSIUM, 2006).

Since pulses wider than the logic transition time of a gate usually can propagate itself without attenuation. For circuits based on micrometer technologies in which typical delays of basic standard logic gates can be around 10 ps, a SET of width around 100 ps can diffuse itself through gates, reach sequential elements and make SEs. On the other hand, in nanometer technologies, the propagation time of gates can be even smaller than the SET duration. In this way, even SET pulses due to perturbations of lower energy, therefore smaller SET widths, might not be attenuated. Furthermore, as the clock frequencies have increased significantly, the probability of latching a SET have also increased. In fact, as more frequent are the latching edges of the clock, higher is the probability to have a SET coinciding with a latching edge (ANGHEL; NICOLAIDIS, 2000-a).

Another critical characteristic of a SET pulse is when it occurs on an internal node of a combinational circuit with a certain width. After propagating through some combinational circuit paths, it can result wider at the output of the combinational circuit (input of a sequential element). Such occurrences make difficult the prevision of the maximum width for a fault-tolerance implementation. This phenomenon is essentially due to reconvergent fan-outs with different delays (ANGHEL; ALEXANDRESCU; NICOLAIDIS, 2000-b). The original pulse can propagate itself through several paths which reconverge and concatenate several pulses into a single one. This pulse can be larger than the original one due to the different delays of the propagation paths (ANGHEL; ALEXANDRESCU; NICOLAIDIS, 2000-b). In the work (NICOLAIDIS; PEREZ, 2003) is proposed a circuit that can measure experimentally the SET widths.

A unique SET pulse arisen in a combinational circuit can sometimes also generate multiple pulses at the output of this circuit as a result of the delay differences among its paths. Nevertheless, by considering a balanced circuit, such multiple events are rare. It is because those delay differences must not exceed the width of the original pulse arisen in the combinational circuit. Modern logic synthesis tools and architectural solutions trend to generate balanced circuits. This kind of circuit has the delays of its paths close to the delay of its largest path (NICOLAIDIS, 1999; ANGHEL; ALEXANDRESCU; NICOLAIDIS, 2000-b).

In addition, depending on the topology of the circuit, a unique SET can also cause a unique or several indirect SEUs. Several SETs can also occur at the same time on any bit of a combinational or sequential circuit, at any moment during the use of the IC.

By reason of all these behaviors of the SET pulses, their evaluations become very complex in circuits composed by many paths. Some works dedicate special attention to analyze the probability of a SET becoming an indirect SEU (HASS et al, 1998; HASS, 1999; MASSENGILL et al, 2000; ALEXANDRESCU; ANGHEL; NICOLAIDIS,

2002). Other approaches like a SET propagation method based on topological timing analysis (NEVES et al, 2006-a, 2006-b) could be used to evaluate such probability too.

#### 2.1.2.4 Multiple SEUs

When multiple indirect or direct SEUs happen at the same time on bits of memories, it is traditionally called of **Multiple Bit Upsets** (**MBUs**). According to the number of upsets that occur at the same time in the circuit, bit upsets can be classified in first, second and third order effects. A single bit upset (SEU) is classified as a first order effect, while multiple bit upsets (MBUs) are classified as second or third order effects (LIMA, 2003-b). MBUs can occur when:

- A single particle hits two adjacent nodes, located in two distinct memory cells.

This event is classified as a second-order effect and can be avoided by specific placement design;

- A single particle strikes two adjacent nodes located in the same memory cell. This event is classified as a third-order effect and can be avoided by physical layout constraints for separating critical nodes;

- Multiple particles strike the circuit causing upsets in multiple nodes. These events can be considered as a group of direct SEUs;

- A unique SET from a combinational circuit result in multiple indirect SEUs;

- Several SETs from a combinational circuit result in multiple indirect SEUs.

### 3 SOFT ERROR MITIGATION TECHNIQUES

The evolution of scaling down technology has raised relevant issues related to the reliability and robustness of circuits. Reliability is normally defined as the immunity of a circuit to faults like, for instance, those that cause Soft Errors (SEs). Design robustness is defined as the ability of a circuit to operate correctly under varying process, temperature, voltage, and noise conditions (KRISHNAMOHAN, MAHAPATRA, 2004).

In order to improve the reliability and guarantee the correct operation of systems, robustness mechanisms to mitigate SEs through fault-tolerance techniques, at least in one abstraction level of the IC design, are currently much used at the industry. Several commercial microprocessors from AMD, Intel, IBM, Freescale and Sun are real implementations of robust systems. As examples, there are processors from the families: Intel P6, AMD Hammer, Intel Itanium, IBM G5 and IBM Power 4. These microprocessors use typically Error Detection and Correction (EDAC) codes and parity focused on protecting memory arrays (IYER et al, 2005).

Many other fault-tolerance techniques were already proposed for protecting ICs. The inherent cost of the robustness can vary depending on the chosen technique. The extra cost can be evident as in area and power as in performance. The manufacture cost of the IC might also be higher when a specific robust technology is used. Each technique due to its different characteristics might attend to many design objectives, therefore a detailed selection of that fault-tolerance technique to be implemented on the target system should always be done before starting the design of a robust IC.

There are fault-tolerance techniques for all design levels. They can be classified into low-level and high-level techniques.

The **low-level techniques** involve specially those techniques applicable or developed at the physical, electrical, switch or transistor levels. Such techniques usually are based on a specific technological process like Silicon-On-Insulator (SOI) or the package shielding; transistor sizing; robust memory cells; or a combination of them.

Otherwise, **high-level techniques** are those able to be used at the logical or gate; RT or micro-architectural; algorithmic; or systemic levels. They are typically based on hardware or software redundancy like Triple Modular Redundancy (TMR); Time Redundancy (TR) in hardware or software; self-checking circuits; parity; EDAC codes like Hamming Code or Reed-Solomon Code; or even a combination of them.

Robust memory cells are suggested in (CALIN; NICOLAIDIS; VELAZCO, 1996; ZHANG; SHANBHAG, 2005) and many other works. A version of TR is proposed in (KRISHNAMOHAN, MAHAPATRA, 2004) modifying only the CMOS flip-flop in such way that it samples and latches its data input at different instants within a clock

cycle. A fault-tolerance technique dedicated to FPGAs is presented in (LIMA; CARRO; REIS, 2003-a). Many concurrent checking schemes (self-checking circuits), as presented in (ANGHEL; NICOLAIDIS, 2000-a), combined with a retry procedure had already been discussed. The tolerance to SE can be achieved by a retry operation after the detection of an error. Several other design solutions for tolerating SE were proposed in (NICOLAIDIS, 1999), in which the idea is taking advantage of the temporal nature of transient faults and mitigating them by using TR.

Techniques based on TR avoid the large hardware overheads of hardware redundancy, since the same operation is computed multiple times on the same hardware (IYER et al, 2005). Nevertheless, they usually incur high performance overhead and also require additional blocks for collecting and comparing the multiple execution results.

Techniques based on any type of redundancy can fail in case of multiple faults affect the redundant parts at the same instant. However, these multiple faults usually have lower probability of occurrence. Triple or higher redundancy usually obtains a correct a correct answer through a majority-voting scheme (IYER et al, 2005). For double redundancy, the computation must restart to recover from an error.

Fault-tolerance techniques implemented in software often determine relatively high performance overheads and high error-detection latency (IYER et al, 2005). Otherwise, techniques implemented in hardware result in lower latency. Furthermore, software-implemented techniques generally are not able to observe a large part of hardware-level errors. It occurs due to masking effects as detailed in section 2.1.2.3 or even because some specific microprocessor registers usually cannot be accessed by software applications.

Many fault-tolerance techniques are designed to protect the system against faults arisen in sequential elements, i.e., to mitigate direct SEUs. However, currently as a result of the scaling and technology issues, the techniques are also developed to protect the system against faults arisen in combinational circuits, i.e., to mitigate indirect SEUs. They are particularly based on hardware and time redundancy due to the nature of the target faults.

Especially, two fault-tolerance techniques are functionally detailed in the next sections due to their closed characteristics to the purposes of this work. They are applicable at the RT level and they do not use multiple clock networks. In addition, for any application, they preserve the total number of clock cycles, even so under a fault occurrence. The TMR scheme is able to mitigate only the direct SEUs and the TR+CWSP scheme is able to mitigate SET and therefore possible indirect SEUs.

## 3.1 Triple Modular Redundancy (TMR)

The TMR scheme is the most traditional fault-tolerance technique due to its good efficiency on error detection and its simple principle. Such scheme can be considered as a high-level technique because it can be implemented on high-level modules. However, it can be modeled at lower levels.

As shown in Figure 3.1, the TMR technique consists on the triplication of the target component to protect, in this case a 1-bit register. The three resulting outputs from triplication are connected to a voter block that compares the three received data and elects that of majority. If one of the three components fails or suffers a direct SEU, in

the case of a register, the error will not be reflected in the voter output (HENTSCHKE et al, 2002).

Figure 3.1: Block diagram of the TMR scheme for a 1-bit register

Observe that, in case of the register triplication, the voter block requires at least two registers without errors to elect a correct output. Therefore for the TMR mechanism working appropriately, direct SEUs, for example, cannot occur at the same time on two or three registers of the triplicated target register.

Another weakness of this technique is when a SET pulse occurs on the combinational block. The SET pulse might propagate itself up to the three registers of the TMR scheme and cause three indirect SEUs at the same time. Thus the voter block will not provide a correct output. By this reason, another technique which mitigates such faults is mandatory, as that presented in section 3.2.

#### 3.1.1 Area and Performance Analysis

TMR technique implies in more than an increase of 200 % in area due to the component triplication. In case of the register triplication, the area related to registers is increased by 200 %. Furthermore, there is the voter that is implemented just with some OR and AND gates for each bit of the triplicated component.

In accord to Figure 3.1 and by considering only delays of the components (i.e., routing and parasitic issues are negligible), the **D**elay of the **C**ritical **P**ath of a **Non-Protected Circ**uit ( $\mathbf{D}_{C\_P\_Non-Prot\_Circ}$ ) is basically affected by the **D**elay of the **Voter** ( $\mathbf{D}_{Voter}$ ) when a TMR-based robustness is applied. It results in a **D**elay of the **C**ritical **P**ath of the **Rob**ust **Circ**uit ( $\mathbf{D}_{C\_P\_Rob\_Circ}$ ):

$$D_{C_P\_Rob\_Circ} > D_{C_P\_Non-Prot\_Circ} + D_{Voter} (3.1)$$

## 3.2 Time Redundancy (TR) + Code Word State Preserving (CWSP)

Such approach was proposed by (NICOLAIDIS, 1999) and evaluated in (ANGHEL; ALEXANDRESCU; NICOLAIDIS, 2000-b; LAZZARI; ANGHEL; REIS, 2005). It exploits the pure TR principle, in which the output of the combinational circuit is duplicated at the time domain generally by using the delay of buffers or inverters. The

two different instants of time are evaluated at two inputs of a peculiar element called Code Word State Preserving (CWSP). A block diagram of this scheme for a 1-bit register is shown in Figure 3.2.

Figure 3.2: Block diagram of the TR+CWSP scheme for a 1-bit register

The CWSP element is an asynchronous sequential circuit able to mitigate SET pulse. It compares the values at its two inputs. When they are identical, the value at its output will be updated with the value of its inputs. On the other hand, when its inputs are not identical, the value at its output will be preserved.

Supposing a SET, which potentially causes an indirect SEU, occurs on a combinational block of a system. This SET arises at the output of the combinational block like that presented in Figure 3.4. The pulse shape meets the requirements of the set-up and hold times, i.e., the latching-window of the memory element as the vertical dotted lines in Figure 3.4. For a system without the TR+CWSP protection, such pulse gives rise to an indirect SEU at the output of the register.

Figure 3.3: Timing behavior of a system without the TR+CWSP protection

In contrast, for a robust system with the TR+CWSP protection, this indirect SEU at the output of the register does not occur. As Figure 3.2 and Figure 3.4 illustrate, the CWSP element compares, by means of its two inputs, the output of the combinational block with the delayed output of the same block. The output of the CWSP element