### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

#### KLEBER HUGO STANGHERLIN

# Energy and Speed Exploration in Digital CMOS Circuits in the Near-threshold Regime for Very-Wide Voltage-Frequency Scaling

Master's thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Prof. Sergio Bampi Advisor

Prof. Valter Roesler Co-advisor

#### CIP - CATALOGING-IN-PUBLICATION

Stangherlin, Kleber Hugo

Energy and Speed Exploration in Digital CMOS Circuits in the Near-threshold Regime for Very-Wide Voltage-Frequency Scaling / Kleber Hugo Stangherlin. – Porto Alegre: PPGC da UFRGS, 2013.

68 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR–RS, 2013. Advisor: Sergio Bampi; Co-advisor: Valter Roesler.

1. Voltage-frequency scaling. 2. Energy-efficiency. 3. Power savings. 4. Near-threshold. I. Bampi, Sergio. II. Roesler, Valter. III. Energy and Speed Exploration in Digital CMOS Circuits in the Near-threshold Regime for Very-Wide Voltage-Frequency Scaling

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luís Lamb

Coordenador do PPGC: Prof. Luigi Carro

Bibliotecária-chefe do Instituto de Informática: Alexsander Ribeiro

# ENERGY AND SPEED EXPLORATION IN DIGITAL CMOS CIRCUITS IN THE NEAR-THRESHOLD REGIME FOR VERY-WIDE VOLTAGE-FREQUENCY SCALING

#### **RESUMO**

Esta tese avalia os benefícios e desafios associados com a operação em uma ampla faixa de frequências e tensões próximas ao limiar do transistor. A diminuição da tensão de alimentação em circuitos digitais CMOS apresenta grandes vantagens em termos de potência consumida pelo circuito. Esta diminuição da potência é acompanhada por uma redução da performance, reflexo da diminuição na tensão de alimentação.

A operação de circuitos digitais no ponto de energia mínima é comumente associada ao regime de operação abaixo do limiar do transistor, trazendo enormes penalidades em performance e variabilidade. Esta dissertação mostra que é possível obter 8X mais eficiência energética com uma ampla faixa dinâmica de tensão e frequência, da tensão nominal até o limite inferior da operação próximo ao limiar do transistor. Como parte deste estudo, uma biblioteca de células digitais CMOS para esta ampla faixa de frequências foi desenvolvida.

A biblioteca de células lógicas foi exercitada em um PDK comercial de 65nm para operação próximo ao limiar do transistor, reduzindo os efeitos da variabilidade sem comprometer o projeto em termos de área e energia quando operando em inversão forte. Para operar próximo e abaixo do limiar do transistor as células devem ser desenvolvidas com um número limitado de transistores em série. Nosso estudo mostra que uma performance aceitável em termos de margens de ruído estático é obtida para um conjunto restrito de células, onde são empregados no máximo dois transistores em série.

Reportamos resultados para projetos de média complexidade que incluem um filtro notch de 25kgates, um microcontrolador 8051 de 20kgates, e 4 circuitos combinacionais/sequenciais do conjunto de avaliação ISCAS. Neste trabalho, é estudada a máxima frequência atingida em cada tensão de alimentação, desde 0.15V até 1.2V. O ponto de mínima energia é demonstrado em operação abaixo do limiar do transistor, aproximadamente 0.29V, oque representa um ganho de 2X em eficiência energética comparado ao regime de operação próximo ao limiar do transistor. Embora o pico de eficiência energética ocorra abaixo do limiar do transistor para os circuitos estudados, nós também demonstramos que nesta tensão de alimentação ultra-baixa o atraso e a potência sofrem um impacto substancial devido ao aumento na variabilidade, atigindo uma degradação em performance de 30X, com respeito à operação próxima ao limiar do transistor.

**Palavras-chave:** variação de tensão e frequência, eficiência energética, economia de energia, próximo ao limiar do transistor.

# ENERGY AND SPEED EXPLORATION IN DIGITAL CMOS CIRCUITS IN THE NEAR-THRESHOLD REGIME FOR VERY-WIDE VOLTAGE-FREQUENCY SCALING

#### **ABSTRACT**

This thesis assesses the benefits and drawbacks associated with a very wide range of frequency when operation at near-threshold is considered. Scaling down the supply voltage in digital CMOS circuits presents great benefits in terms of power reduction. Such scaling comes with a performance penalty, hence in digital synchronous circuits the reduction in frequency of operation follows, for a given circuit layout, the VDD reduction.

Minimum-energy operation of digital CMOS circuits is commonly associated to the sub-VT regime, carrying huge performance and variability penalties. This thesis shows that it is possible to achieve 8X higher energy-efficiency with a very-wide range of dynamic voltage-frequency scaling, from nominal voltages down to the lower boundary of near-VT operation. As part of this study, a CMOS digital cell-library for such wide range of frequencies was developed.

The cell-library is exercised in a 65nm commercial PDK and targets near-VT operation, mitigating the variability effects without compromising the design in terms of area and energy at strong inversion. For near-VT or sub-VT operation the cells have to be designed with few stacked transistors. Our study shows that acceptable performance in terms of static-noise margins is obtained for a constrained set of cells, for which a maximum of 2-stacked transistors are allowed. In this set we include master-slave registers.

We report results for medium complexity designs which include a 25kgates notch filter, a 20kgates 8051 compatible core, and 4-combinational/4-sequential ISCAS benchmark circuits. In this work the maximum frequency attainable at each supply for a wide variation of voltage is studied from 150mV up to nominal voltage (1.2V). The sub-VT operation is shown to hold the minimum energy-point at roughly 0.29V, which represents a 2X energy-saving compared to the near-VT regime. Although energy-efficiency peaks in sub-VT for the circuits studied, we also show that in this ultra-low VDD the circuit timing and power suffer from substantially increased variability impact and a 30X performance drawback, with respect to near-VT.

**Keywords:** Voltage-frequency scaling, energy-efficiency, power savings, near-threshold.

# **LIST OF FIGURES**

| Figure 2.1:             | Systematic variations from lithography process                                                                                                                                             | 18                              |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Figure 2.2:             | Line edge roughness (LER) for polysilicon gate on devices with L=22nm and L=90nm                                                                                                           | 19                              |

| Figure 2.3:             | Random dopant fluctuations (RDF) simulated in 3D for a 30nm by 30nm MOSFET device                                                                                                          | 20                              |

| Figure 2.4:             | Thermal distribution of Intel Core Duo processor running a single core application                                                                                                         | 21                              |

| Figure 2.5:             | POWER6 dual core voltage drop during start-up; (a) Core #1 (left) as it turns on, and (b) Core #2 (right) as it turns on 4ns later                                                         | 22                              |

| Figure 2.6:             | Negative-Bias Temperature instability (NBTI) for PFET devices working under high electric fields and/or high temperatures                                                                  | 23                              |

| Figure 2.7:             | Hot electrons are accelerated through the inverted channel, generating electron-hole pairs through impact ionization which in turn may result in traps at the interface or gate dielectric | 24                              |

| Figure 2.8:             | Electromigration effects due to material movement on metal (a) wires and (b) vias                                                                                                          | 25                              |

| Figure 2.9:             | Design corners performance evaluation for sub-VT and strong-inversion.  (a) Ring-oscillator with 11 stages and fan-out of 4; (b) Cycle time in-                                            | 26                              |

| Figure 2.10:            | crease for each design corner considered                                                                                                                                                   | <ul><li>26</li><li>27</li></ul> |

| Figure 2.11:            | Timing variation histogram for the ring-oscillator in two voltage corners, 250mV and 1.2V.                                                                                                 | 27                              |

| Figure 2.12:            | Ring-oscillator timing variability zone considering both process and temperature variations                                                                                                | 28                              |

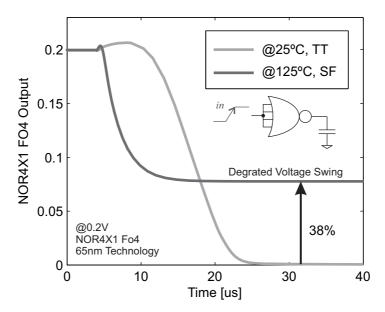

| Figure 2.13:            | Voltage swing degradation with process variation and high temperature. The pull-up static current generates a weak zero at the output.                                                     | 29                              |

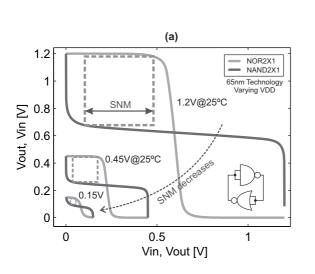

| Figure 2.14:            | Voltage transfer curves (VTC) and static-noise margins (SNM) plots, (a) multiple voltage SNM; (b) SNM variability at 1.2V; and (c) SNM variability at 0.15V                                | 30                              |

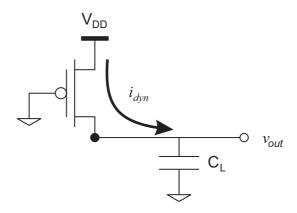

| Figure 3.1:             | Dynamic power equivalent circuit for zero slope times                                                                                                                                      | 32                              |

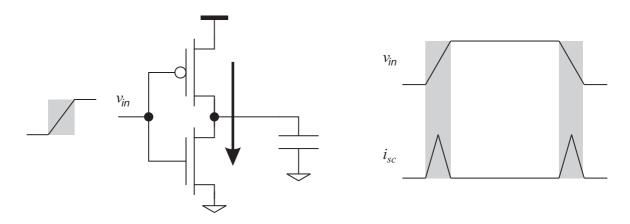

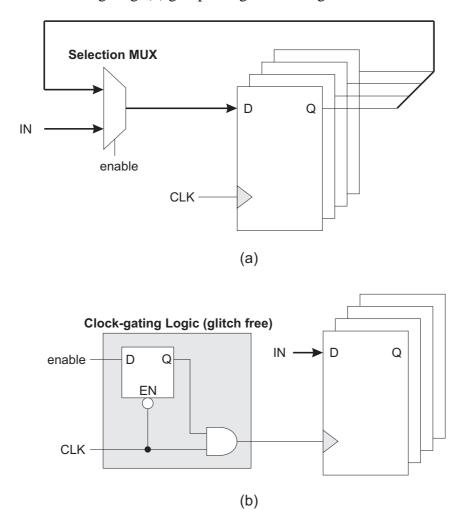

| Figure 3.2: Figure 3.3: | Short-circuit energy due to direct current with non-zero input slopes Clock gating technique poor saving energy at the clock tree; (a) group                                               | 33                              |

| Figure 3.4:             | of registers without clock gating, (b) group of registers with gated clock.<br>Operand isolation technique for energy-saving at combinational logic                                        | 34                              |

|                         | blocks                                                                                                                                                                                     | 36                              |

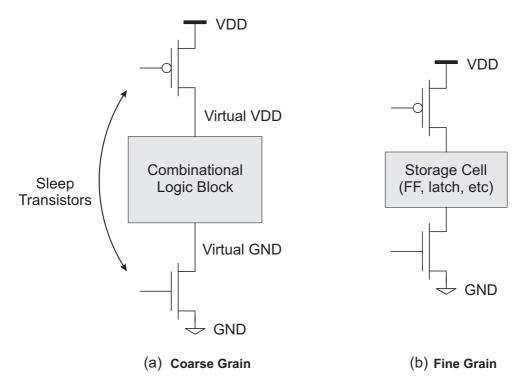

| Figure 3.5:             | Power gating technique for reducing the static power consumption,                                                                                                                                                                                                          |    |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| F! 0.6                  | with (a) coarse-grain and (b) fine-grain methodologies                                                                                                                                                                                                                     | 37 |

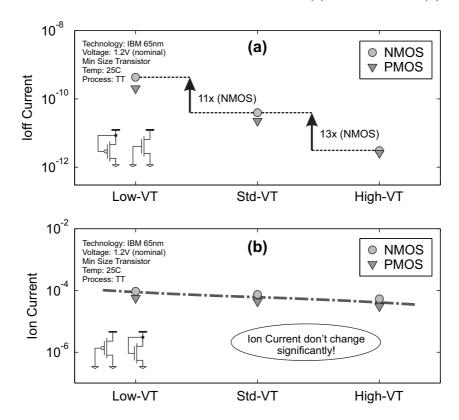

| Figure 3.6:             | Multi-VT device electrical characteristics for (a) on current and (b) off current                                                                                                                                                                                          | 38 |

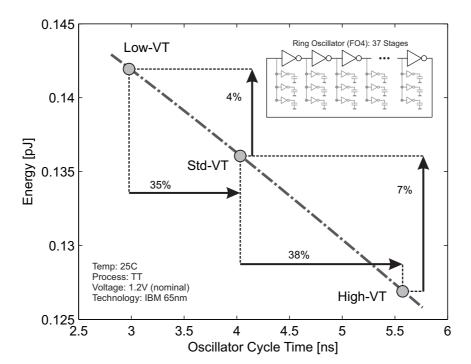

| Figure 3.7:             | Energy-speed improvements though multi-VT devices applied to a 37-stages ring-oscillator                                                                                                                                                                                   | 39 |

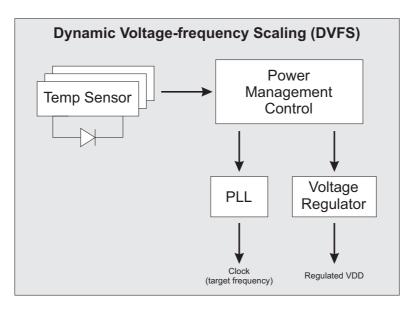

| Figure 3.8:             | Dynamic voltage-frequency scaling block diagram for support hardware.                                                                                                                                                                                                      | 40 |

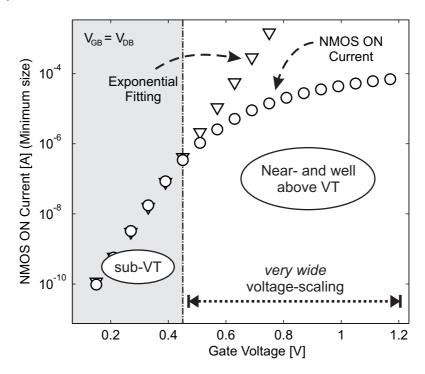

| Figure 4.1:             | Sub- and near-VT boundary definition based on the exponential fitting of a minimum sized saturated NMOS ON current (standard-VT at 25°C). For this 65nm PDK, the boundary mark is $V_{GB} = V_{DB}$ at 450mV                                                               | 42 |

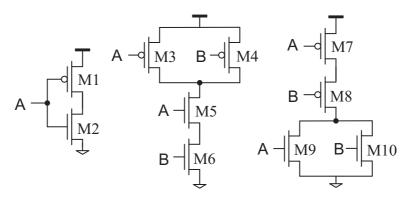

| Figure 4.2:             | Digital CMOS cell-design parameters for near-VT operation. All dimensions refer to transistor width with minimal length. The transistor                                                                                                                                    |    |

| F: 4.2                  | stack factor $ALFA$ is individually selected for each cell                                                                                                                                                                                                                 | 43 |

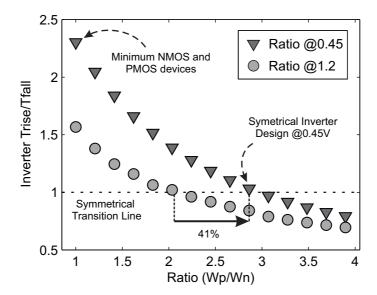

| Figure 4.3:             | Rise/Fall transition times for inverter cell versus ratio $R_{INV}$                                                                                                                                                                                                        | 44 |

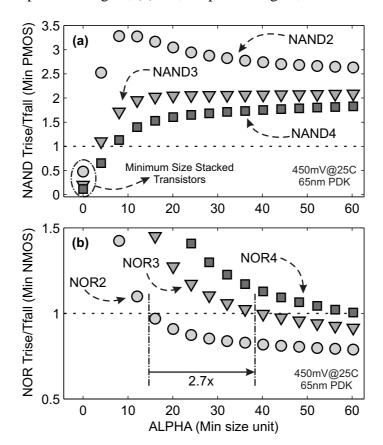

| Figure 4.4:             | Rise/Fall transition times for minimal strength gates versus ALFA                                                                                                                                                                                                          | 15 |

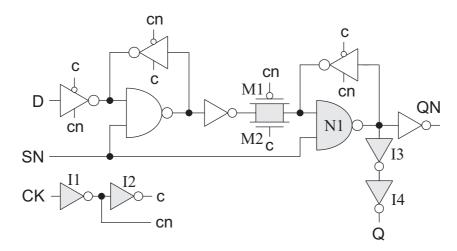

| Figure 4.5:             | stacking factor: (a) 2,3,4-input NAND gate; (b) 2,3,4-input NOR gate; Master-slave register architecture sizing. White gates are minimum size, while gray gates are optimized through simulation according to                                                              | 45 |

|                         | the sizing ranges                                                                                                                                                                                                                                                          | 46 |

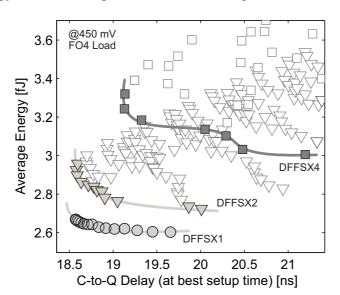

| Figure 4.6:             | Master-slave register design space for DFFS with multiple strengths X1, X2, and X4. The energy-efficient designs for each cell strength                                                                                                                                    |    |

| T: 4.5                  | are marked                                                                                                                                                                                                                                                                 | 47 |

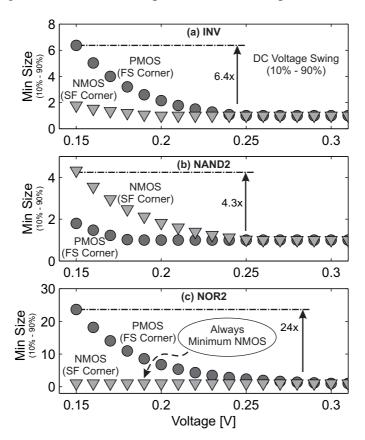

| Figure 4.7:             | Minimum transistor size (in multiples of $W_{MIN}$ ) for achieving 10% to 90% DC voltage swing: (a) Inverter; (b) 2-input NAND; (c) 2-input                                                                                                                                |    |

|                         | NOR                                                                                                                                                                                                                                                                        | 48 |

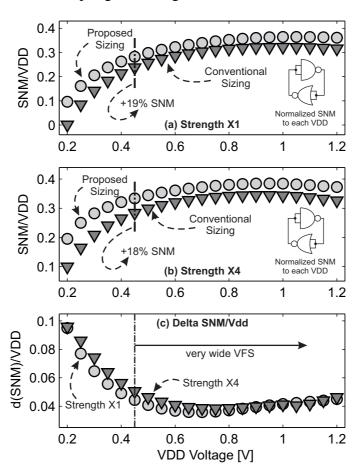

| Figure 4.8:             | Static-noise margin (SNM) of a 2-input NAND/NOR SRAM cell (normalized for each VDD). (a) NAND/NOR strength X1; (b) NAND/NO                                                                                                                                                 | OR |

|                         | strength X4; (c) Relative increment of SNM when adopting our sizing instead of the conventional one.                                                                                                                                                                       | 50 |

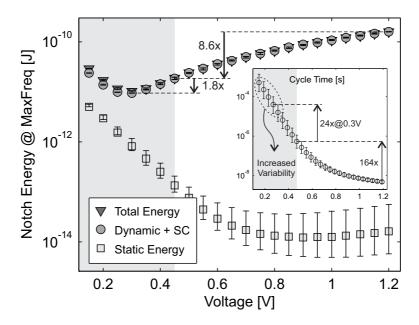

| Figure 5.1:             | Notch filter energy to process 2048 samples at maximum frequency and varying supply voltage. The inset refers to the cycle time applied for each voltage. Upper and lower error bars refers to 3-sigma process variation (SS and FF corners).                              | 52 |

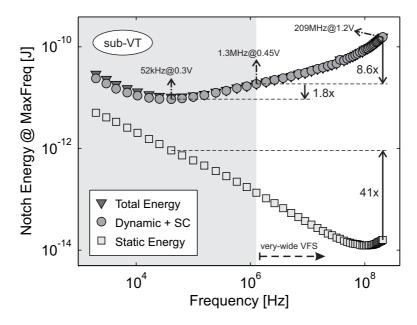

| Figure 5.2:             | Notch filter energy to process 2048 samples with varying VDD and maximum frequency (TT corner). Each point correspond to a differ-                                                                                                                                         |    |

| Figure 5.3:             | ent VDD and associates to a different frequency                                                                                                                                                                                                                            | 53 |

|                         | by the multi-mode multi corner (MMMC) analysis tool                                                                                                                                                                                                                        | 54 |

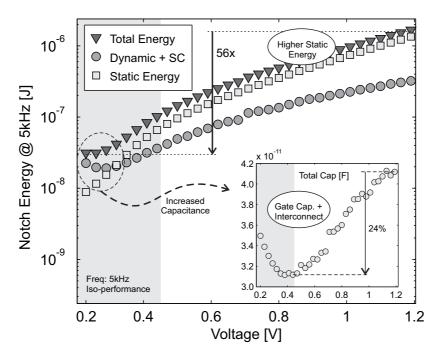

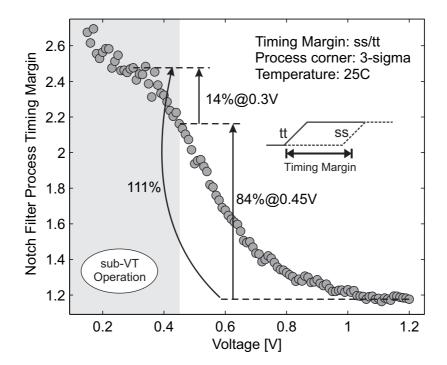

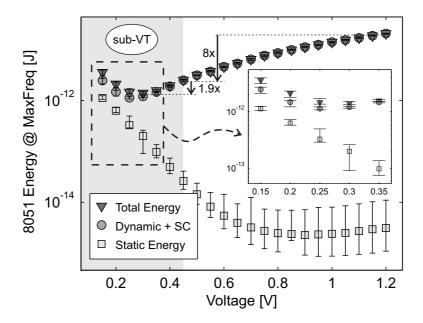

| Figure 5.4: Figure 5.5: | Notch filter timing margin (TT/SS) for 3-sigma process conditions 8051 compatible core energy versus varying VDD. The simulation environment runs 10 loop iterations of the fixed point Dhrystone benchmark. Upper and lower error bars refer to 3-sigma process variation | 55 |

|                         | (SS and FF corners)                                                                                                                                                                                                                                                        | 56 |

# **LIST OF TABLES**

| Table 3.1: | Power gating methodologies comparison                                  | 35 |

|------------|------------------------------------------------------------------------|----|

| Table 3.2: | Threshold voltage for minimum device size in 65nm CMOS Bulk            |    |

|            | PDK from IBM. Values extracted from (IBM, 2009)                        | 38 |

| Table 4.1: | Cells included on near-VT library                                      | 44 |

| Table 5.1: | Energy increase with respect to the sub-VT minimum energy point,       |    |

|            | the near-VT @0.45V and the nominal voltage @1.2V                       | 57 |

| Table 5.2: | Frequency increase with respect to the sub-VT minimum energy point     |    |

|            | performance, the near-VT @0.45V and the nominal voltage @1.2V          | 57 |

| Table 5.3: | Energy-saving results for the Notch filter, 8051 core and ISCAS bench- |    |

|            | marks. Energy in Joules, frequency in Hz, and voltage in Volts. The    |    |

|            | 'Ratio' refers to static energy ratio over total energy                | 58 |

#### LIST OF ABBREVIATIONS AND ACRONYMS

BTI Bias Temperature Instability

CMOS Complementary Metal-oxide-semiconductor

DVFS Dynamic Voltage-frequency Scaling

FET Field Effect Transistor

FFT Fast-fourier transform

FF 3-Sigma Process conditions: Fast NMOS, Fast PMOS

FO4 Fan-out of four identical loads

FPU Floating Point Unit

FS 3-Sigma Process conditions: Fast NMOS, Slow PMOS

HCI Hot Carrier Injection

IC Initial Condition

IR Current-resistance (Voltage)

LER Line-Edge Roughness

MMMC Multi-mode Multi Corner

MOSFET Metal-oxide-semiconductor Field Effect Transistor

NBTI Negative-Bias Temperature Instability

NMOS N-type MOSFET

OPC Optical Proximity Correction

PBTI Positive-Bias Temperature Instability

PDK Process Development Kit

PLL Phased-locked Loop

PMC Power management control

PMOS P-type MOSFET

PVT Process Voltage Temperature

RDF Random Dopant Fluctuations

RSCE Reverse-short channel effect

SF 3-Sigma Process conditions: Slow NMOS, Fast PMOS

SNM Static-noise Margin

SRAM Static-random access memory

SS 3-Sigma Process conditions: Slow NMOS, Slow PMOS

STA Static Timing Analysis

SoC System on chip

TDDB Time-Dependent Dielectric Breakdown

TT 3-Sigma Process conditions: Typical NMOS, Typical PMOS

V-F Voltage-frequency

VFS Voltage-frequency Scaling

VLSI Very Large Scale Integration

VR Voltage Regulator

VTC Voltage-transfer curve

VT Threshold Voltage

### **LIST OF SYMBOLS**

$\sigma$  Standard deviation

$\sigma_{VT}$  Threshold voltage standard deviation

$\mu$  Mean value

$\sigma/\mu$  Coefficient of variation

W Transistor width

L Transistor length

$W_P$  PMOS transistor width

$W_N$  NMOS transistor width

$W_{MIN}$  Minimum transistor width

$E_{DYN}$  Dynamic Energy

$E_C$  Energy stored in the capacitor

$P_{DYN}$  Dynamic power

$V_{GS}$  Gate to source voltage

$P_{STA}$  Static power

$V_{DD}$  Supply voltage

$i_{sta}$  Static current

$v_{out}$  Output voltage

$C_L$  Load capacitor

$i_{dyn}$  Dynamic current

$i_{sc}$  Short-circuit current

$v_{in}$  Input voltage

$f_{0\rightarrow 1}$  Zero-to-one frequency

$\alpha$  Switching activity factor

# **CONTENTS**

| 1 IN                                                                        | NTRODUCTION                                                                                                                                                                                                                                                                                                                                                   | 14                                                                         |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 2 P                                                                         | ROCESS, AGING, AND ENVIRONMENTAL VARIABILITY                                                                                                                                                                                                                                                                                                                  | 17                                                                         |

| 2.1                                                                         | Process Variations                                                                                                                                                                                                                                                                                                                                            | 17                                                                         |

| 2.1.1                                                                       | Lithografic Variations                                                                                                                                                                                                                                                                                                                                        | 17                                                                         |

| 2.1.2                                                                       | Random Dopant Fluctuations (RDF)                                                                                                                                                                                                                                                                                                                              | 19                                                                         |

| 2.2                                                                         | Temperature and Supply Voltage Variations                                                                                                                                                                                                                                                                                                                     | 19                                                                         |

| 2.2.1                                                                       | Thermal Management                                                                                                                                                                                                                                                                                                                                            | 20                                                                         |

| 2.2.2                                                                       | Supply Voltage Tolerance                                                                                                                                                                                                                                                                                                                                      | 20                                                                         |

| 2.3                                                                         | Temporal Variations: Aging                                                                                                                                                                                                                                                                                                                                    | 21                                                                         |

| 2.3.1                                                                       | Bias Temperature Instability (BTI)                                                                                                                                                                                                                                                                                                                            | 21                                                                         |

| 2.3.2                                                                       | Hot Carrier Injection (HCI)                                                                                                                                                                                                                                                                                                                                   | 23                                                                         |

| 2.3.3                                                                       | Time-Dependent Dielectric Breakdown (TDDB)                                                                                                                                                                                                                                                                                                                    | 24                                                                         |

| 2.3.4                                                                       | Electromigration                                                                                                                                                                                                                                                                                                                                              | 24                                                                         |

| 2.4                                                                         | Impact on Circuit Performance                                                                                                                                                                                                                                                                                                                                 | 24                                                                         |

| 2.4.1                                                                       | Ring-oscillator FO4                                                                                                                                                                                                                                                                                                                                           | 25                                                                         |

| 2.4.2                                                                       | Voltage Swing and Static-noise Margin (SNM)                                                                                                                                                                                                                                                                                                                   | 28                                                                         |

| 3 U                                                                         | LTRA-LOW POWER TECHNIQUES FOR DIGITAL CMOS CIRCUITS                                                                                                                                                                                                                                                                                                           | 31                                                                         |

|                                                                             |                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| 3.1                                                                         |                                                                                                                                                                                                                                                                                                                                                               | 31                                                                         |

|                                                                             | Power and Energy Components                                                                                                                                                                                                                                                                                                                                   | 31<br>31                                                                   |

| 3.1                                                                         | Power and Energy Components                                                                                                                                                                                                                                                                                                                                   |                                                                            |

| <b>3.1</b> 3.1.1                                                            | Power and Energy Components                                                                                                                                                                                                                                                                                                                                   | 31                                                                         |

| <b>3.1</b> 3.1.1 3.1.2                                                      | Power and Energy Components                                                                                                                                                                                                                                                                                                                                   | 31<br>32                                                                   |

| 3.1.1<br>3.1.2<br>3.1.3                                                     | Power and Energy Components  Dynamic Energy  Short-circuit Energy  Static Energy                                                                                                                                                                                                                                                                              | 31<br>32<br>33                                                             |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2                                       | Power and Energy Components  Dynamic Energy                                                                                                                                                                                                                                                                                                                   | 31<br>32<br>33<br>33                                                       |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1                                                 | Power and Energy Components  Dynamic Energy  Short-circuit Energy  Static Energy  Circuit-level Techniques  Clock Gating  Operand Isolation                                                                                                                                                                                                                   | 31<br>32<br>33<br>33<br>34                                                 |

| 3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.2.2                            | Power and Energy Components  Dynamic Energy  Short-circuit Energy  Static Energy  Circuit-level Techniques  Clock Gating                                                                                                                                                                                                                                      | 31<br>32<br>33<br>33<br>34<br>35                                           |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1 3.2.2 3.2.3                                     | Power and Energy Components  Dynamic Energy Short-circuit Energy Static Energy Circuit-level Techniques Clock Gating Operand Isolation Power Gating                                                                                                                                                                                                           | 31<br>32<br>33<br>33<br>34<br>35<br>35                                     |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5                         | Power and Energy Components  Dynamic Energy Short-circuit Energy Static Energy Circuit-level Techniques Clock Gating Operand Isolation Power Gating Multi-VT Devices                                                                                                                                                                                          | 31<br>32<br>33<br>33<br>34<br>35<br>35<br>37                               |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5                         | Power and Energy Components  Dynamic Energy Short-circuit Energy Static Energy Circuit-level Techniques Clock Gating Operand Isolation Power Gating Multi-VT Devices Voltage-Frequency Scaling (VFS)                                                                                                                                                          | 31<br>32<br>33<br>34<br>35<br>35<br>37<br>39                               |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 4 N                     | Power and Energy Components  Dynamic Energy Short-circuit Energy Static Energy Circuit-level Techniques Clock Gating Operand Isolation Power Gating Multi-VT Devices Voltage-Frequency Scaling (VFS)                                                                                                                                                          | 31<br>32<br>33<br>34<br>35<br>35<br>37<br>39                               |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 4 N                     | Power and Energy Components  Dynamic Energy Short-circuit Energy Static Energy Circuit-level Techniques Clock Gating Operand Isolation Power Gating Multi-VT Devices Voltage-Frequency Scaling (VFS)  IEAR-VT CELL-LIBRARY FOR DYNAMIC VFS Cell-design for Near-VT Regime                                                                                     | 311<br>322<br>333<br>343<br>355<br>357<br>399<br>411<br>411                |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 4 N 4.1 4.1.1           | Power and Energy Components  Dynamic Energy Short-circuit Energy Static Energy Circuit-level Techniques Clock Gating Operand Isolation Power Gating Multi-VT Devices Voltage-Frequency Scaling (VFS)  IEAR-VT CELL-LIBRARY FOR DYNAMIC VFS Cell-design for Near-VT Regime Near-threshold and very wide VFS                                                    | 311<br>322<br>333<br>343<br>353<br>373<br>3941<br>411                      |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 4 N 4.1 4.1.1 4.1.2     | Power and Energy Components  Dynamic Energy Short-circuit Energy Static Energy Circuit-level Techniques Clock Gating Operand Isolation Power Gating Multi-VT Devices Voltage-Frequency Scaling (VFS)  IEAR-VT CELL-LIBRARY FOR DYNAMIC VFS Cell-design for Near-VT Regime Near-threshold and very wide VFS Digital CMOS Sizing at Near-VT Robustness Analysis | 31<br>32<br>33<br>33<br>34<br>35<br>35<br>37<br>39<br>41<br>41<br>41<br>42 |

| 3.1.1 3.1.2 3.1.3 3.2 3.2.1 3.2.2 3.2.3 3.2.4 3.2.5 4 N 4.1 4.1.1 4.1.2 4.2 | Power and Energy Components  Dynamic Energy Short-circuit Energy Static Energy Circuit-level Techniques Clock Gating Operand Isolation Power Gating Multi-VT Devices Voltage-Frequency Scaling (VFS)  IEAR-VT CELL-LIBRARY FOR DYNAMIC VFS Cell-design for Near-VT Regime Near-threshold and very wide VFS Digital CMOS Sizing at Near-VT                     | 311<br>322<br>333<br>343<br>355<br>377<br>399<br>411<br>411<br>422<br>460  |

| 5 E   | NERGY-SPEED EXPLORATION FOR VERY-WIDE VFS                           | 51 |

|-------|---------------------------------------------------------------------|----|

| 5.1   | Power Analysis Methodology                                          | 51 |

| 5.2   | Results on very wide range of VFS                                   | 51 |

| 5.2.1 | Notch Filter: Maximum Frequency, Iso-Performance, and Timing Margin | 52 |

| 5.2.2 | 8051 Core: Maximum Frequency with Dhrystone Benchmark               | 54 |

| 5.2.3 | ISCAS Benchmark: Minimum-energy and Near-VT Analysis                | 55 |

| 6 C   | ONCLUSION                                                           | 59 |

| REFE  | ERENCES                                                             | 60 |

| APPE  | ENDIX A INTRODUÇÃO                                                  | 63 |

| APPE  | ENDIX B RESUMO DA DISSERTAÇÃO                                       | 66 |

| APPE  | ENDIX C CONCLUSÃO                                                   | 68 |

#### 1 INTRODUCTION

CMOS circuit design was historically focused on performance. High-end processors frequency kept increasing until the year of 2004, when reached near 4.0GHz – dissipating 120W of power in a single die. The performance-only oriented approaches for chip design no longer sustained the demanded performance increase at reasonable cost. The power scenario change was in fact caused by the failure of Dennard scaling (DENNARD et al., 1974), where intrinsic material parameters like junction potential and device threshold imposed a barrier for scaling the voltage across process nodes as Dennard predicted, thus increasing chip power-density every new technology. For overcoming this barrier, a new power-oriented design methodology has been developed. Techniques for saving power in VLSI designs vary from process optimizations, layout, circuit level, architectural, up to software stack and application.

From the architectural point of view, a significant change occurred in order to continue improving performance: the shift to multicores chips. Even though it required a whole new programming paradigm, multicore designs enabled a continued increase in performance, without compromising the design in terms of dissipated power. However, recent research points out that regardless of chip organization and topology, multicore scaling is also power limited; at the 22nm node, 21% of the transistors in a chip should be powered-off to provide a chance of dissipating the heat, and this number grows to more than 50% at the 8nm node (ESMAEILZADEH et al., 2011). In addition to this very critical power-density issue, an increasing number of applications demand ultra-low-energy solutions, able to maximize the battery lifetime for autonomous systems like sensor networks, wearable devices, lightweight sensors, ubiquitous environment monitoring, and so on.

For minimizing the power and energy of CMOS circuits, several techniques have been proposed such as: clock gating, for reducing unnecessary clock toggles in group of registers; operand isolation, for avoiding unnecessary glitch propagation through datapaths; power gating, for reducing static current and thus improving static energy consumption; multi-threshold devices, for reducing static energy in non-critical paths; and finally, voltage-frequency scaling (VFS), which reduces voltage and frequency, seeking to explore the bursty nature of most workloads. These techniques enable the design of processors that serve a wide spectrum of performance and energy dissipation range, providing highly configurable solutions to trade-off energy and performance – without compromising time-to-market.

This work dedicates special attention to the VFS technique, which enables a *dynamic* change in key aspects of the core such as voltage and frequency. Thus, providing the integrated run-time capability of power-performance exploration according to the workload. Notably, in most applications the workload varies from full performance (like in process-

ing/transmit modes), to power-savvy operation in idle modes. In this scenario of varying workloads, dynamic VFS emerges as a preeminent energy-saving technique, causing a dramatically, monotonic decrease in power, with one order of magnitude energy-savings. The industry however, explores a narrow range of dynamic VFS in high-end processors, which usually translates to a 2X-3X frequency variation.

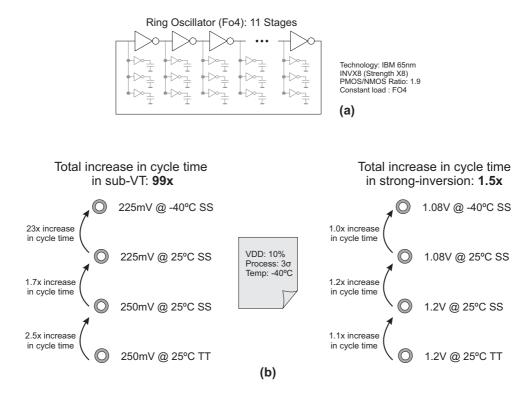

The limited employment of the VFS technique in industry occurs due to process and environmental variability effects. These variability issues are also present at nominal voltage, but present a dramatically increased impact at lower voltages, where MOSFET devices work in sub- and near-VT regimes. When operating in those regimes, the current shows an exponential dependence on device's threshold voltage, which in turn, presents a very significant coefficient of variability in recent technology nodes (sub-100nm) (ZHAI et al., 2005). To illustrate, a design that operates at 250mV, should account for 2.5X increase in cycle-time due to 3-sigma process variation, 1.7X due to 10% supply voltage variation, and 23X for the -40°C temperature corner – resulting in a total timing variation of 99X. The same design at nominal voltage, under the same conditions, should account only for an overall 1.5X variation.

This master thesis seeks to demonstrate the challenges and advantages of operating robust digital CMOS circuits in the near-VT regime, assuming a dynamic VFS case. In order to overcome the variability effects at ultra-low voltages, and ensure robust operation with respect to process and environmental variations, circuits that operate in sub- and near-VT regimes require the careful design of a robust, variation aware, digital cell-library. The designed cells should take into account all the low voltage effects that emerge when operating in such reduced supply voltages, e.g., reduced voltage swings, degraded static-noise margins, and higher dynamic/static current ratio. This new cell-library designed for ultra-low voltages may present slight penalties in performance and area when operating at nominal voltage with respect to commercial libraries, but the achieved energy-savings at lower voltages are substantial, and offer a new perspective for low-power CMOS circuit design.

Related works in (CHANDRAKASAN; SHENG; BRODERSEN, 1992), search for the lowest possible supply voltage, while the throughput degradation is compensated with architectural parallelism. In (CALHOUN; WANG; CHANDRAKASAN, 2005), the authors derive equations for the minimum energy point and show that, theoretically, minimum size devices are optimum for reducing energy. The work in (WANG; CHAN-DRAKASAN, 2005) demonstrates, using a FFT processor, the design methodology for a sub-VT cell-library and SRAM memory. The FFT processor is fabricated into a 0.18u technology, achieving for 16-bit/1024 points design with minimum energy point at 180mV and 10kHz frequency. In (KWONG; CHANDRAKASAN, 2006), the authors propose a new transistor sizing methodology, based on Monte Carlo simulations and static-noise margin measurements. The results showed that upsizing is a need for robust sub-VT operation. The simulation-based sizing methodology proposed in (KEANE et al., 2006) uses SPICE DC simulations to find the best transistor widths in order to improve staticnoise margins. The author also derives a closed form solution for stacked devices width. The sizing of such ultra-low voltage circuits may also depend on process technology, i.e., in (KIM et al., 2007) an optimal sub-VT sizing is showed to use a larger than minimal transistor channel length due to reverse-short channel effect (RSCE).

Regarding ultra-low voltage SRAM design, a 10T SRAM cell is proposed in (CAL-HOUN; CHANDRAKASAN, 2007). The SRAM memory is demonstrated working properly at 380mV in 65nm CMOS. In (KIM et al., 2008) the 10T cell is showed to work at

0.2V in 130nm CMOS. From the circuit topology point of view, the 10T SRAM cell separates the read and write lines, and inserts an additional read buffer for improved bitline sensing during read operations. Even though the 10T cell operates well in deeply scaled supply voltages, the increased area due to the higher number of transistors in the cell still defines a strong limitation for its widely adoption. Even the later improved 8T cell design proposed in (VERMA; CHANDRAKASAN, 2008) is not as dense as the traditional 6T cell. In (HE et al., 2010) a SIMD processor that uses a 10Mbit SRAM memory is presented; memory density issues lead the designers to use an onchip 6T SRAM memory, which lies in a separate voltage island that does not scale.

Other strategies have also been recently developed for variability mitigation at circuit level. In (LIU; RABAEY, 2013) a neural signal processor is proposed using asynchronous design techniques, thus the critical path delay may theoretically be the minimum for any process and environmental conditions. Another demonstration of circuit level techniques for variability mitigation is presented in (LEFURGY et al., 2011), where a critical path monitor coupled with the clock generation circuitry optimizes the processor guardband time, which depends on many sources of timing deviations, e.g. process and environmental conditions, aging, workload, etc.

Recent works have demonstrated processors working under dynamic VFS. In (JAIN et al., 2012), an IA-32 microprocessor fabricated in 32nm CMOS technology works from 280mV up to 1.2V. The performance varies 3-orders of magnitude, from 3MHz up to 915MHz, enabling a 4.7X energy-efficiency variation. In (HSU et al., 2012), a reconfigurable 4-way to 32-way SIMD vector permutation engine is demonstrated on 22nm CMOS working from 240mV up to 1.1V. The performance varies from 15MHz up to 2.5GHz, while minimum energy VDD point provides a 9X greater energy-efficiency than that attainable at the nominal supply voltage.

This thesis is organized as follows: Chapter 2 discusses the major sources of variability, including process, environmental, and aging effects. This chapter also includes a quantitative analysis of variability for ultra-low power circuits from a design perspective. Chapter 3 brings a brief overview of the major techniques for ultra-low power CMOS circuit design, including clock gating, operand isolation, power gating, multi-VT devices, and dynamic VFS. Chapter 4 shows the design methodology used to develop this near-VT cell-library. Chapter 5 reports the methodology used for simulation, and list the obtained energy savings achieved with our developed near-VT cell library for dynamic VFS. Finally, Chapter 6 presents the conclusions of this work.

# 2 PROCESS, AGING, AND ENVIRONMENTAL VARIABIL-ITY

Advanced process nodes present an increasing challenge for the circuit designer with respect to variability. This chapter discusses the main sources of variation in CMOS circuits, including systematic sources through lithography, and also statistical as the dopant originated variations, random dopant fluctuations (RDF). The environmental variations are also discussed, and focus on thermal and supply voltage conditions. Regarding CMOS circuits reliability, temporal variations are also briefly explored through bias temperature instability, hot carrier injection, and time-dependent dielectric breakdown. The end of this chapter presents some quantitative analysis of process and environmental variability using a study case of a ring oscillator.

#### 2.1 Process Variations

The process variations occur due to limited control over the semiconductor fabrication processes. Even though variations during fabrication have always occurred, its impact on circuit design has significantly increased in decananometer CMOS (sub-100nm). These variations affect the devices electrical characteristics, resulting in variations which may decrease performance or cause a failure, reducing the yield and increasing the cost. They can be categorized into *systematic* and *statistical* natures. The systematic variations are often related to lithography, and repeat from chip-to-chip, causing a constant offset on device characteristics. The statistical variations, on the other hand, produce chips with different characteristics according to some statistical distribution. This section presents a brief overview of the two major sources of process variations, both systematic and statistical: lithografic and dopant, respectively.

#### 2.1.1 Lithografic Variations

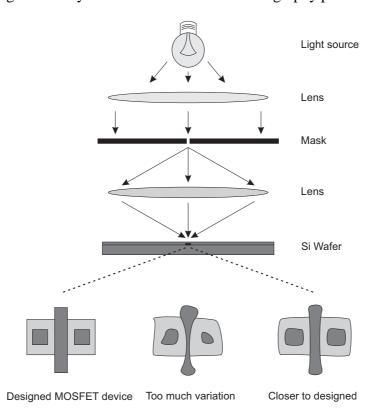

Variations due to lithography depend on the physical design, and are related to imperfections on the employed tool. Figure 2.1 shows a simplified view of the lithografic apparatus required to pattern a MOSFET device, including gate, active diffusion region, contacts, vias, and interconnects. The lithography is currently employing a light source of 193nm wavelength, which is a very large wavelength considering the device features being printed on decananometer CMOS. Thus, for achieving high yield lithography, advanced lens systems and mathematical algorithms, such as optical proximity correction (OPC) are used to enable a reliable device patterning over the silicon wafer (BHUNIA; MUKHOPADHYAY, 2011).

One of the major sources of variations related to lithography is Line-Edge Roughness

Figure 2.1: Systematic variations from lithography process.

Source: Modified from (BHUNIA; MUKHOPADHYAY, 2011).

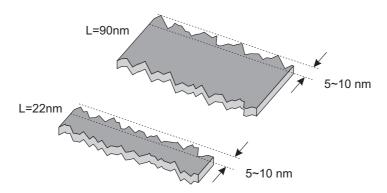

Figure 2.2: Line edge roughness (LER) for polysilicon gate on devices with L=22nm and L=90nm.

Source: Modified from (BHUNIA; MUKHOPADHYAY, 2011).

(LER), which appears as an edge roughness on the gate of MOSFET devices (shown in Figure 2.2). In addition to lithography itself, this effect is also caused by the etching tools and depends on material properties. The traditional polysilicon material for example, has varied grain sizes from 5 to 10nm. Similar roughness is expected on metal gates as well. The impact of LER is much more significant in advanced nodes due to this intrinsic variation, e.g., considering the same LER roughness, a 90nm gate length device will present a smaller variation impact than a 20nm gate length. From a circuit designer perspective, the LER impact may be seen as an increased threshold voltage variation. In order to mitigate such variation, one approach is to increase the device area, since it is well known that the standard deviation of threshold voltage is proportional to the inverse of square root of the area, as stated by Equation 2.1. (ASENOV et al., 2002).

$$\sigma_{VT} \propto \frac{1}{\sqrt{WL}}$$

(2.1)

#### 2.1.2 Random Dopant Fluctuations (RDF)

FET devices are doped with impurities to control the transistor's electrical properties, like short-channel effects and threshold-voltage. The statistical nature of the ion implantation process together with the decreasing feature size of MOSFETs made the Random Dopant Fluctuation (RDF) the major contributor on threshold-voltage variability. The variations are not only caused by the number of dopants on the channel, but also by their positions. When a FET is doped with impurities, the number of dopant atoms and their placements can not be controlled preciselly, posing an enormous challenge for decananometer CMOS with very small device areas. Figure 2.3 shows the result of a 3D simulation for a 30nm by 30nm MOSFET device, where the impurity atoms clearly diffuse across the silicon wafer.

# 2.2 Temperature and Supply Voltage Variations

Besides process originated variabilities, a circuit may also be influenciated by environmental conditions with respect to temperature and supply voltage. The device current is dictated by the voltages on its terminals and hence influenciated by the supply voltage.

Gate

Drain

Dopants difusing through Silicon

Figure 2.3: Random dopant fluctuations (RDF) simulated in 3D for a 30nm by 30nm MOSFET device.

Source: Modified from A. Brown/University of Glasgow.

In addition, the threshold voltage and channel mobility also heavily depend on the operating temperature. Thus, these environmental conditions contribute for the overall design variability, requiring careful analysis from the circuit designer. This section reviews the major environmental variation sources; temperature and voltage.

#### 2.2.1 Thermal Management

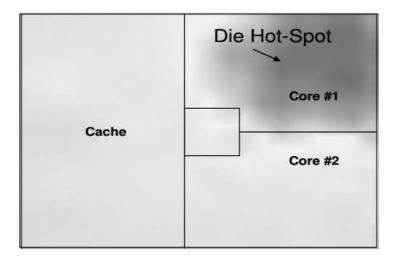

The thermal profile at circuit level depends on switching activities and capacitive load. High activity blocks such as clock trees will present higher temperatures than low-activity ones, such as SRAMs. A large capacitive load on a block also implies a higher current, resulting in increased temperatures as well. From a system designer perspective, the workload may influenciate the spatial thermal distribution, e.g., consider a multi-core system where some of the cores are idle while others are performing intense computations; the power management algorithm should distribute tasks properly in order to balance this temperature distribution. Regarding the 3D stacking technology, much has been said about the cooling efficiency, which is very degraded for the devices far away from the heat sink. One approach for handling this issue is to place the lower activity circuits far from the heat sink, while the power-hungry components will be closer to it. Figure 2.4 shows the thermal distribution of a single core application that stresses the floating point unit (FPU) running on a Intel Core Duo processor (ROTEM et al., 2006). Note that in order to generate this thermal gradient, more than one temperature sensor is needed into the same chip, hence it is possible to capture the temperature gradient between cache, Core #2 and Core #1 (which is depicted as the hot spot).

#### 2.2.2 Supply Voltage Tolerance

The power grid plays a very important role with respect to timing variability. A correctly designed power distribution network delivers a stable supply voltage for all por-

Figure 2.4: Thermal distribution of Intel Core Duo processor running a single core application.

Source: (ROTEM et al., 2006).

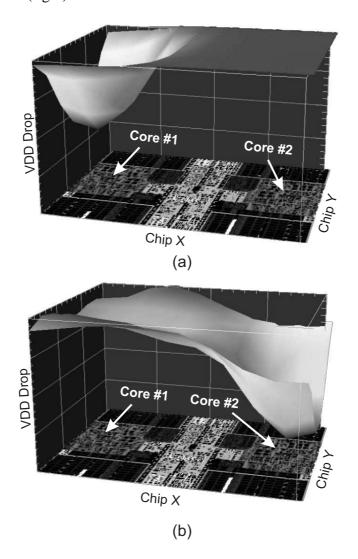

tions of the chip, with adequate current densities to mitigate electromigration (see Section 2.3.4). One of the major concerns for a robust chip design is to minimize the voltage drop across the power grid, also known as IR-drop. An IR-drop aware design must address both the steady and the static currents, creating a power grid with adequate resistance for the current demands of the design, which may vary substantially between blocks of a single chip. Figure 2.5 shows the voltage drop of a POWER6 dual core processor during start-up. The start-up was splitted into two phases, where the Core #2 turns on 4ns after Core #1. This approach was adopted in order to reduce the voltage drop due to high start-up current. Simulation measurements indicate that the noise wave from Core #1 takes only 4ns to reach Core #2, 9mm away from the first core.

# 2.3 Temporal Variations: Aging

Once a chip is fabricated, tested, packaged, and shipped to the costumers, it is expected to work during its life time. Even though a chip does not have moving parts as mechanical machines do, it still suffers from aging effects. The movement of electrons and holes in a semiconductor may produce physical changes which affect the FET's behavior. It is important to mention that every aging mechanism accelerates under large electric fields and high temperature – promoting near-VT operation from the reliability point of view due to its low voltages and most likely lower temperature. The major contributors to aging in FET devices are briefly covered in this section, including Bias Temperature Instability, Hot Carrier Injection, and Time-Dependent Dielectric Breakdown. In addition to this FET related effects, another important phenomenon also discussed in this section is named electromigration and may produce severe injures to chip interconnect, especially when associated with high temperatures.

#### 2.3.1 Bias Temperature Instability (BTI)

The Bias Temperature Instability (BTI) is the phenomenon where high electric fields and/or high temperature stress the MOSFET gate changing the VT of the device (DEAL

Figure 2.5: POWER6 dual core voltage drop during start-up; (a) Core #1 (left) as it turns on, and (b) Core #2 (right) as it turns on 4ns later.

Source: Modified from (FRANCH et al., 2008).

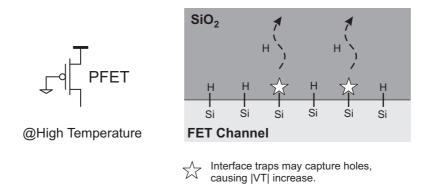

Figure 2.6: Negative-Bias Temperature instability (NBTI) for PFET devices working under high electric fields and/or high temperatures.

Source: Modified from (BHUNIA; MUKHOPADHYAY, 2011)

et al., 1967). It is classified into two categories: Negative-BTI (NBTI) and Positive-BTI (PBTI), one that accounts for PMOS and the other for NMOS devices, respectively. Both BTI types relate to the instability induced in a FET due to generation of traps at FET channel and gate dielectric interface. Those traps occur due to the interface of two very different materials: the highly ordered crystalline Si at the FET channel and the amorphous  $SiO_2$  or high-k dielectric. This rough interface results in some dangling silicon atoms from the channel due to unsatisfied chemical bonds. These dangling atoms are interface traps which can lead to poor performance due to charge trapping and scattering. For mitigating those traps in a PMOS device and thus enhance device performance, FETs are hydrogen annealed during fabrication after the formation of the interface between Siand  $SiO_2$ . Hydrogen gas diffuses to the interface binding themselves to the dangling silicon atoms, thus passivating the interface traps. Figure 2.6 shows the NBTI phenomenon, which takes place when PMOS devices are under high electric fields and/or high temperature stress, under such conditions the Si-H bonds can break, and this dissociation will re-generate those interface traps that were passivated during the fabrication process. These new interface traps can capture holes in an inverted PFET channel resulting in performance degradation, which may be modeled as an increase in threshold voltage. The PBTI on the other hand, relates to the NFET devices, and has become relevant only in advanced nodes where high-k dielectric is introduced.

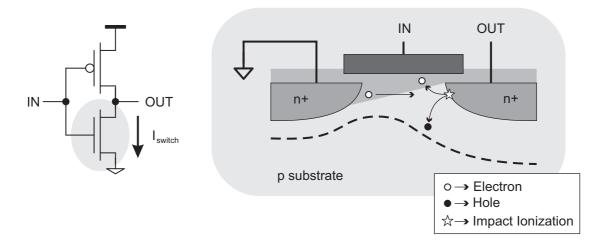

#### 2.3.2 Hot Carrier Injection (HCI)

Considering an NFET of a static CMOS inverter as shown in Figure 2.7. At the begining of the input switching from high voltage to ground, the output node starts to discharge through the NMOS device. The first few carriers passing through the inverted channel are accelerated under a very high electric field. Some of the accelerated electrons (hot electrons) gain high kinetic energy and, near the drain junction, generate an additional secondary electron-hole pair through impact ionization. Both the primary and secondary carriers may gain enough energy to be injected into the  $Si - SiO_2$  interface, or even accumulate traps in the gate dielectric itself. These traps are electrically active and capture carriers, resulting in increased threshold voltage. The HCI occurs in both NMOS and PMOS, being more prominent in the NMOS due to the lower potential barrier at the gate dielectric interface compared to holes. Note in Figure 2.7 that the hole generated by

Figure 2.7: Hot electrons are accelerated through the inverted channel, generating electron-hole pairs through impact ionization which in turn may result in traps at the interface or gate dielectric.

Source: Modified from (BHUNIA; MUKHOPADHYAY, 2011).

impact ionization flows back to the substrate. Therefore, excessive substrate current may be an indication of HCI degradation (BHUNIA; MUKHOPADHYAY, 2011).

#### 2.3.3 Time-Dependent Dielectric Breakdown (TDDB)

The TDDB effect refers to the gate dielectric breakdown due to high vertical electric field, which induces a time and usage dependent formation of traps at the gate dielectric. These traps may join together creating a conductive path from gate contact to the inverted channel, causing the gate dielectric breakdown. This phenomenon is of increasing concern due to continued scaling of gate dielectric thickness, i.e. less defects required to produce a breakdown. One may measure this aging mechanism by sensing gate current, which should hold an increase over the usual gate tunneling current.

#### 2.3.4 Electromigration

High *direct* current density in a metal wire, over a substantial time period, may cause transport of ions. Eventually, this causes the wire to break or to short circuit with another wire as show in Figure 2.8. This phenomenon takes a considerable amount of time to occur, and it is named electromigration. Even though the movement of material occurs in all wires of a circuit, electromigration only affects the wires under direct current stress, e.g. supply rails. In addition to current density, high temperature also increases the rate of degradation. Thus, from a design perspective, the most effective way to address electromigration is to use strict wire-sizing guidelines, according the estimated chip's temperature ranges (RABAEY; CHANDRAKASAN; NIKOLIC, 2003).

## 2.4 Impact on Circuit Performance

The process and environmental variabilities impose great challenges on circuit design for near-VT operation. This section first evaluates the variability impact on circuit performance for the employed Process Development Kit (PDK): 65nm CMOS Bulk from IBM.

Figure 2.8: Electromigration effects due to material movement on metal (a) wires and (b) vias.

(a) Line-open failure

(b) Open failure in contact plug.

Source: (RABAEY; CHANDRAKASAN; NIKOLIC, 2003).

The study case circuit for variation-aware designs is a ring-oscillator with fan-out of 4 (FO4). Typical design specifications are used for constraining the analysis: 10% supply voltage variation is allowed, 3-sigma process variations, and temperature corners at -40°C and 125°C. Also, this section brings a brief description of voltage swings and static-noise margins, which are crucial for evaluating the robustness of an ultra-low voltage design.

#### 2.4.1 Ring-oscillator FO4

The ring-oscillator depicted in Figure 2.9 (a) is used as study case for evaluating the variability impact. The simulations are performed using a SPICE simulator and a 65nm CMOS Bulk PDK from IBM. The transistor model used is BSIM4. The inverter ratio  $(W_P/W_N)$  is tuned for 1.9, resulting in nearly symmetrical rise and fall transitions at 150mV. The inverter size is equal to 8 times the minimum size (strength X8). The total number of stages is 11, a prime number to avoid harmonics during operation. Every oscillator stage has a FO4 load. This whole ring-oscillator configuration was thought to be a reasonable approximation of timing paths found in typical VLSI designs. Considering the process and environmental specifications, the circuit was evaluated at the -40°C and  $125^{\circ}$ C, with 3-sigma process variation, and 10% voltage variation.

Figure 2.9 (b) presents a summary of the timing impact on sub-VT operation at 250mV compared to strong inversion at 1.2V. The analysis starts on the bottom of the first column, from typical process conditions (TT), typical voltage for this sub-VT analysis (250mV), and room temperature (25°C). Only by assuming 3-sigma process variation, the cycletime increases 2.5X. Another 1.7X for 10% voltage reduction, and finally, 23X for the -40°C temperature corner. Thus the sub-VT design should be aware that a 99X timing deviation is indeed possible. The strong-inversion design, on the other hand, faces much smaller timing variations. The total increase in cycle-time for strong-inversion is 1.5X. Even though the variation in strong inversion is much smaller than sub-VT, it still shows a 50% impact on typical circuit timing for this 65nm PDK.

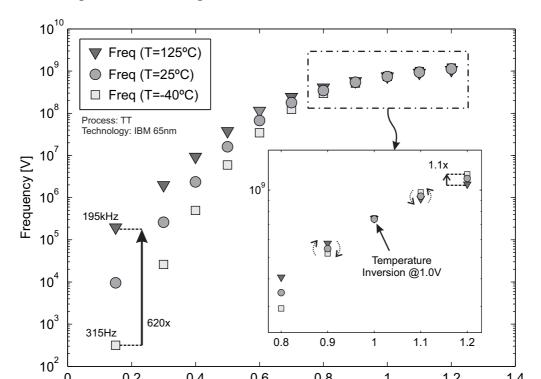

Figure 2.9 (b) shows that the temperature variation has a dramatical impact on timing at sub-VT voltages. In Figure 2.10, a detailed view on this temperature impact is provided for the studied ring-oscillator. A 620X timing variation at 150mV is observed,

Figure 2.9: Design corners performance evaluation for sub-VT and strong-inversion. (a) Ring-oscillator with 11 stages and fan-out of 4; (b) Cycle time increase for each design corner considered.

from 195kHz in the fast case at 125°C to 315Hz in the slow case at -40°C. Figure 2.10 also shows the *temperature inversion* phenomenon, which happens at 1V and swap the fast/slow temperature corners. This inversion point is dictated by two different effects: the decrease of mobility and VT with high temperature. The first slows the circuit down at high temperature, while the second speeds the circuit up at high temperature. The decrease of VT with high temperatures dominates at voltages lower than 1V, while the decrease of mobility with high temperatures dominates at voltages higher than 1V.

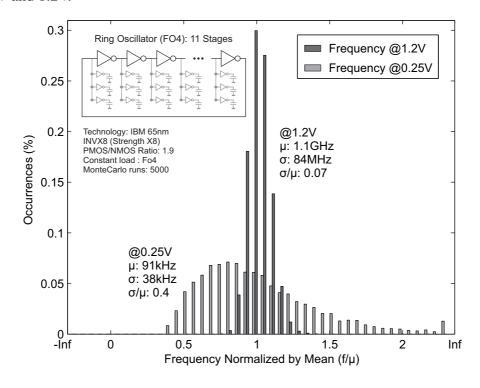

Figure 2.11 explores the statistical nature of the timing data extracted from the analyzed circuit. Figure 2.11 shows the timing distribution of the same ring-oscillator operating at 250mV and at 1.2V. This analysis was performed running 5000 Monte Carlo simulations. The horizontal axis was normalized for better visualization. Regarding the 1.2V analysis, it shows a well shaped bell curve, centered at 1.1GHz with 84MHz frequency deviation and  $\sigma/\mu$  of 0.07. The 250mV analysis on the other hand, shows the shape of a lognormal distribution, centered at 91kHz, with 38kHz frequency deviation and  $\sigma/\mu$  of 0.4.

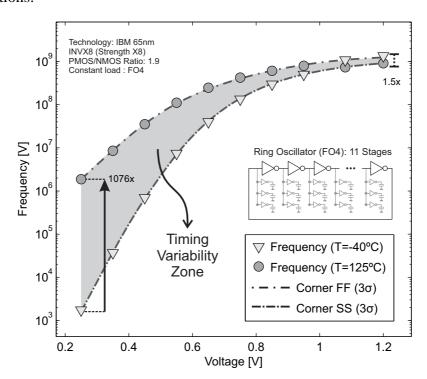

Figure 2.12 shows a the fast and slow cases for the ring-oscillator frequency, considering -40°C and 125°C for temperature variation and 3-sigma for process variation. The plot clearly delimits a wide timing variability zone, which presents a 1076X increase on cycle time (from slow to fast) at the 150mV voltage corner. Designs operating at the near-VT regime should be aware of this significantly increased timing variability.

Figure 2.10: Ring-oscillator evaluated under different temperature corners. The inset shows the temperature inversion phenomenon.

Figure 2.11: Timing variation histogram for the ring-oscillator in two voltage corners, 250mV and 1.2V.

0.6

8.0

Voltage [V]

1

1.2

1.4

0.2

0

0.4

Figure 2.12: Ring-oscillator timing variability zone considering both process and temperature variations.

#### 2.4.2 Voltage Swing and Static-noise Margin (SNM)

The design of CMOS digital circuits that operate in ultra-low voltages is very challenging from the robustness point of view. The cells may present different driving strengths for pull-up and pull-down network, causing insufficient *voltage swings* or *degraded static-noise margins* (SNM). Both are very important metrics that ensure cell functionality under the target every operating condition. The SNM is a measure of cell stability, and became popular due to the widely adoption of SRAM cells for cache memory. The voltage swing, on the other hand, relates to the range of output values that are found when a cell is switching.

Figure 2.13 shows the output node of a 4-input NOR gate. The situation depicted in Figure 2.13 refers to a high-to-low transition at supply voltage of 0.2V. The temperature and process conditions differ from one curve to another; the light gray curve runs at 25°C and typical process (TT), while the dark gray runs at 125°C and slow NMOS/fast PMOS (SF) process. One may note that the light gray presents a *full* voltage swing, from supply voltage to zero, while the dark gray presents a very degraded zero logic value. The degraded zero value is called a *weak zero*, and occurs due to high static current from pull-up network allied to the low driving current from the pull-down network. In addition to the process conditions that enabled this limited voltage swing, note that the temperature is also higher than room temperature – increasing even more the static currents in off transistors.

Regarding the SNM measure, it was shown in (LOHSTROH; SEEVINCK; GROOT, 1983) that two back-to-back gates represent the maximum noise that can be applied before failure to an infinitely long chain composed of the same two gates alternatedly. For a pragmatical definition of SNM, Figure 2.14 (a) shows it as the side length of the largest

Figure 2.13: Voltage swing degradation with process variation and high temperature. The pull-up static current generates a weak zero at the output.

inscribed square fitting the worst-case side of the butterfly plot. This thesis adopt the method proposed in (SEEVINCK; LIST; LOHSTROH, 1987) for measuring the SNM using a simulation based approach. Note in Figure 2.14 (a) that the absolute value of SNM decreases at low voltages. Figures 2.14 (b) and (c) show the effects of process variability into the butterfly plots, and consequently on the SNM. Analogous to the voltage swing, the major factor that degrades the SNM is a not well balanced pull-up and pull-down networks. Therefore, the data presented in Figure 2.14 refers not to the basic back-to-back inverter configuration, but a more complex configuration using a 2-input NOR and NAND cells. The two stacked PMOS of the NOR gate and two stacked NMOS of the NAND provide a worst-case analysis with respect to cell selection for the SNM metric.

Figure 2.14: Voltage transfer curves (VTC) and static-noise margins (SNM) plots, (a) multiple voltage SNM; (b) SNM variability at 1.2V; and (c) SNM variability at 0.15V.

# 3 ULTRA-LOW POWER TECHNIQUES FOR DIGITAL CMOS CIRCUITS

The design of ultra-low power circuits requires power optimizations in all levels, i.e, process, circuit, micro-architectural, and system level. The high level optimizations present large energy impact, but are very specific for a certain case or application. This chapter seeks to provide background information on low-power circuit level design techniques, which are not application dependent and may be applied to a large number of designs. The chapter begins with a brief explanation of the main power components, and follows with several circuit level techniques for low-power digital CMOS circuit design, including clock gating, power gating, operand isolation, multi-VT devices, and finally, voltage-frequency scaling.

## 3.1 Power and Energy Components

The power and energy are mainly classified into three different categories: dynamic, short-circuit, and static. Each one of them refers to a different kind of energy consumption that helps in identifying how the power profile of a VLSI design can be improved. This section covers each one of those energy components, providing analytical models when it is suitable. This master thesis follows the standard presented in this section for referring to energy and power.

#### 3.1.1 Dynamic Energy

Also known as *switching energy*, the dynamic energy is draw from the power supply each time the capacitor in Figure 3.1 is charged (zero to one transition). Current  $i_{dyn}$  passes through the PMOS transistor, dissipating part of the energy as heat, and storing the remaining energy at the capacitor  $C_L$ . When the capacitor  $C_L$  discharges (one to zero transition), the energy stored in the capacitor is then dissipated into the NMOS transistor, generating a current flow back to the ground rail.

For modeling the dynamic energy drawn from the power supply during the zero to one transition at the output node, we first make the assumption of zero slope time. Then, the circuit shown in Figure 3.1 is valid. The energy is derived from the integration of the instantaneous power, resulting in Equation 3.1. Note that only part of this energy will be stored into the capacitor  $C_L$ , and the other part will be dissipated into the PMOS device during the capacitor charging process. For estimating how much energy will stored into the capacitor, we integrate the instantaneous power with respect to the output voltage  $v_{out}$ . Equation 3.2 shows that half of the total dynamic power will be stored into  $C_L$ , and this energy will be later dissipated into NMOS transistor during the one to zero discharge.

Figure 3.1: Dynamic power equivalent circuit for zero slope times.

Source: Modified from (RABAEY; CHANDRAKASAN; NIKOLIC, 2003).

Thus, assuming zero slope time, the total dynamic energy  $E_{DYN}$  drawn from power supply during zero to one transition is given by,

$$E_{DYN} = \int_0^\infty i_{dyn} V_{DD} dt = V_{DD} \int_0^\infty C_L \frac{dv_{out}}{dt} dt$$

$$= C_L V_{DD} \int_0^{V_{DD}} dv_{out} = C_L V_{DD}^2$$

(3.1)

While the energy  $E_C$  in fact stored into the capacitor is

$$E_C = \int_0^\infty i_{dyn} v_{out} dt = \int_0^\infty C_L \frac{dv_{out}}{v}_{out} dt dt$$

$$= C_L \int_0^{V_{DD}} v_{out} dv_{out} = \frac{C_L V_{DD}^2}{2}$$

(3.2)

The dynamic power  $P_{DYN}$  component of a circuit shall be estimated simply by multiplying the dynamic energy  $E_{DYN}$  and the frequency  $f_{0\rightarrow 1}$  in which the cell change state from zero to one. In a large VLSI design however, a cell rarely changes its state as fast as the system clock, thus it is common in literature the adoption of an  $\alpha$  term that accounts for logic cell activity. From Equation 3.3, one may conclude that the dynamic power varies quadractically with voltage and linearly with frequency.

$$P_{DYN} = C_L V_{DD}^2 f_{0 \to 1} \tag{3.3}$$

#### 3.1.2 Short-circuit Energy

It is well known the actual circuit slopes are not as ideal a step function. The slope at voltage input  $v_{in}$  causes a direct current  $i_{sc}$  to flow from power supply to ground while the input switches. This is due to the middle way value of the gate to source voltage on both PMOS and NMOS devices. The energy consumed through the direct current is known as short-circuit energy. It is directly proportional to the slope time at the input. Figure 3.2 shows that short-circuit power is dissipated during both the rise and fall transitions of the