# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

# TIAGO JOSÉ REIMANN

# Cell Selection to Minimize Power in High-Performance Industrial Microprocessor Designs

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microeletronics

Advisor: Prof. Dr. Ricardo A. da Luz Reis

#### **CIP** — **CATALOGING-IN-PUBLICATION**

Reimann, Tiago José

Cell Selection to Minimize Power in High-Performance Industrial Microprocessor Designs / Tiago José Reimann. – Porto Alegre: PGMICRO da UFRGS, 2017.

130 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR-RS, 2017. Advisor: Ricardo A. da Luz Reis.

1. Gate Sizing. 2. Threshold Voltage Assignment. 3. Lagrangian Relaxation. 4. EDA. 5. Microelectronics. I. Reis, Ricardo A. da Luz. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento

Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb

Coordenador do PGMICRO: Prof. Gilson Inácio Wirth

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"Seja você quem for, seja qual for a posição social que você tenha na vida, a mais alta ou a mais baixa, tenha sempre como meta muita força, muita determinação e sempre faça tudo com muito amor e com muita fé em Deus, que um dia você chega lá. De alguma maneira você chega lá."

# CONTENTS

| LIST OF ABBREVIATIONS AND ACRONYMS                                               | 6   |

|----------------------------------------------------------------------------------|-----|

| LIST OF FIGURES                                                                  | 7   |

| LIST OF TABLES                                                                   | 9   |

| ABSTRACT                                                                         | 10  |

| RESUMO                                                                           | 11  |

| 1 INTRODUCTION                                                                   | 12  |

| 2 STATIC TIMING ANALYSIS                                                         | 14  |

| 2.1 Standard Cells                                                               |     |

| 2.2 Interconnect Model                                                           |     |

| 2.2.1 Effective Capacitance                                                      |     |

| 3 THE CELL SELECTION PROBLEM                                                     |     |

| 3.1 Physical Design Flow                                                         |     |

| 3.2 Transistor Sizing                                                            |     |

| 3.3 Gate Sizing                                                                  |     |

| 3.3.1 Continuous Gate Sizing                                                     |     |

| 3.3.2 Discrete Gate Sizing and Threshold Voltage Assignment                      |     |

| 4 RELATED WORKS AND STATE-OF-THE-ART                                             |     |

|                                                                                  |     |

| 4.1 Early Literature                                                             |     |

| 4.1.1 TILOS                                                                      |     |

| 4.1.2 Gate Sizing in MOS Digital Circuits with Linear Programming                |     |

| 4.1.3 Delay and Area Optimization in Standard-Cell Design                        |     |

| 4.1.4 On the Circuit Implementation Problem                                      |     |

| 4.1.5 Gate sizing for constrained delay/power/area optimization                  |     |

| 4.1.6 Fast and Exact Simultaneous Gate and Wire Sizing by Lagrangian Relaxat     |     |

| 4.1.7 Forge                                                                      |     |

| 4.1.8 Linear Programming for Sizing, $V_{th}$ and $V_{dd}$ assignment            |     |

| 4.1.9 Timing-aware Power Minimization via Extended Timing Graph Methods          |     |

| 4.1.10 Gate Sizing for Cell-Library-based Designs                                |     |

| 4.1.11 Gate Sizing for Large Cell-based Designs                                  |     |

| 4.1.12 A New Algorithm for Simultaneous Gate Sizing and Threshold Voltage A      | .S- |

| signment                                                                         |     |

| 4.1.13 Lagrangian Relaxation for Gate Implementation Selection                   |     |

| 4.1.14 Power Reduction Via Near-optimal Library-based Cell-size Selection        |     |

| 4.1.15 Gate Sizing and Device Technology Selection Algorithms for High-perform   |     |

| Industrial Designs                                                               |     |

| 4.2 State-of-the-Art                                                             |     |

| 4.2.1 The ISPD Contest 2012                                                      |     |

| 4.2.2 An Efficient Algorithm for Library-based Cell-type Selection in High-perfo |     |

| Low-power Designs                                                                |     |

| 4.2.3 Trident                                                                    |     |

| 4.2.4 The ISPD Contest 2013                                                      | 56  |

| 4.2.5 Trident 2.0                                                                |     |

| 4.2.6 Fast Lagrangian Relaxation Based Gate Sizing using Multi-Threading         | 60  |

| 4.3 Summary and Discussion                                                       |     |

| 5 PROPOSED FLOWS AND TECHNIQUES                                                  | 66  |

| 5.1 Simulated Annealing-based Algorithm                                          | 66  |

| 5.1.1 Logical Effort                                                             |     |

| 5.1.2 Fanout-of-n Sizing                                                         | 67  |

| 5.1.3 Timing Engine                                               | 68  |

|-------------------------------------------------------------------|-----|

| 5.1.4 Simulated Annealing with Dynamic Cost Function              | 70  |

| 5.2 Empirical Validation                                          | 73  |

| 5.3 Lagrangian Relaxation-based Algorithm                         | 77  |

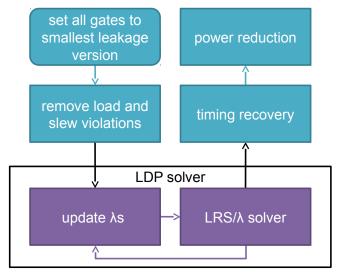

| 5.3.1 Proposed Flow for the ISPD 2012 and 2013 Contest Benchmarks | 79  |

| 5.3.2 Eliminating Load and Slew Violations                        | 82  |

| 5.3.3 Cell Selection Problem Formulation                          | 82  |

| 5.3.4 Interconnection Modeling                                    | 90  |

| 5.3.5 Improving the Lagrangian Relaxation Solution                | 91  |

| 5.4 Empirical Validation                                          | 92  |

| 5.4.1 ISPD 2012 Contest                                           | 93  |

| 5.4.2 ISPD 2013 Contest                                           | 95  |

| 6 INDUSTRIAL DESIGN FLOW APPLICATION                              | 101 |

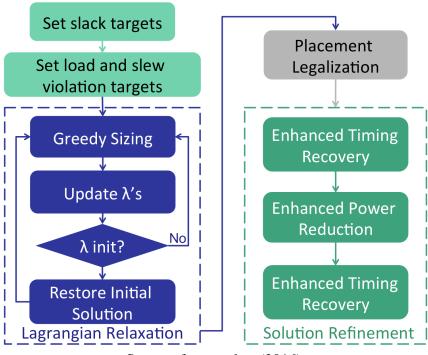

| 6.1 The New Lagrangian Relaxation Formulation                     | 103 |

| 6.1.1 Initializing the Lagrange Multipliers                       | 106 |

| 6.1.2 Lagrange Multiplier Update                                  | 107 |

| 6.1.3 Filtering Gates Options                                     | 108 |

| 6.2 Solution Refinement                                           | 109 |

| 6.2.1 Enhanced Timing Recovery                                    | 109 |

| 6.2.2 Enhanced Power Reduction                                    | 110 |

| 6.3 Empirical Validation                                          | 110 |

| 6.3.1 Preliminary results                                         | 110 |

| 6.3.2 Final results                                               | 115 |

| 7 CONCLUSION                                                      | 119 |

| REFERENCES                                                        | 120 |

## LIST OF ABBREVIATIONS AND ACRONYMS

CAD Computer Aided Design

DAG Directed Acyclic Graph

DRC Design Rules Checking

EDA Electronic Design Automation

HDL Hardware Description Language

ISPD International Symposium on Physical Design

IC Integrated Circuit

KKT Karush–Kuhn–Tucker

LR Lagrangian relaxation

NLDM Non-Linear Delay Model

RTL Register Transfer Level

SPICE Simulation Program with Integrated Circuit Emphasis

SA Simulated Annealing

STA Static Timing Analysis

TNS Total Negative Slack

TTNS True Total Negative Slack

TR Timing Recovery

$V_t$  Threshold Voltage

VLSI Very Large Scale Integration

WMIS Weighted Maximum Independent Set

WNS Worst Negative Slack

# LIST OF FIGURES

| Figure 2.1 Examples of input/output timing arcs for gates of different unateness                   | 16 |

|----------------------------------------------------------------------------------------------------|----|

| Figure 2.2 STA applications in the design flow                                                     | 16 |

| Figure 2.3 (a) Distributed RC model. (b) Examples of parasitics networks                           | 21 |

| Figure 2.4 Example of reduced order model                                                          | 22 |

| Figure 2.5 The effective capacitance model for cell delay calculation in the presence of RC loads. |    |

| Figure 3.1 General Electronic Design Automation flow.                                              | 26 |

| Figure 3.2 Sources of leakage power in a MOS transistor                                            |    |

| Figure 3.3 Normalized inverter gate leakage powers in a commercial 45nm library                    |    |

| Figure 4.1 Comparison of the behaviors of the proposed method and a greedy                         |    |

| method for power optimization.                                                                     |    |

| Figure 4.2 Behavior of three different methods for power optimization.                             | 35 |

| Figure 4.3 Power-delay curves for different designs for $GS$ and greedy method                     | 35 |

| Figure 4.4 Circuit representation after replacing the components by their models                   |    |

| (dashed lines).                                                                                    | 36 |

| Figure 4.5 Algorithms (a) $SOLVE\_LRS/\mu$ , (b) $SOLVE\_LDP$ , and (c) $SGWS-LP$                  | •  |

| LR                                                                                                 |    |

| Figure 4.6 Optimization flow.                                                                      |    |

| Figure 4.7 Timing optimization gate sizing algorithm (LIU; HU, 2010)                               |    |

| Figure 4.8 Active area and delay results for continuous and discrete sizing methods                |    |

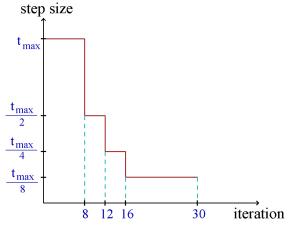

| Figure 4.9 Step size function for Lagrange multipliers update                                      |    |

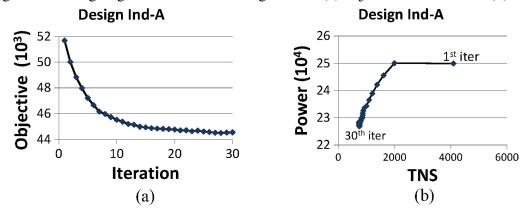

| Figure 4.10 Lagrangian relaxation convergence for (a) objective function and (b) TNS               |    |

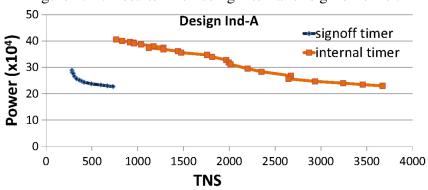

| Figure 4.11 Results when using internal or sign-off timer.                                         | 48 |

| Figure 4.12 Comparison for the DP algorithm and a single node method in LR                         | 49 |

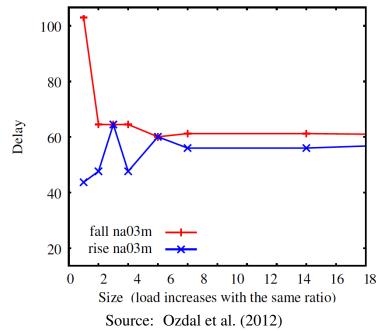

| Figure 4.13 Non-convex gate delays for a 3-inputs medium $V_t$ NAND gate                           | 50 |

| Figure 4.14 (a) Initial sizing to fix electrical violations, (b) Min-Clock LR, and (c)             |    |

| Lagrange multiplier update algorithms.                                                             |    |

| Figure 4.15 Resizing effect example                                                                |    |

| Figure 4.16 Overall gate sizing flow.                                                              |    |

| Figure 4.17 Sensitivity functions used.                                                            |    |

| Figure 4.18 Optimization flow.                                                                     | 58 |

| Figure 4.19 (a) Impact of calibration frequency and (b) leakage power results for                  |    |

| different calibration strategies.                                                                  |    |

| Figure 4.20 TNS and power progression over LR iterations on $b19_f ast$ benchmark                  |    |

| Figure 4.21 Greedy sensitivity-based sizing example                                                | 63 |

| Figure 4.22 Lagrangian relaxation convergence.                                                     | 64 |

| Figure 5.1 Timer Data Structure                                                                    | 70 |

| Figure 5.2 Number of updated nodes for two different threshold values $\varepsilon$                | 71 |

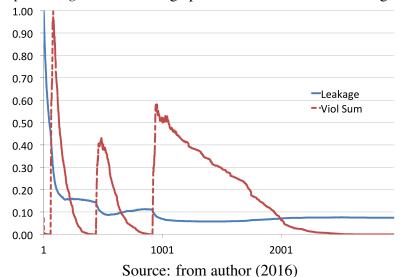

| Figure 5.3 <i>pci_bridge32</i> total leakage power and total violation along SA iterations         |    |

| Figure 5.4 High-level view of our cell selection flow.                                             |    |

| Figure 5.5 Lambda-Delay Cost Computation                                                           |    |

| Figure 5.6 Example circuit for delay sensitivity computation.                                      |    |

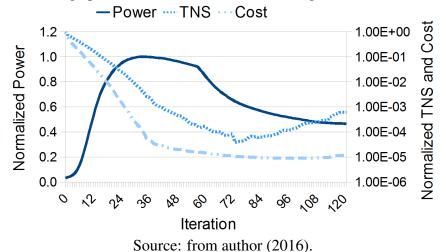

| Figure 5.7 Leakage power, TNS and solution cost along iterations for $cordic\_fast$                |    |

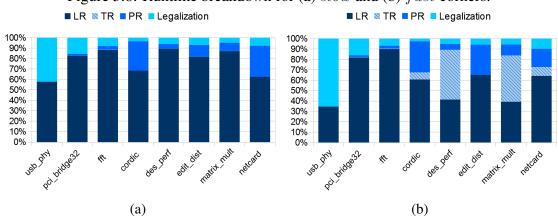

| Figure 5.8 Runtime breakdown for (a) slow and (b) fast corners                                     |    |

| (··/ ··································                                                            |    |

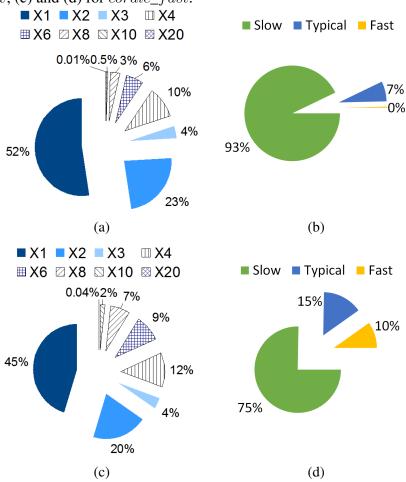

| Figure 5.9 Gate usage by sizes and $V_{th}$ for the $cordic$ benchmark. (a) and (b) for |     |

|-----------------------------------------------------------------------------------------|-----|

| cordic_slow, (c) and (d) for cordic_fast                                                | 100 |

| Figure 6.1 The proposed cell selection flow.                                            | 102 |

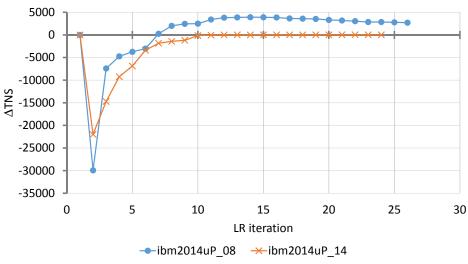

| Figure 6.2 TNS change along LR iterations.                                              |     |

| Figure 6.3 Leakage power improvement at the end of LR in five different scenarios       |     |

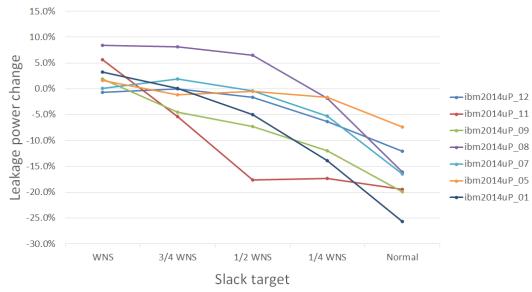

| for physical synthesis slack target (target clock period).                              | 114 |

# LIST OF TABLES

| Table 2.1 NLDM lookup table from the ISPD Contest 2013. Transition times in $ps$ and load capacitances in $fF$ .                                                                                                                                                                                                        | 19    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table 4.1 Number of combinational gates and leakage power (W) on ISPD 2012 benchmarks.                                                                                                                                                                                                                                  | 51    |

| Table 4.2 Number of combinational gates, leakage power $(W)$ and runtime $(min)$ on ISPD 2013 benchmarks                                                                                                                                                                                                                | 57    |

| Table 4.3 Summary of techniques present in references. <i>Optimal</i> refers to the optimality claimed for the chosen (inaccurate) models in each work                                                                                                                                                                  | 62    |

| Table 5.1 Leakage power ratio to best solution found for all ISPD'12 circuits  Table 5.2 Total violation and total leakage power results with different Fanout-of-n rules and different flows using one or four SA loops and alternating the use                                                                        | 74    |

| of an initial solution.                                                                                                                                                                                                                                                                                                 | 75    |

| Table 5.3 Total violation and total leakage power results with different flows using one or four SA loops without an initial solution.                                                                                                                                                                                  | 76    |

| Table 5.4 Runtime in minutes for the different flows under test                                                                                                                                                                                                                                                         |       |

| Table 5.5 Notation.                                                                                                                                                                                                                                                                                                     | 78    |

| Table 5.6 Notation.                                                                                                                                                                                                                                                                                                     | 80    |

| Table 5.7 Leakage power (W) for ISPD 2012 benchmarks and number of combinational cells for all circuits.                                                                                                                                                                                                                | 94    |

| Table 5.8 Runtime (minutes) for ISPD 2012 benchmarks and number of combina-                                                                                                                                                                                                                                             |       |

| tional cells for all circuits. Runtimes are taken from the corresponding papers. Table 5.9 Leakage power $(W)$ , runtime $(min)$ and clock period $(ps)$ on ISPD 2013 benchmarks comparing the contest results and our new results using accurate timing information in Timing Recovery and Power Reduction algorithms. |       |

| Power results are truncated.                                                                                                                                                                                                                                                                                            |       |

| Table 5.10 Total leakage power after each step                                                                                                                                                                                                                                                                          | 99    |

| Table 6.1 Characteristics for 14 high performance microprocessor designs                                                                                                                                                                                                                                                | 111   |

| Table 6.2 Results assuming timing closure can be achieved. Only LR step in the flow is executed.                                                                                                                                                                                                                        | 112   |

| Table 6.3 Results considering the worst slack as the target for all timing paths.                                                                                                                                                                                                                                       | 112   |

| Only LR step in the flow is executed.                                                                                                                                                                                                                                                                                   | 113   |

| Table 6.4 Results with proposed modifications included for a set of 14 high perfor-                                                                                                                                                                                                                                     | 1 1 5 |

| mance microprocessor designs.                                                                                                                                                                                                                                                                                           | 115   |

| Table 6.5 Experimental results for 14 high performance microprocessor blocks                                                                                                                                                                                                                                            |       |

| Table 6.6 Experiments without $TTNS$ degradation in PR step.                                                                                                                                                                                                                                                            |       |

| Table 6.7 Number of gates and runtimes for Table 6.5 and Table 6.6                                                                                                                                                                                                                                                      |       |

| Table 6.8 Experiments without lambda tuning iterations                                                                                                                                                                                                                                                                  | 118   |

#### **ABSTRACT**

This work addresses the gate sizing and  $V_t$  assignment problem for power, area and timing optimization in modern integrated circuits (IC). The proposed flow is applied to the Benchmark Suites of the International Symposium on Physical Design (ISPD) 2012 and 2013 Contests. It is also adapted and evaluated in the post placement and post global routing stage of an industrial IC design flow using a sign-off static timing analysis engine. The proposed techniques are able to generate the best solutions for all benchmarks in the ISPD 2013 Contest (in which we were the winning team), with on average 8% lower leakage with respect to all other contestants. Also, after some refinements in the algorithms, we reduce leakage by another 10% on average over the contest results.

The focus of this work is to develop and apply a state-of-the-art cell selection algorithm to further improve already optimized high-performance industrial designs after the placement and routing stages of the industrial physical design flow. We present the basic concepts involved in the gate sizing problem and how earlier literature addresses it. Several problems found when applying global optimization techniques in real-life industrial designs, which are not fully covered in publications found in literature, are presented and discussed. Considering the industrial application, the proposed techniques reduce leakage power by up to 18.2%, with average reduction of 10.4% without any degradation in timing quality.

**Keywords:** Gate Sizing. Threshold Voltage Assignment. Lagrangian Relaxation. EDA. Microelectronics.

# Seleção de Portas Lógicas para Minimização de Potência em Projetos de Microprocessadores de Alto Desempenho

#### **RESUMO**

Este trabalho aborda o problema de dimensionamento portas lógicas e assinalamento de  $V_t$  para otimização de potência, área e temporização em circuitos integrados modernos. O fluxo proposto é aplicado aos conjuntos de circuitos de teste dos Concursos do *International Symposium on Physical Design* (ISPD) de 2012 e 2013. Este fluxo também é adapatado e avaliado nos estágios pós posicionamento e roteamento global em projetos industriais de circuitos integrados, que utilizam uma ferramenta precisa de análise estática de temporização.

As técnicas propostas geram as melhores soluções para todos os circuitos de teste do Concurso do ISPD 2013 (no qual foi a ferramenta vencedora), com em média 8% menos consumo de potência estática quando comparada com os outros concorrentes. Além disso, após algumas modificações nos algoritmos, nós reduzimos o consumo em mais 10% em média a pontência estáticas com relação aos resultados do concurso.

O foco deste trabalho é desenvolver e aplicar um algoritmo estado-da-arte de seleção portas lógicas para melhorar ainda mais projetos industriais de alto desempenho já otimizados após as fases de posicionamento e roteamento do fluxo de projeto físico industrial. Vamos apresentar e discutir vários problemas encontrados quando da aplicação de técnicas de otimização global em projetos industriais reais que não são totalmente cobertos em publicações encontradas na literatura. Os métodos propostos geram as melhores soluções para todos os circuitos de referência no Concurso do ISPD 2013, no qual foi a solução vencedora. Considerando a aplicação industrial, as técnicas propostas reduzem a potência estática em até 18,2 %, com redução média de 10,4 %, sem qualquer degradação na qualidade de temporização do circuito.

**Palavras-chave:** Dimensionamento de Portas Lógicas, Assinalamento de Tensão de Limiar, Relaxação Lagrangiana, EDA, Microeletrônica.

#### 1 INTRODUCTION

The growing importance of low power designs for portable devices to extend battery life and to reduce cooling costs, the challenges imposed by the power density of new technology nodes and cost of energy for server centers is making both industry and academia focus on algorithms to provide power optimized IC designs.

One way to achieve this goal is through gate sizing and  $V_t$  assignment. The process of gate sizing defines the sizes of the transistors inside each logic gate that composes the design. In many technology processes transistors sizes can be continuously assigned, i. e., any size is accepted, or previously determined by a standard cell library. In library-based designs, only discrete gate sizes are available. Gate sizing and  $V_t$  assignment optimization methods can be applied in several stages of the design synthesis flow, from the logic synthesis to post-route optimization, with increasing accuracy in the timing analysis models as a result of more accurate physical information.

The discrete gate sizing problem has been the subject of many works in the literature. The techniques proposed are based on different methods like Lagrangian relaxation (LR) (CHEN; CHU; WONG, 1999; TENNAKOON; SECHEN, 2005; OZDAL; BURNS; HU, 2011; FLACH et al., 2013; FLACH et al., 2014), Dynamic Programming (DP)(OZDAL; BURNS; HU, 2011), Linear Programming (CHINNERY; KEUTZER, 2005), greedy iterative sensitivity-based methods (LIN; MAREK-SADOWSKA; KUH, 1990; QIAN; ACAR, 2007; HU et al., 2012; KAHNG et al., 2013), Stochastic optimization (HU et al., 2012; KAHNG et al., 2013), network-flow (REN; DUTT, 2008; REN; DUTT, 2011), and Sequential Quadratic Programming (SQP) (MENEZES; BALDICK; PILEGGI, 1995; MENEZES; BALDICK; PILEGGI, 1997).

Throughout this work we refer to simultaneous gate sizing and  $V_t$  assignment as cell selection. Despite the many contributions in the field, many of the cell selection problems are not fully handled by existing methods. Also, most of the previous works do not present solutions that are practical for industrial designs. Several simplifications adopted in these works, like simpler delays models and incomplete timing propagation, are not applicable any more or have inaccuracies that prevent the convergence to a near-optimal solution.

Power consumption in integrated circuits has two components: static (leakage) and dynamic. The former is related to the leakage current of the components while the latter is associated with signal transition and short-circuit currents. Both components can

be addressed through gate sizing and  $V_t$  assignment.

Most recent works focus only on the leakage power optimization in a timing-constrained optimization. This focus is a consequence of the problem definition on the two ISPD Discrete Gate Sizing Contests (2012 and 2013). However, it is important to also ensure that the other design objectives like timing, dynamic power, and area are (at least) not degraded by the power optimization process. Moreover, those parameters may also be an optimization objective. These objectives are conflicting and optimizing only one may be detrimental to the others. For instance, if a cell with a larger area (size) and higher  $V_t$  (less leakage power) replaces a smaller but lower  $V_t$  cell option in a non-critical path, the leakage power will decrease, but dynamic power may increase because of the increase in the capacitance of the new cell option. Also, the area in this case will increase. Since leakage power grows exponentially with respect to reduction in  $V_t$  (as detailed later), the area increase in order to reduce power can be excessive.

A good formulation for gate sizing and  $V_t$  assignment must enable an appropriate balance of those conflicting objectives to further improve the solution provided by the earlier stages of the physical synthesis flow.

The objective of this work is to develop and apply a state-of-the-art cell selection algorithm to further improve already optimized high-performance industrial designs after the placement and global routing stages of the industrial physical design flow, where wiring parasitics are available and timing models are more accurate.

This work is organized as follows. First, given the importance of timing analysis for the cell selection algorithms, we introduce some basic concepts of Static Timing Analysis (STA) and the relevant methods for timing analysis in Chapter 2. Chapter 3 presents the cell selection problem and gives several options for how it can be inserted in a general physical design flow with some examples of the different methodologies and applications of algorithms. In Chapter 4, we revisit the related works and the state-of-the-art prior to this work. Next, Chapter 5 presents the proposed methodologies to address the cell selection problem in the ISPD contests. Chapter 6 details the industrial applications proposed, including the differences in formulations and the respective experimental validation. The conclusions are presented in Chapter 7.

#### **2 STATIC TIMING ANALYSIS**

The quality of results given by cell selection algorithms in post-route optimization strongly relies on the accuracy of the timing models used during the optimization. The presence of wiring parasitics and the non-linearity of cell delay models undermines the performance of analytical optimization methods that required closed-form models, which may present high inaccuracies when compared to the sign-off timing analysis. More accurate timing enables better optimization results, as presented in recent publications (KAHNG et al., 2013; FLACH et al., 2014).

In that context, it is important to present the relevant concepts involved in static timing analysis (STA) that are taken into account for the development of this work.

The concept of static timing analysis (STA) is presented in (HITCHCOCK R.B., 1982) and other publications, including (HITCHCOCK; SMITH; CHENG, 1982; ABATO et al., 1996; KIRKPATRICK; CLARK, 1966; GUNTZEL, 2000). Details can be found in (SAPATNEKAR, 2004; BHASKER; CHADHA, 2009)

The idea of STA is to perform a block-based analysis of the circuit to obtain the fastest and slowest path delays between all the timing start and endpoints. Also, the slacks at each cell pin and input—output (I/O) pins are calculated. This is done by propagating arrival times in topological order and required times in reverse topological order.

Timing startpoints can be either a primary input (PI) or a sequential element (latch, flip-flop) output. Timing endpoints are the primary outputs (PO) and the data input of sequential elements.

The blocks in the circuit are usually represented by the gates. The timing information for each gate is found in the standard cell library. Gates are modeled with different delays and slew rates for each transition (rise and fall), depending on input slew and output load capacitance.

In this work we follow the definitions found in (LEE; GUPTA, 2012) with some small modifications. The definitions are:

- Primary inputs (PI): input ports in the design that are driven by external sources.

- Primary outputs (PO): output ports in the design.

- Cell rise time or rise delay: time from when the input crosses 50% voltage to when the rising output crosses 50% voltage.

- Cell fall times or fall delay: time from when the input crosses 50% voltage to when the falling output crosses 50% voltage.

- Cell rise transition or slew: the time elapsed from when the output signal crosses the 20% voltage to when it crosses 80%.

- Cell fall transition or slew: the time elapsed from when the output signal crosses the 80% voltage to when it crosses 20%.

- Arrival time  $(t_a)$ : the time that the signal crosses the 50% voltage threshold at a given point in the circuit. The time associated with a rising and falling signal is called the rise arrival time and the fall arrival time, respectively.

- Required arrival time  $(t_r)$ : the time a signal needs to cross the 50% voltage threshold at a given point in the circuit to be timing feasible. The required arrival time associated with a rising and falling signal are called the rise and fall required arrival time, respectively.

- Slack (s): the difference of the required arrival time and the arrival time, represents the amount of timing slack available at that point in the circuit.

- Timing arc: a concept used to relate the delay between two adjacent nodes in the circuit.

- Positive unate: when a rising input to a gate causes a rising output, or a falling input causes a falling output.

- Negative unate: when a rising input to a gate causes a falling output, or a falling input causes a rising output.

- Non-unate: when there is no direct relation between the type of transition (rise/fall) in the input and the type of transition in the output, e.g. XOR gate where a rising or falling output transition can be triggered by either rising or falling input transition.

- $\bullet$   $\beta$  ratio: the ratio between the width of the PMOS transistors and the width of the NMOS transistors in a CMOS gate.

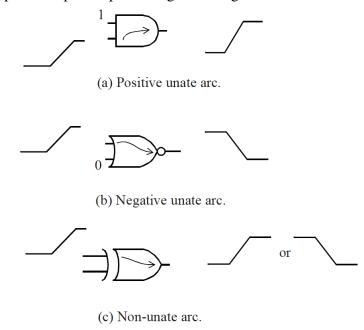

The unateness concept is shown in Figure 2.1. Sign-off timers handle rising and falling delays and transitions separately, and the unateness of a cell will determine the possible combinations for signal propagation through its timing arcs. The unateness also determines the timing information available in the cell library. Positive and negative unate arcs only require two timing tables (rise-to-rise, fall-to-fall or rise-to-fall, fall-to-rise) for delay and transition times for each input-output pin pair. Non-unate cells require four timing tables (rise-to-rise, fall-to-fall, rise-to-fall and fall-to-rise) for delay and transition times for each input-output pin pair.

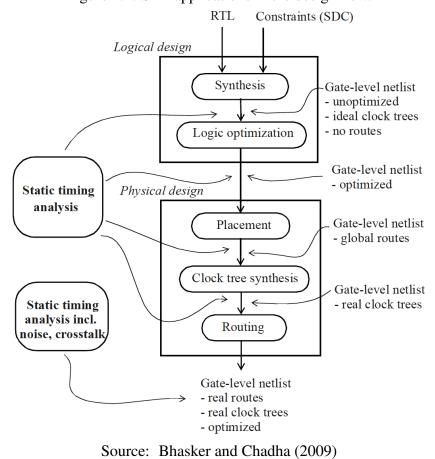

STA is used in the design flow at several stages, with different levels of accuracy,

Figure 2.1: Examples of input/output timing arcs for gates of different unateness.

Figure 2.2: STA applications in the design flow.

Source: Bhasker and Chadha (2009)

as shown in Figure 2.2.

In this work we apply STA with library-based technologies. Although cell selec-

tion algorithms do not require a specific timing analysis model to work with, global cell selection methods in post global routing optimization perform better with sign-off timers, taking advantage of the actual positive slacks existent in the design and the accurate trade-offs between timing and power. Simplified timing models, which are linear, convex, or differentiable introduce inaccuracy that will reduce the ability of the algorithm to find the actual best combinations of sizes and threshold voltages for a single cell in the design due to reduced timing slack for the rest of the design caused by timing propagation.

Next we discuss the standard cell library model and the interconnect models commonly used in modern designs.

#### 2.1 Standard Cells

Most functions in a chip are designed using basic building blocks which implement simple boolean logic functions such as AND, OR, NAND, NOR, AND-OR-INVERT, OR-AND-INVERT, XOR, MUX, inverters, and sequential elements (latch, flip-flop and its variants). There are also utility cells, such as filler cells, antenna cells, and buffer cells, which are used to help with the physical implementation of the design. These basic building blocks are referred to as standard cells. The functionality and timing of the standard cells is pre-designed and pre-characterized and made available to the circuit designer. Also, larger functional blocks, known as macros, may be in the design and have similar treatment as standard cells, with timing properties assigned to their input and output pins. Designers use Electronic Design Automation (EDA) tools to implement the required functionality of the design using the standard cells as the building blocks.

Usually, several options are available in the library for each logic function. Despite having the same logic function, each cell has different characteristics regarding: transistor widths and folding (that changes the electrical properties of the transistor), transistor channel length, threshold voltage  $(V_t)$ , and  $\beta$  ratios (that affect the timing performance for different rising and falling output transitions). Those differences imply a change in timing, area, power, and parasitic characteristics. With those options available, the design can be optimized for one or more objectives.

The cell library uses table models to specify the delays and timing checks for each timing arc of the cell. The models used may vary between libraries and technologies depending on the level of accuracy needed. The table models used for delay, output slew, or other timing checks are referred to as NLDM (Non-Linear Delay Model). Newer

libraries for nanometer technologies may use more accurate current source based timing models. CCS (Composite Current Source) and ECSM (Effective Current Source Model) are two examples of these models. Current source models are not used throughout this work and their characteristics and properties are not relevant to the application of the methods developed here.

The NLDM table is usually a discretization of simulation data or real prototype measurements. It contains the delay through the cell for several combinations of input transition time at the cell input pin and total output capacitance at the cell output. The models for delay are typically presented in a two-dimensional form, with the two independent variables being the input transition time and the output load capacitance, and the entries in the table denoting the delay. The same is applied to the output transition time (slew rate) calculation.

The following equation shows the bilinear interpolation to the nearest four data points in the lookup table used for NLDM calculation.

$$z = a + b \times x + c \times y + d \times x \times y \tag{2.1}$$

where z is the calculated value for delay or slew, x is the input slew, and y is the output load capacitance.

The timing tables contained in a cell library are:

- Rise delay

- Fall delay

- Rise slew

- Fall slew

- Clock hold time (data input of sequential elements only)

- Clock setup time (data input of sequential elements only)

An example of a delay lookup table is shown in Table 2.1. It represents the delay for the smallest and slowest inverter in the ISPD Contest 2013 library. The calculation is done by interpolating/extrapolating the two-dimensional data in the lookup table. Knowing the input transition time  $slew_{input}$  and the output load  $C_{load}$  the value from the lookup table is obtained as follows. The two nearest table indices in each dimension are chosen for the table interpolation. Assuming that we are calculating the delay  $D_A$  for a given input transition and output load which the closest indices are  $x_1, x_2$  and  $y_1, y_2$ , respectively:

|             | v                     |       |       |       |        |        |        |        |

|-------------|-----------------------|-------|-------|-------|--------|--------|--------|--------|

|             | Input transition time |       |       |       |        |        |        |        |

| Output load | 5.00                  | 30.00 | 50.00 | 80.00 | 140.00 | 200.00 | 300.00 | 500.00 |

| 0.00        | 11.72                 | 18.22 | 22.67 | 27.61 | 34.82  | 40.44  | 48.21  | 61.24  |

| 1.00        | 16.93                 | 23.43 | 28.60 | 34.95 | 44.15  | 51.18  | 60.65  | 75.83  |

| 2.00        | 22.13                 | 28.63 | 33.83 | 41.24 | 52.23  | 60.57  | 71.67  | 89.00  |

| 4.00        | 32.55                 | 39.05 | 44.25 | 52.05 | 66.05  | 76.76  | 90.85  | 112.34 |

72.88

114.55

197.88

Table 2.1: NLDM lookup table from the ISPD Contest 2013. Transition times in ps and load capacitances in fF.

65.08

106.75

190.08

$$D_{A} = (1 - w_{x}) \times (1 - w_{y}) \times D_{11}$$

$$+ (1 - w_{x}) \times w_{y} \times D_{12}$$

$$+ w_{x} \times (1 - w_{y}) \times D_{21}$$

$$+ w_{x} \times w_{y} \times D_{22}$$

$$(2.2)$$

88.48

130.15

213.48

103.09

145.75

229.08

122.40

171.59

255.08

151.42

213.31

307.08

where  $D_{xy}$  is the table entry for indices x, y and

8.00

16.00

32.00

53.38

95.05

178.38

59.88

101.55

184.88

$$w_x = \frac{x_0 - x_1}{x_2 - x_1}$$

$$w_y = \frac{y_0 - y_1}{y_2 - y_1}$$

(2.3)

For the example in Table 2.1, assuming  $slew_{input} = 220ps$  and  $C_{load} = 4.5fF$ :

$$w_x = \frac{220 - 200}{300 - 200} = 0.2$$

$$w_y = \frac{4.5 - 4}{8 - 4} = 0.125$$

(2.4)

$$D_A = (1 - 0.2) \times (1 - 0.125) \times 76.76$$

$$+ (1 - 0.2) \times 0.125 \times 103.09$$

$$+ 0.2 \times (1 - 0.125) \times 90.85$$

$$+ 0.2 \times 0.125 \times 122.40$$

(2.5)

$$D_A = 83.00ps$$

As aforementioned, the same calculation is done to obtain the output transition time from its lookup table. When the input transition time and/or the output load are out of the indices' ranges, an extrapolation is made with the last two indices in both dimensions. The calculation process is the same. However, since the cell is not characterized for such parameters, the resultant delay and output transition time may be quite inaccurate. Maximum load and maximum transition time are two electrical constraints specified in the library to guarantee the accuracy of times obtained from the lookup tables.

Each timing arc inside a cell has its respective tables. Timing arcs relate the input and output pins for both rising and falling transitions and both delay and output slew. In sequential cells, timing arcs relate the clock pin with the synchronous input and output pins. The data input is a timing endpoint (sometimes also called a time barrier). Sequential cells also usually have scan-related pins for testing – scan enable and scan input. Scan pins and scan timing are omitted in this work for simplicity. They are either not present (ISPD Contest) or are not setup timing critical (industrial high-performance designs) in this work. Sequential cells may also have asynchronous inputs (like the clear data pin).

#### 2.2 Interconnect Model

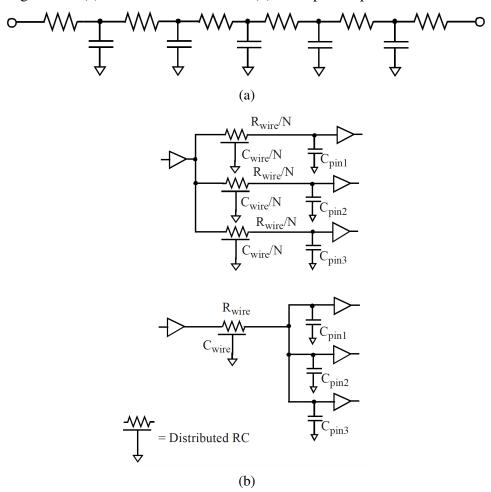

Interconnect models have a significant importance in modern designs where the interconnect delay has become a considerable percentage of total delay. Also, the slew propagation through wires has significant impact in timing calculations. Accurate interconnection delay and slew propagation metrics must be used in the late stages of physical design, where parasitics information is available. Interconnect parasitics are extracted from the circuit layout to form RC (resistance and capacitance) networks. They are commonly represented as RC trees or RC meshes – Figure 2.3.

Figure 2.3: (a) Distributed RC model. (b) Examples of parasitics networks.

Source: Bhasker and Chadha (2009)

Lumped capacitance models are inaccurate<sup>1</sup> for timing analysis in post global routing stages.

Electrical simulation (like SPICE – Simulation Program with Integrated Circuit Emphasis (NAGEL; PEDERSON, 1973)) can be used to accurately calculate timing by solving the differential equations related to the currents, charges and voltages. However, the runtime for this approach is prohibitive in large or even mid-size designs. The runtime of timing analysis is a key aspect for gate sizing and threshold voltage assignment, where fast delay estimates are needed for optimization.

The Elmore delay (ELMORE, 1948) is a simple method to estimate delays. This method calculates the first moment of the impulse response applied to the RC network. The Elmore delay is an upper bound on the actual delay (GUPTA et al., 1995).

However, modern timers employ more accurate methods that utilize higher order

<sup>&</sup>lt;sup>1</sup>The lumped capacitance model for interconnects is only accurate when the driver resistance overwhelms the wire resistance (SAPATNEKAR, 2004)

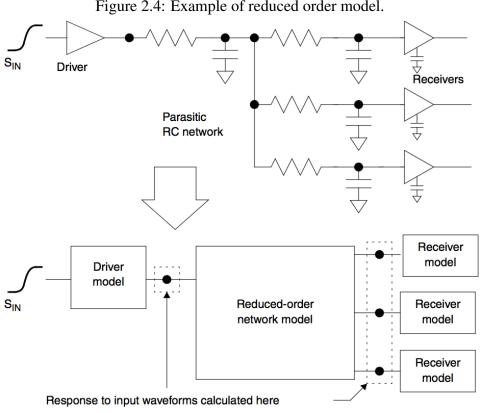

Figure 2.4: Example of reduced order model.

Source: Synopsys (2004)

moments to improve the accuracy. The Asymptotic Waveform Evaluation Method (PIL-LAGE; ROHRER, 1990; PILLAGE; HUANG; ROHRER, 1989; ODABASIOGLU; CE-LIK; PILEGGI, 1997; RATZLAFF; PILLAGE, 1994) and Arnoldi-based methods (SIL-VEIRA; KAMON; WHITE, 1996; ELFADEL; LING, 1997; SILVEIRA et al., 1996) are examples of higher order models commonly used to model the parasitics network - Figure 2.4. More details can be found in (SAPATNEKAR, 2004; CELIK; PILEGGI; ODABASIOGLU, 2002).

The propagation of the output transitions (slews) of cells is also crucial for timing calculations. Signal slews in the input pins play a major role in determining the output delay. It is not possible to ignore slew effects in post global route timing analysis. Especially in cell selection algorithms, ignoring the slew misses the potential in increasing gate size or decreasing the threshold voltage to improve the slew in its fanout gates, and the corresponding gate delays.

For simplicity in timing analysis in industrial STA tools (i.e. Synopsys Prime-Time®) the propagated output slew is usually the slower slew calculated at the output, regardless of the arrival time associated. However, most sign-off timers can also propagate the slew associated with the greatest arrival time at the output if specified (e.g.

Figure 2.5: The effective capacitance model for cell delay calculation in the presence of RC loads.

path-based static timing analysis).

## 2.2.1 Effective Capacitance

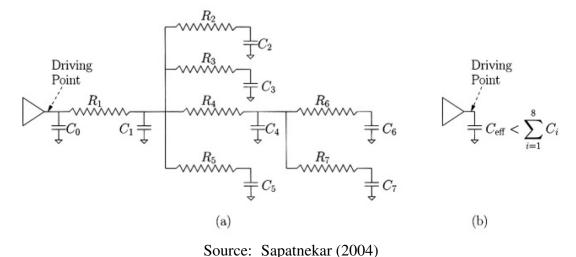

Interconnect models may be simplified to use only a lumped capacitance to represent the wires. However, the lumped capacitance model is not accurate when the driver resistance and the wire resistance are comparable. The phenomenon of *resistive shield-ing* causes the delay at the driver timing arc to be equivalent to a delay where the output load is smaller than the total capacitance in the RC network. This smaller capacitance is called *effective capacitance*. Figure 2.5 shows an example of effective capacitance  $(C_{eff})$  equivalence.

The effective capacitance models used in accurate STA tools calculate an equivalent capacitance that has the same timing arc delay as the cell with RC tree load. Using an effective capacitance model is useful because cells may continue to be characterized in terms of a load capacitance (Section 2.1).

Many methods for effective capacitance calculation can be found in the literature by O'Brien and Savarino (1989), Dartu et al. (1994), Dartu, Menezes and Pileggi (1996), Puri, Kung and Drumm (2002), Qian, Pullela and Pillage (2006). The driver model used for effective capacitance calculations is usually the same used for the parasitics network analysis (see Figure 2.4). Dartu, Menezes and Pileggi (1996) propose the use of a Thevenin model (NILSSON; RIEDEL, 2005) to represent the driver.

The effective capacitance is calculated based on the current necessary to charge the

equivalent RC  $\pi$ -model derived from the complete RC network (O'BRIEN; SAVARINO, 1989). The gate is characterized by the determination of the values of a driver resistance  $(R_d)$ , transistion delay  $(t_0)$  and transistion time  $(\Delta t)$ , according to the library timing information (DARTU et al., 1994; DARTU; MENEZES; PILEGGI, 1996).

#### 3 THE CELL SELECTION PROBLEM

In this chapter we define the cell selection problem, showing how it can be inserted in a general physical design flow and give some examples of the different methodologies and applications of algorithms related to the cell selection problem.

First we talk about the physical design flow and how cell selection algorithms can be applied in several stages of the flow.

#### 3.1 Physical Design Flow

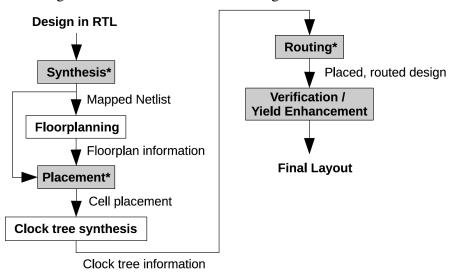

Cell selection algorithms can be applied in many parts of the design flow, from the logic synthesis to the post-route stages. Figure 3.1 shows an example of a general Electronic Design Automation (EDA) flow. For each stage in the flow, the actions expected can be summarized as follows:

The *Logic Synthesis* step starts with a Register Transfer Level (RTL)/Hardware Description Language (HDL) design description, a standard cell library information and timing constraints for the design. A gate level netlist mapped to the standard cell library is generated to meet the constraints and optimized different objectives.

The *Floorplanning* stage creates a floorplan with rows for standard cell placement, I/O pads and locations for macro blocks.

A *Placement* step defines the positions for the cells into the rows created by the floorplanning algorithm, flipping and rotating cells as necessary for the optimization objectives. The main objective is usually to minimize the wirelength in the resulting layout. Another common target is routing congestion mitigation and improve timing in critical paths (timing-driven placement).

The *Clock Tree Synthesis* stage will create a clock tree of buffers to distribute the clock signal to all sequential elements of the design. The main goals are to minimize the size of the clock tree (to minimize clock power and latency), and the skew at each of the outputs of the clock tree.

Routing connects the pins from the placed cells using wires on the available metal layers and vias between layers. The objective is to minimize the total wiring needed (reduce congestion and delay), while avoiding design rule violations and meeting timing constraints.

Cell selection methods can be used throughout the design flow to:

Figure 3.1: General Electronic Design Automation flow.

Source: Lee and Gupta (2012)

- fix timing violations, and to optimize the design.

- fix maximum fanout rule violations or maximum slew violations.

- fix design rule violations.

- optimize the design for timing/area/power/variability/yield.

#### 3.2 Transistor Sizing

The transistor sizing problem has been studied for decades and is applied to handle many different problems. The reader is referred to the following publications Kao, Movahed-Ezazi and Sabiers (1984), Glasser and Hoyte (1984), Kao, Fathi and Lee (1985), Fishburn and Dunlop (1985), Pincus and Despain (1986), Matson and Glasser (1986), Hedlund (1987), Cirit (1987), Marple and Gamal. (1987), Shyu et al. (1988), Marple (1989), Dai and Asada (1989), Hoppe et al. (1990), Sapatnekar, Rao and Vaidya (1991), Sapatnekar et al. (1993), Borah, Owens and Irwin (1995), Borah, Owens and Irwin (1996), Sirichotiyakul et al. (1999), Kasamsetty, Ketkar and Sapatnekar (2000), Sundararajan, Sapatnekar and Parhi (2002), Santos et al. (2003), Kursun, Ghiasi and Sarrafzadeh (2004), Chou, Wang and Chen (2005), Santos et al. (2005/a), Boyd et al. (2005), Beece et al. (2010), Kasamsetty and Sapatnekar (2000), Nikoubin et al. (2010), Liao and Hu (2011), Marranghello et al. (2011), Yoshida and Fujita (2011), Posser et al. (2012) for more details about the problem and several formulations and algorithms to handle it.

Transistor sizing can be applied for analog designs and custom digital IC designs.

Both cases are not covered in this work since the focus here in on cell selection in designs using standard cell libraries.

Most formulations for the transistor sizing problem assume a direct and linear relationship between the delay and the transistor width. However, modern designs have several sources of non-linearities that make such models inaccurate.

As mentioned before, with the use of standard libraries, digital IC designs rarely make use of transistor sizing algorithms. One of the major problems is the lack of fast and accurate characterization tools to provide good models and layout parasitic extraction for new cell sizes. Tools for library characterization can take weeks, especially with turn around to correct the generated cells.

The typical formulation for the transistor sizing problem is:

minimize

$$f(x)$$

subject to  $Delay \leq T_{spec}$  (3.1)

$L_i \leq x_i \leq U_i$

where x is the variable available for optimization (usually transistor width), f(x) is the objective function (usually area or power),  $T_{spec}$  is the maximum allowed delay and  $L_i$ ,  $U_i$  are the lower and upper bounds for the transistor size.

# 3.3 Gate Sizing

The gate sizing problem assumes a fixed set of transistor widths for a logic gate in order to model the gate size. Then, the whole gate is sized, instead of sizing separately each one of its transistors.

Gate sizing algorithms can be divided in two categories: continuous gate sizing and discrete gate sizing. We detail both methodologies next.

#### 3.3.1 Continuous Gate Sizing

The continuous gate sizing approach assumes that any size can be implemented in the layout. This approach is suitable for custom digital designs that do not use a cell library.

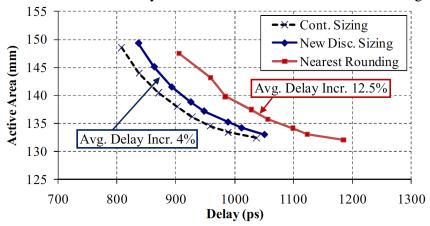

Continuous gate sizing is not in the scope of this work. However, many discrete

sizing algorithms use the continuous sizing formulation to find a discrete solution, by discretizing the continuous solution or using it to guide another discrete approach. Therefore, this work describes some continuous sizing approaches to explain the concepts behind such algorithms that can be applied in the discrete problem as well.

Continuous sizing methods model the delay, area and power as continuous functions of the design parameters similarly to the transistor sizing problem. This model is used to formulate an optimization problem to find a set of continuous sizes that optimize an objective.

With the use of convex delay models, it can be optimally solved by Lagrangian relaxation algorithms. Examples of approaches applied to the continuous gate sizing problem are presented in Chapter 4.

#### 3.3.2 Discrete Gate Sizing and Threshold Voltage Assignment

Discrete gate sizing is a known NP-hard combinatorial optimization problem (LI, 1993). It has been extensively studied in the last couple of decades with several different focuses. Many approaches have been proposed to handle a variety of objectives. Sizing algorithms for power (COUDERT; HADDAD, 1996), timing yield (DUTT; REN, 2010), low power standard cell library generation (RAHMAN et al., 2010; AFONSO et al., 2009), placement (CHEN; HSIEH; PEDRAM, 1999; REN; DUTT, 2011), glitch reduction (HASHIMOTO; ONODERA; TAMARU, 1998), variation-aware optimization (SINGH et al., 2005; SINGH; LUO; SAPATNEKAR, 2008) and others have been published. More details about related literature can be found in Chapter 4.

Most works use the following problem definition. Given a design, a standard cell library  $\mathcal L$  and a timing analysis engine:

where  $x_i$  is the objective associated with cell i (usually area or power),  $a_i$  is the arrival

Junction /

Substrate leakage Subthreshold leakage leakage

Figure 3.2: Sources of leakage power in a MOS transistor.

Source: Lee and Gupta (2012)

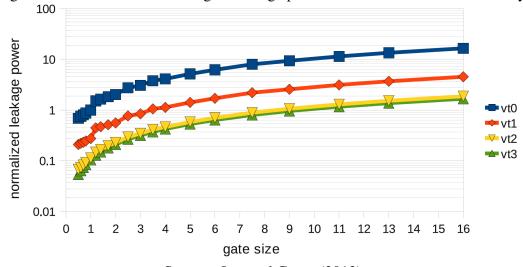

Figure 3.3: Normalized inverter gate leakage powers in a commercial 45nm library.

Source: Lee and Gupta (2012)

time at i, T is the maximum delay allowed (clock period) and  $D_i$  is the delay associated with cell i.

The  $V_t$  assignment problem has a formulation similar to the discrete gate sizing problem. In fact, the formulation is the same if there are no specific rules/constraints to the use of different  $V_t$  levels.

While the delay of a gate decreases linearly with increasing width, it decreases super-quadratically with decreasing  $V_t$  (SAPATNEKAR, 2004). This makes  $V_t$  decreasing more effective for reducing the delays of gates.

Figure 3.2 shows the sources of leakage power. The leakage power due to subthreshold conduction is exponentially related to the threshold voltage. This is the main reason for the presence of multiple- $V_t$  cells in standard cell libraries. Since the relationship between leakage and gate size is linear, high- $V_t$  cells enable much bigger leakage power reduction than using sizing alone. Figure 3.3 shows the normalized leakage power as a function of the gate size.

<sup>&</sup>lt;sup>1</sup>Less than linear if the increase in capacitance for the previous stage of logic is accounted for – internal capacitances also go up.

Most modern technologies allow the use of two or more  $V_t$  levels in order to provide cell options with less leakage power than the standard or fastest  $V_t$ . When combined with gate sizing,  $V_t$  assignment adds another dimension to the solution space, making the use of simplified delay models more complicated. Therefore, many works in literature deal with the  $V_t$  assignment problem separated from the gate sizing, using specific algorithms to solve it. Also, it is common to let the designer choose which  $V_t$  are available for the algorithms, limiting or expanding the number of options.

In this work, we simultaneously address discrete gate sizing and  $V_t$  assignment in order to provide power-optimized solutions. In this way we are able to explore a larger solution space to find a near-optimal solution.

#### 4 RELATED WORKS AND STATE-OF-THE-ART

This chapter presents the previous literature that addresses the cell selection problem. The first section of this chapter briefly summarizes the early literature and publications that have relevant contributions to the problem and especially to the development of this work. The second section summarizes the most recent publications that delimit the state-of-the-art and the two ISPD contests held in 2012 and 2013.

The titles of subsections reflect the respective paper titles or the name of the proposed tool.

#### **4.1 Early Literature**

This section details the most relevant related works. The publications are presented in a chronological order to better relate the research to the challenges imposed by the evolution of fabrication process and the design methodologies to which the algorithms can be applied to.

We briefly describe the methods present in some of the most relevant works in the literature that have contributed to the development of cell selection algorithms, especially the algorithms developed and presented in this work.

#### **4.1.1 TILOS**

Fishburn and Dunlop (1985) present a transistor sizing algorithm using posynomial programming and convex optimization techniques with a distributed RC model. The capacitances are proportional to transistor size and the resistance is inversely proportional to transistor size.

TILOS starts with minimum transistor sizes for all transistors. A static timing analysis is performed, assigning the latest times (to go low/high) to each node. Then, paths violating the setup timing constraint are traversed in reverse topological order. Transistors that are too slow are examined and the transistor with the highest sensitivity is increased.

The sensitivity function is as follows.

$$D'(x) = RC_u - \frac{R_u C}{x^2} \tag{4.1}$$

where x is the transistor width,  $C_u$  and  $R_u$  are capacitance and resistance of a unit-sized transistor and C and R are the wire capacitance and resistance, respectively.

Results show that TILOS can improve circuit timing and reduce area. However, the runtime is proportional to the number of timing paths, which is exponential with the number of elements, making it impractical to apply such an algorithm to medium size (10K+) CMOS circuits.

#### 4.1.2 Gate Sizing in MOS Digital Circuits with Linear Programming

References published by Berkelaar and Jess (1990), Berkelaar, Buurman and Jess (1994), Berkelaar, Buurman and Jess (1996) present an algorithm where the gate sizing optimization problem is mapped into a linear program, which is then solved by the Simplex algorithm. A simple (nonlinear) delay model is proposed. A piece-wise linear approximation is performed to reduce linearization error. Any convex delay model can be used with the algorithm without loss of optimality.

The approach guarantees to find the global optimum (considering the inaccurate timing model used), and has proven feasible for circuits of up to several thousand cells. However, this comes with considerable increase in area of up to 172%.

## 4.1.3 Delay and Area Optimization in Standard-Cell Design

Lin, Marek-Sadowska and Kuh (1990) apply a sensitivity-based heuristic to the discrete cell selection problem. Sensitivities are defined as the ratio between the variation of delay and area. This process of choosing cells based on local cost calculations is the base of several algorithms, with different objectives and different formulations to include, or not, components that estimate the impact on the global solution.

Another feature used together with sensitivities is the "criticality". The criticality is the ratio between the cell delay and its weighted slack. The weighted slack is the slack divided by the path length.

The proposed algorithm starts from all cells set to the smallest option. Then an iterative phase that increase the sizes is applied to solve timing violations. Next a size decreasing phase recovers area on cells on positive slack paths. The two phases are repeated until convergence or stop criteria are met.

The complexity of the proposed algorithm is  $O(n^2)$ . The results show area improvements ranging from -2%<sup>1</sup> to 29% for a set of nine benchmarks obtained from misII technology mapping tool (DETJENS et al., 1987).

#### **4.1.4** On the Circuit Implementation Problem

References (LI et al., 1992; LI et al., 1993) present a pseudo-polynomial time algorithm, applying suitable decomposition techniques and dynamic programming that obtain optimal solutions for basic series-parallel circuits<sup>2</sup>.

Six heuristics are presented to obtain minimal area circuit implementations given a delay constraint. The authors observe that more sophisticated heuristics handle the problem better than the simpler ones. Also, proofs that both basic circuit implementation and general circuit implementation problems are NP-hard are presented.

Another publication by Li (1993) proves that the discrete gate sizing algorithm is strongly NP-hard, implying that for arbitrary DAGs there is no pseudo-polynomial time algorithm to obtain the exact solution unless P=NP.

#### 4.1.5 Gate sizing for constrained delay/power/area optimization

The works from Coudert (1996), Coudert, Haddad and Manne (1996), Coudert (1997) present a general purpose gate sizing algorithm GS that is oriented to a pure combinatorial problem optimization, enabling the use of complex cost models. To the best of our knowledge, Coudert (1996) is the first work to address the challenges of gate sizing in modern real-life designs using a standard cell library and an accurate table lookup based nonlinear delay model. With focus on real-life designs, the proposed algorithm uses accurate delay and power models during the optimization process.

The proposed method first evaluates all cells with the calculation of gradients (variation of the cost function when resizing a node). These gradients are used to choose the new sizes for all cells based on the cost function. Then, a new iteration is performed only with cells that have an updated gradient. The process repeats until some convergence criterion is met.

<sup>&</sup>lt;sup>1</sup>Degradation in area caused by improvement in delay.

<sup>&</sup>lt;sup>2</sup>McNall and Casavant (1990) apply similar techniques (dynamic programming) for the synthesis of pipelined architectures.

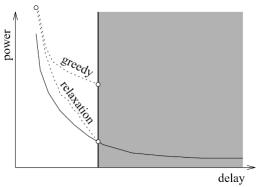

Figure 4.1: Comparison of the behaviors of the proposed method and a greedy method for power optimization.

Source: Coudert (1997)

The proposed algorithm can be applied to delay, area and power minimization. In the first case, the algorithm will iteratively process the netlist to choose the best (discrete) sizes that minimize delay. The second and third cases start from a delay optimized solution (obtained with GS) and then proceeds to area/power optimization for the following reasons: 1) Optimizing the delay gives plenty of alternatives for area/power optimization, i.e., going far away from the infeasible region makes power minimization less likely to be trapped in a local minimum. 2) The power optimization is done within the feasible region by relaxing the delay constraints using a penalty/benefit function.

This penalty/benefit function will balance the delay and power through the whole path, as opposed to a greedy method that resizes as many noncritical nodes as possible to their minimal power. Such a greedy approach would deliver low quality results by creating critical paths without power savings proportional to the increase in path delays, preventing most of the other nodes from being resized and saving more power. This behaviour is exposed in Figure 4.1, showing the superiority of the proposed method over the greedy method in scenarios with different timing constraints. The shaded areas in the charts represent solutions with timing constraint violations.

The work also shows a very important analysis of different methods to find a feasible solution with minimal power. Figure 4.2 shows (a) ping-pong, (b) penalty function, and (c) relaxation based constrained optimization. The case shown in Figure 4.2 (b) resembles the behavior of the simulated annealing method presented in this work (Section 5.1, Chapter 5), where the power reduction is obtained while creating timing violations until the point where violations are penalized in detriment of power. The main Lagrangian relaxation algorithm proposed in this work has an hybrid behavior between Figure 4.2 (a) and (c), where the algorithm finds a feasible solution in terms of timing and

(b) (c) (a) Source: Coudert (1997)

Figure 4.2: Behavior of three different methods for power optimization.

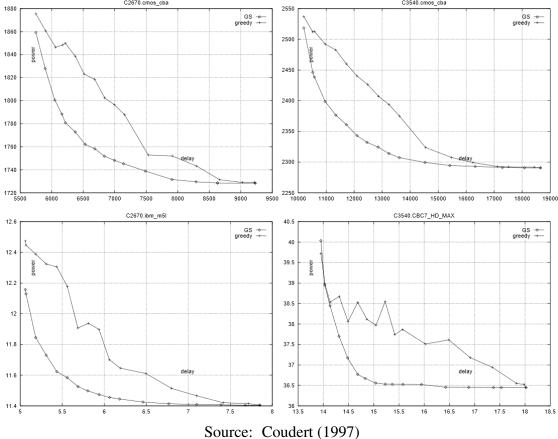

Figure 4.3: Power-delay curves for different designs for GS and greedy method.

then reduces power, but allowing unfeasible solutions with small violations (ping-pong effect).

Figure 4.3 shows four power-delay curves for different designs for GS and a greedy method. The curves clearly show the superiority of GS over the greedy method in terms of power. The smooth behavior of power along with different target delays is important to measure the quality of the proposed methods because it shows the stability of the algorithm in different scenarios where delay and power have different weights in the input design.

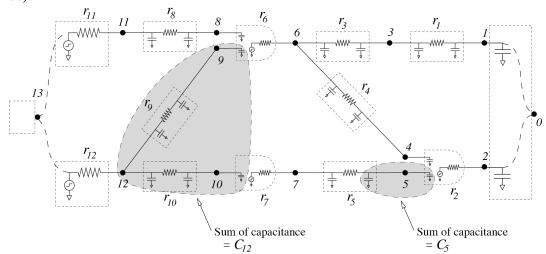

Figure 4.4: Circuit representation after replacing the components by their models (dashed lines).

Source: Chen, Chu and Wong (1999)

Both GS and greedy results show good improvements in both delay and power. Comparing GS with the greedy method, there is only a small difference for delay values. On the other hand, GS results for power are in average 5.2% better than the greedy method.

## 4.1.6 Fast and Exact Simultaneous Gate and Wire Sizing by Lagrangian Relaxation

One of the most relevant Lagrangian relaxation works in gate sizing is presented by Chen, Chu and Wong (1999). It was the first work to prove convergence and to guarantee theoretical optimality for the continuous gate sizing problem using convex delay model. An exact algorithm for gate and wire sizing based on Lagrangian Relaxation and "one-gate/one-wire-at-a-time" local optimization is presented. The timing constraints are defined on the gates rather than on the signal paths. This will generate a linear number of timing constraints, allowing time complexity of  $O(n \times i)$ , where n is the number of gates and i is the number of iterations.

The proposed method uses the Elmore delay model (ELMORE, 1948) and the gate is modelled as a switch-level RC circuit with a resistance proportional to the gate size. Figure 4.4 shows how the circuit is represented after replacing the components by the their models (dashed lines).

The Primal Problem (PP) in the Lagrangian relaxation is formulated as follows:

$\mathcal{PP}$ :

minimize

$$\sum_{i=1}^{n} \alpha_{i} x_{i}$$

subject to

$$a_{j} \leq A_{0} \quad j \in input(0)$$

$$a_{j} + D_{i} \leq a_{i} \quad i \in \mathcal{G} \cup \mathcal{W} \land \forall j \in input(i)$$

$$D_{i} \leq a_{i} \quad i \in \mathcal{D}$$

$$L_{i} \leq x_{i} \leq U_{i} \quad i \in \mathcal{G} \cup \mathcal{W}$$

$$(4.2)$$

where  $\alpha$  is a user-specified constant weight for each component, x represents the area (or the leakage power) of the component, a is the arrival time, D the delay, L and U are the lower and upper limits for x. '0' is the sink node of the circuit and  $A_0$  the required arrival time at the output components.  $\mathcal{G}$ ,  $\mathcal{W}$  and  $\mathcal{D}$  are respectively the set of component indexes of gates, wires segments and input drivers in the circuit.

Introducing the Lagrange multipliers for each constraint:

$$L_{\lambda}(x,a) = \sum_{i=1}^{n} \alpha_{i} x_{i} + \sum_{j \in input(0)} \alpha_{j0}(a_{j} - A_{0})$$

$$+ \sum_{i \in \mathcal{G} \cup \mathcal{W}} \sum_{j \in input(i)} \lambda_{ij}(a_{j} + D_{i} - a_{i}) + \sum_{i \in \mathcal{D}} \lambda_{mi}(D_{i} - a_{i})$$

$$(4.3)$$

The Lagrangian relaxation subproblem then becomes:

$$\mathcal{LRS}/\lambda$$

:

minimize  $L_{\lambda}(x,a)$  (4.4)

subject to  $L_{i} \leq x_{i} \leq U_{i} \quad i \in \mathcal{G} \cup \mathcal{W}$

Using the Karush-Kuhn-Tucker (KKT) conditions to optimality, the problem is greatly simplified, eliminating the arrival time from the equation for the dual problem. This transformation allows only delay calculation during the  $\mathcal{LRS}$  solving. The simplified equation becomes:

$$L_{\mu}(x) = \sum_{i=1}^{n} \alpha_i x_i + \sum_{i=1}^{n+s} \mu_{ij} D_i$$

(4.5)

where,  $\mu_i = \sum_{j \in input(i)} \lambda_{ij}$  for  $0 \le i \le n + s$  (any node in the circuit).

This equation only depends on the gate delays. Using a convex delay model (like the Elmore delay model) the solution is guaranteed to be optimal, although such model is inaccurate.

In order to solve the Lagrangian relaxation subproblem, a new set of sizes for all components is calculated for a fixed set of multipliers. When  $i \in \mathcal{G}$ , let  $x_i$  be the gate size,  $r_i$  be the output resistance of the gate and  $c_i$  be the input capacitance of a pin of the gate. Let  $\hat{r}_i$  and  $\hat{c}_i$  be respectively the unit size output resistance and the input capacitance per unit size of gate i. The optimal local sizing of component i is given by equation 4.6.

$$x_i^* = min\left(U_i, max\left(L_I, \sqrt{\frac{\mu_i \hat{r}_i C_i}{R_i \hat{c}_i + \alpha_i}}\right)\right)$$

(4.6)

where

$$R_{i} = \sum_{j \in input(i)} \mu_{i} \frac{\hat{r}_{i}}{x_{j}}$$

$$C_{i} = \sum_{k \in output(i)} \mu_{i} \frac{\hat{c}_{k}}{x_{k}}$$

$$(4.7)$$

The proposed iterative algorithm to solve the Lagrangian relaxation subproblem  $SOLVE\_LRS/\mu$  is shown in Figure 4.5a. This algorithm performs the sizing (based on the calculated values of capacitance and resistance) with fixed Lagrange multipliers.

Algorithm  $SOLVE\_LDP$  shown in Figure 4.5c finds the optimal set of multipliers. Initially, an arbitrary set of Lagrange multipliers respecting the Karush–Kuhn–Tucker (KKT) conditions ( $\lambda \in \Omega_{\lambda}$ , where  $\Omega_{\lambda}$  is the set of multipliers that respect the flow conservation property) is set (line 1). Then, the iterative sizing algorithm calculates the new sizes until convergence (line 2). After convergence of  $SOLVE\_LRS/\mu$ , a new set of Lagrange multipliers is calculated (line 3) and projected into  $\Omega_{\lambda}$  (line 4).

The algorithm SGWS-LR shown in Figure 4.5b solves optimally the gate sizing problem. Line 1 is the the iterative method to find the optimal set of Lagrange multipliers  $\lambda$ . Then,  $SOLVE\_LRS$  performs the optimal sizing for each component. Algorithm  $SOLVE_LDP$  in Figure 4.5c finds the set of Lagrange multipliers for the new solution, using an user-defined step size  $\rho_k$ .

Those algorithms are the main inspiration for the Lagrangian relaxation-based algorithm presented in this work. In the discrete case, the optimality properties are lost, but the algorithm is still able to converge to an optimized solution.

Our work also presents algorithms to circumvent the use of an arbitrary initial set of multipliers in  $SOLVE\ LDP$ .

Figure 4.5: Algorithms (a)  $SOLVE\_LRS/\mu$ , (b)  $SOLVE\_LDP$ , and (c) SGWS-LR.

```

ALGORITHM SOLVELRS/\mu:

ALGORITHM SGWS-LR:

Output: x = (x_1, \dots, x_n) which minimizes L_{\mu}(x)

Output: the optimal gate and wire sizing solution x

1. for i := 1 to n do x_i := L_i

2. /* Finding C'_i for 1 \le i \le n by traversing

1. Call SOLVE_LDP to find the optimal \lambda.

2. \mu = (\mu_0, \dots, \mu_{n+s}) where \mu_i = \sum_{j \in input(i)} \lambda_{ji}

the circuit in a reverse topological order */

\quad \mathbf{for} \ i := 1 \ \mathbf{to} \ t \ \mathbf{do}

3. Call SOLVE_LRS/\mu to find the optimal x.

C_i' := \left\{ \begin{array}{ll} C_i^L & \text{if } i \in \mathcal{G} \\ C_i^L + f_i/2 & \text{if } i \in \mathcal{W} \end{array} \right.

(b)

for i := t + 1 to n do

C_i' := \left\{ \begin{array}{ll} 0 & \text{if } i \in \mathcal{G} \\ f_i/2 & \text{if } i \in \mathcal{W} \end{array} \right.

ALGORITHM SOLVE_LDP:

Output: \lambda which maximizes \mathcal{LRS}/\lambda

for all k s.t. i \in input(k) do

C'_i := \begin{cases} C'_i + \widehat{c}_k x_k & \text{if } k \in \mathcal{G} \\ C'_i + \widehat{c}_k x_k + f_k/2 + C'_k & \text{if } k \in \mathcal{W} \end{cases}

1. \hat{k} := 1 / * \text{ step counter } * /

\boldsymbol{\lambda} := \overline{\text{arbitrary initial vector in } \Omega_{\lambda}

2. \mu = (\mu_0, \dots, \mu_{n+s}) where \mu_i = \sum_{j \in input(i)} \lambda_{ji}

Solve \mathcal{LRS}/\lambda. (Solve \mathcal{LRS}/\mu by SOLVE LRS/\mu,

3./* Finding R_i and x_i for 1 \le i \le n by traversing

the circuit in a topological order */

and then calculate a_1, \ldots, a_{n+s} as in Section 3.2).

\quad \mathbf{for} \ i := n \ \mathbf{downto} \ 1 \ \mathbf{do}

3. /* Move to a new \lambda by adjusting multipliers \lambda_{ji} */

R_i := 0

for i := 0 to n + s do

for all j \in input(i) do

\text{ for all } j \in input(i) \text{ do }

\begin{cases} \lambda_{ji} + \rho_k(a_j - A_0) & \text{if } i = 0 \\ \lambda_{ji} + \rho_k(a_j + D_i - a_i) & \text{if } i \in \mathcal{G} \cup \mathcal{W} \\ \lambda_{ji} + \rho_k(D_i - a_i) & \text{if } i \in \mathcal{D} \end{cases}

\begin{cases} R_i + \mu_j \widehat{r}_j / x_j & \text{if } j \in \mathcal{G} \\ R_i + \mu_j \widehat{r}_j / x_j + R_j & \text{if } j \in \mathcal{W} \\ R_i + \mu_j R_{j-n}^D & \text{if } j \in \mathcal{D} \end{cases}

4. Project \lambda onto the nearest point in \Omega_{\lambda}.

x_i := \min \left( U_i, \max \left( L_i, \sqrt{\mu_i \hat{r}_i C_i' / (\hat{c}_i R_i + \alpha_i)} \right) \right)

5. k := k + 1

4. Repeat step 2 and 3 until no improvement.

6. Repeat step 2–5 until (\sum_{i=1}^n \alpha_i x_i - Q(\boldsymbol{\lambda})) \leq \text{error bd.}

(a)

(c)

```

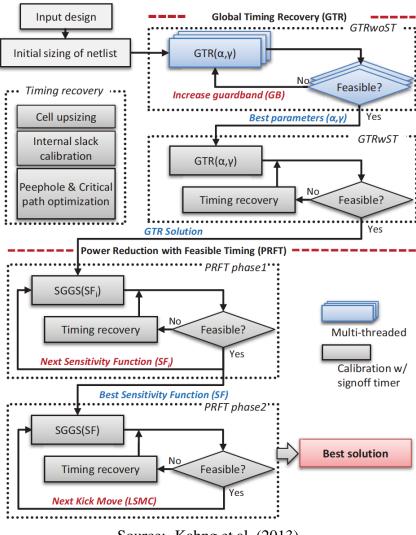

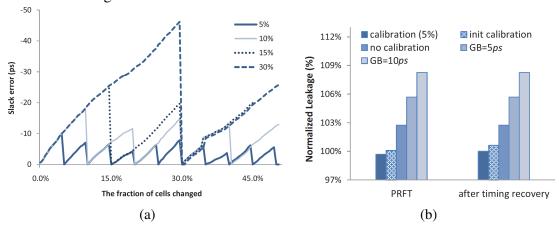

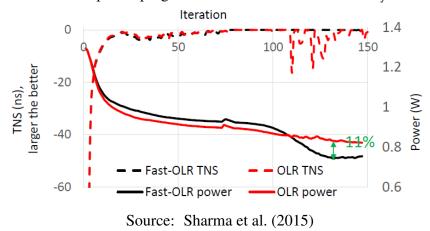

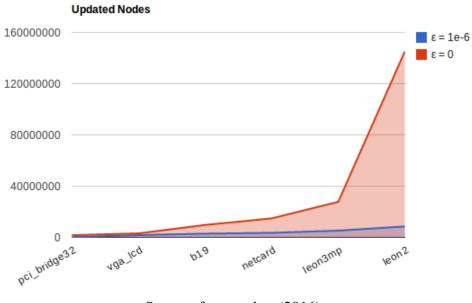

Source: Chen, Chu and Wong (1999)