## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

ISRAEL SPEROTTO DE MELLO

All-MOSFET M-2M Digital-to-Analog Converter for Operation with Very Low Supply Voltage

> Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Hamilton Duarte Klimach

Porto Alegre October 2015 Mello, Israel Sperotto de

All–MOSFET M–2M Digital–to–Analog Converter for Operation with Very Low Supply Voltage / Israel Sperotto de Mello. – Porto Alegre: PGMICRO da UFRGS, 2015.

85 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2015. Advisor: Hamilton Duarte Klimach.

CMOS analog design.

Digital to analog converter.

Low voltage design.

Mismatch.

Klimach, Hamilton Duarte. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Carlos Alexandre Netto Vice-Reitor: Prof. Rui Vicente Oppermann Pró-Reitor de Pós-Graduação: Prof. Vladimir Pinheiro do Nascimento Diretor do Instituto de Informática: Prof. Luis da Cunha Lamb Coordenador do PGMICRO: Prof<sup>a</sup>. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"If I have seen farther than others, it is because I stood on the shoulders of giants." — SIR ISAAC NEWTON

## ACKNOWLEDGMENTS

I would like to express my deepest gratitude to my advisors, Dr. Hamilton Klimach and Dr. Sergio Bampi, for their excellent guidance, caring, patience, and for providing me with an excellent atmosphere for doing research.

CNPq and Capes for the funding support given to this research. The IC–Brazil program, NSCAD support to Cadence tools and MOSIS for the MOSIS Educational Program (MEP), which gave opportunity to fabricate the circuits designed in this work.

Many thanks to Renato, Luís, Arthur, Filipe, Alonso, Jhon, Oscar, Diogo, Pedro, David and other workers in the laboratory for helping me. My research would not have been possible without their helps.

I would also like to thank my parents and my little brother. They were always supporting me and encouraging me with their best wishes.

Finally, I would like to thank my wife, Mariana. She was always there cheering me up and stood by me through the good times and bad.

## ABSTRACT

Since the 80s, development of manufacturing processes in semiconductors industry have sought to reduce supply voltage. The main purpose is to reduce circuits power consumption. The starting point was the old 5 V standard, set by TTL logic in the 70s, until modern circuits that operate with supply voltages below 1 V. However, since the early 2000s, supply voltage is stabilized at this level due to technological limitations difficult to overcome. This challenge has been studied by research groups around the world and several strategies have been proposed to design analog and digital circuits operating with supply voltages far below than 1 V. In fact, these groups have focused their studies on circuits operating with supply voltages lower than 0.5 V, some of them around 200 mV or even less. Among various classes of circuits, digital to analog data converters (DACs) and analog to digital data converters (ADCs) are fundamental circuits for integration process between analog and digital processing modules, thus essential for the implementation of complex SoCs (System-on-a-Chip) nowadays. This thesis presents a performance study over the MOSFET configuration in a M-2M ladder network (similar to the R-2R ladder network that is built with resistors) used as a digital to analog converter, when sized to operate at very low supply voltages (200 mV or less). This study is based on a MOSFET model that is continuous from the condition of weak inversion (subthreshold) to strong inversion, and includes a mismatch model between MOSFETs also valid for any operating condition. Based on this study, a design methodology able to establish trade-offs between "supply voltage", "effective resolution" and "silicon area" is developed. Electrical simulation results are presented and compared with the analytical results to support the methodology. The circuit has been sent to manufacturing and should start to be tested soon.

**Keywords:** CMOS analog design, digital to analog converter, low voltage design, mismatch.

# Projeto de um Conversor D/A M-2M para operação em baixa tensão de alimentação.

## RESUMO

Desde os anos 80 a evolução dos processos de fabricação de circuitos integrados MOS tem buscado a redução da tensão de alimentação, como forma de se reduzir o consumo de energia dos circuitos. Partiu-se dos antigos 5 V, padrão estabelecido pela lógica TTL nos anos 70, até os circuitos modernos que operam com alimentação pouco abaixo de 1 V. Entretanto, desde os primeiros anos da década de 2000, a tensão de alimentação está estabilizada neste patamar, devido a limitações tecnológicas que tem se mostrado difíceis de serem transpostas. Tal desafio tem sido estudado por grupos de pesquisa ao redor do mundo, e diversas estratégias tem sido propostas para se chegar a circuitos analógicos e digitais que operem sob tensão de alimentação bem inferior a 1 V. De fato estes grupos têm focado seus estudos em circuitos que operam com tensão de alimentação inferior a 0,5 V, alguns chegando à casa de 200 ou 100 mV, ou até menor. Dentre as diversas classes de circuitos, os conversores de dados dos tipos digital-analógico (DAC) e analógicodigital (ADC) são circuitos fundamentais ao processo de integração entre os módulos que processam sinais analogicamente e os que processam sinais digitalmente, sendo assim essenciais à implementação dos complexos SoCs (System-on-Chips) da atualidade. Este trabalho apresenta um estudo sobre o desempenho da configuração MOSFET em rede M-2M (similar à rede R-2R que emprega resistores), utilizada como circuito conversor digital-analógico, quando dimensionada para operar sob tensão de alimentação muito baixa, da ordem de 200 mV ou inferior. Tal estudo se baseia no emprego de um modelo para os MOSFETs que é contínuo desde a condição de inversão fraca (subthreshold) até a inversão forte, e inclui o uso de um modelo de descasamento entre MOSFETs que é válido para qualquer condição de operação. Com base neste estudo foi desenvolvida uma metodologia de projeto, capaz de estabelecer as relações de compromisso entre "tensão de alimentação", "resolução efetiva" e "área ocupada em silício", fundamentais para se atingir um circuito otimizado. Resultados de simulação elétrica são apresentados e confrontados com os resultados analíticos, visando a comprovação da metodologia. O circuito já foi enviado para fabricação, e deve começar a ser testado em breve.

**Palavras-chave:** projeto de circuito analógico, conversor D/A, projeto com baixa tensão, descasamento.

## **LIST OF FIGURES**

| 1.1  | Evolution of (average) minimum channel length of MOS transistors over time. Picture taken from RABAEY (2002). | 16 |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Evolution of minimum and maximum supply voltage in digital in-                                                |    |

|      | tegrated circuits as a function of feature size. Picture taken from                                           |    |

|      | RABAEY (2002)                                                                                                 | 17 |

| 1.3  | Energy Generation and conversion network.                                                                     | 18 |

| 1.4  | Different energy gathering devices.                                                                           | 19 |

| 1.5  | Energy harvesting estimates, taken from Texas Instruments website                                             |    |

|      | TI (2010)                                                                                                     | 19 |

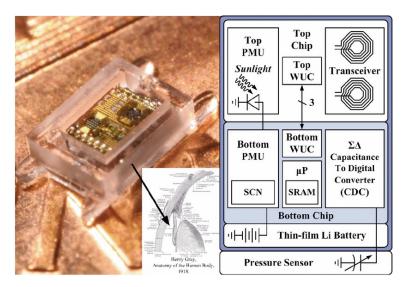

| 1.6  | The IOPM contains a MEMS pressure sensor, integrated solar cell,                                              |    |

|      | and microbattery in a biocompatible enclosure. Its cubic-millimeter                                           |    |

|      | size enables implantation through a minimally invasive incision                                               | 20 |

| 1.7  | Basic diagram for the use of converters                                                                       | 20 |

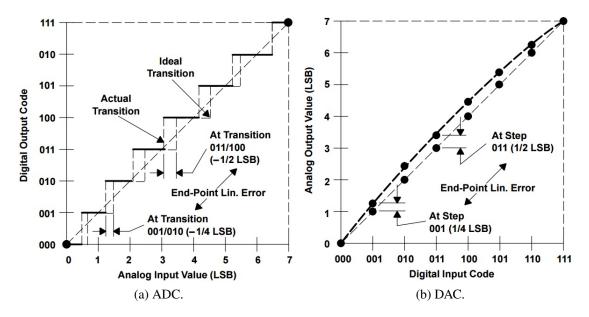

| 1.8  | Integral Nonlinearity (INL) Error. End-point linearity error of a linear                                      |    |

|      | 3-Bit natural binary-coded ADC or DAC. Offset error and gain error                                            |    |

|      | are adjusted to the value zero                                                                                | 21 |

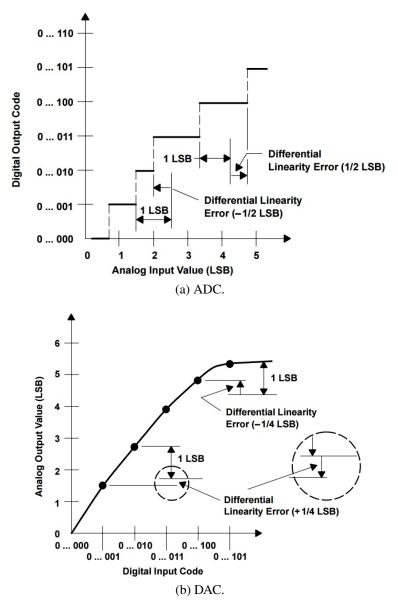

| 1.9  | Differential Nonlinearity (DNL) Error. Differential linearity error of                                        |    |

|      | a linear ADC or DAC.                                                                                          | 22 |

| 1.10 | Supply voltage for scientific ADCs through the years                                                          | 23 |

| 1.11 | SAR ADC architecture. Picture taken from LIN; HSIEH (2015)                                                    | 23 |

| 2.1  | DAC unity cell types: (a) charge, (b) voltage, (c) current and (d) current.                                   | 25 |

| 2.2  | R–2R voltage mode ladder network. Picture taken from MALOBERTI                                                |    |

|      | (2007)                                                                                                        | 26 |

| 2.3  | Current division principle.                                                                                   | 26 |

| 2.4  | Similar circuit showing the current division principle related to the                                         |    |

|      | aspect ratios.                                                                                                | 27 |

| 2.5  | M–2M Ladder Network                                                                                           | 28 |

| 2.6  | Low voltage DAC design. Picture taken from MORTEZAPOUR;                                                       |    |

|      | LEE (2000)                                                                                                    | 28 |

| 2.7  | DAC Schematic Showing the Segmented, Binary, and R-2R Combi-                                                  |    |

|      | nation. Picture taken from GREENLEY et al. (2001)                                                             | 29 |

| 2.8  | SAR ADC block diagram. Picture taken from HAMMERSCHMIED;                                                      |    |

|      | HUANG (1998)                                                                                                  | 29 |

| 2.9  | Circuit diagram of the 8-bit DAC. Picture taken from WANG; FUKATSU                                            | J; |

|      | WATANABE (1998)                                                                                               | 30 |

| 2.10 | Simplified schematic of an 8-bit DAC. The shift register at the bot-<br>tom is used for the series-to-parallel conversion of the input words. |          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | Picture taken from KLIMACH et al. (2008)                                                                                                      | 30       |

| 2.11 | Block diagram of a basic noise-shaping A/D converter                                                                                          | 31       |

| 2.12 | Typical baseband and RF transceiver configuration in wireless de-<br>vices back in 2002, e.g., WCDMA, WLAN. Picture taken from LIN;           |          |

| 2.13 | HAROUN (2002)                                                                                                                                 | 31       |

| 2.14 | SAUERBREY et al. (2003)                                                                                                                       | 32<br>32 |

| 3.1  | MOSFET association principle: one transistor can be substituted by a series-parallel association of identically designed transistors          | 34       |

| 3.2  | $M_d$ in Fig. 3.1 can be substituted by a series-parallel equivalent association.                                                             | 35       |

| 3.3  | M–2M CMOS Ladder Network.                                                                                                                     | 35       |

| 3.3  | Different implementations of a M–2M ladder.                                                                                                   | 35<br>36 |

|      | -                                                                                                                                             | 30<br>36 |

| 3.5  | 4-bits M–2M ladder for nonlinearity analysis.                                                                                                 | 30       |

| 3.6  | INL comparison between an asymmetric ladder with same sized tran-                                                                             | 27       |

| . –  | sistors and with INL reduction technique.                                                                                                     | 37       |

| 3.7  | Simplified 2-bit DAC and current division process.                                                                                            | 38       |

| 3.8  | Small-signal model for mismatch analysis.                                                                                                     | 39       |

| 3.9  | 3 bits DAC topology. This circuit                                                                                                             | 39       |

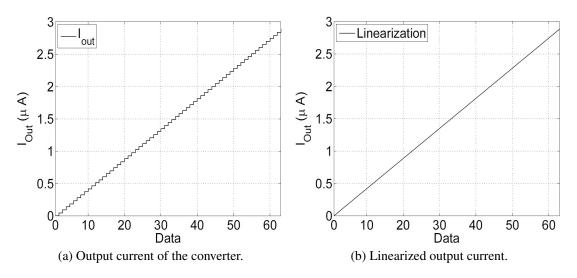

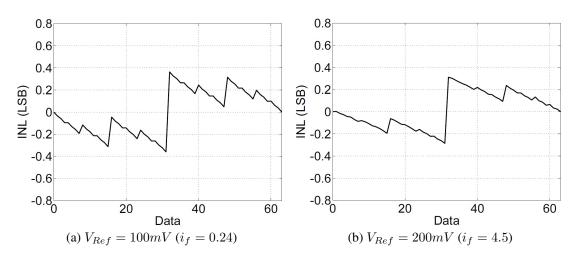

| 3.10 | Analytical behavior using Matlab.                                                                                                             | 41       |

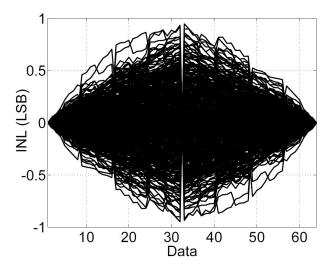

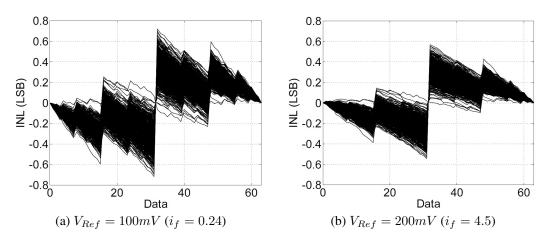

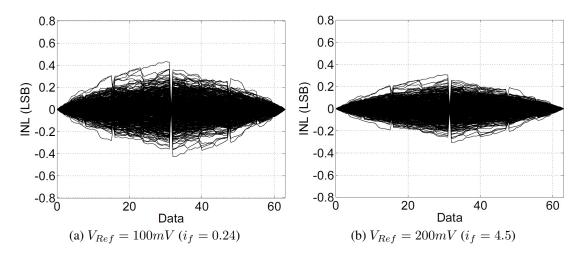

| 3.11 | Integral Nonlinearity of 500 samples analytically performed in Matlab.                                                                        | 41       |

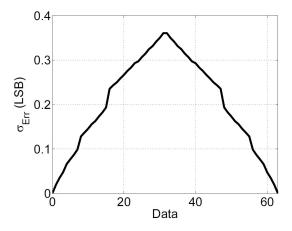

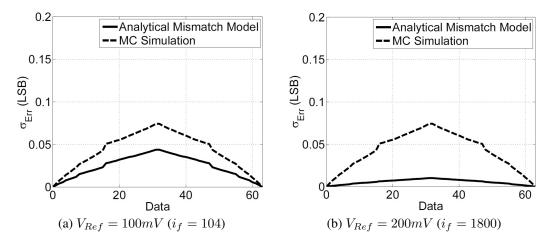

| 3.12 | Statistical error in terms of the standard-deviation of the output current.                                                                   | 42       |

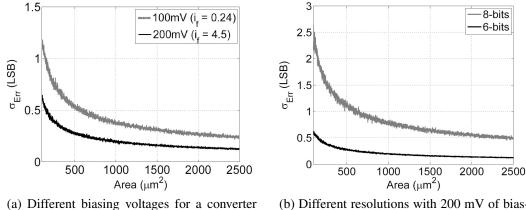

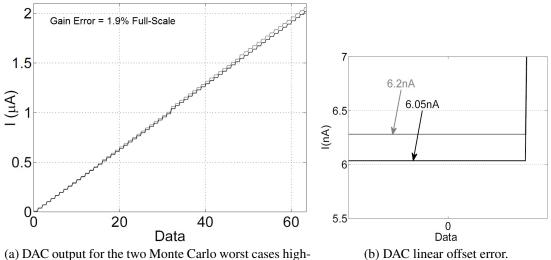

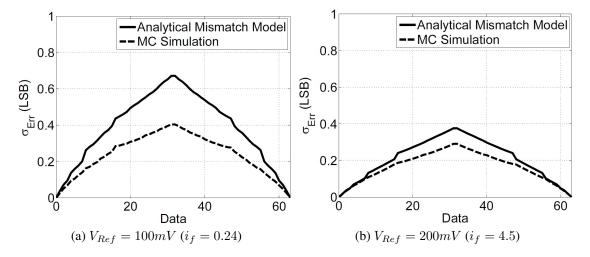

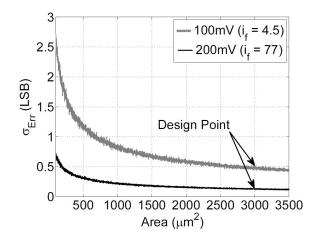

| 3.13 | Standard deviation of the M–2M DAC error as a function of the tran-<br>sistor area.                                                           | 42       |

| 3.14 | Standard deviation of the DAC error as a function of transistor area                                                                          |          |

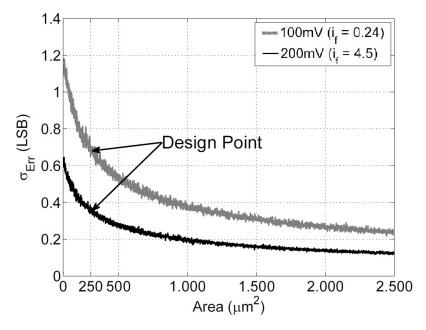

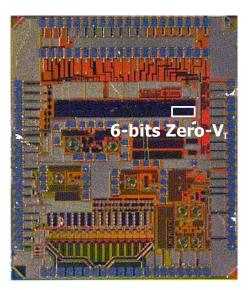

| 3.15 | and biasing voltage. Considering the converter with 6 bits of resolution. DAC layout.                                                         | 44<br>44 |

| 3.15 | Chip micrograph highlighting the 6-bit converter.                                                                                             | 44       |

|      |                                                                                                                                               |          |

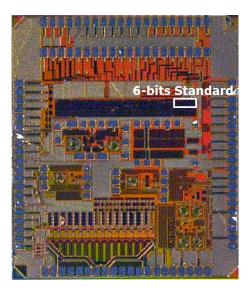

| 3.17 | DAC linear errors.                                                                                                                            | 45       |

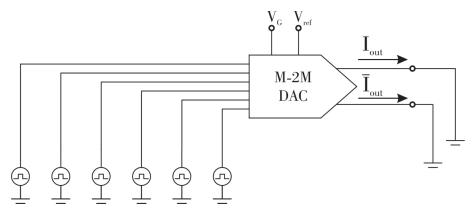

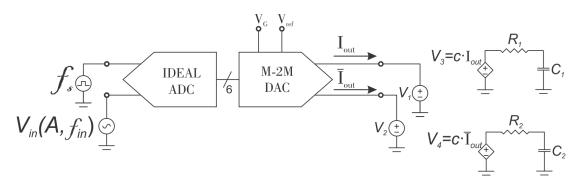

| 4.1  | Testbench for error analysis of a 6-bit DAC.                                                                                                  | 46       |

| 4.2  | Testbench for speed analysis.                                                                                                                 | 47       |

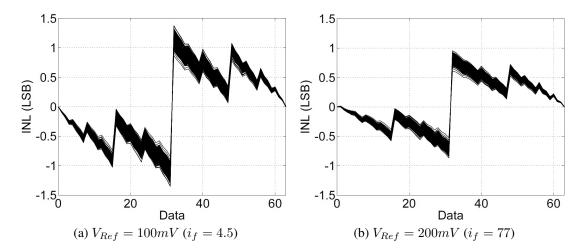

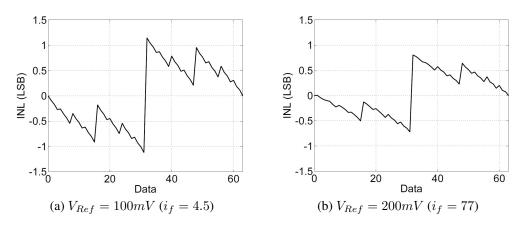

| 4.3  | 6-bit SVT converter INL for post-layout simulated results.                                                                                    | 48       |

| 4.4  | 6-bit SVT DAC Intrinsic nonlinearity.                                                                                                         | 48       |

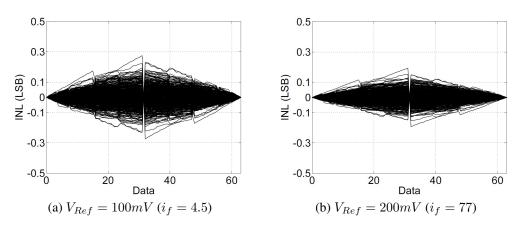

| 4.5  | 6-bit SVT converter INL given by mismatch for post-layout simulated results.                                                                  | 48       |

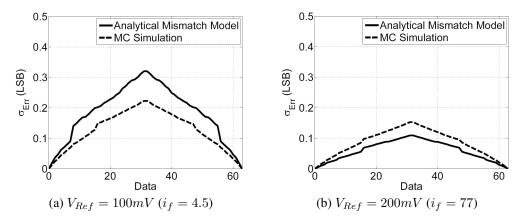

| 4.6  | 6-bit SVT DAC comparison between analytical and post-layout sim-<br>ulated results.                                                           | 49       |

| 4.7  | Standard deviation of DAC error as a function of $Low-V_T$ transistor                                                                         | 47       |

| 4./  | area. 8-bits converter. $V_G = V_{Ref} = 100mV$ ( $i_f = 4.5$ ) and $V_G =$                                                                   | 50       |

|      | $V_{Ref} = 200mV (i_f = 77).$                                                                                                                 | 50       |

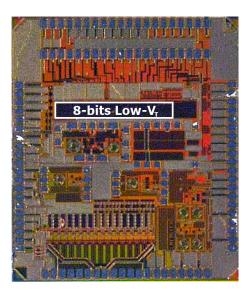

| 4.8  | 8-bits LVT DAC layout.                                                                                                                        | 50       |

| 4.9  | Chip micrograph highlighting the 8-bit Low– $V_T$ converter                                                                                   | 50       |

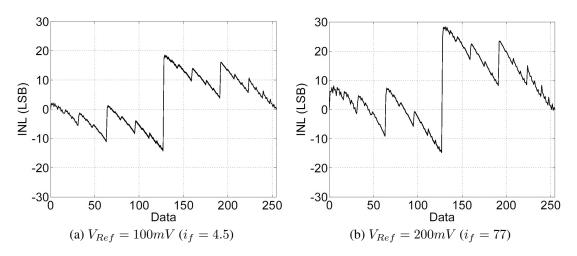

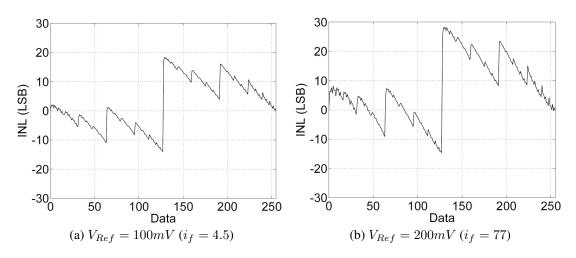

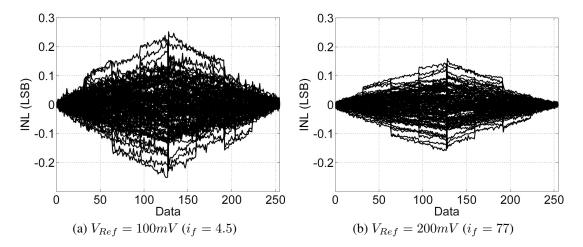

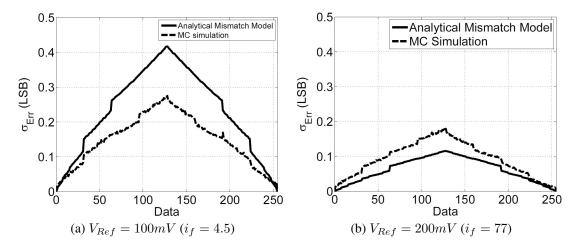

| 4.10 | 8-bit LVT converter INL for post-layout simulated results                                                                                     | 51       |

| 4.11 | 8-bit LVT DAC Intrinsic nonlinearity.                                                                                                         | 51       |

| 4.12  | 8-bit LVT converter INL given by mismatch for post-layout simulated results.              | 51       |

|-------|-------------------------------------------------------------------------------------------|----------|

| 4.13  | 8-bit LVT DAC comparison between analytical and post-layout simulated results.            | 52       |

| 4.14  | 6-bit LVT converter INL for post-layout simulated results.                                | 52<br>52 |

| 4.14  | 6-bit LVT DAC Intrinsic nonlinearity.                                                     | 52<br>53 |

| 4.15  | 6-bit LVT converter INL given by mismatch for post-layout simulated                       | 55       |

| 4.10  | results.                                                                                  | 53       |

| 4.17  | 6-bit LVT DAC comparison between analytical and post-layout sim-                          | 00       |

| 1.17  | ulated results.                                                                           | 53       |

| 4.18  | 6-bit ZVT DAC layout                                                                      | 54       |

| 4.19  | Chip micrograph highlighting the 6-bit ZVT DAC.                                           | 54       |

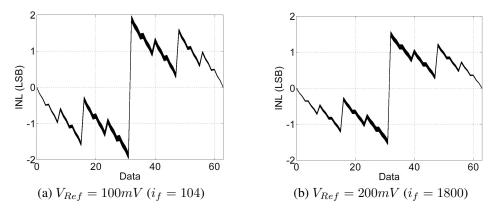

| 4.20  | 6-bit ZVT converter INL for post-layout simulated results                                 | 55       |

| 4.21  | 6-bit ZVT DAC Intrinsic nonlinearity.                                                     | 55       |

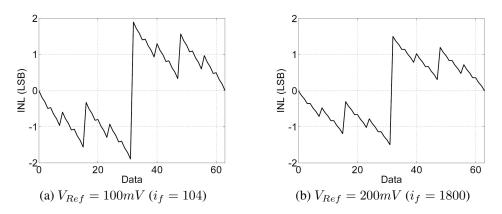

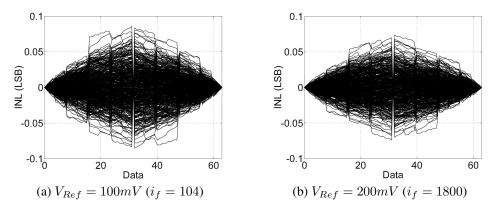

| 4.22  | 6-bit ZVT converter INL given by mismatch for post-layout simu-                           |          |

|       | lated results.                                                                            | 55       |

| 4.23  | 6-bit ZVT DAC comparison between analytical and post-layout sim-                          |          |

|       | ulated results.                                                                           | 56       |

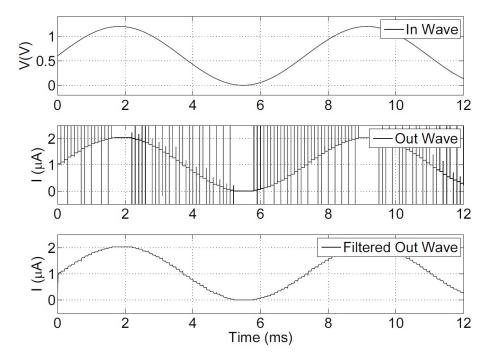

| 4.24  | ADC input and the 6-bit SVT DAC output waves. The sampling fre-                           |          |

|       | quency is 10 kS/s and $V_{Ref} = 200 mV$ .                                                | 57       |

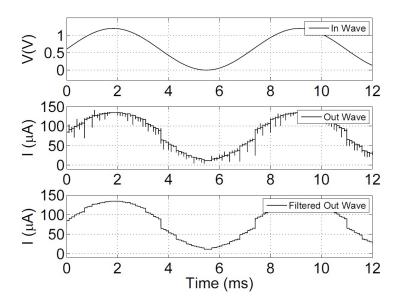

| 4.25  | ADC input and LVT DAC output waves. 8-bits of resolutions and                             |          |

|       | sampling frequency of 10 kS/s at $V_{Ref} = 200mV$                                        | 58       |

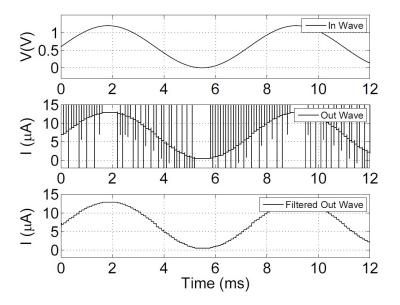

| 4.26  | ADC input and LVT DAC output waves. 6-bits of resolutions and                             |          |

|       | sampling frequency of 10 kS/s at $V_{Ref} = 200mV$                                        | 58       |

| 4.27  | ADC input and 6-bit ZVT DAC output waves. The sampling fre-                               |          |

|       | quency is 10 kS/s and $V_{Ref} = 200 mV$                                                  | 59       |

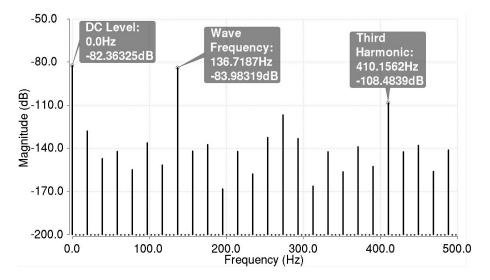

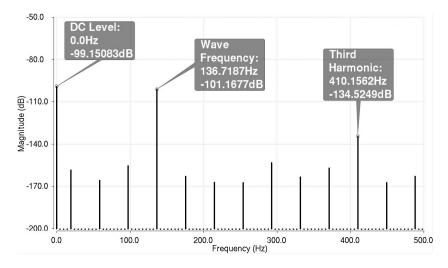

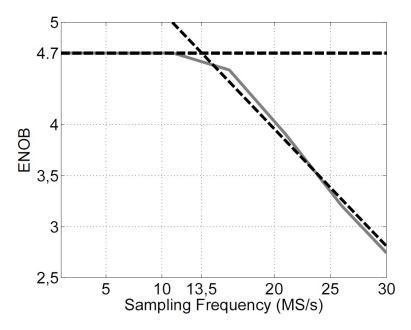

| 4.28  | Discrete Fourier Transform of the 6-bit SVT DAC output signal at 10                       |          |

|       | kS/s and $V_{Ref} = 200mV$                                                                | 59       |

| 4.29  | Variation of the ENOB with the sampling frequency ( $V_{Ref} = 200mV$ ).                  |          |

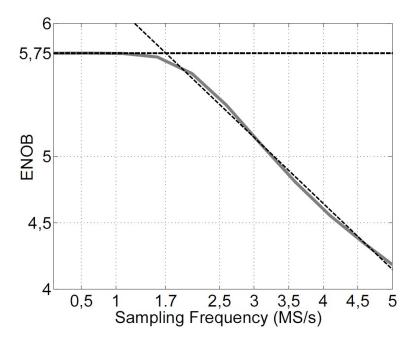

|       | 6-bit SVT DAC.                                                                            | 60       |

| 4.30  | Discrete Fourier Transform of the 6-bit SVT DAC output signal at 10                       |          |

|       | kS/s and $V_{Ref} = 100mV$                                                                | 60       |

| 4.31  | Variation of the ENOB with the sampling frequency ( $V_{Ref} = 100mV$ ).                  | (1       |

| 4.22  | 6-bit SVT DAC.                                                                            | 61       |

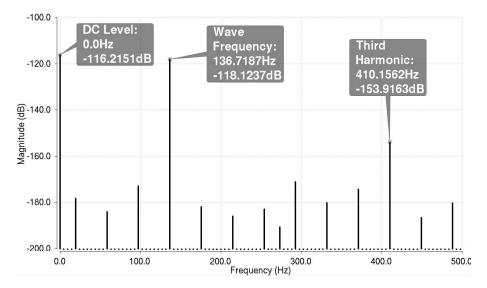

| 4.32  | Discrete Fourier Transform of the 8-bit LVT DAC output signal at 10                       | (1       |

| 4.22  | kS/s and $V_{Ref} = 200mV$                                                                | 61       |

| 4.33  | Discrete Fourier Transform of the 6-bit LVT DAC output signal at 10                       | ()       |

| 4.2.4 | kS/s and $V_{Ref} = 200mV$                                                                | 62       |

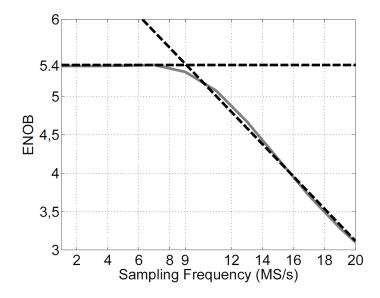

| 4.34  | Variation of the ENOB with the sampling frequency $(V_{Ref} = 200mV)$ .<br>6-bit LVT DAC. | 62       |

| 4.35  | Discrete Fourier Transform of the 6-bit ZVT DAC output signal at 10                       | 02       |

| 4.55  | kS/s and $V_{Ref} = 200mV$                                                                | 63       |

| 4.36  | Variation of the ENOB with the sampling frequency $(V_{Ref} = 200mV)$ .                   | 05       |

| 1.50  | 6-bit ZVT M–2M DAC                                                                        | 63       |

|       |                                                                                           | 00       |

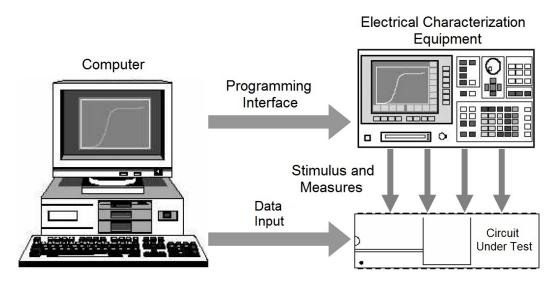

| 5.1   | Test setup for measurements                                                               | 70       |

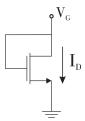

| B.1   | Standard NMOS transistor diode connected                                                  | 76       |

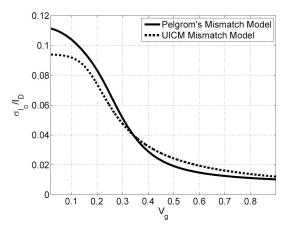

| B.2 | Comparison between the UICM Mismatch model used in this work |    |

|-----|--------------------------------------------------------------|----|

|     | and the Pelgrom's Mismatch model                             | 76 |

## LIST OF TABLES

| 1.1 | ITRS Summary 2013                                                                                                                                          | 17 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Transistors width (W). The channel length is the same for all $L = 2\mu m$ .                                                                               | 37 |

| 3.2 | Maximum channel length as a function of the maximum error                                                                                                  | 43 |

| 4.1 | Comparison between performances of all converters designed in this work with $V_{Ref} = 200mV$ . Results for post-layout extraction simulated on Virtuoso. | 65 |

| 4.2 | Comparison between performances of all converters designed in this work with $V_{Ref} = 100mV$ . Results for post-layout extraction simu-                  |    |

|     | lated on Virtuoso                                                                                                                                          | 65 |

| 4.3 | Comparison between state of art ADCs and this work                                                                                                         | 67 |

| 4.4 | Comparison between other DACs and this work.                                                                                                               | 68 |

## LIST OF ABBREVIATIONS AND ACRONYMS

| AC     | Alternating Current                                  |  |

|--------|------------------------------------------------------|--|

| ADC    | Analog-to-Digital Converter                          |  |

| CMOS   | Complementary metal-oxide-semiconductor              |  |

| CVS    | Carrier Velocity Saturation                          |  |

| DAC    | Digital-to-Analog Converter                          |  |

| dB     | Decibel                                              |  |

| DC     | Direct Current                                       |  |

| DNL    | Differential Nonlinearity                            |  |

| DSP    | Digital Signal Processing                            |  |

| ENOB   | Effective Number of Bits                             |  |

| FDSM   | Frequency-to-Digital $\Sigma\Delta$ Modulator        |  |

| FoM    | Figure of Merit                                      |  |

| Hz     | Hertz                                                |  |

| IBM    | International Business Machines Corporation          |  |

| IEEE   | Institute of Electrical and Electronics Engineers    |  |

| INL    | Integral Nonlinearity                                |  |

| ITRS   | International Technology Roadmap for Semiconductors  |  |

| LSB    | Least Significant Bit                                |  |

| LVT    | Low $V_T$ Transistor                                 |  |

| MC     | Monte Carlo                                          |  |

| MOS    | Metal-oxide-semiconductor                            |  |

| MOSFET | ET Metal-oxide-semiconductor Field Effect Transistor |  |

| MSB    | Most Significant Bit                                 |  |

| NMOS   | N-channel MOSFET                                     |  |

| Op-Amp | Operational Amplifier                                |  |

| PDK    | Process Design Kit                                   |  |

| PMOS  | P-channel MOSFET                        |

|-------|-----------------------------------------|

| RF    | Radio Frequency                         |

| SAR   | Successive Approximation Register       |

| SVT   | Standard $V_T$ Transistor               |

| UICM  | Unified Current Control Model           |

| VCO   | Voltage-Controlled Oscillator           |

| WCDMA | Wide-Band Code-Division Multiple Access |

| WLAN  | Wireless Local Area Network             |

| ZVT   | Zero $V_T$ Transistor                   |

## CONTENTS

| 1     |                                                                 | 16 |

|-------|-----------------------------------------------------------------|----|

| 1.1   | Power Supply Voltage Reduction in Electronic Circuits           | 16 |

| 1.2   | Electronic Circuits for Very Low Supply Voltage                 | 18 |

| 1.3   | Analog and Digital Signal Converters                            | 20 |

| 1.4   | Motivation                                                      | 24 |

| 1.5   | Organization                                                    | 24 |

| 2     | DATA CONVERTERS EVOLUTION                                       | 25 |

| 2.1   | The R–2R binary current divider                                 | 25 |

| 2.2   | The Current Division Principle                                  | 26 |

| 2.3   | The M-2M Ladder DAC                                             | 27 |

| 2.4   | Bibliographic Review                                            | 28 |

| 2.4.1 | R-2R ladder Review                                              | 28 |

| 2.4.2 | 2 M–2M ladder Review                                            | 29 |

| 2.4.3 | Very Low Voltage Converters Review                              | 31 |

| 3     | LOW VOLTAGE ALL-MOSFET DAC                                      | 33 |

| 3.1   | The All-Regions UICM MOSFET Model and Mismatch Model            | 33 |

| 3.2   | The Binary Weighting Principle                                  | 34 |

| 3.3   | DAC Circuit Description                                         | 35 |

| 3.3.1 |                                                                 | 36 |

| 3.4   | Circuit Design Methodology                                      | 38 |

| 3.5   | Design Space Exploration                                        | 41 |

| 3.6   | Channel Length Determination                                    | 43 |

| 3.7   | Transistor Sizing                                               | 44 |

| 3.8   | Linearity Errors                                                | 45 |

| 4     | RESULTS                                                         | 46 |

| 4.1   | DAC Simulation Test Benches                                     | 46 |

| 4.2   | DAC Simulation Results                                          | 47 |

| 4.2.1 | DAC Results: Standard MOSFETs                                   | 47 |

| 4.2.2 | DAC Results: Low- $V_T$ MOSFETs                                 | 49 |

| 4.2.3 |                                                                 | 54 |

| 4.3   | DAC Performance in Time Domain                                  | 57 |

| 4.3.1 | DAC Performance in Time Domain with Low– $V_T$ transistors      | 57 |

| 4.3.2 | DAC Performance in Time Domain with Zero– $V_T$ transistors     | 58 |

| 4.4   | DAC Performance in Frequency Domain                             | 59 |

| 4.4.1 | DAC Performance in Frequency Domain with Low– $V_T$ transistors | 61 |

| 1 2 1                                                                                                                                                                                                                  | 63<br>64       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 5         CONCLUSIONS                                                                                                                                                                                                  | 69<br>70       |

| REFERENCES                                                                                                                                                                                                             | 71             |

| APPENDIX A LIST OF PUBLICATIONS                                                                                                                                                                                        | 75             |

| APPENDIX B MISMATCH MODEL CONSIDERATIONS                                                                                                                                                                               | 76             |

| APPENDIX C MATLAB CODE                                                                                                                                                                                                 | 77             |

| APPENDIX D       SUMMARY IN PORTUGUESE         D.1       Introdução                                                                                                                                                    | 80<br>80       |

| <ul> <li>D.1.1 Redução da Tensão de Alimentação em Circuitos Eletrônicos</li> <li>D.1.2 Circuitos eletrônicos para baixíssima tensão de alimentação</li> <li>D.1.3 Conversores de Sinal Digital e Analógicos</li></ul> | 80<br>81<br>82 |

| D.1.4MotivaçãoD.1.5Organization                                                                                                                                                                                        | 83<br>83       |

|                                                                                                                                                                                                                        | 83<br>84<br>84 |

## **1 INTRODUCTION**

In this chapter will be presented the main subjects that were used as a motivation for this work, like supply voltage reduction on electronic circuits over the years and circuits operating with very low supply voltage. A brief review on the converters evolution over the years related to supply voltage is also performed. We then state the main objectives of this thesis and describe the work structure.

### **1.1 Power Supply Voltage Reduction in Electronic Circuits**

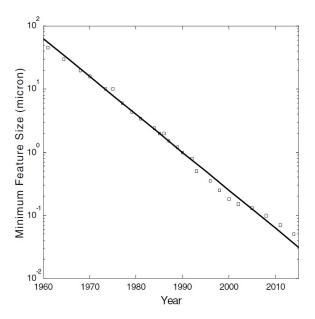

Over the last decades we have observed a spectacular increase in integration density and computational complexity of digital integrated circuits. Advances in device manufacturing technology allow a steady reduction of the minimum feature size such as the minimum transistor channel length realizable on a chip. To illustrate this point we have Fig. 1.1, which presents the evolution of the (average) minimum device dimensions starting from the 60s and projecting into the 21st century.

Figure 1.1: Evolution of (average) minimum channel length of MOS transistors over time. Picture taken from RABAEY (2002).

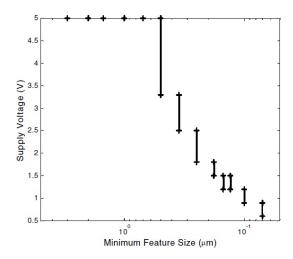

A scaling analysis performed by RABAEY (2002) showed how supply voltage is affected by the scaling process. Different scaling scenarios were presented for short channel devices, full scaling, general scaling and fixed–voltage scaling. In reality, full scaling is not a feasible option. First of all, to keep new devices compatible with existing components, voltages cannot be scaled arbitrarily. Having to provide for multiple supply voltages adds considerably to the cost of a system. As a result, voltages have not been scaled down along with feature sizes, and designers adhere to well-defined standards for supply voltages and signal levels. As is illustrated in Fig. 1.2, 5 V was the de *facto* standard for all digital components up to the early 90s, and a fixed-voltage scaling model was followed.

Figure 1.2: Evolution of minimum and maximum supply voltage in digital integrated circuits as a function of feature size. Picture taken from RABAEY (2002).

With the introduction of the  $0.5\mu m$  CMOS technology, new standards such as 3.3V and 2.5V make an inroad. Nowadays, a closer tracking between voltage and device dimension can be observed with the aid of the fixed–voltage scaling model. The International Technology Roadmap for Semiconductors ITRS (2013) build tables predicting some important features about semiconductor industry. In this case, we are interested in the supply voltage, so, using the fixed–voltage scaling model, the most recent compilation for technology nodes and supply voltages is presented on Tab. 1.1.

| Year of Production                                     | 2013    | 2015 | 2017 | 2019 | 2021  | 2023  |

|--------------------------------------------------------|---------|------|------|------|-------|-------|

| Logic Industry "Node Name" Label                       | "16/14" | "10" | "7"  | "5"  | "3.5" | "2.5" |

| $V_{dd}$ (High Performance, high $V_{dd}$ transistors) | 0.86    | 0.83 | 0.80 | 0.77 | 0.74  | 0.71  |

Table 1.1: ITRS Summary 2013

The aforementioned analysis provides a wide view of the CMOS technology advancements, which lead us to the next section that presents some electronic circuits operating with very low supply voltage.

## **1.2 Electronic Circuits for Very Low Supply Voltage**

The continuing scaling of CMOS technologies is the main driving factor behind low voltage operation, rapidly achieving sub-1 V supplies for process nodes below 130 nm. Current battery-operated systems require ultra-low current operation, that ranges from a few nanoamperes to a few microamperes, depending on the function being executed. Also future self-powered and self-sustaining electronic systems will require very low voltage operation, since the physical or chemical environmental strategies that can be used for energy harvesting generates from 10's to a few 100's of millivolts RABAEY et al. (2007).

The energy available is very small, therefore ultra low power design for both computation and communication devices is required. We will now present some circuits and solutions for this topic. With the evolution of MEMS and semiconductor technologies, it is now possible to integrate complete sense, compute and communicate features into ever smaller size factors. This opens the door for ubiquitous deployment, often in hard to reach or unreachable areas. In such cases battery replacement is virtually impossible, and replenishment of the energy supply using harvesting is essential. In recent years, researchers have identified a wide range of harvesting opportunities, and efficient harvesting devices have been developed. Yet, the energy available is still quite small, so ultra low power design for both computation and communication devices is an absolute necessity.

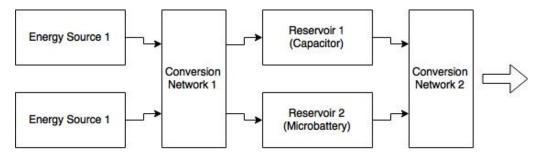

Of course that some complicating issues have to be considered when it comes to the efficient delivery of energy to circuits. The efficiency of the harvester often depends upon operating conditions. For instance: light may not always be available; storage is required if the operational cycles of the harvester and the circuitry are out of phase; voltages and currents delivered by a harvester are often not compatible with the needs of the circuitry. To overcome this issues its common to use the architecture showed on Fig. 1.3.

Figure 1.3: Energy Generation and conversion network.

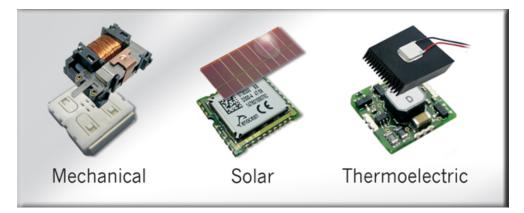

From this diagram we can relate several applications in use nowadays. From motion, solar and thermal energy sources we can gather power through sensors, like showed on Fig. 1.4, and convert it to a temporary energy reservoir. This stored energy can be used to power several kinds of circuits.

We have to keep in mind that energy levels are quite low, so the circuits must have low power consumption. Just to make it clear, the Fig. 1.5 was taken from the Texas Instruments website and presents the estimated energy that can be harvested from different sources.

Figure 1.4: Different energy gathering devices.

| Energy Source                 | Harvested Power          |

|-------------------------------|--------------------------|

| Vibration/Motion              |                          |

| Human                         | 4 μW/cm <sup>2</sup>     |

| Industry                      | 100 µW/cm <sup>2</sup>   |

| <b>Temperature Difference</b> |                          |

| Human                         | 25 μW/cm <sup>2</sup>    |

| Industry                      | 1–10 mW/cm <sup>2</sup>  |

| Light                         |                          |

| Indoor                        | 10 µW/cm <sup>2</sup>    |

| Outdoor                       | 10 mW/cm <sup>2</sup>    |

| RF                            |                          |

| GSM                           | 0.1 µW/cm <sup>2</sup>   |

| WiFi                          | 0.001 µW/cm <sup>2</sup> |

Figure 1.5: Energy harvesting estimates, taken from Texas Instruments website TI (2010).

A circuit example that is very interesting is an Intra-Ocular Pressure Monitor (IOPM) device, showed in Fig. 1.6, that was implanted in the eye of a glaucoma patient. This device is presented by CHEN et al. (2011) and uses a custom 1  $\mu$ Ah thin-film Li battery. The lifetime is 28 days with no energy harvesting. To extend lifetime, the device harvests light energy entering the eye with an integrated  $0.07mm^2$  solar cell and recharges the battery. Given the ultra-small solar cell size, energy autonomy requires average power consumption of less than 10nW. The IOPM achieved a power consumption of 5.3nW and the solar cell supplies up to 80nW ( $V_{HARVEST} = 500mV$ ) to the battery on a sunny day. Finally, the circuits requires 10 hours of indoor lighting or 1.5 hours of sunlight per day to achieve energy-autonomy.

All this talk is to reinforce the importance of this work. Low power circuits are undoubtedly one of the most important research areas nowadays.

Figure 1.6: The IOPM contains a MEMS pressure sensor, integrated solar cell, and microbattery in a biocompatible enclosure. Its cubic-millimeter size enables implantation through a minimally invasive incision.

## **1.3** Analog and Digital Signal Converters

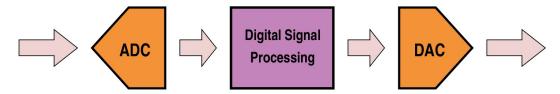

Of all circuits that can be study material for low voltage operation this thesis focus on Data Converters. This type of circuit appear on several different applications, like consumer electronics, communications, computing and control, instrumentation, etc.. Data converters emerged back in the 80s as a solution for signal processing. Digital Signal Processing (DSP) proved to be more efficient and replaces several application of analog circuits. The block diagram of Fig. 1.7 shows how to use Analog-to-Digital and Digital-to-Analog Converters.

Figure 1.7: Basic diagram for the use of converters.

Conversion involves quantization of the input, so it necessarily introduces a small amount of error. Instead of doing a single conversion, an ADC often performs the conversions ("samples" the input) periodically. The result is a sequence of digital values that have been converted from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal. The inverse operation is performed by a digital-to-analog converter (DAC).

Converters performance can be evaluated in several ways. Resolution, supply voltage, sampling frequency, linearity, power consumption and area are usually the main concerns when designing a converter. There are also other concerns linked to the aforementioned, like process technology, that directly affect supply voltage and area, Integral and Differential Nonlinearities (INL and DNL), Effective Number of Bits (ENOB), Total Harmonic Distortion and others.

We will briefly explain the INL and DNL errors that are of vital importance on this

work. The integral nonlinearity error shown in Fig. 1.8 (sometimes seen as simply linearity error) is the deviation of the values on the actual transfer function from a straight line. This straight line can be either a best straight line which is drawn so as to minimize these deviations or it can be a line drawn between the end points of the transfer function once the gain and offset errors have been nullified. The second method is called end-point linearity and is the usual definition adopted since it can be verified more directly. For an ADC the deviations are measured at the transitions from one step to the next, and for the DAC they are measured at each step. The name integral nonlinearity derives from the fact that the summation of the differential nonlinearities from the bottom up to a particular step, determines the value of the integral nonlinearity at that step TI (1999).

Figure 1.8: Integral Nonlinearity (INL) Error. End-point linearity error of a linear 3-Bit natural binary-coded ADC or DAC. Offset error and gain error are adjusted to the value zero.

The differential nonlinearity (DNL) error shown in Fig. 1.9 (sometimes seen as simply differential linearity) is the difference between an actual step width (for an ADC) or step height (for a DAC) and the ideal value of 1 LSB. Therefore if the step width or height is exactly 1 LSB, then the differential nonlinearity error is zero. If the DNL exceeds 1 LSB, there is a possibility that the converter can become non-monotonic. This means that the magnitude of the output gets smaller for an increase in the magnitude of the input. In an ADC there is also a possibility that there can be missing codes i.e., one or more of the possible  $2^n$  binary codes are never output.

Figure 1.9: Differential Nonlinearity (DNL) Error. Differential linearity error of a linear ADC or DAC.

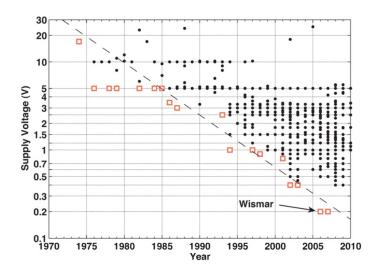

As pointed out by JONSSON (2010), the supply voltage can vary as much as one order of magnitude within the same node for scientific Analog to Digital converters (ADCs). Figure 1.10 is a scatter plot showing the highest supply voltage applied to each ADC, and the evolution of low-voltage state-of-the-art over time has been highlighted. Since DACs are mainly a vital part of ADCs we can apply the same rule to them.

Recent researches are focusing on low consumption converters for specific applications. The highly digital flash ADC designed by DALY; CHANDRAKASAN (2009) operates on the range of 0.2 V to 0.9 V with 6-bits of resolution. This converter intends to be energy efficient and have a figure of merit (FoM) of 125 fJ/conversion-step at a 0.4 V supply, where it achieves an ENOB of 5.05 at 400 kS/s. It is also important to say that this architecture uses a 5-bits capacitive feedback DAC in order to cancel comparator offsets.

Nowadays, power efficient circuits becomes more and more important. Sensing devices for detecting and monitoring biomedical signals are an example of this kind of circuits. The sensed signals are usually digitized by ADCs with moderate resolutions

Figure 1.10: Supply voltage for scientific ADCs through the years.

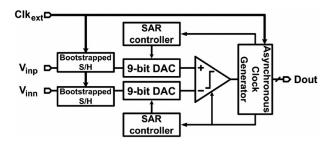

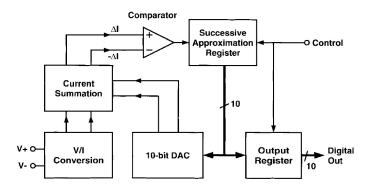

(8 - 12 bits) and sampling rate (1 - 1000 kS/s). Among various ADC architectures the SAR ADC shows a better power efficiency, also benefits from technology downscaling because it mainly consists of digital circuits, which get faster in advanced technologies. LIN; HSIEH (2015) developed a SAR ADC with 0.3 V supply and 10 bits of resolution. They used a merge-and-split switching DAC without common-mode voltage shift in order to reduce the switching energy of the DAC network by 83%. The circuit diagram is presented on Fig. 1.11 and achieved a FoM of 1.78 fJ/conversion-step.

Figure 1.11: SAR ADC architecture. Picture taken from LIN; HSIEH (2015).

## **1.4 Motivation**

We already pointed out the importance of data converters among electronic circuits and also highlighted a strong tendency on low voltage operation. Circuits working under this circumstances usually presents new design challenges. This work is focused on Digital-to-Analog Converters, more specifically on the CMOS R–2R ladder that is just a resistor ladder with MOS transistors instead. This particular topology is suitable for low voltage operation because the transistor network current division, that is the base of the digital–to–analog conversion process, is performed with the MOSFETs in the linear region either in strong or in weak inversion (or subthreshold) condition. Throughout this work it is demonstrated a design methodology that establish trade-off's between resolution, area, sampling speed and supply voltage.

## 1.5 Organization

This work is organized as follows: a review on the evolution of data converters will be presented on Chapter 2. The MOSFET model used for the circuit design and the all-MOSFET DAC for low voltage supply operation design is done in chapter 3. Post-layout simulation results are presented and discussed in Chapter 4. In Chapter 5 it is exposed the main conclusions and on the appendixes is presented some considerations about mismatch model, a Matlab routine used on the design methodology and the text in Portuguese.

## 2 DATA CONVERTERS EVOLUTION

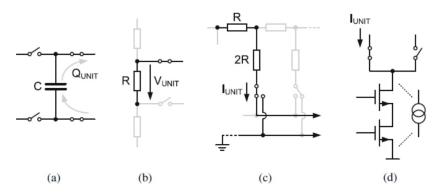

There are several strategies for implementing converters using weighting elements that are related to certain electrical quantities such as voltage, current and charge. In Fig. 2.1 we can see four different basic conversion cells.

Figure 2.1: DAC unity cell types: (a) charge, (b) voltage, (c) current and (d) current.

Associating the unity cells it is possible to represent quantities in a unary or binary way. This work will focus only on binary weighted current DACs.

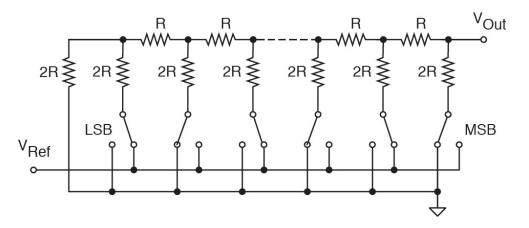

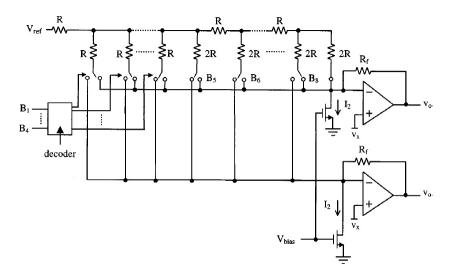

## 2.1 The R–2R binary current divider

Resistor ladder networks provide a simple, inexpensive way to perform digital to analog conversion (DAC). The most popular network is the R–2R ladder, mainly because of its inherent accuracy and ease of manufacture. Fig. 2.2 is a diagram of the basic R–2R ladder network with N bits. The "ladder" portrayal comes from the ladder-like topology of the network. Note that the network consists of only two resistor values, R and 2R (twice the value of R) no matter how many bits make up the ladder. Assume that a voltage-mode ladder connects the most significant bit (MSB) arm to  $V_{Ref}$  and all the others to ground. The circuit becomes a R–2R resistive divider of  $V_{Ref}$  leading to  $V_{Out} = V_{Ref}/2$ . If the next left switch is the only one connected to  $V_{Ref}$ , the voltage of the corresponding intermediate node results from a 2R - 6/5R division of  $V_{Ref}$  giving  $V_{n-1} = 3V_{Ref}/8$  and  $V_{Out} = V_{Ref}/4$ . It can be also verified that connecting the next left switch to  $V_{Ref}$  leads to  $V_{Out} = V_{Ref}/8$  and so forth.

The output of an R–2R ladder in the voltage mode is the superposition of terms that are the successive division of  $V_{Ref}$  by 2. For *n*-bit this gives

$$V_{Out} = \frac{V_{Ref}}{2}b_{n-1} + \frac{V_{Ref}}{4}b_{n-2} + \dots + \frac{V_{Ref}}{2^{n-1}}b_1 + \frac{V_{Ref}}{2^n}b_0,$$

(2.1)

which is the DAC conversion of a digital input  $b_{n-1}, b_{n-2}, \dots, b_1, b_0$ .

Figure 2.2: R–2R voltage mode ladder network. Picture taken from MALOBERTI (2007)

The resistor ladder is a subject matter since long time ago. One of the first works made with this topology was a 6-bit D/A converter proposed by DOOLEY (1971). In the early 80s, ERB; WIERZBA (1983) and BAPESWARA RAO; RAO (1985), presented methods for determining the resistance output of the ladder. Through the 90s other aspects of the ladder became objects of study, like a reduced physical model of the INL error performed by BONI et al. (1994) and investigations over the impact of different process resistors on the performance of the ladder WITTMANN et al. (1995). Some more complete studies started to appear after that, like in KENNEDY (2000) where he developed a model in terms of the effective resistances at the nodes of the ladder to perform appropriate trimming, design, and test strategies.

## 2.2 The Current Division Principle

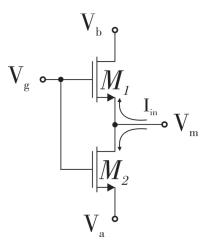

BULT; GEELEN (1992) noted that two series-connected MOS transistors, with same size and gate voltage  $(V_g)$ , equally divide the current applied on their common terminal, regardless the voltage applied on other terminals  $(V_a \text{ and } V_b)$  or the operation region. This principle is depicted on Fig. 2.3 where the current  $I_{in}$  goes through each transistor  $M_1$  and  $M_2$  with half of its value  $(M_1 = M_2)$ .

Figure 2.3: Current division principle.

For a better understanding, the similar circuit of Fig. 2.4 shows that a current  $I_{in}$  flowing into or out of the circuit will be divided into two parts, in which  $\Delta I_1$  flows into  $V_a$  and  $\Delta I_2$  flows to  $V_b$ . The ratio of the two currents is given by

$$\frac{\Delta I_1}{\Delta I_2} = -\frac{\frac{W_1}{L_1}}{\frac{W_2}{L_2}} \tag{2.2}$$

where  $\Delta I_1$  represents the increase in the current that flows through  $M_1$  and  $\Delta I_2$  the increase in the current that flows through  $M_2$ , both resulting from the applied current  $I_{in}$ . It is also clear that  $I_{in} = \Delta I_1 - \Delta I_2$ . The two transistors can be viewed as a resistive current divider using nonlinear resistors. The accuracy of current division does not depend on the linearity of the two devices  $M_1$  and  $M_2$ , but only on the matching of their V - I curves. We can use this concept in the resistor ladder network to design a MOS-only digital to analog converter.

Figure 2.4: Similar circuit showing the current division principle related to the aspect ratios.

#### 2.3 The M-2M Ladder DAC

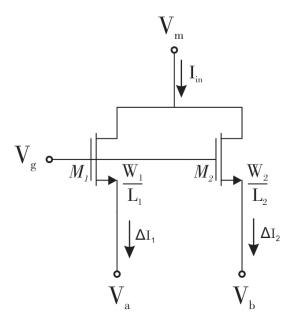

Although the structure of an R-2R ladder consisting of MOS transistors (M-2M ladder) is similar to the classical resistor-based R-2R ladder, the transistors do not have to emulate identical resistor values. The MOSFET ladder is based on the linear current division principle (previously explained) and its topology is shown in Fig. 2.5.

The resistors in Fig. 2.2 are replaced by unit NMOS transistors operating in the linear region and four unit transistors form the unit cell for 1-bit conversion. Those unit transistors driven by the digital input  $S_i$  and  $\overline{S_i}$  operate also as switches. Since the division principle works on every operating region, with devices in triode second order effects are reduced and the current mismatch due to threshold voltage mismatch can be controlled by the effective gate-source voltage. Large gate overdrive is normally avoided to reduce the nonlinearity due to mobility degradation, but this is not necessary here since the current division is independent of mobility variations. This is an interesting feature especially for

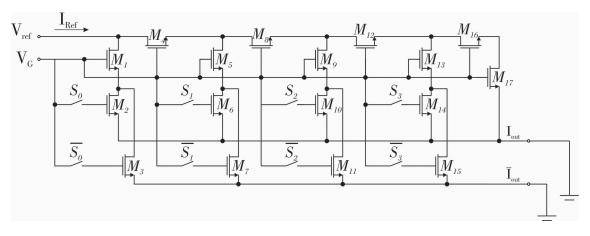

Figure 2.5: M–2M Ladder Network.

deep submicron processes, where the gate oxide becomes very thin and thus the transversal field increases and the surface scattering becomes worse.

## 2.4 **Bibliographic Review**

#### 2.4.1 R-2R ladder Review

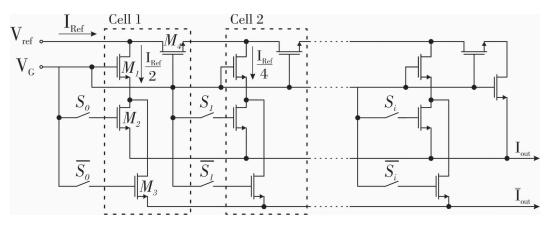

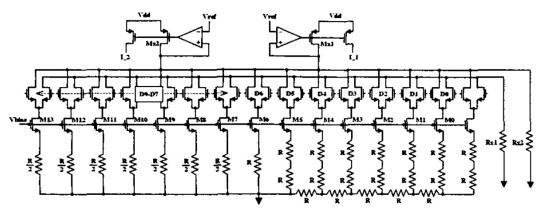

We already quoted some works about the resistor ladder but none of them says a thing about low voltage that is the main reason of this work. Then, MORTEZAPOUR; LEE (2000) explored the low voltage operation of the resistor ladder on his 1–V, 8–Bit Successive Approximation ADC. He designed the converter on a  $1.2\mu m$  CMOS process, so 1 V of supply can be considered low voltage. The circuit achieved a sampling speed of 50kS/s and the entire ADC including all the digital circuits consumes less than 0.34 mW. The DAC topology that he used is shown in Fig. 2.6 and the strategy for low voltage operation is biasing the negative input terminals of the op-amps using two current sources ( $I_2$ ) such that the op-amp input common-mode voltages can be set close to ground and the switches can have sufficient overdrive voltages.

GREENLEY et al. (2001) faced the downscaling problem designing a 1.8V, 10-bit DAC on a  $0.18\mu m$  CMOS process by mixing segmented current sources with the R-2R

ladder. The circuit is shown in Fig. 2.7 and the idea is to use the performance advantages of segmentation on the upper 3-bits, while capitalizing on the area savings of the R-2R ladder for the lower 6-bits.

Figure 2.7: DAC Schematic Showing the Segmented, Binary, and R-2R Combination. Picture taken from GREENLEY et al. (2001).

An interesting work to highlight is SEO; WEIL; FENG (2000), even not being about low voltage it's important because shows that high speed and resolutions are achievable with the resistor ladder. They built a 14-bit, 1GS/s DAC using a double segmented decoding plus the R–2R architecture.

The resistor ladder it is still subject of study nowadays. A more recent work MARCHE; SAVARIA (2010) expands the ladder modeling to segmented architectures, and a new equivalent circuit is proposed for voltage-mode designs.

#### 2.4.2 M–2M ladder Review

Now changing the focus to the M–2M ladder, HAMMERSCHMIED; HUANG (1998) used the ladder to design a 10-bit DAC for a SAR ADC, as can be seen in the block diagram of Fig. 2.8. The complete circuit was implemented in a  $1\mu m$  technology and achieved a maximum conversion rate of 200 kS/s with 9-bits of resolution. They extensively measured the ladder and got very good results showing that this topology presents better matching accuracy in comparison with circuits using capacitors or resistors arrays.

Figure 2.8: SAR ADC block diagram. Picture taken from HAMMERSCHMIED; HUANG (1998)

It was also pointed out that the ladder works better in the linear region, which helps to reduce second order effects. In terms of speed it depends on the equivalent resistance of the MOS devices and their parasitic capacitance.

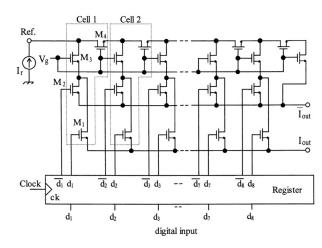

Further works, like WANG; FUKATSU; WATANABE (1998), characterized the currentmode M–2M ladder of the Fig. 2.9 showing that this topology is best suited for low-power operation. To validate their results a D/A converter with 8-bits of resolution was fabricated using a  $0.6\mu m$  CMOS process.

Figure 2.9: Circuit diagram of the 8-bit DAC. Picture taken from WANG; FUKATSU; WATANABE (1998)

In KLIMACH et al. (2008) the same converter was designed using a physical mismatch model on a 0.35  $\mu m$  CMOS technology. As can be seen in Fig. 2.10, the circuit is very similar to the one made by WANG; FUKATSU; WATANABE (1998) but the approach was different.

Figure 2.10: Simplified schematic of an 8-bit DAC. The shift register at the bottom is used for the series-to-parallel conversion of the input words. Picture taken from KLIMACH et al. (2008).

This two last circuits are the strong basis of this work, summed with the appropriate MOSFET model (UICM) it is possible to design a M–2M DAC using the mismatch approach. The ladder operates with transistors in triode condition and can also work in subthreshold, being a very promising topology for ULV operation. This possibility was already observed by KVITSCHAL et al. (2012) where they proposed a 6-bit DAC working with 0.1 V in 130 nm CMOS process.

Another very interesting application for the M-2M ladder was exposed by LEE; LIN (2010) exploring a nonlinear topology. They added transistors on the conventional M-2M ladder in order to obtain nonlinear characteristics of the output current. One of the applications of nonlinear DACs is for gamma correction in the driving systems of displays.

#### 2.4.3 Very Low Voltage Converters Review

Until now we made an extensive review of the R-2R and M-2M ladders, but it is also interesting to review what happened to the converters when dealing with very low voltage supplies. From the Fig. 1.10 we can highlight the decrease of the supply voltage through the years showing that designers are always trying to achieve the lowest supply voltages on each technology node.

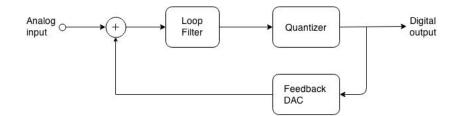

Lets first point out to the design made by MATSUYA; YAMADA (1994) where the main goal was to design a battery operated converter that has to work with low supply voltages. Until that time the lowest supply was 2.5 V (KUSUMOTO; MATSUZAWA; MURATA (1993)) which wasn't enough for battery operated circuits. To met the low voltage specification they implemented a 10-bits noise shaping ADC that works with 1 V of supply on a  $0.5\mu m$  CMOS process. To accomplish this they used an RC integrator composed by an integrator, a quantizer and a feedback DAC, as shown on the block diagram of Fig. 2.11, in order to solve issues presented by switching capacitors working with low voltage supplies.

Figure 2.11: Block diagram of a basic noise-shaping A/D converter.

Following this line, PELUSO et al. (1998) reinforced the difficulties of using switching capacitors for low voltage operation and used a switched Op-Amp technique to design a 900mV Low Power  $\Sigma$ - $\Delta$  ADC with 10-bits of resolution on a 0.5 $\mu$ m CMOS process. They also chose this method to avoid the use of expensive multithreshold processes.

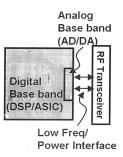

The downscaling of CMOS devices brings up new design possibilities, as well new difficulties. On a  $0.13\mu m$  CMOS process, LIN; HAROUN (2002) designed a 0.8 V/22 MHz Flash ADC with 5-bits of resolution using a nonlinear double interpolation technique. At that time, high data rate converters became an interesting option by integrating a receive converter with digital baseband signal processing circuits (rather than an RF transceiver), as shown in Fig. 2.12. This architecture brings a design challenge because when converters are integrated on the digital baseband chip they need to be protected from the large digital noise.

Figure 2.12: Typical baseband and RF transceiver configuration in wireless devices back in 2002, e.g., WCDMA, WLAN. Picture taken from LIN; HAROUN (2002).

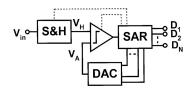

SAUERBREY et al. (2003) designed a Successive Approximation (SAR) ADC with 0.5 V and 8-bits of resolution on a  $0.18 \mu m$  CMOS process. In this work they pointed out that switched opamp circuits, reset-opamp circuits and circuits using bootstrapping techniques are suited for low  $V_{DD}$  but presented another approach where only reference voltages are switched. The SAR architecture shown on Fig. 2.13 is opamp-free with a passive sample-and-hold (S & H) stage and a capacitor based DAC.

Figure 2.13: Successive approximation converter architecture. Picture taken from SAUERBREY et al. (2003).

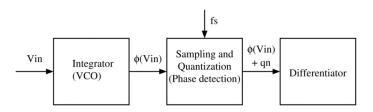

The last state-of-art design that JONSSON (2010) mentioned was a Frequency-todigital  $\Sigma\Delta$  modulator (FDSM) made by WISMAR et al. (2006). They use an inverterring voltage controlled oscillator (RVCO) as the integrator. The block diagram is shown in Fig. 2.14 and works with 0.2 V in a 90nm CMOS process.

Figure 2.14: FDSM block diagram. Picture taken from WISMAR et al. (2006).

Two other works that fit in here were already quoted in section 1.3 (DALY; CHAN-DRAKASAN (2009) and LIN; HSIEH (2015)) to support the importance of ultra low voltage converters. To reinforce, we will quote now two recent works made by Chandrakasan and his colleagues that are state-of-art ADCs. In LEE; CHANDRAKASAN; LEE (2012), they developed a 12-bits 5 to 50 MS/s on the range of 0.5 to 1 V, voltage scalable zero-crossing based pipelined ADC. The circuit was manufactured on a 65 nm CMOS process and enables energy efficient operation. It uses switched-capacitor multiplying DACs (MDACs). The other work, YIP; CHANDRAKASAN (2013), is a resolution-reconfigurable, 5 to 10 bits, 0.4 V to 1 V, Power Scalable SAR ADC for sensor applications. This ADC features a reconfigurable 5 to 10 bits DAC whose power scales exponentially with resolution. The ADC operates up to 2 MS/s at 1 V and 5 kS/s at 0.4 V. Prototyped in a low power 65 nm CMOS process, the ADC in 10-bit mode achieves an INL and DNL of 0.57 LSB and 0.58 LSB respectively at 0.6 V, and the Nyquist SNDR and SFDR are 55 dB and 69 dB respectively at 0.55 V and 20 kS/s. From the two common DAC approaches, resistive DACs (RDACs) and capacitive DACs (CDACs), they chose the CDAC approach because it is more amenable to voltage scaling

## 3 LOW VOLTAGE ALL-MOSFET DAC

From the previous chapters we get the main ideas in order to design a Digital-to-Analog Converter that works with very low supply voltage. We want low voltage operation because it is ubiquitous among every circuits nowadays and the M–2M ladder topology proved to be suited for this specification. Through this chapter we perform a circuit description showing the schematic and explaining the operation regime. The design methodology based on the UICM Mismatch model and operation principles are shown in sequence. We also point out that some linearity issues, that might become a problem, are actually easy solvable problems.

#### 3.1 The All-Regions UICM MOSFET Model and Mismatch Model

The Unified Current Control Model (UICM) SCHNEIDER; GALUP-MONTORO (2010), is a physics-based all-region MOSFET model that uses the "inversion level" concept, and it provides the modeling foundation for the analytical formulation used by KLIMACH et al. (2008). This model represents the drain current of a transistor as the difference between a forward  $(I_F)$  and a reverse  $(I_R)$  component

$$I_D = I_F - I_R = I_{SQ} \frac{W}{L} (i_f - i_r)$$

(3.1)

where  $I_{SQ} = \frac{1}{2}\mu C'_{ox}n\phi_t^2$  is the sheet normalization current, (W/L) the aspect ratio, n is the slope factor,  $\mu$  is the low field mobility,  $C'_{ox}$  the oxide capacitance per unit of area and  $\phi_t$  is the thermal voltage. Parameters  $i_f$  and  $i_r$  are the normalized forward and reverse currents, or "inversion levels", at source and drain, respectively.

The "ideal" slope factor (n) is equal to one. The bulk MOS transistor, however, is characterized by a slope factor a few percent to tens of percent higher than one. The deviation from ideal slope factor in bulk transistors happens because the change in gate voltage is not only accompanied by a change in the inversion charge but also by a change in the bulk charge SCHNEIDER; GALUP-MONTORO (2010).

The forward and reverse inversion levels are also related to the terminal voltages as follows

$$V_G - V_T - nV_{S(D)} = n\phi_t \left[ ln \left( \sqrt{1 + i_{f(r)}} - 1 \right) + \sqrt{1 + i_{f(r)}} - 2 \right]$$

(3.2)

where  $V_G$ ,  $V_S$  and  $V_D$  are the gate, source and drain voltages referred to bulk, respectively, and  $V_T$  is the threshold voltage.

The MOSFET mismatch model based on the UICM model, used as basis of KLI-MACH et al. (2008) work, was previously proposed by GALUP-MONTORO et al. (2005),

being more appropriate to the DAC variability analysis than the traditional Pelgrom's mismatch model, that does not consider the subthreshold nonlinear nature of MOSFETs in a proper way. In appendix B there's a comparison between the two models, explaining a little better their differences.

The following equation presents the dependency of current mismatch with transistor area, inversion levels and technology parameters

$$\frac{\sigma_{I_D}^2}{I_D^2} = \frac{1}{WL} \left[ \frac{N_{oi}}{N^{*2}} \frac{1}{i_f - i_r} \ln\left(\frac{1 + i_f}{1 + i_r}\right) + B_{I_{SQ}}^2 \right]$$

(3.3)

where  $N^* = nC'_{ox}\phi_t/q$  is the carrier density at pinch-off condition,  $N_{oi}$  is the main mismatch model parameter, related to the number of impurity atoms inside the depletion volume under the channel area, and  $B_{I_{SQ}}$  is a less significant model parameter that accounts for variations in the specific normalization current  $I_{SQ}$ .

## **3.2** The Binary Weighting Principle

For a long-channel MOSFET under any bias condition, the drain current is directly proportional to the channel width (W), and inversely proportional to its length (L). Based on this statement, one can show that any series-parallel association of identical transistors (Fig. 3.1) works similarly to one device with equivalent aspect ratio (W/L) KLIMACH et al. (2008). Assume  $M = M_a = M_b = M_c = M_d$  in Fig. 3.1.

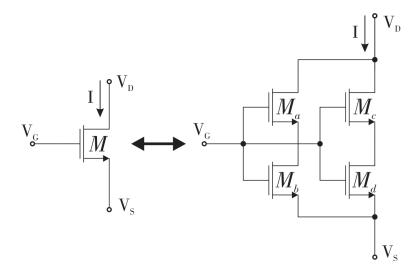

Figure 3.1: MOSFET association principle: one transistor can be substituted by a seriesparallel association of identically designed transistors.

Using this association principle, transistor  $M_d$  in Fig. 3.1 can also be substituted by a series-parallel association of identical transistors,  $M_{da}$ ,  $M_{db}$ ,  $M_{dc}$  and  $M_{dd}$ , resulting the circuit in Fig. 3.2. Since the main branches in Fig. 3.2 are equivalent, the applied current I is equally divided between them. The same current division principle can be used in secondary branches. One can see that it is rather simple to establish a binary division of currents that flow through different branches of a series-parallel association of MOSFETs.

Transistor  $M_{dd}$  of 3.2 can also be substituted by another set of four transistors in seriesparallel association, resulting in another binary division of the current. This procedure can be repeated successively, resulting in the network traditionally called the "M–2M ladder".

Figure 3.2:  $M_d$  in Fig. 3.1 can be substituted by a series-parallel equivalent association.

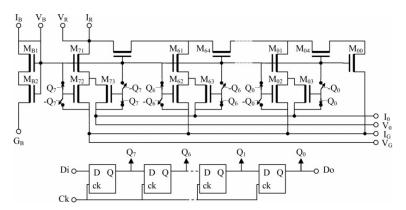

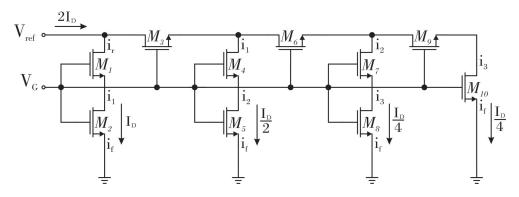

### **3.3 DAC Circuit Description**

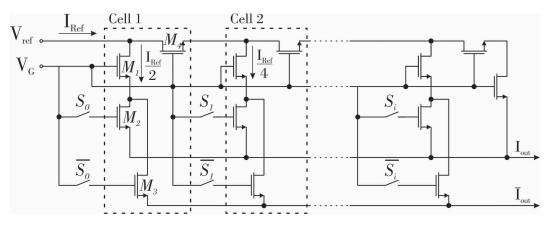

The ladder network shown in Fig. 3.3 is formed by a sequence of M–2M cells, one per bit, and finalized by a 2M termination. In general this ladder is formed by cells with transistors having the same geometry, simplifying the layout. Each cell divides its input current by half, performing the DAC weighting through successive binary divisions of the reference current  $I_{Ref}$  generated by  $V_{Ref}$ . The two drain connected transistors  $M_2$  and  $M_3$  deviates the binary fraction of the current to  $I_{out}$  or  $\overline{I}_{out}$  node, depending on the  $S_i$  switch state, since these nodes are tied to ground through a very low impedance connection, resulting for any binary combination that

$$I_{Ref} = I_{out} + I_{out} \tag{3.4}$$

The switches are implemented with transmission gates driven by a digital register that stores the input binary data. At this work we do not explore the register design since our main focus is the ladder variability analysis, that's why the register operates at nominal supply (1.2V). Digital circuits like logical gates and registers operating with very low supply voltages have already been studied in recent works MELEK et al. (2014).

Figure 3.3: M–2M CMOS Ladder Network.

Finally, the current summing that results in  $I_{out}$  node represents a binary proportion of  $I_{Ref}$ , controlled by the input digital data. The four identical MOSFETs on each cell results a very regular and compact layout that improves matching.

#### 3.3.1 Intrinsic Nonlinearity Considerations

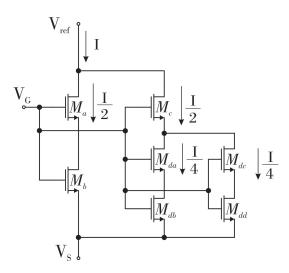

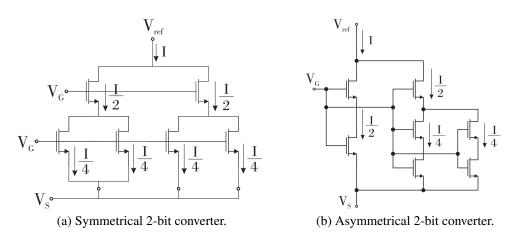

The MOSFET DAC ladder topology can be symmetric or asymmetric, both exemplified in Fig. 3.4. Because the reduced number of transistors the asymmetric topology is most commonly used. However, this circuit presents an intrinsic nonlinearity that even not being the focus of this works it's important to make a few comments. As usual in the design of M-2M ladders, all transistors were designed with same size.

Figure 3.4: Different implementations of a M-2M ladder.

As a proof of concept we simulated on Cadence-Virtuoso tool the 4-bit asymmetric ladder showed in Fig. 3.5 with  $V_G = V_{Ref} = 200mV$  and transistors size according to table 3.1. We kept the channel length equal for simplicity and since this is just a proof of concept we choose the sizes by trial and error. In this case we are not worried about the current magnitude, but we must assure that the current value on main branch ( $M_1$  and  $M_2$ ) is lower than on the other branches. This way the nonlinearity error, which is bigger on the main branch, will have less impact.

Figure 3.5: 4-bits M–2M ladder for nonlinearity analysis.

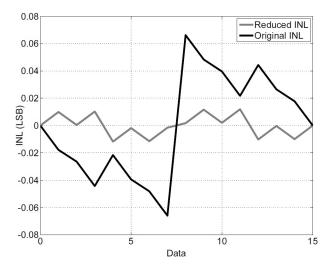

The Integral Nonlinearity (INL) was calculated in terms of the least significant bit (LSB). At first, all transistors have the same size and the INL appear by the name "Original INL" in Fig. 3.6, as can be seen, the higher nonlinearity appears at half scale. Then we applied one technique to reduce the nonlinearity by gradually decreasing the transistors size from the LSB to the most significant bit (MSB). The result is shown in the same

| Transistors                                      | Original Width | Reduced Width |

|--------------------------------------------------|----------------|---------------|

| $M_1, M_2, M_3$                                  | $4\mu m$       | $3.85 \mu m$  |

| $M_4, M_5, M_6, M_7$                             | $4\mu m$       | $3.9 \mu m$   |

| $M_8, M_9, M_{10}, M_{11}$                       | $4\mu m$       | $3.95 \mu m$  |

| $M_{12}, M_{13}, M_{14}, M_{15}, M_{16}, M_{17}$ | $4\mu m$       | $4\mu m$      |

Table 3.1: Transistors width (W). The channel length is the same for all  $L = 2\mu m$ .

figure by the name of "Reduced INL". Another option to reduce the nonlinearity is using the symmetrical ladder topology, that is perfectly linear.

Figure 3.6: INL comparison between an asymmetric ladder with same sized transistors and with INL reduction technique.

The reader must note that this simulation was performed only with typical transistors and this error is not related to any variability issue, being it an intrinsic nonlinearity related to the asymmetrical MOSFET DAC topology. Also, a predistortion can be applied to the input data to correct this nonlinearity, since it is a predictive behavior. To summarize, there are options to mitigate the intrinsic nonlinear behavior of the asymmetric ladder used in this work. This issues will appear on development of this thesis and will be pointed out, but we want to make it clear that our focus is only the variability analysis caused by mismatch of MOSFETs.

## 3.4 Circuit Design Methodology

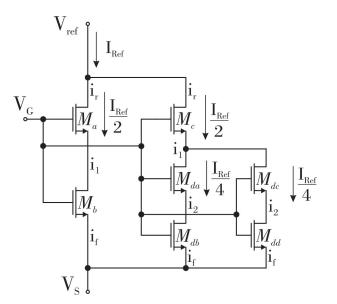

The analysis of the resulting inversion levels of transistor terminals that are connected to the ladder nodes can be done using a simplified version with only 2 bits of resolution, as shown in Fig. 3.7, where  $i_f$  and  $i_r$  are the inversion level of transistors source and drain terminals, respectively. Note that all transistors have same gate biasing, and since the lower transistors of the ladder have also same source biasing, they present same  $i_f$  level. Since the current in series transistors  $M_a$  and  $M_b$  is the same, having both same geometry, from eq. (3.1) one can state the following relationship for the intermediate inversion level  $i_1$

$$i_1 = \frac{i_f + i_r}{2} \tag{3.5}$$

Figure 3.7: Simplified 2-bit DAC and current division process.

Also, since the input current  $I_{Ref}$  is divided in two equal portions by equally sized transistors ( $M_a$  and  $M_c$ ), the inversion level on source terminal of these transistors must be the same ( $i_1$ ). This analysis can be done in the next cell (formed by  $M_{da}$ ,  $M_{db}$ ,  $M_{dc}$  and  $M_{dd}$ ), resulting that the inversion level of the intermediate node ( $i_2$ ) is given by

$$i_2 = \frac{i_f + i_1}{2} \tag{3.6}$$

Expanding this analysis one can determine the intermediate inversion level  $(i_i)$  for any branch *i* of the ladder from  $i_f$  (determined by  $V_G$ ) and  $i_r$  (determined by  $V_{Ref}$ ) using the following expression

$$i_i = \frac{i_r + (2^i - 1)i_f}{2^i} \tag{3.7}$$

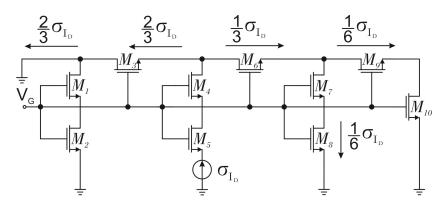

From this point a variability analysis can be performed over the ladder using a smallsignal model, since the drain current mismatch in the branches can be considered small. Using eq. (3.3) and the forward and reverse inversion levels of the lower transistors of the ladder ( $M_2$ ,  $M_5$  and  $M_8$  in Fig. 3.8), one can estimate the mismatch statistical contribution of these transistors in the current flowing in each branch (in Fig. 3.8 the drain current mismatch contribution of  $M_5$  is indicated as  $\sigma_{I_D}$ ).

Figure 3.8: Small-signal model for mismatch analysis.

After that, the mismatch contribution of each branch can be propagated to the other branches following the relationship given by Eq. 2.2, using the small-signal approximation and considering the current division property of the MOS transistors BULT; GEE-LEN (1992). Finally, the contributions from the mismatch of all lower transistors can be combined in each branch to keep the total current equal to the reference current, resulting an approximation of the drain current error, which can be used to estimate the DAC variability.

For example, in Fig. 3.8 the  $M_5$  mismatch error  $\sigma_{I_D}$  propagates through  $M_3$  and  $M_6$ , according to the current division properties of both branches, the equivalent aspect ratio of transistors  $M_6$ ,  $M_7$ ,  $M_8$ ,  $M_9$ ,  $M_{10}$  is  $\frac{W}{2L}$  and  $M_1$ ,  $M_2$ ,  $M_3$  is  $\frac{W}{L}$ . Again, from equation 2.2, the contribution that flows through  $M_6$  is  $\sigma_{I_D}/3$ , through  $M_3$  is  $\frac{2}{3}\sigma_{I_D}$  and through  $M_8$  is  $\sigma_{I_D}/6$ .

Now we will exemplify the design methodology considering a 130 nm standard process and applying it to a 3-bit DAC explaining in detail every step. We are using the IBM 130 nm process technology because its a very reliable process, also because we have access to it through the university. Another good reasons to use it is the variety of transistors and devices that can be found. From the circuit in Fig. 3.9, we assume  $V_G = V_{ref} = 200mV$  and  $\frac{W}{L} = \frac{25\mu m}{10\mu m}$ . From Eq. 3.2, with n = 1.35 (that is a common value when using MOSFETs with less than 500mV of biasing SCHNEIDER; GALUP-MONTORO (2010)),  $\phi_t = 26mV$  and  $V_T = 200mV$ , we can calculate  $i_f$  of transistors  $M_2$ ,  $M_5$ ,  $M_8$  and  $M_{10}$ , which value is 4.8. From the same equation,  $i_r$  of transistor  $M_1$ is 0.002. Using Eq. 3.7 and the corresponding values of  $i_f$  and  $i_r$  it is possible to calculate the intermediate inversion levels  $i_1$ ,  $i_2$  and  $i_3$ , which values are 2.4, 3.6 and 4.3 respectively.

Figure 3.9: 3 bits DAC topology. This circuit

Now that we have all inversion levels, from Eq. 3.1, using  $I_{SQ} = 243.7nA$ , one can calculate the currents on each branch. The currents flowing through  $M_2$ ,  $M_5$ ,  $M_8$  and  $M_{10}$  are  $1.48\mu A$ , 744nA, 372nA and 372nA respectively.

The next step is to calculate the current mismatch on each transistor given by Eq. 3.3. Mismatch parameter  $B_{I_{SQ}}$  has the same meaning of parameter  $K_{\beta}$  that can be obtained from the process PDK (3% –  $\mu m$  for the IBM 130 nm process). Since parameter  $N_{oi}$  is related to a new MOSFET mismatch model it is not usually estimated by foundries and should be measured from fabricated test mismatch structures as shown in KLIMACH; GALUP-MONTORO; ARNAUD (2005). An easier way to estimate  $N_{oi}$  is from the following approximate equation that establishes the relation between this parameter and the Pelgrom's mismatch  $A_{V_T}$  model parameter, that is related to the threshold voltage mismatch (KLIMACH (2008)), resulting  $N_{oi} = 7 \cdot 10^{13} cm^{-2}$  for this process.

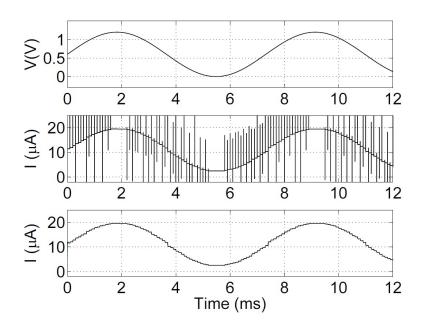

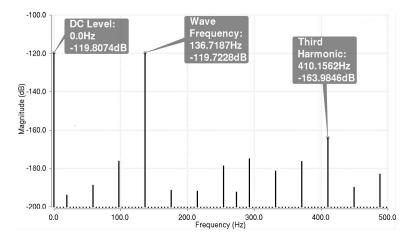

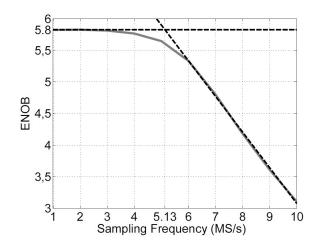

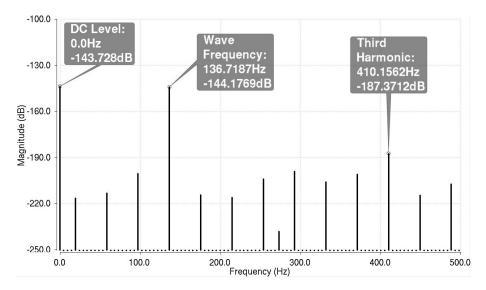

$$\sqrt{N_{oi}} = \frac{C'_{ox}A_{V_T}}{q} \tag{3.8}$$