# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

FELIPE ROCHA DA ROSA

# Early Evaluation of Multicore Systems Soft Error Reliability Using Virtual Platforms

Thesis presented in partial fulfillment of the requirements for the degree of Doctor of Microeletronics

Advisor: Prof. Dr. Ricardo A. da Luz Reis Coadvisor: Dr. Luciano Ost

Porto Alegre June 2018 Rocha da Rosa, Felipe

Early Evaluation of Multicore Systems Soft Error Reliability Using Virtual Platforms / Felipe Rocha da Rosa. – Porto Alegre: PGMICRO da UFRGS, 2018.

166 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2018. Advisor: Ricardo A. da Luz Reis; Coadvisor: Luciano Ost.

1. Multi/Manycore Systems. 2. Fault Tolerance. 3. Reliability. 4. Virtual Platforms. 5. Simulation. 6. ARM. 7. Soft Errors. 8. Machine Learning. I. Reis, Ricardo A. da Luz. II. Ost, Luciano. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PGMICRO: Prof. Fernanda Gusmão de Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro "Scientists investigate that which already is; Engineers create that which has never been." — DR. ALBERT EINSTEIN

"Scientists dream about doing great things. Engineers do them." — JAMES A. MICHENER

# ABSTRACT

The increasing computing capacity of multicore components like processors and graphics processing unit (GPUs) offer new opportunities for embedded and high-performance computing (HPC) domains. The progressively growing computing capacity of multicore-based systems enables to efficiently perform complex application workloads at a lower power consumption compared to traditional single-core solutions. Such efficiency and the ever-increasing complexity of application workloads encourage industry to integrate more and more computing components into the same system. The number of computing components employed in large-scale HPC systems already exceeds a million cores, while 1000-cores on-chip platforms are available in the embedded community.

Beyond the massive number of cores, the increasing computing capacity, as well as the number of internal memory cells (e.g., registers, internal memory) inherent to emerging processor architectures, is making large-scale systems more vulnerable to both hard and soft errors. Moreover, to meet emerging performance and power requirements, the underlying processors usually run in aggressive clock frequencies and multiple voltage domains, increasing their susceptibility to soft errors, such as the ones caused by radiation effects. The occurrence of soft errors or Single Event Effects (SEEs) may cause critical failures in system behavior, which may lead to financial or human life losses. While a rate of 280 soft errors per day has been observed during the flight of a spacecraft, electronic computing systems working at ground level are expected to experience at least one soft error per day in near future. The increased susceptibility of multicore systems to SEEs necessarily calls for novel cost-effective tools to assess the soft error resilience of underlying multicore components with complex software stacks (operating system-OS, drivers) early in the design phase.

The primary goal addressed by this Thesis is to describe the proposal and development of a fault injection framework using state-of-the-art virtual platforms, propose set of novel fault injection techniques to direct the fault campaigns according to with the software stack characteristics, and an extensive framework validation with over a million of simulation hours. The second goal of this Thesis is to set the foundations for a new discipline in soft error reliability management for emerging multi/manycore systems using machine learning techniques. It will identify and propose techniques that can be used to provide different levels of reliability on the application workload and criticality. **Keywords:** Multi/Manycore Systems. Fault Tolerance. Reliability. Virtual Platforms. Simulation. ARM. Soft Errors. Machine Learning.

# Avaliação de sistema de larga escala sob à influência de falhas temporárias durante a exploração de inicial projetos através do uso de plataformas virtuais.

### RESUMO

A crescente capacidade de computação dos componentes multiprocessados como processadores e unidades de processamento gráfico oferecem novas oportunidades para os campos de pesquisa relacionados computação embarcada e de alto desempenho (do inglês, high-performance computing). A crescente capacidade de computação progressivamente dos sistemas baseados em multicores permite executar eficientemente aplicações complexas com menor consumo de energia em comparação com soluções tradicionais de núcleo único. Essa eficiência e a crescente complexidade das cargas de trabalho das aplicações incentivam a indústria a integrar mais e mais componentes de processamento no mesmo sistema. O número de componentes de processamento empregados em sistemas grande escala já ultrapassa um milhão de núcleos, enquanto as plataformas embarcadas de 1000 núcleos estão disponíveis comercialmente.

Além do enorme número de núcleos, a crescente capacidade de processamento, bem como o número de elementos de memória interna (por exemplo, registradores, memória RAM) inerentes às arquiteturas de processadores emergentes, está tornando os sistemas em grande escala mais vulneráveis a erros transientes e permanentes. Além disso, para atender aos novos requisitos de desempenho e energia, os processadores geralmente executam com frequências de relógio agressivos e múltiplos domínios de tensão, aumentando sua susceptibilidade à erros transientes, como os causados por efeitos de radiação. A ocorrência de erros transientes pode causar falhas críticas no comportamento do sistema, o que pode acarretar em perdas de vidas financeiras ou humanas. Embora tenha sido observada uma taxa de 280 erros transientes por dia durante o voo de uma nave espacial, os sistemas de processamento que trabalham à nível do solo devem experimentar pelo menos um erro transiente por dia em um futuro próximo. A susceptibilidade crescente de sistemas multicore à erros transientes necessariamente exige novas ferramentas para avaliar a resiliência à erro transientes de componentes multiprocessados em conjunto com pilhas complexas de software (sistema operacional, drivers) durante o início da fase de projeto.

O objetivo principal abordado por esta Tese é desenvolver um conjunto de técnicas de injeção de falhas, que formam uma ferramenta de injeção de falha. O segundo objetivo desta Tese é estabelecer as bases para novas disciplinas de gerenciamento de confiabi-

lidade considerando erro transientes em sistemas emergentes multi/manycore utilizando aprendizado de máquina. Este trabalho identifica multiplicas técnicas que podem ser usadas para fornecer diferentes níveis de confiabilidade na carga de trabalho e na criticidade do aplicativo.

**Palavras-chave:** Sistemas Multi/Manycore, Tolerância a Falhas, Confiabilidade, Plataformas Virtuais, Simulação, ARM, Falhas Transientes, Aprendizado de Máquina .

# LIST OF ABBREVIATIONS AND ACRONYMS

- ASIC Application-specific Integrated Circuit

- ABNT Associação Brasileira de Normas Técnicas

- COTS Commercial Off-the-shelf

- DSE Design Space Exploration

- DSE Design Space Exploration

- DBT Dynamic Binary Translation

- DRAM Dynamic Random-Access Memory

- DVFS Dynamic Voltage and Frequency Scaling

- FIM Fault Injection Module

- GPU Graphics Processing Unit

- HPC High Performance Computing

- ISA Instruction Set Architecture

- JIT Just-in-time

- MPI Message Passing Interface

- MIPS Million Instructions per Second

- MBU Multiple Bit Upset

- MET Multiple Event Transient

- nm Nanometer

- OVP Open Virtual Platforms

- **OVPsim Open Virtual Platforms Simulator**

- OS Operating System

- PE Processing Units

- SDC Silent Data Corruption

- SMT Simultaneous Multithreading

- SEU Single Event Upset

- SER Soft Error Rate

- SMP Symmetric Multi-Processor

- KIPS Thousand Instructions per Second

- TMR Triple Modular Redundancy

- VA Virtual Address

- VP Virtual Platform

- VP-FIM Virtual Platform Fault Injection Module

# LIST OF FIGURES

| <ul> <li>Figure 1.1 Evolution of commercial processors during the last decades considering the number of transistors (top), number of cores (middle), and associeted technology node (botton) from 1970 to 2018. Information gathered from multiple sources including the ITRS (https://www.itrsgroup.com/).</li> <li>Figure 1.2 Diagram with the design space exploration flow and this thesis contributions.</li> </ul> |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.1 Charge generation and collection phases in a reverse-biased junction<br>and the resultant current pulse caused by the passage of a high-energy ion                                                                                                                                                                                                                                                             |     |

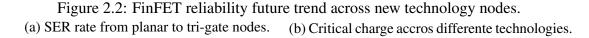

| Figure 2.2 FinFET reliability future trend across new technology nodes                                                                                                                                                                                                                                                                                                                                                    |     |

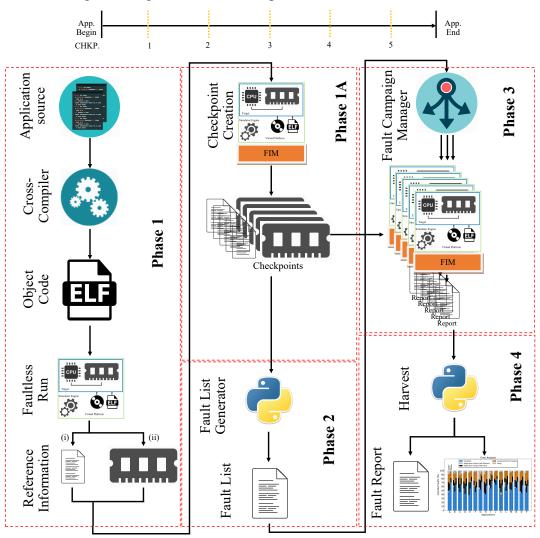

| Figure 3.1 Fault injection campaign simulation flow                                                                                                                                                                                                                                                                                                                                                                       | 42  |

| Figure 3.2 OVPsim-FIM main components.                                                                                                                                                                                                                                                                                                                                                                                    | 44  |

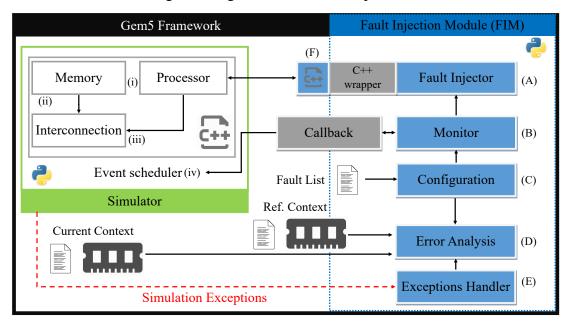

| Figure 3.3 gem5-FIM main components                                                                                                                                                                                                                                                                                                                                                                                       | 46  |

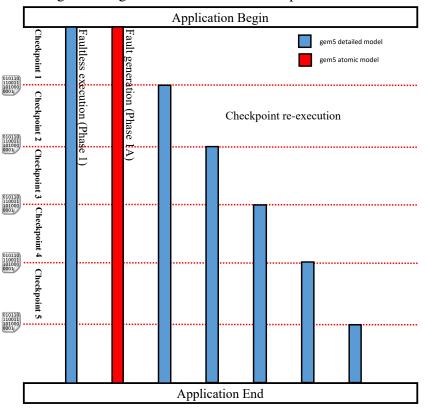

| Figure 3.4 gem5 atomic checkpoint modified simulation flow.                                                                                                                                                                                                                                                                                                                                                               | 50  |

| Figure 3.5 gem5 detailed mode checkpoint scheme.                                                                                                                                                                                                                                                                                                                                                                          | 51  |

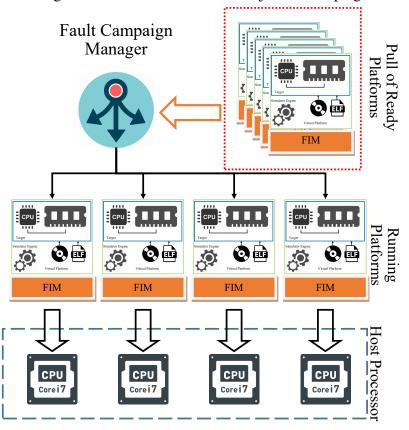

| Figure 3.6 Host multicore fault injection campaign                                                                                                                                                                                                                                                                                                                                                                        | 52  |

| Figure 3.7 Distributed fault injection campaign flow                                                                                                                                                                                                                                                                                                                                                                      | 53  |

| Figure 3.8 OVPsim-FIM fault injection techniques according to with fault location and injection time.                                                                                                                                                                                                                                                                                                                     |     |

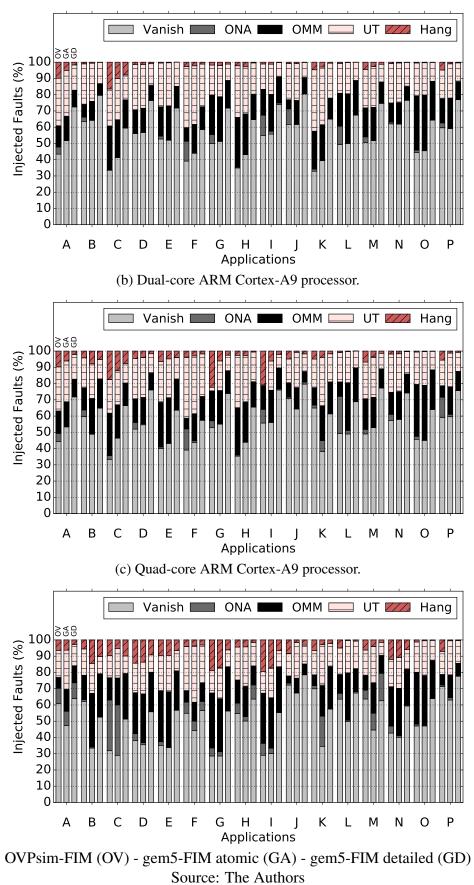

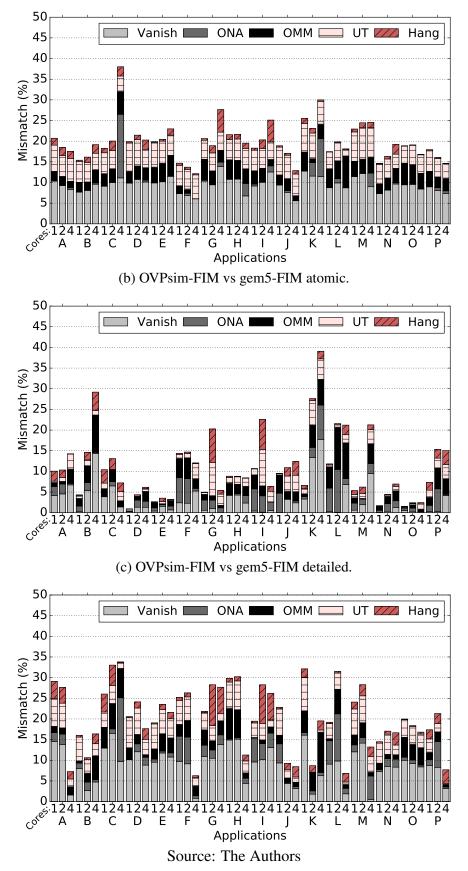

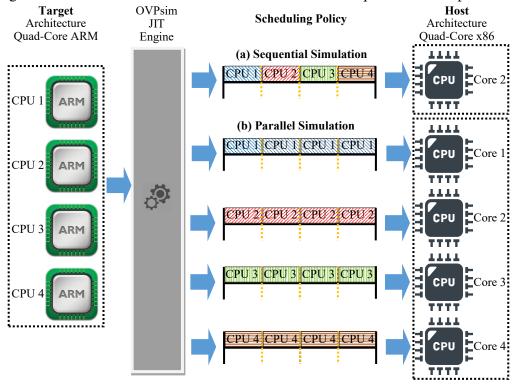

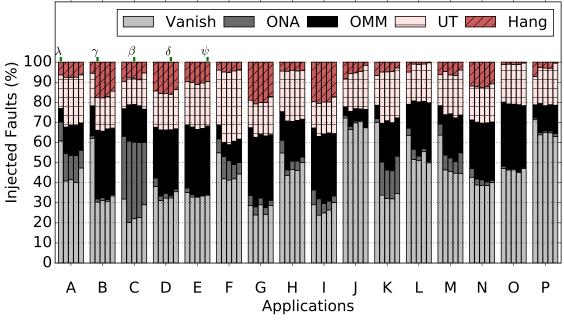

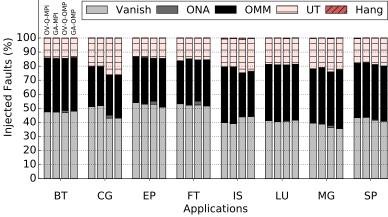

| Figure 4.1 Rodinia benchmarks 8000-fault injection campaign for a multicore ARM<br>Cortex-A9 processor.                                                                                                                                                                                                                                                                                                                   | 60  |

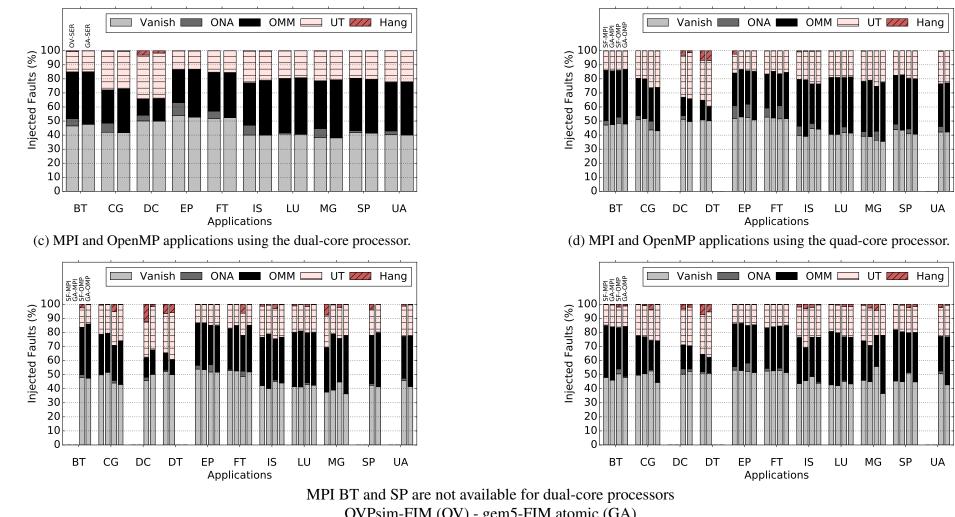

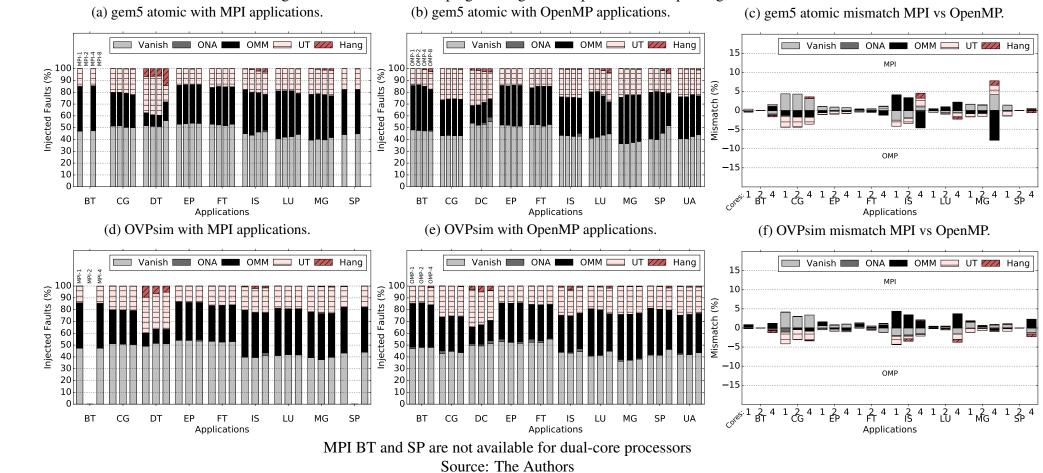

| Figure 4.2 NPB applications 8000-fault injection campaign for a multicore ARM                                                                                                                                                                                                                                                                                                                                             |     |

| Cortex-A9 processor.                                                                                                                                                                                                                                                                                                                                                                                                      | 70  |

| Figure 4.3 Rodinia benchmarks ACM considering a multicore ARM Cortex-A9.                                                                                                                                                                                                                                                                                                                                                  |     |

| Figure 4.4 NPB applications ACM between the OVPsim-FIM and gem5-FIM atomic considering a multicore ARM Cortex-A9.                                                                                                                                                                                                                                                                                                         |     |

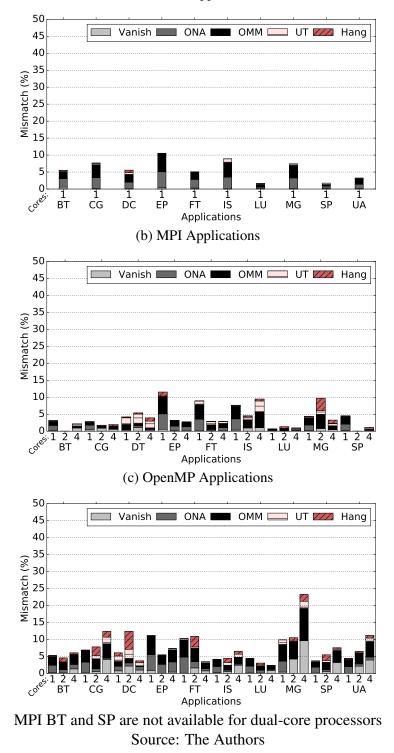

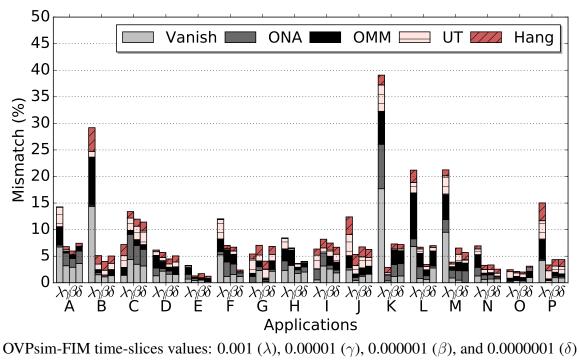

| Figure 4.5 OVPsim scheduling policy varying the quantum size for a dual-core processor executing the same workload.                                                                                                                                                                                                                                                                                                       |     |

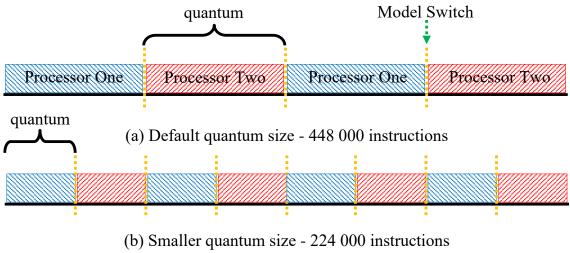

| Figure 4.6 OVPsim simulation workload division into a quad-core host processor                                                                                                                                                                                                                                                                                                                                            |     |

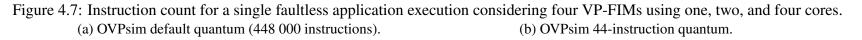

| Figure 4.7 Instruction count for a single faultless application execution considering four VP-FIMs using one, two, and four cores.                                                                                                                                                                                                                                                                                        | 81  |

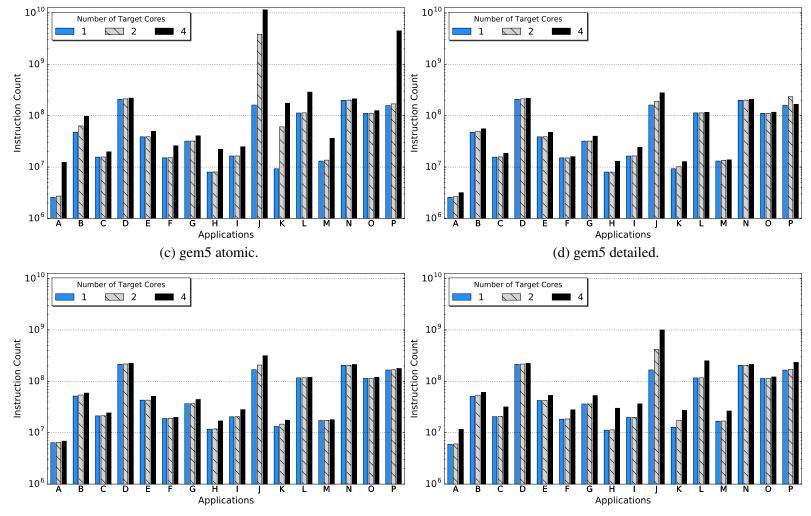

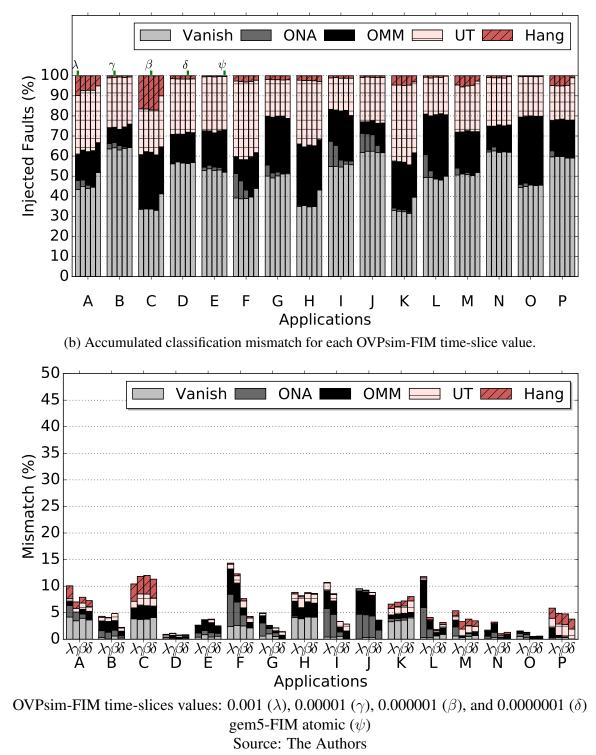

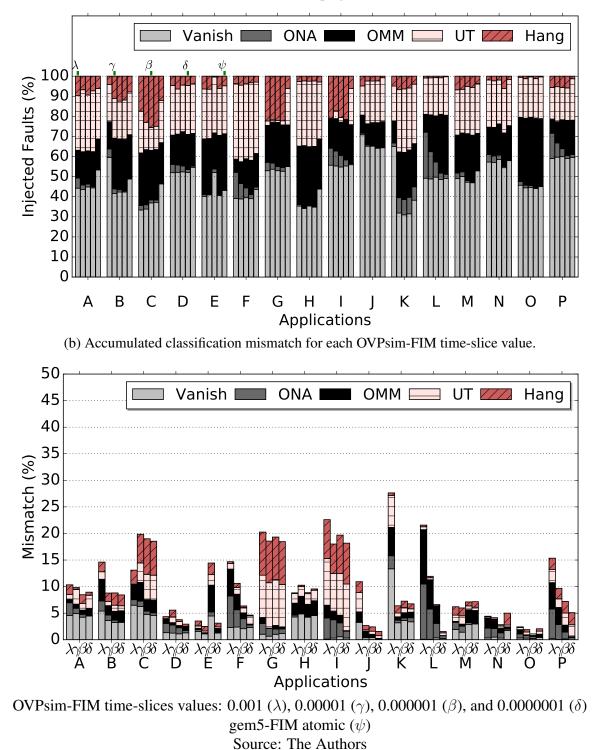

| Figure 4.8 8000-fault injection campaign deploying the OVPsim-FIM for a single-<br>core ARM Cortex-A9 processor varying the time-slice and the reference gem5-<br>FIM atomic.                                                                                                                                                                                                                                             | 82  |

| Figure 4.9 8000-fault injection campaign deploying the OVPsim-FIM for a dual-<br>core ARM Cortex-A9 processor varying the time-slice and the reference gem5-                                                                                                                                                                                                                                                              |     |

| FIM atomic.                                                                                                                                                                                                                                                                                                                                                                                                               | 83  |

| Figure 4.10 8000-fault injection campaign deploying the OVPsim-FIM for a quad-<br>core ARM Cortex-A9 processor varying the time-slice and the reference gem5-                                                                                                                                                                                                                                                             | 0.4 |

| FIM atomic.                                                                                                                                                                                                                                                                                                                                                                                                               | 84  |

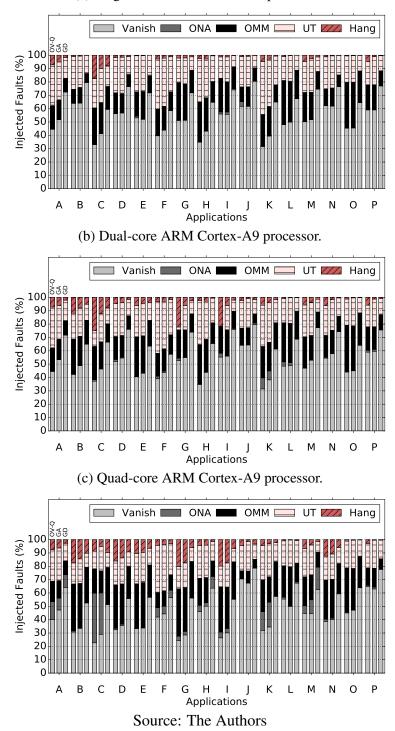

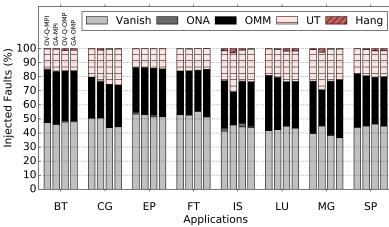

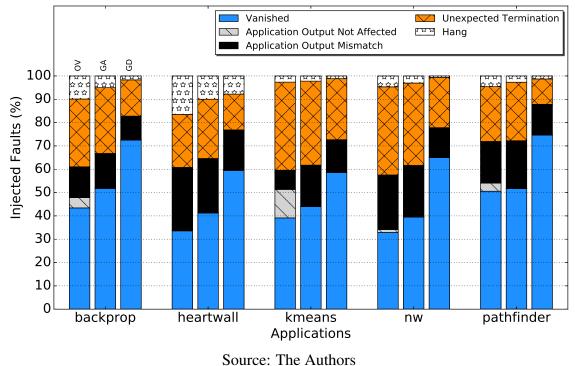

| Figure 4.11 Rodinia benchmarks the OVPsim-FIM with reduced quantum (OV-Q),<br>the gem5-FIM atomic (GA), the and gem5-FIM detailed (GD) for a multicore                                                                                                                                                                                                                                                                    | 07  |

| ARM Cortex-A9 processor.                                                                                                                                                                                                                                                                                                                                                                                                  | ð/  |

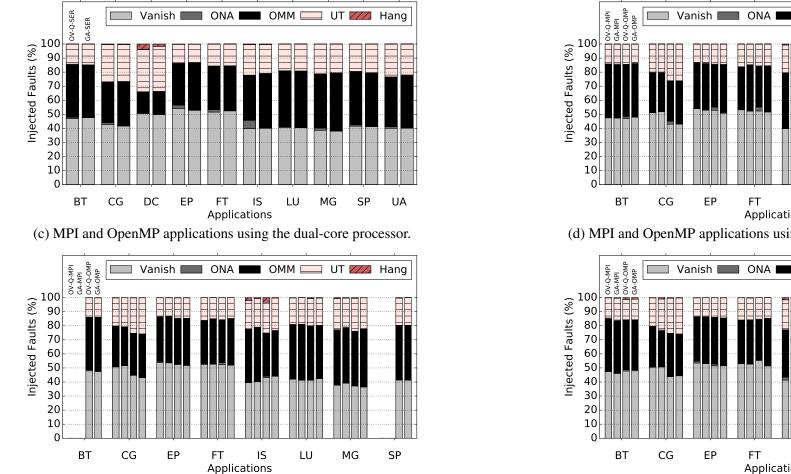

| Figure 4.12 NPB applications using the OVPsim with smaller quantum (OV-Q) and gem5-FIM atomic (GA) for a multicore ARM Cortex-A9 processor                                                                                                                                                                                                                                                                                | 88  |

| $1 \rightarrow 1$                                                                                                                                                                                                                                                                                                                                                                                                         |     |

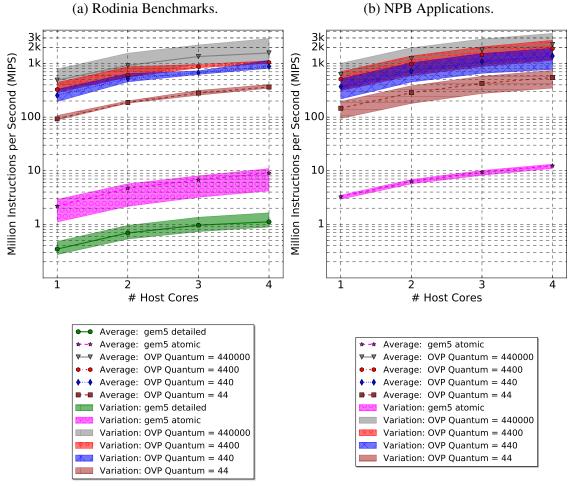

| Figure 4.13 Multiple VP-FIMs simulation speed and scalability using a quad-core                                                                    |       |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| host processor in terms of MIPS.                                                                                                                   | 89    |

| Figure 4.14 Fault injections using a multicore ARM Cortex-A72 processor (ARMv8                                                                     | 3).91 |

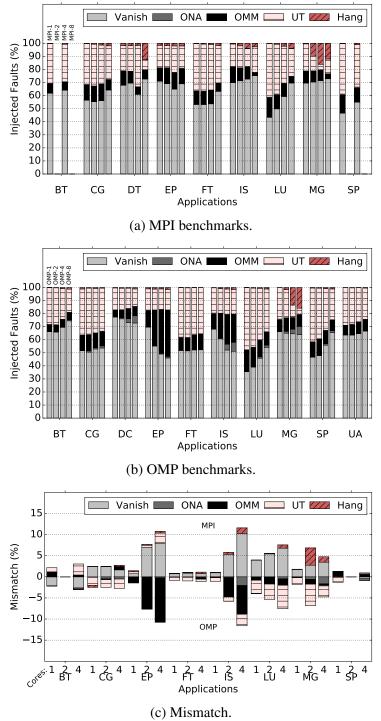

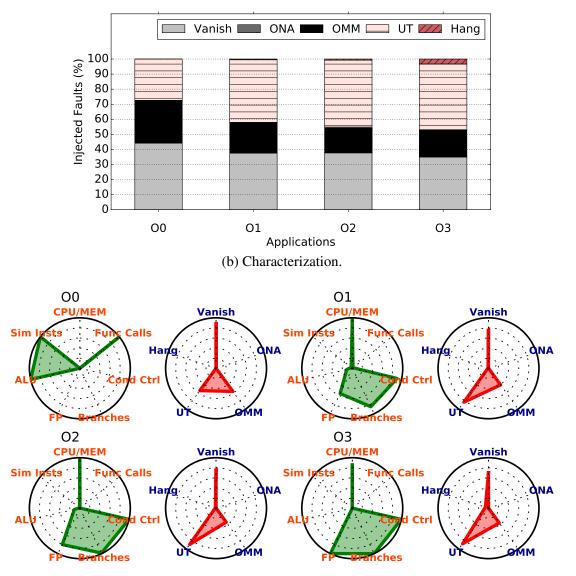

| Figure 4.15 NPB fault campaigns using distinct parallelization paradigms                                                                           | 96    |

| Figure 4.16 Soft error classification according to the system behavior under reg-                                                                  |       |

| ister fault injection considering 5 Rodinia benchmarks executing onto sin-                                                                         |       |

| gle core ARM Cortex-A9, regarding the three fault injection module (FIM)                                                                           |       |

| implementations: gem5-FIM atomic (GA), gem5-FIM detailed (GD), and                                                                                 |       |

| OVPsim-FIM (OV).                                                                                                                                   | 99    |

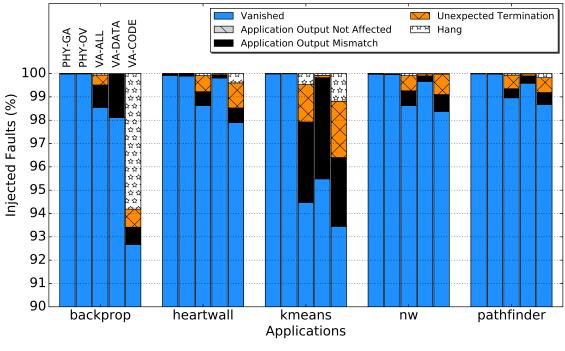

| Figure 4.17 Memory-based fault injection campaigns targeting physical memory                                                                       |       |

| gem5-FIM atomic (PHY-GA) and OVPsim-FIM (PHY-OV), comparing with                                                                                   |       |

| OVPsim-FIM extension VA the entire range (VA-ALL), the code section (VA-                                                                           |       |

| CODE), and data section (VA-DATA).                                                                                                                 | 99    |

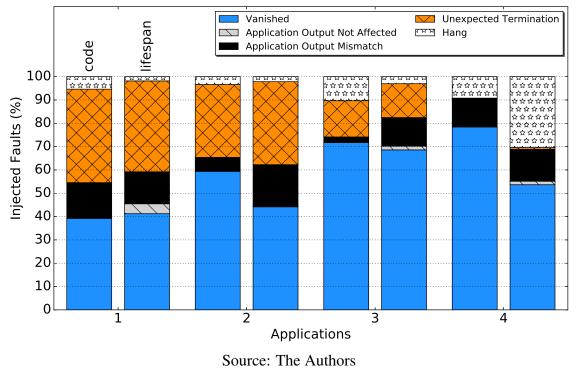

| Figure 4.18 Function-based fault injection techniques targeting four different func-                                                               |       |

| tions: bpnn_adjust_weightsomp_fn.1, bpnn_layerforward, gomp_barrier                                                                                | 101   |

| wait_end, and pick_next_task_fair.                                                                                                                 | 101   |

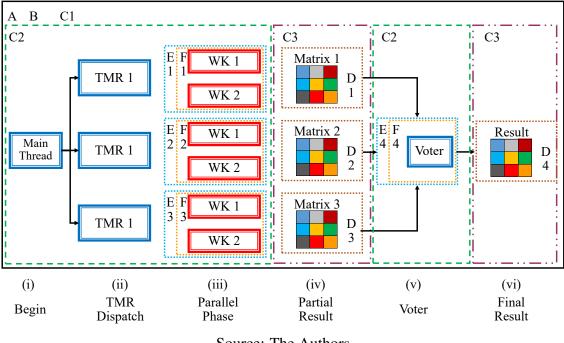

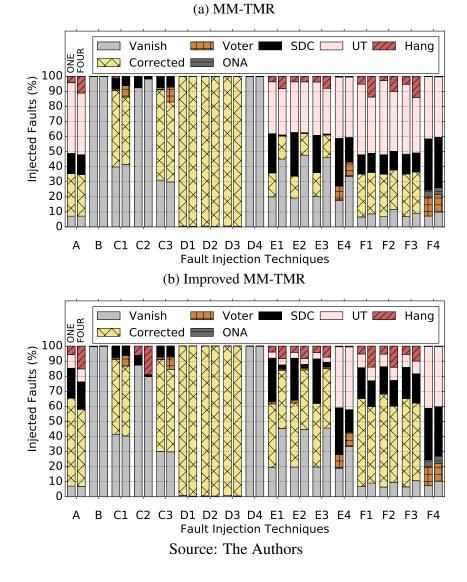

| Figure 4.19 TMR-Based Matrix Multiplication execution flow and fault target lo-                                                                    | 104   |

| cations according Table 4.19. WK refers to working thread.                                                                                         | 104   |

| Figure 4.20 MM soft error vulnerability analysis considering a single and quad-<br>core ARM Cortex-A9 processor.                                   | 106   |

| core ARM Cortex-A9 processor.                                                                                                                      | 100   |

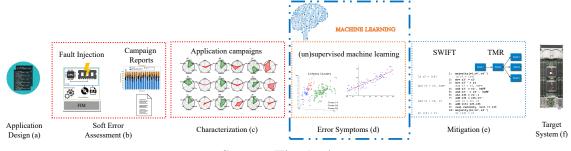

| Figure 5.1 Proposed system design cycle using machine learning.                                                                                    | 113   |

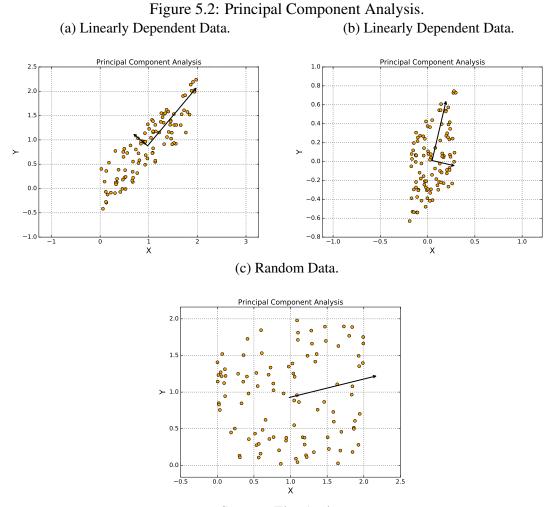

| Figure 5.2 Principal Component Analysis.                                                                                                           |       |

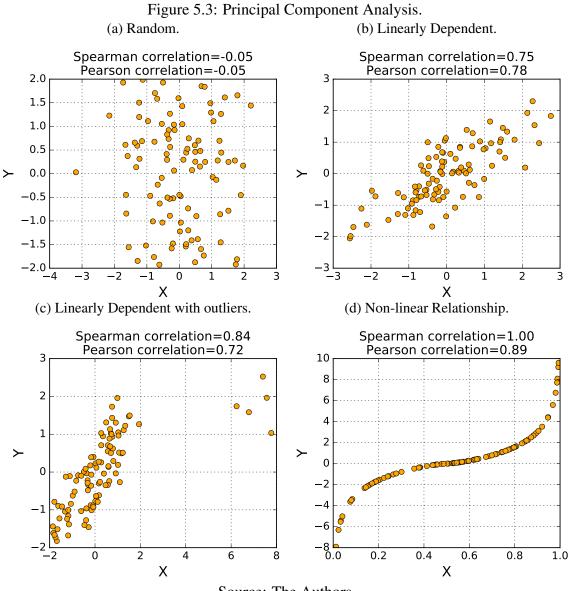

| Figure 5.3 Principal Component Analysis.                                                                                                           | 119   |

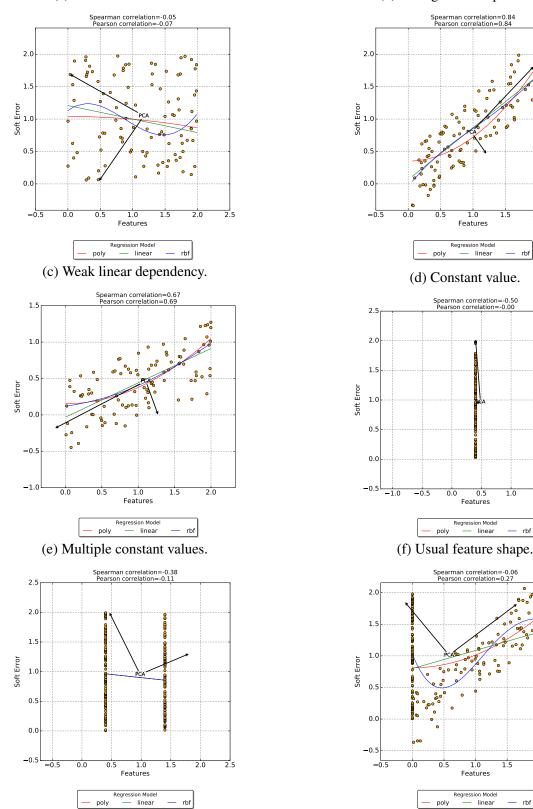

| Figure 5.4 Different of feature combination extracted from the gem5                                                                                | 121   |

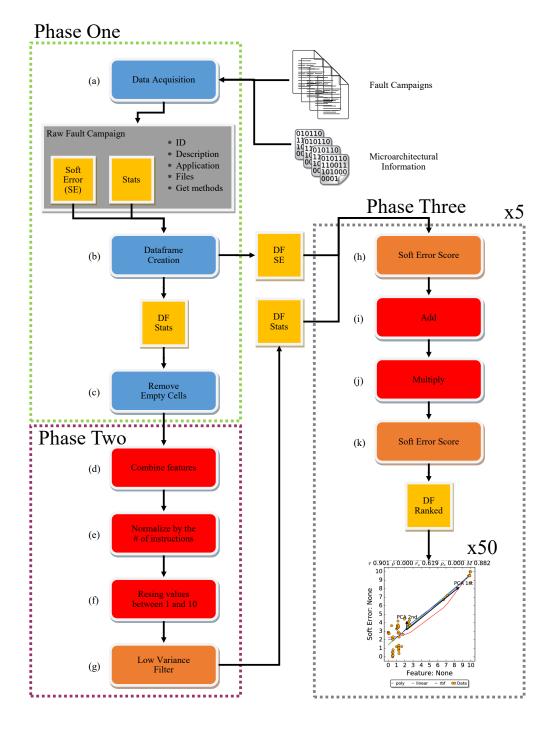

| Figure 5.5 Proposed Automated Flow                                                                                                                 | 123   |

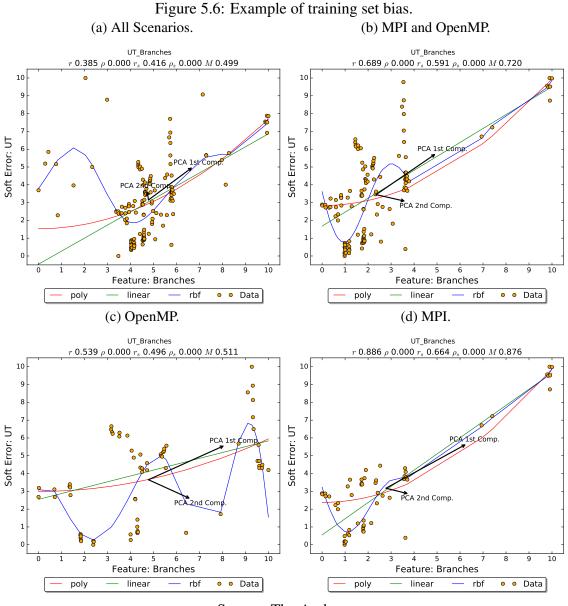

| Figure 5.6 Example of training set bias.                                                                                                           | 126   |

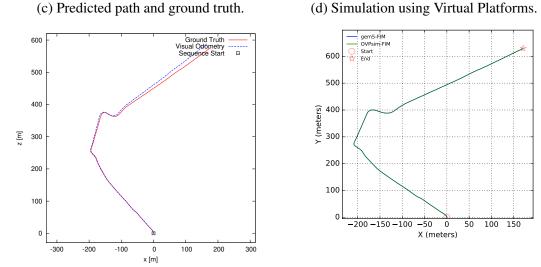

| Figure 5.7 NPB characterization.                                                                                                                   |       |

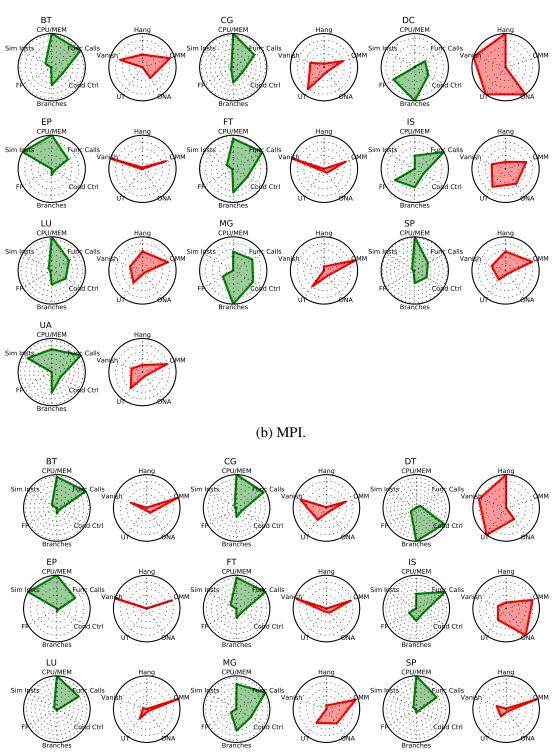

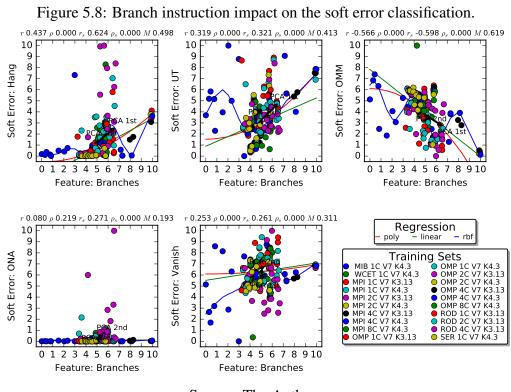

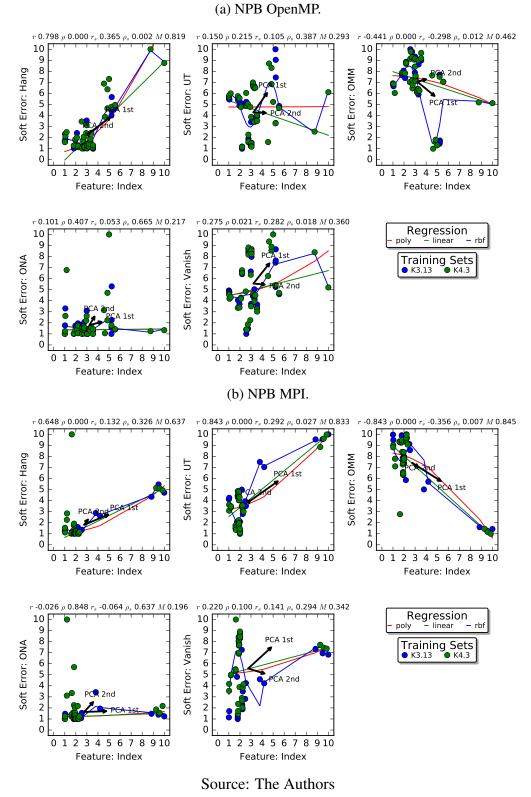

| Figure 5.8 Branch instruction impact on the soft error classification.                                                                             | 129   |

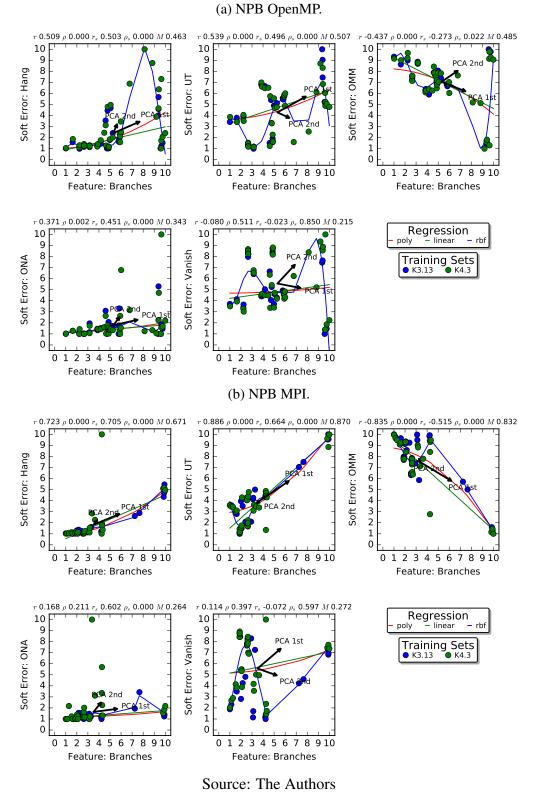

| Figure 5.9 Branch instruction impact on the soft error classification targeting par-                                                               |       |

| 11                                                                                                                                                 | 131   |

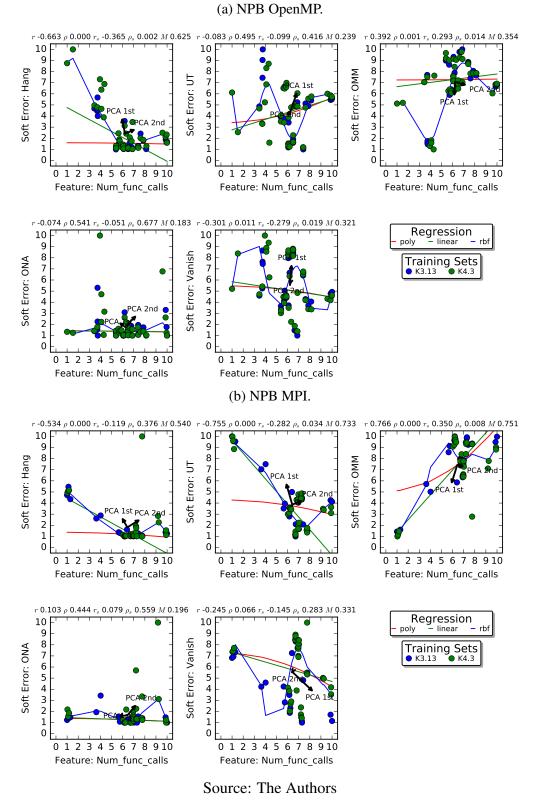

| Figure 5.10 Function calls impact on the soft error classification targeting parallel                                                              | 100   |

| applications.                                                                                                                                      | 132   |

| Figure 5.11 Proposed index impact on the soft error classification targeting parallel                                                              | 122   |

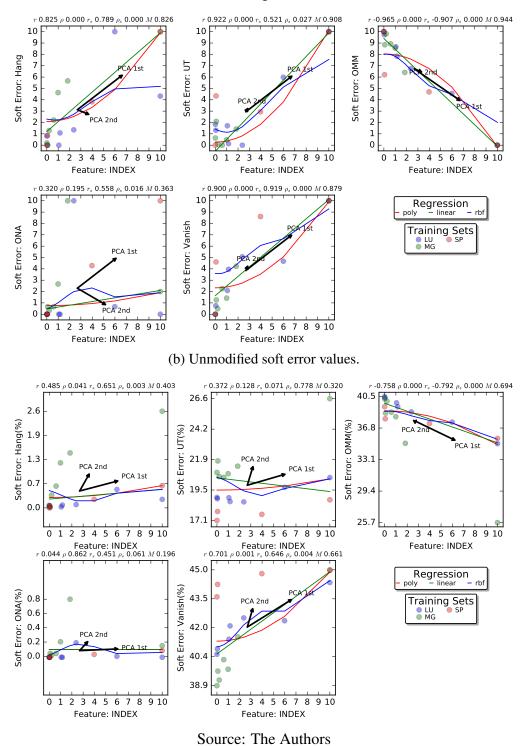

| applications<br>Figure 5.12 Proposed index targeting the LU,SP, and MG applications                                                                |       |

|                                                                                                                                                    | 134   |

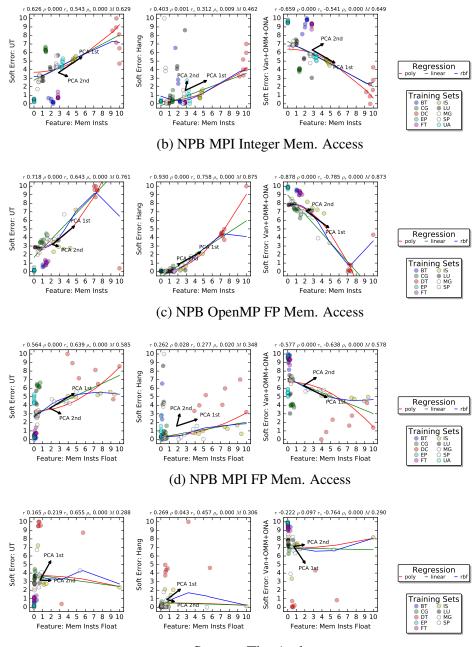

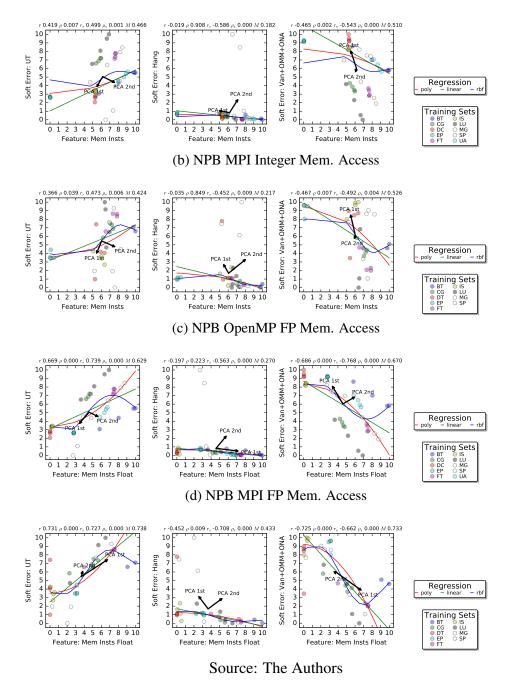

| Figure 5.13 Integer and Float-pointing (FP) memory access instructions impact on<br>the soft error classification targeting parallel applications. | 135   |

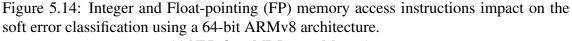

| Figure 5.14 Integer and Float-pointing (FP) memory access instructions impact on                                                                   |       |

| the soft error classification using a 64-bit ARMv8 architecture                                                                                    | 137   |

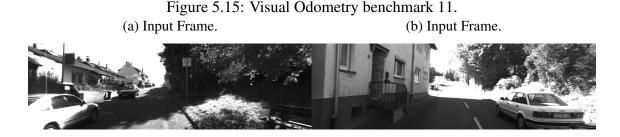

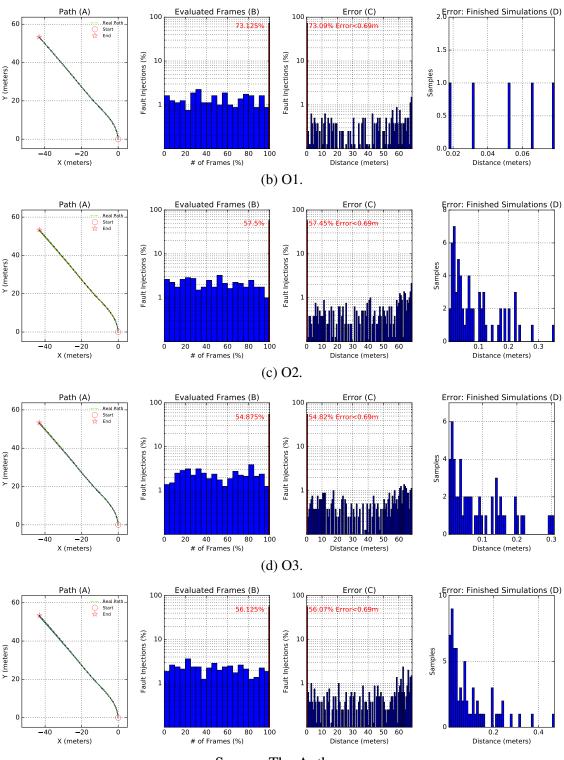

| Figure 5.15 Visual Odometry benchmark 11.                                                                                                          |       |

| Figure 5.16 Benchmark 11 initial exploration.                                                                                                      |       |

| Figure 5.17 Benchmark 11 initial exploration traveled route.                                                                                       |       |

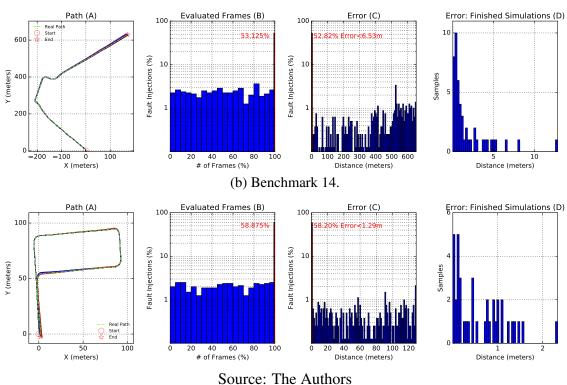

| Figure 5.18 Benchmarks complete execution.                                                                                                         |       |

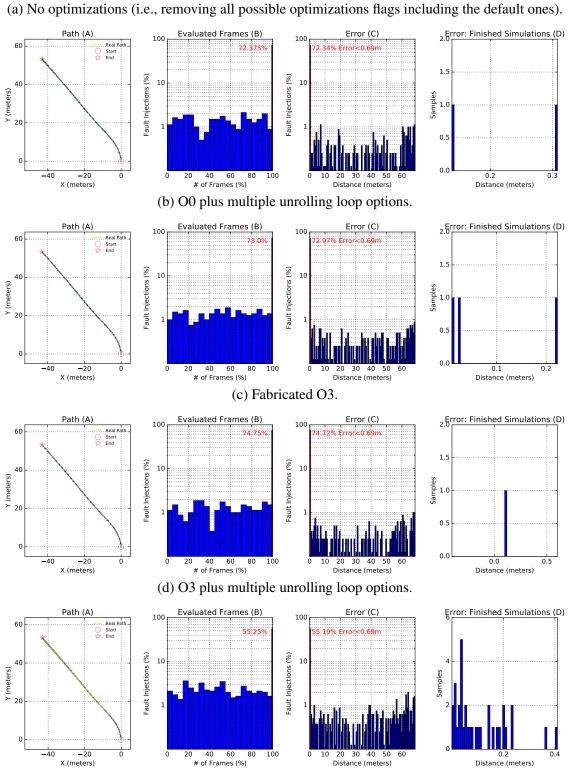

| Figure 5.19 Exploring the gcc optimization flags.                                                                                                  |       |

|                                                                                                                                                    |       |

| Figure 6.1 Proposed application design cycle using reinforced learning                                                                             | 151   |

# LIST OF TABLES

| Table 3.1 Most recognizable virtual platforms simulators                                        | 36  |

|-------------------------------------------------------------------------------------------------|-----|

| Table 3.2 Most recognizable virtual platform fault injection simulators.                        | 40  |

| Table 4.1 Fault injection campaigns summary.                                                    | 61  |

| Table 4.2 Virtual platforms experimental setup.                                                 | 63  |

| Table 4.3 Selected Rodinia applications.                                                        | 64  |

| Table 4.4 Rodinia applications simulation time varying the VP and number of cores.              | 65  |

| Table 4.5 NAS parallel benchmarks                                                               |     |

| Table 4.6 NPB serial benchmarks simulation time.                                                | 66  |

| Table 4.7 NPB openMP-based benchmarks simulation time                                           | 66  |

| Table 4.8 NPB MPI-based benchmarks simulation time.                                             |     |

| Table 4.9 Accumulated classification mismatch hypothetical 150-faults scenario                  | 71  |

| Table 4.10 Rodinia benchmarks ACM summary comparing three distinct VP-FIMs                      | 72  |

| Table 4.11 NPB ACM summary considering the OVPsim-FIM against the gem5-                         |     |

| FIM atomic.                                                                                     | 72  |

| Table 4.12 Rodinia benchmarks time-slice explorations worst, best, and average                  |     |

| cases considering the gem5-FIM atomic as reference                                              | 79  |

| Table 4.13 Rodinia mismatch benchmarks comparison considering the OVPsim-                       |     |

| FIM with default (DF) and 44-instruction quantum (Q) against the gem5-FIM                       |     |

| atomic.                                                                                         | 85  |

| Table 4.14 NPB mismatch comparison considering the OVPsim-FIM with default                      |     |

| (DF) and 44-instruction quantum (Q) against the gem5-FIM atomic.                                | 85  |

| Table 4.15 NPB workload summary.                                                                | 92  |

| Table 4.16 Hang occurrence compared with the normalized function calls multi-                   |     |

| plied branches (F*B)                                                                            | 93  |

| Table 4.17 ARMv7 Memory transactions and soft error classification for selected                 |     |

| scenarios.                                                                                      | 94  |

| Table 4.18         ARMv8         Memory transactions and soft error classification for selected |     |

| scenarios.                                                                                      | 94  |

| Table 4.19 Deployed fault injection techniques into the TMR-Based Matrix Multi-                 |     |

| plication reliability exploration                                                               | 103 |

| Table 5.1 Most recognizable virtual platform fault injection simulators.                        | 110 |

| Table 5.2 Available training sets.                                                              |     |

|                                                                                                 |     |

# CONTENTS

| 1 INTRODUCTION                                                                       | 16 |

|--------------------------------------------------------------------------------------|----|

| 1.1 Hypothesis to be demonstrated in Thesis                                          | 18 |

| 1.2 Thesis Goal                                                                      |    |

| 1.3 Original Contributions of this Thesis                                            | 20 |

| 1.3.1 Early soft error evaluation                                                    | 20 |

| 1.3.2 Novel non-intrusive fault injection techniques                                 |    |

| 1.3.3 Instruction-accurate fault injection consistency                               | 22 |

| 1.3.4 Extensive investigation of the software stack impact on the system reliability |    |

| 1.3.5 Correlating Soft Errors and Microarchitectural Data                            | 23 |

| 1.4 Thesis Outline                                                                   |    |

| 2 BACKGROUND ON SOFT ERRORS                                                          | 25 |

| 2.1 Main Reliability Challenges in Electronic-based Systems                          | 25 |

| 2.2 Radiation Induced Soft Errors                                                    |    |

| 2.2.1 Radiation Source and Soft Errors Mechanisms                                    |    |

| 2.2.2 Fault Propagation and Masking                                                  |    |

| 2.2.3 Soft Error Metrics                                                             |    |

| 2.2.4 Soft Error Trends in Electronic Systems                                        | 31 |

| 2.3 Soft Error Assessment                                                            |    |

| <b>3 PROPOSED FAULT INJECTION FRAMEWORK</b>                                          |    |

| 3.1 Virtual Platforms                                                                | 35 |

| 3.2 Related Work on Fault Injection Approaches using Virtual Platforms               |    |

| 3.3 Fault Modeling                                                                   |    |

| 3.4 Fault Injection Flow                                                             |    |

| 3.5 OVPsim-FIM                                                                       |    |

| 3.6 gem5-FIM                                                                         |    |

| 3.7 Extensions                                                                       |    |

| 3.7.1 Targeting Complex SW Stacks                                                    |    |

| 3.7.2 Injecting Faults on Multicore systems                                          |    |

| 3.7.3 ARMv8 Architecture extension                                                   |    |

| 3.7.4 Fault Campaign Speed Enhancement                                               |    |

| 3.7.4.1 Checkpoint and Restore Technique                                             |    |

| 3.7.4.2 Shared Memory Multicore Parallelization                                      |    |

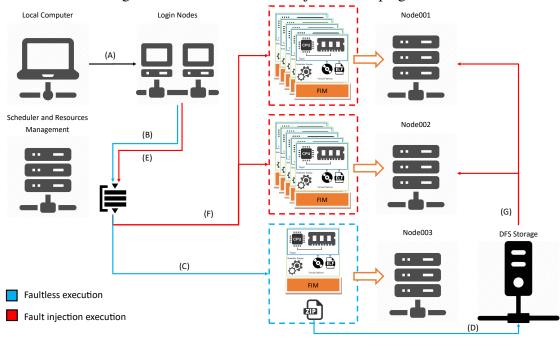

| 3.7.4.3 Distribute Fault Injection Campaigns using HPCs                              |    |

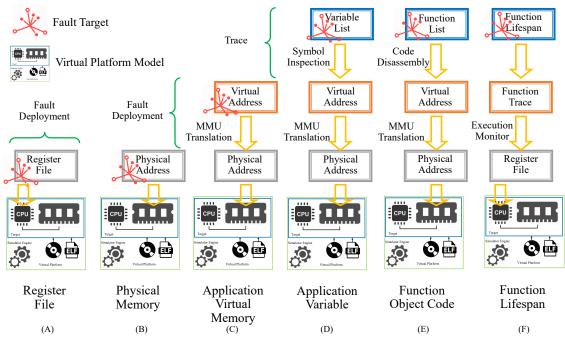

| 3.8 Focused Fault Injection Extension                                                |    |

| 3.8.1 SOFIA                                                                          |    |

| 3.8.1.1 Application Virtual Memory                                                   |    |

| 3.8.1.2 Application Variables and Data Structures                                    |    |

| 3.8.1.3 Function Code                                                                |    |

| 3.8.1.4 Function Lifespan                                                            |    |

| 3.8.1.5 Fault Inspection                                                             |    |

| 3.9 Closing Remarks                                                                  |    |

| 4 EVALUATION OF PROPOSED FAULT INJECTION FRAMEWORK                                   |    |

| 4.1 Experimental Setup                                                               | 62 |

| 4.2 Performance and Accuracy Evaluation of Instruction-Accurate Virtual              |    |

| Platforms                                                                            |    |

| 4.2.1 Accuracy                                                                       | 67 |

| 4.2.2 Instruction-accurate Simulation Engine Parameters Impact On Soft Error As-<br>sessment | 76  |

|----------------------------------------------------------------------------------------------|-----|

| 4.2.2.1 Quantum-leap impact on soft error assessment                                         |     |

|                                                                                              |     |

| 4.2.2.2 Mismatch considering the quantum size                                                |     |

| 4.2.3 Performance and Speedup                                                                |     |

| 4.3 Soft Error Evaluation Considering Multicore Design Metrics/Decisions                     | 90  |

| 4.3.1 ISA Reliability Assessment                                                             |     |

| 4.3.1.1 Execution Time and Workload                                                          |     |

| 4.3.1.2 Register File Size                                                                   |     |

| 4.3.1.3 Branches and Function calls                                                          |     |

| 4.3.1.4 Memory Transactions                                                                  |     |

| 4.3.2 Parallelization API                                                                    |     |

| 4.3.2.1 Serial vs APIs                                                                       |     |

| 4.3.2.2 Vulnerability Window                                                                 |     |

| 4.4 Focused Fault Injection Results                                                          |     |

| 4.4.1 Case Study                                                                             |     |

| 4.4.1.1 Triple Modular Redundancy                                                            |     |

| 4.4.1.2 Improving the Triple Modular Redundancy                                              | 107 |

| 4.5 Closing Remarks                                                                          | 108 |

| <b>5 MACHINE LEARNING APPLIED TO SOFT ERROR ASSESSMENT IN</b>                                |     |

| MULTICORE SYSTEMS                                                                            | 109 |

| 5.1 Machine Learning Applied to System Reliability                                           | 110 |

| 5.2 Problem Description                                                                      | 112 |

| 5.3 Proposed Solution                                                                        |     |

| 5.4 The Promoted ML Investigation Tool                                                       |     |

| 5.4.1 Feature Acquisition                                                                    |     |

| 5.4.1.1 Pandas DataFrames                                                                    |     |

| 5.4.2 Feature Transformation                                                                 |     |

| 5.4.2.1 Rescaling                                                                            |     |

| 5.4.2.2 Normalization                                                                        |     |

| 5.4.2.3 Merging Similar Features                                                             |     |

| 5.4.2.4 Feature Combination                                                                  |     |

| 5.4.3 Feature Selection                                                                      |     |

| 5.4.3.1 Variance Threshold                                                                   |     |

| 5.4.3.2 Principal Component Analysis                                                         |     |

| 5.4.3.3 Linear Regression                                                                    |     |

| 5.4.3.4 Correlation Coefficient                                                              |     |

|                                                                                              |     |

| 5.4.3.5 Recursive Feature Elimination                                                        |     |

| 5.4.3.6 Euclidean Distance                                                                   |     |

| 5.4.3.7 Soft Error Score                                                                     |     |

| 5.5 Exploration Flow                                                                         |     |

| 5.5.1 Phase 1 - Feature acquisition and data homogenization                                  |     |

| 5.5.2 Phase 2 - Unidimensional Feature Transformation and Selection                          |     |

| 5.5.3 Phase 3 - Multidimensional Feature Transformation and Selection                        |     |

| 5.6 Results                                                                                  |     |

| 5.6.1 Training Set Selection and Bias                                                        |     |

| 5.6.2 Characterization                                                                       |     |

| 5.6.3 Branches and Function calls                                                            |     |

| 5.6.4 Memory Transactions                                                                    |     |

| 5.7 Case Study                                                                               |     |

| 5.8 Closing Remarks                                                                          | 144 |

| 6 CONCLUSION AND FUTURE WORKS                                                        | .146 |

|--------------------------------------------------------------------------------------|------|

| 6.1 Contributions                                                                    | .146 |

| 6.1.1 Early soft error evaluation                                                    | .146 |

| 6.1.2 Fault Injection Controllability                                                | .147 |

| 6.1.3 Instruction-accurate fault injection consistency                               | .147 |

| 6.1.4 Extensive investigation of the software stack impact on the system reliability | .147 |

| 6.1.5 Using machine learning techniques to explore the software stack reliability    | .148 |

| 6.2 Future Works                                                                     | .148 |

| 6.2.1 Soft Error Mitigation                                                          | .148 |

| 6.2.2 Self-Driven Reliability Assessment and Reaction                                |      |

| REFERENCES                                                                           | .153 |

| APPENDICES                                                                           | .163 |

| APPENDIXA LIST OF WORKS PUBLISHED BY THE AUTHOR                                      | .164 |

# **1 INTRODUCTION**

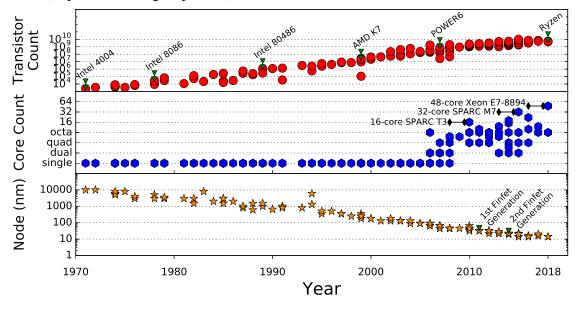

Computers become ubiquitous in our modern society ranging from everyday life devices (e.g., televisions, vending machines, smartphones) to complex systems such as those used to weather forecast or search for microscopic subatomic particles (BUCHA-NAN, 2018; Inside HPC, 2018). The continuous technology scaling (BORKAR; CHIEN, 2011) and the advance of multicore components such as processors and graphics processing unit (GPUs) are driving the microelectronics industry forward. This evolution can be exemplified by the advanced driver-assistance systems (ADAS),(VLACIC; PARENT; HARASHIMA, 2001; MCCLUSKEY, 2017; JONES, 2002; BISHOP, 2005) enabling self-driven cars in the near future (GEIGER; LENZ; URTASUN, 2012a). The emerge of The Internet of Things (IoT) is another example(PERERA et al., 2014; ZANELLA et al., 2014) which is expected to integrate about 30 billion of devices by 2020 (NORDRUM, 2016). The semiconductor systems dissemination phenomenon was possible (or caused) by Gordon Moore's seminal work (MOORE, 1965) on transistor scaling. This work introduces the famous Moore's Law which states that the number of transistors per square inch doubles every 18 months. As a consequence, every new technology node had delivered increasing performance, lower power consumption, and smaller transistor cost. The top plot of Figure 1.1 displays the increasing number of transistors in microprocessors since 1970.

Single-thread processors have benefited from technological advancements to improve their performance by increasing clock frequency (BORKAR; CHIEN, 2011). However, in mid-2000, this trend reaches the physical limits due to the increased power consumption and the current density within the chip (ESMAEILZADEH et al., 2011; ES-MAEILZADEH et al., 2012). The central plot of Figure 1.1 shows the growing number of cores in commercial processors over the last decades. Integrating modern multicore processors (e.g. big.LITTLE (ARM, 2017)) and GPUs in the same system is now commonplace in both embedded and high-performance computing (HPC) domains (DINECHIN et al., 2013; BORKAR; CHIEN, 2011). Such systems aim to perform complex software stacks (i.e., operating system OS, drivers, and applications) from diverse fields (e.g., spatial, avionics, automotive). However, the ever-increasing demand for performance, energy efficiency and high reliability of emerging systems is imposing a myriad of challenges to the design of underlying systems:

• programmability, ease of programming is a feature of paramount importance in

Figure 1.1: Evolution of commercial processors during the last decades considering the number of transistors (top), number of cores (middle), and associeted technology node (botton) from 1970 to 2018. Information gathered from multiple sources including the ITRS (https://www.itrsgroup.com/).

Source: The Authors

large-scale systems composed of different processors, resulting in different platform libraries (e.g., MPI, OpenMP), compilers, instruction set architecture (ISAs) (GARIBOTTI et al., 2013).

- security, with the increasing number of components and devices sending and receiving user sensitive data, providing a secure service is fundamental. The increasing system complexity introduces vulnerabilities to software and hardware architectures compromising the system behavior. Attackers can exploit such vulnerabilities to introduce malicious code, which may incur in undesired effects, security breaches, or damage to a system (MCCLUSKEY, 2017).

- energy efficiency, while the constant supply and threshold voltage scaling in transistors led to an exponential increase of leakage current. In addition to that, other physical restrictions related to device packaging, intra-chip current distribution, and cooler dissipation during power peaks further impact on the systems energy consumption (ZHANG et al., 2013). Energy-efficiency is becoming more critical than high-speed operation, and dark silicon era is imposing more power-oriented constraints to the design of such systems.

- reliability and dependability, the technology transistors reach the operation physical

limits, thus becomes increasingly difficult for the hardware components to achieve reliable execution. The unreliability of multicore-based systems is emerging from several sources, e.g., electrical noise, cross-talk, radiation particles, aging, and variability (KARNIK; HAZUCHA, 2004).

Reliability is rapidly emerging as a significant design metric in both embedded and HPC domains. The increasing chip power densities allied to the continuous technology shrink is making emerging multicore-based systems more vulnerable to soft errors, such as the ones caused by radiation events (KARNIK; HAZUCHA, 2004). As illustrated in the bottom graph of Figure 1.1, commercial processors based on 10 nm process node are likely to be available in the market in the coming years. Until recently, radiation-induced faults issue was relegated to high-availability systems such as military applications and radiation-bounded systems as spatial and avionics. Nowadays, the occurrence of soft error appears as a primary concern of electronics systems working at ground level (MUKHER-JEE, 2008). A transient error, also known as a soft error, induced by radiation particles can lead to financial or human life losses (YOSHIDA, 2015). For instance, the occurrence of a soft error in HPC systems could lead to the underutilization of resources, which results in extra cost and time wasted waiting for the re-execution of applications/jobs. Although, a supercomputer with 900 compute nodes registered a rate of 0.15 error per day, over a year of operation (BAUTISTA-GOMEZ et al., 2016), electronic computing systems working at ground level are expected to experience at least one soft error per day in near future (GRANLUND; GRANBOM; OLSSON, 2003).

The resulting growing susceptibility of multicore systems to soft errors necessarily calls for novel cost-effective tools to assess the soft error resilience of underlying systems early in the design phase. The preceding context provides the *motivation* for this Thesis, which aims at investigating novel fault injection techniques and tools that can be used to assess soft errors of multicore-based systems under fault campaigns at early design time.

#### 1.1 Hypothesis to be demonstrated in Thesis

This Thesis relies on two hypothesis:

• Enhancing virtual platforms with fault injection capabilities enable to speed up the evaluation of more realistic multicore systems (i.e., real software stacks, state-of-the-art ISAs) at early design phases. The use of such fault injection frameworks

increases the probability of generating soft errors and failures in those multicore systems, which allows to generate and collect more error/failure-related data in a reasonable time.

With large error/failure-related data sets, engineers are more likely to identify meaningful relationships or associations between fault injection results, application characteristics, and platform parameters. When dealing with large failure-related data sets obtained from the fault campaigns, it is essential to filter out non-correlated features (i.e., Parameters without a direct relationship with the system reliability). In this regard, the second hypothesis of this Thesis is that the use of supervised and unsupervised machine learning techniques are appropriate to filter and identify the correlation between fault injection results and application and platform characteristics, enabling them to improve existing fault mitigation techniques, as well as to investigate and propose new and more efficient ones.

# **1.2 Thesis Goal**

In order to address the hypothesis mentioned above, the strategic goal of this Thesis is first to combine existing and novel simulation and fault injection techniques into virtual platforms, targeting fast and detailed soft error reliability exploration of state-ofthe-art multicore systems. The second strategic goal of this Thesis is investigate appropriete machine learning techniques to develop an automated engine capable of searching and identifying the individual (or combinations of) microarchitectural (e.g., instruction types, memory stats) and software parameters (e.g., number of branches, etc), which present the most substantial relation relationship with each detected soft error and failures.

To accomplish the first strategic goal, the following specific objectives should be fulfilled:

- Identify the most suitable and efficient virtual platforms to include fault injection capabilities, aiming to support the soft error analysis of state-of-the-art processor models;

- Port of several benchmarks from embedded and HPC domains, including the Rodinia and NASA NAS Parallel Benchmark (NPB) suites;

- Investigate the soft error analysis consistency between an instruction-accurate VP

and a cycle-accurate full system simulator;

• Proposal and development of novel fault injection techniques and tools that enable to trace, evaluate, and identify particular source of errors (e.g., application functions, code structure).

The second goal requires the following task to be achieved:

- Support the use of machine learning techniques to enable the identification of individual (or combinations of) microarchitectural and software parameters that present the most substantial relation relationship with each detected soft error or failure.

- Employ proposed techniques and developed tools to investigate the impact of software and hardware parameters on soft error system resiliency, considering a significant number of fault injection campaigns.

#### **1.3 Original Contributions of this Thesis**

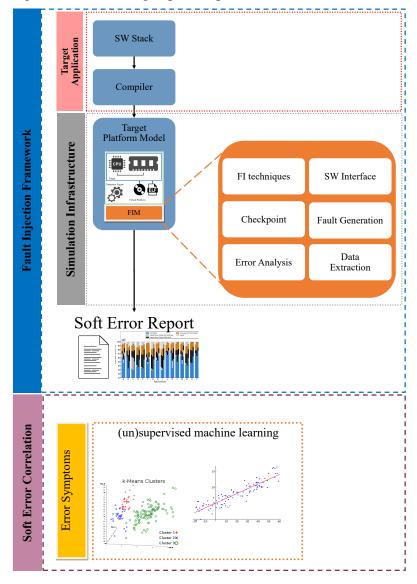

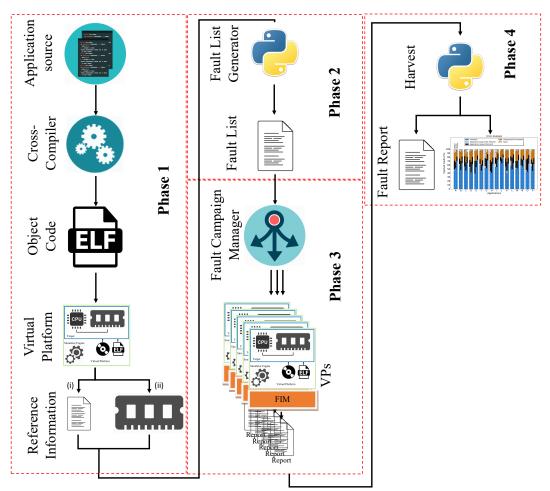

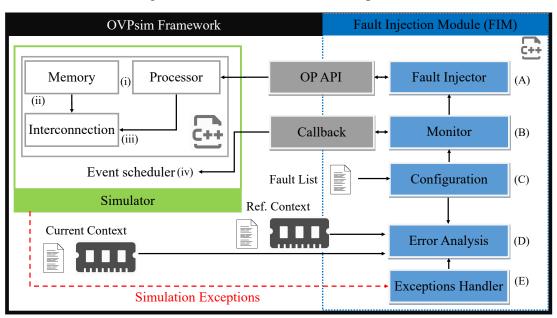

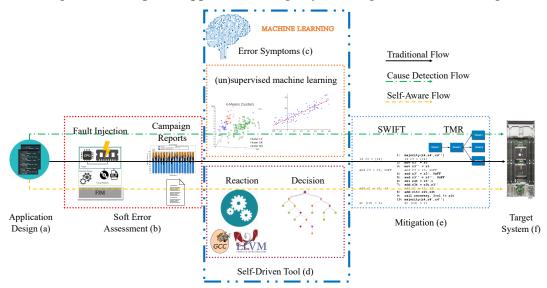

Figure 1.2 illustrates the main contributions of this work, which are joined into a soft error analysis flow that includes fault injection and soft error analysis extensions(fully described in Chapter 3), and automated soft error correlation using machine learning techniques (described in Chapter 5).

The main contributions of this Thesis are described as follows:

#### **1.3.1** Early soft error evaluation

Proposal of two flexible fault injection (FI) frameworks: the OVPsim-FIM developed on top of the OVPsim (IMPERAS, 2017) and the gem5-FIM, which relies on the gem5 (BINKERT et al., 2011). Both frameworks integrate a set of fault injection techniques, allowing fast soft error susceptibility exploration considering state-of-the-art multicore processor architectures, such as ARMv7, ARMv8, and big.LITTLE.

Figure 1.2: Diagram with the design space exploration flow and this thesis contributions.

Source: The Authors

# 1.3.2 Novel non-intrusive fault injection techniques

Random fault injection homogeneously probes the application (i.e., every function has an equal fault probability), nevertheless, some code segments are more critical than others to the system reliability. The OVPsim-FIM was extended with four novel and non-intrusive FI techniques targeting: (i) the virtual memory, : (ii) variables, : (iii) function code, and : (iv) function execution. The underlying techniques offer flexibility and full control over the fault injection process when targeting complex software stacks. Further, this new module provides a more powerful fault inspection module, enabling the user to add custom verifications. In other words, it is possible to check data structures and execution patterns during or after the application simulation. For example, this new module reduces false-positive SDC (i.e., silent data corruption) detections by checking only a select group of variables instead of the entire memory. This tool provides software engineers with detailed and comprehensive fault injection capabilities to explore critical code sections in a quick and non-intrusive manner.

# **1.3.3 Instruction-accurate fault injection consistency**

Instruction-accurate simulators provide a simulation performance of thousands of millions of instructions per second (MIPS), enabling quick explorations of large and complex scenarios. However, its accuracy regarding soft error assessment was never addressed and to investigate this matter, the proposed OVPsim-FIM (i.e., instruction-accurate simulator) was compared against the cycle-accurate gem5-FIM. This exploration comprises millions of fault injections. Results show that the unmodified OVPsim-FIM can achieve an average mismatch of less 25% when considering the gem5-FIM. This work further explores the OVPsim-FIM engine by investigating different configurations. With the proper simulator settings, the average mismatch can be reduced to less than 15%. More interesting, the worst-case mismatch can be reduced by fivefold while sustaining the high-performance simulation suitable to early design space explorations.

#### 1.3.4 Extensive investigation of the software stack impact on the system reliability

This work uses the proposed FI framework scalability to explore early design decisions impact on the system reliability, e.g., architecture, number of cores, ISA, OS, parallelization library, among other possible configurations. Different from other works, the promoted frameworks use a realistic software stack comprising multiple unmodified operating systems (e.g., Linux 4.3, Linux 3.13, FreeRTOS) alongside parallelization libraries (e.g., OpenMP, MPI, PTHREADS, and OmpSs). Further, this work addresses another common issue of fault injection frameworks: *performance* and *scalability*. The developed fault injector adopt three simulation techniques to increases the soft error analysis performance: (*i*) host multicore parallelization, (*ii*) checkpoint and restore technique, and (*iii*) large-scale and distributed simulation, targeting its use on supercomputers.

This extensive evaluation considers more than three million fault injections (re-

quiring up to three million of simulation hours) targeting 45 distinct benchmarks, considering serial, MPI, and OpenMP implementations from the NAS Parallel Benchmark (NPB) suite (BAILEY et al., 1991) and the Rodinia Benchmark suite (CHE et al., 2009) among others. This exploration targets single, dual, quad, and octa-core ARM Cortex-A9 and ARM Cortex-A72 processor models. The investigation shows distinct effects of the chosen parallelization (e.g., OpenMP vs. MPI) library on the system fault tolerance, also, how the ISA decision can impact the system behavior under fault influence.

#### **1.3.5 Correlating Soft Errors and Microarchitectural Data**

Converting fault injection explorations into actual system reliability improvements is not a straightforward process. This Thesis proposes a cross-layer investigation toolset that uses machine learning techniques to perform multi-variable and statistical analysis using the gem5 microarchitectural information (e.g., memory usage, application instruction composition) along with other software profiling tools (e.g., line coverage) that are combined with soft error vulnerability evaluation results (i.e., fault injection campaigns). Proposed toolset enables to reduce the number of fault injection campaigns required during early design space exploration by using software symptoms (e.g., execution time, number of branches) correlated with soft error vulnerabilities to improve the target application reliability. Developed toolset provides users with a flexible investigation, where several information sources can be easily included, selected, and conformed to different machine learning investigation techniques.

#### **1.4 Thesis Outline**

This Thesis is organized into six chapters. Chapter 1 introduces the reliability issues in modern system design and this Thesis contributions. The following paragraphs present a succinct Thesis summary chapter by chapter.

**Chapter 2 - Background on Soft Errors:** The first section of this chapter (Section 2.1) introduces the modern challenges to modern electronic devices then Section 2.2 presents a brief background on soft errors history and source mechanisms. Section 2.3 presents the state-of-the-art on soft error assessment using distinct approaches.

Chapter 3 - Simulation-based Fault Injection Using Virtual Platforms: First,

Sections 3.1 and 3.2 provide a discussion on the available virtual platforms and their fault injection frameworks. Section 3.3 describes the adopted fault model while Section 3.4 presents the fault injection flow. The fault injection framework detailed development is shown by Sections 3.5 and 3.6 targeting the gem5 and OVPsim simulators respectively. Several features had been included in the fault injection framework including speed boosting techniques (Section 3.7). Section 3.8 provides extra tooling to help software developers to explore in deep the application effects under soft errors this chapter proposes two FIM extensions: (i) include new software-focused fault injection techniques to restrict the targeting area, e.g., a particular function or data representation. (ii) provide a non-intrusive library to customize the error analysis and detection to accommodate the user necessities.

**Chapter 4 - Evaluation of Proposed Fault Injection Framework:** This chapter presents results for several fault injection campaign using dozens of applications in hundred of distinct scenarios. Section 4.1 describes the 45 adopted applications from the Rodinia benchmarks and the NAS Parallel Benchmark. The chapter is divided in three main parts: Section 4.2; Performance and Accuracy Evaluation of proposed OVPsim-FIM. Section 4.3; Soft Error Evaluation Considering Multicore Design Metrics/Decisions. Section 4.4; Focused Fault Injection Preliminary Results.

**Chapter 5 Machine Learning Applied to Soft Error Assessment in Multicore systems** This chapter describes the promoted a cross-layer investigation tool which performs multivariable and statistical analyses. First, Section 5.1 debates the state-of-the-art of reliability using machine learning techniques. Sections 5.2 and 5.3 discusses, respectively, the problem of investigating large-scale fault injection campaigns and how this work mitigates this issue. The proposed tool requires multiple machine learning techniques which are described by Section 5.4, while Section 5.5 details the tool execution flow. Finally, Section 5.6 shows results related to multiple investigations using the proposed tool.

**Chapter 6 - Conclusion and Future Works:** This chapter summarizes this work contribution until this point. Also, it describes the future works related to this Thesis.

#### **2 BACKGROUND ON SOFT ERRORS**

This chapter details some necessary backgrounds and state-of-the-art works related to this Thesis exploration on soft error assessment. First, Section 2.1 enumerates several reliability challenges encountered by modern electronic devices, while Section 2.2 provides a brief history and background on radiation-induced soft errors. In particular, Section 2.2.1 explains the particle strike and the charge accumulation process, Section 2.2.2 shows several fault masking mechanisms, and Section 2.2.3 introduces useful metrics to evaluate the occurrence of soft errors. The Section 2.3 investigates the recent innovations in soft error vulnerability assessment.

#### 2.1 Main Reliability Challenges in Electronic-based Systems

The semiconductor industry is facing significant reliability challenges to guarantee the correct functionally of electronic systems (KARNIK; HAZUCHA, 2004). Problems such as process variability, permanent faults, and transient faults are a significant issues for semiconductor-related industry sectors (HENKEL et al., 2013; SHIVAKUMAR et al., 2002). Three main fault groups comprehensive encompass the device reliability challenges for the future technologies:

- (i) Process Variability: As the transistor's features scales down the chip variability grows during the fabrication process (PANDINI, 2009) impacting multiple parameters, e.g., channel length, doping concentration, oxide thickness. For comparison's sake, state-of-the-art fabrication processes 10 nm shapes are only four times larger than the diameter of a DNA strand. Consequently, devices with identical logical design have distinct physical and electrical characteristics from die to die (i.e., interdie variations) and on the same die (i.e., intra-die variations). These issues result in yield, power, and performance reduction as the same design must withstand a wider parameter variation (BORKAR et al., 2003).

- (ii) Permanent faults: are physical imperfections such as stuck-at-zero and timing violations in conjunction with aging problems. For instance, decreasing transistor sizes cause faster aging and eventually transistor wear out due to distinct phenomena such as Hot Carrier Injection (HCI), Bias Temperature Instability (BTI), Electromigration, and Time Dependent Dielectric Breakdown (TDDB) (ALAM et al.,

2007). These problems reduce the chip average lifetime and impact on its meantime between failures (MTBF) by steadily increasing propagation delays.

(iii) Transient faults: or soft errors encompass all sort of malfunctions without permanent circuit damage. Such errors may occur due to the occurrence of electrical noise, electromagnetic interference, as well as exposition to radiation. Soft errors cause single event effects (SEEs) in a processor, which can be propagated through logical (e.g., logic gates) and memory elements (e.g., latches, registers). Whenever an SEE surpasses a specific charge threshold<sup>1</sup> it will induce an incorrect computation affecting logical and storage elements. In contrast to permanent faults and process variability, new data can still be correctly written and stored on the affected device. Due to the technology high-frequency, low voltage supply, and continuous technology shrink the transistor becomes more susceptible to soft errors as the minimal energy to provoke it is reducing (SEIFERT, 2010; BAUMANN, 2005).

While process variability increases the production cost and development time, permanent faults lead to premature wearing (i.e., reducing the system's lifetime). The technology fabrication process and new low-level system designs (i.e., gate-level) can partially mitigate its occurrence. Also, it affects appears during a prolonged time span enabling early detection and correction. In contrast, transient faults will introduce erroneous behavior in the system at random time without previous warning or at predictable rates. Soft errors may emerge either during intensive or idle working periods, affecting both critical and non-essential system functionalities. Among aforementioned reliability challenges, soft errors are the most prominent one in several sectors of the semiconductor industry. Processor-based systems working at sea level are expected to experience at least one soft error per day (GRANLUND; GRANBOM; OLSSON, 2003).

#### 2.2 Radiation Induced Soft Errors

Soft Errors caused by radiation particles became in the last years a recurring research topic in both academia and industry (SLAYMAN, 2010; LI et al., 2016). Nevertheless, the radiation effects on semiconductor materials are well-known for more than half-century. In 1961, (WALLMARK; MARCUS, 1961) predicted the transistor scaling limits arround 10 µm for several reasons, including cosmic rays. A decade later in 1975,

<sup>&</sup>lt;sup>1</sup>This critical threshold depends on the technology node, cell design, and neighboring gates.

the misbehavior of digital circuits used in a communication satellite was identified and studied by (BINDER; SMITH; HOLMAN, 1975). Binder *et al.* reported galactic cosmic rays effects in the processor flip-flops as the principal error source. In a retrospective investigation, (NORMAND et al., 2010) found an unusual number of parity errors in the Los Alamos Cray-1 supercomputer during the year of 1976, pointing to ground-level high-energy neutrons as its cause. DRAM soft error vulnerability to heavily-ionizing radiation are discussed by (MAY; WOODS, 1978), and (ZIEGLER; LANFORD, 1979) investigate the silicon interactions at sea-level with cosmic-ray nucleons and muons. The next subsection presents examples of radiation strike mechanisms. Afterward, Section 2.2.2 discusses fault masking mechanisms during and fault propagation, Section 2.2.3 shows some soft errors quantification metrics, and Section 2.2.4 explores the trends of soft errors in future systems.

### 2.2.1 Radiation Source and Soft Errors Mechanisms

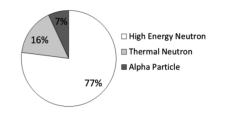

According to Baumann *et al.* (BAUMANN, 2005) soft errors induced by radiation originate from three primary sources: (*i*) the emissions of **alpha particles** due to the presence of radiative impurities on the chip packaging; (*ii*) an alpha particle (i.e., two neutrons and two protons) traveling through a semiconductor material loses kinetic energy leaving an ionization trail behind; and (*iii*)**high-energy cosmic rays** originating from outer space, which produce a complex cascade of secondary particles in earth's atmosphere (e.g., muons, protons, neutrons, and pions). For example, a neutron collision with one Si atom emits lighter ions and sub-particles (e.g., protons, alpha particles). **Lowenergy cosmic rays** (i.e., up to 1 MeV) create ionizing particles in electronic devices from the interaction of neutrons and borons atoms (i.e., p-type dopant).

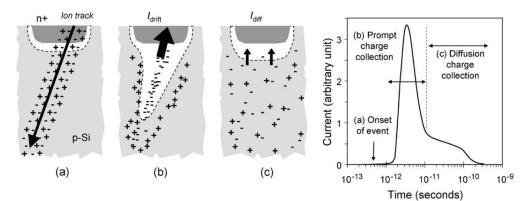

The collision of a sub-atomic particle induces a single event transient (SET) by generating secondary particles capable of ionizing the n-p junctions of sensitive transistors causing a voltage charge or discharge in the stroke node. Modern and smaller technology can also suffer from multiple event transients (MET) as the same particle induces a charge in several neighboring transistors. For simplicity's sake, this subsection focuses on single event effects. Figure 2.1 (a-c) shows a high-energy ion path through a reverse-biased junction, i.e., the most charge-sensitive circuit node (BAUMANN, 2005; LI et al., 2016). The Figure 2.1a displays the corresponding current pulse resulting from the following three phases:

Figure 2.1: Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a high-energy ion.

Source: Baumann, R.C., figure adapted from (BAUMANN, 2005).

- (i) The high-energy particle interaction with the silicon transfers kinetic energy to the semiconductor material creating a track of electron-hole pairs and forming a conical high carrier concentration in the wake of the energetic ion's passage (Figure 2.1a).

- (ii) The electric field in the depletion region collects the closest charge carriers creating a transient current/voltage at the target device node (Figure 2.1b). During this phenomenon, a temporary channel may be formed for a short period, around few picoseconds.

- (iii) A nanosecond later the diffusion begins to dominate the collection process Figure 2.1c, inducing additional current formation.

The radiation event deposits a certain amount of charge  $(Q_{all})$  due to the holepair formation (IBE et al., 2010; HUBERT; ARTOLA, 2013). The collection mechanism described above has a maximum efficiency coefficient  $(L_{max})$  and depends on the ion track length  $(x_c)$ . For instance, the total amount of collected charge by a SRAM is giving by Equation (2.1) (IBE et al., 2010):

$$Q_{collected} = Q_{all} \left(\frac{x_c}{L_{max}}\right) \tag{2.1}$$

$Q_{collected}$  values range from one to several hundred pC, and the precise  $Q_{collected}$  estimation involves the ion strike angle, path, energy, mass, and point of impact considering the nearest reverse-biased junction. The device geometry and electrical characteristics have additional influence on the collection process. The displacement of charge carriers

in the time creates an electrical current in the target devices modeled by Equation (2.2):

$$I(t) = \frac{Q_{collected}}{\tau_{\alpha} - \tau_{\beta}} \left( e^{-\frac{t}{\tau_{\alpha}}} - e^{-\frac{t}{\tau_{\beta}}} \right)$$

(2.2)

$\tau_{\alpha}$  and  $\tau_{\beta}$  are process dependent constants denoting the collection time and iontrack establishment time. The literature reports a typical value of 164 ps for the  $\tau_{\alpha}$  and 50 ps for the  $\tau_{\beta}$  (PALAU et al., 2001; LI et al., 2016). The charge collection in the stroke node may lead to a single event upset (SEU), in other words, introducing an incorrect bit in the memory cell. The quantity of  $Q_{collected}$  required to create an SEU in a device is denoted by the critical charge ( $Q_{critical}$ ) and expressed by:

$$Q_{critical} = \int_0^{T_F} I_D(t) \,\mathrm{d}t \tag{2.3}$$

In the Equation (2.3),  $I_D(t)$  represents the time-dependent drain transient current, and (PALAU et al., 2001) defines the flipping time ( $T_F$ ) as the time instant when the struck transistor drain voltage is equal to the gate voltage after the radiation event. In simple circuits such as DRAMs, an error only occurs whenever the  $Q_{critical}$  is greater than  $Q_{collected}$ masking otherwise the radiation event. The SRAM feedback loop can restore the original value if the recovery time<sup>2</sup> does not exceed the feedback time<sup>3</sup> (DODD; SEXTON, 1995).

#### 2.2.2 Fault Propagation and Masking

The transient errors create unintentional electrical signals that need to travel through many design abstraction layers from the transistor until reaching the application variables and control flow. Several mechanisms can mask this fault: First, a particle strike needs to generate enough charge collection to create a noticeable electrical signal, which depends on the transistor electrical characteristics. The signal propagation also is attenuated by the circuit resistance (*electrical masking*) The internal logic structure leads to *logical masking* when the fault propagation path is blocked by another dominating data path. The circuit timing requirements (e.g., setup and hold times) constrain all electrical signals, including faults. Whenever the faulty signal violates one delay constraints (i.e., the signal arrives either too early or too late to be captured during the clock edge) results in a *temporal masking*.

<sup>&</sup>lt;sup>2</sup>Time taken for the struck node voltage to return to its pre-strike value.

<sup>&</sup>lt;sup>3</sup>The time taken for the struck node voltage to become latched as incorrect data.

Digital systems present two main circuit components: Combinational (e.g., AND, OR, XOR) and sequential circuits (e.g., SRAM cells, latches, flip-flops). Combinational circuits are regarded as less prone to soft errors due to the above-described masking mechanisms and the absence of feedback loop in the underlying circuit. In turn, the sequential circuits are more vulnerable to radiation events as a single strike has enough energy to reverse the stored data as result of the feedback loop. Also, memory elements are susceptible to bit-flips during extended periods of time when holding data, in contrast, the sequential circuit switches (i.e., changes the value) more often. For example, an SRAM cell may be affected by SEUs during almost the entire clock cycle (SEIFERT, 2010). Also, the clock network under the influence of soft errors results in memory elements incorrect operation.

At *architecture level* (e.g., program counter, pipeline registers, register-file, arithmetic, and logic unit), an erroneous bit can be further masked due to the write and the read operations. For example, a fault present in a register can be overwritten by a write before a read, and thus eliminate the incorrect bit. An error is a fault that propagated inside the application (or OS) before being perceived by the user. At the software level, SEUs are incorrect variable values or wrong control flow executions. An algorithm can overwrite the variable before its value is consumed masking the fault. Even with all those masking processes, the incidence of soft errors is increasing due to the technology susceptibility to radiation events. Well defined metrics and methods are necessary to analyze the impact of transient faults under different conditions considering system architecture, application, and compiler.

## 2.2.3 Soft Error Metrics

This subsection describes some useful soft error metrics: The transient errors occurrence per time are quantified by the *Soft Error Rate* (SER) and measured by the *Failure-In-Time* (FIT) parameter. The FIT is equivalent to the number of failures (i.e., soft errors in this context) in one billion of operation hours (BAUMANN, 2005).

A well-established metric is the architectural vulnerability factor (AVF) (MUKHER-JEE et al., 2003) that estimates a particular bit susceptibility to create a visible error in the application. The architectural bits can be divided into two subgroups: (1) The bits required for an *architecturally correct execution* (ACE) and (2) the un-ACE bits. While an ACE bit propagates faults to the final output, un-ACE bit does not create a visible

error. The used of AVF enables the search for the most vulnerable architectural state bits. The AVF focus on the correct result, and thus bit fault can change the intermediary computations and still have an AVF of 0%. For instance, a transient fault in a branch predictor generates a miss-prediction, which potentially requires the re-execution of some instructions without altering the final application.

The AVF lacks an explicit masking rate model that varies according to the hardware component, which may lead to an over-estimation the number of errors. The register vulnerability factor (RVF) (YAN; ZHANG, 2005) is a metric explicitly used to measure the register file susceptibility to soft errors. The RVF accounts for the vulnerability factor by calculating the intervals between two vulnerable register operations (i.e., write/read and read/read). Write operations mask any fault previously propagated, and thus, the interval between writes is the most vulnerable register operations.

The AVF shows a larger granularity than desired to measure the instructions interaction. To address this issue, (BORODIN; JUURLINK, 2010) create an instruction-based criticality assessment metric called Instruction Vulnerability Factor (IVF). This metric uses distinct fault injection techniques to probe every instruction in the code. Given the involved complexity, complete coverage can be difficult to achieve. Another instructionoriented approach is the Instruction Vulnerability Index (IVI) (REHMAN et al., 2011). Its composition includes the ACE-bits, the area, and specific pipeline components vulnerability. This analytical approach avoids the exhaustive simulation by using a fault probability in each pipeline component. Also, the IVI metric allows the extension to register file IVI by incorporating the vulnerability window of each register in the instruction<sup>4</sup>.

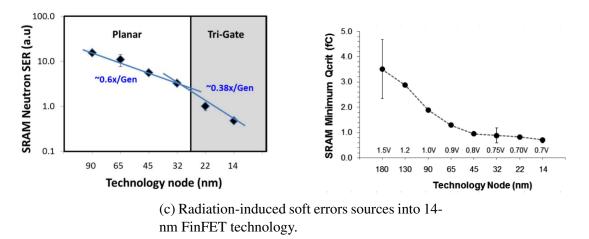

## 2.2.4 Soft Error Trends in Electronic Systems