# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

## **BRUNNO ALVES DE ABREU**

# Exploring Partial Distortion Elimination Techniques in the Sum of Absolute Differences Architecture for HEVC Integer Motion Estimation

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. Sergio Bampi

Coadvisor: Prof. Dr. Mateus Grellert da Silva

#### **CIP — CATALOGING-IN-PUBLICATION**

Abreu, Brunno Alves de

Exploring Partial Distortion Elimination Techniques in the Sum of Absolute Differences Architecture for HEVC Integer Motion Estimation / Brunno Alves de Abreu. – Porto Alegre: PGMI-CRO da UFRGS, 2019.

101 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2019. Advisor: Sergio Bampi; Coadvisor: Mateus Grellert da Silva.

1. High Efficiency Video Coding. 2. Integer Motion Estimation. 3. Sum of Absolute Differences. 4. Partial Distortion Elimination. I. Bampi, Sergio. II. Silva, Mateus Grellert da. III. Título.

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenador do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **AGRADECIMENTOS**

First of all, I would like to thank my parents, Fernando César Ávila de Abreu and Jaqueline Alves de Abreu, for fully supporting me in my choices and giving me advices when needed.

To all my professors, who have made their best to teach me all they could and helped me to find outside sources to learn even more.

To all my classmates, from my undergraduate and post-graduate studies, with whom I have shared the difficulties, stressful and happy moments we all have been through during our graduation years.

To my research colleagues Guilherme Paim, Leandro Rocha, Eduardo Costa, Gustavo Santana, Thomas Fontanari, Vitor Lima, who have helped me, directly or indirectly, in my maturation as a researcher, and also in the completion of this work. To the colleagues from my laboratory who, even though worked on other research topics, were great companies during coffee time.

Special thanks to my advisor Sergio Bampi, and my co-advisor Mateus Grellert, who have dedicated countless hours in helping me with doubts I had, to work with me in many other side projects, and to encourage me when I lacked the motivation.

#### **ABSTRACT**

Digital videos are among the multimedia applications that have been given the most importance in the recent years, leading to the development of better compression techniques at the cost of higher computing requirements. In the most recent video-coding standard, named High Efficiency Video Coding (HEVC), Integer Motion Estimation (IME) is one of the most computing- and memory-intensive steps. IME exploits temporal redundancy by minimizing the rate-distortion cost estimated from two metrics: Sum of Absolute Differences (SAD) and motion vector cost ( $MV_{Cost}$ ). Partial Distortion Elimination (PDE) techniques may be used to optimize the calculation of the SAD unit itself, avoiding the computation of candidates that will certainly not be selected in the IME. This work explores the impact of employing PDE on circuit area and on energy consumption. Differently from related solutions found in the literature, the designed architectures include the  $MV_{Cost}$  in its decision, which enhances the compression efficiency by up to 1.5%. Different designs were also proposed and implemented for the rate-distortion computation unit, in order to discover the best alternative in terms of energy consumption. The architectures were synthesized for ASIC with a 65 nm standard cells library, considering real-input vectors from video sequences to obtain accurate power results. The use of PDE without the  $MV_{Cost}$  achieves an average energy reduction of 16.4% for 1080p and of 11.64% for 2160p sequences when compared to non-PDE implementations. By accumulating the  $MV_{Cost}$  before SAD, approaches using a multiplexer and a Carry-Save Adder (CSA) were analyzed. Compared to the case that accumulates  $MV_{Cost}$  after SAD, average reductions of 17.51% and 5.05% were obtained when using a multiplexer for the HEVC Model (HM) and x265 implementations respectively. The comparisons also showed that using a CSA is the best solution in terms of total energy, with additional reductions of 1.94% (for the HM implementation) and 2.27% (for the x265) when compared to the multiplexer implementation.

**Keywords:** High Efficiency Video Coding. Integer Motion Estimation. Sum of Absolute Differences. Partial Distortion Elimination.

# Explorando Técnicas de Eliminação Parcial de Distorções em Arquiteturas da Soma das Diferenças Absolutas para Estimação de Movimento Inteira no Padrão HEVC

#### **RESUMO**

Vídeos digitais estão entre as aplicações multimídia para as quais têm se dado a maior importância nos últimos anos, levando ao desenvolvimento de melhores técnicas de compressão ao custo de maiores requisitos computacionais. No padrão de codificação de vídeo mais recente, High Efficiency Video Coding (HEVC), a Estimação de Movimento Inteira (IME) é uma das etapas que demandam maior esforço computacional e mais acessos à memória. A IME explora a redundância temporal, minimizando o custo rate-distortion estimado por duas métricas: a Soma das Diferenças Absolutas (SAD) e o custo de vetor de movimento ( $MV_{Cost}$ ). Técnicas de Eliminação de Distorção Parcial (PDE) podem ser usadas para otimizar o cálculo da unidade de SAD, evitando a computação de candidatos que certamente não serão selecionados na IME. Esse trabalho explora o impacto da utilização de PDE na área e no consumo energético do circuito. Diferentemente de soluções relacionadas encontradas na literatura, as arquiteturas desenvolvidas incluem o  $MV_{Cost}$ na decisão, o que melhora a eficiência de compressão em até 1.5%. Diferentes modelos foram propostos e implementados para a unidade que computa o rate-distortion, para determinar a melhor alternativa em termos de consumo energético. As arquiteturas foram sintetizadas para ASIC com uma biblioteca de standard cells de 65 nm, considerando vetores de entradas reais de sequências de vídeos para obter resultados de potência precisos. O uso da PDE sem o  $MV_{Cost}$  atinge uma redução média de energia de 16.4% para sequências 1080p e de 11.64% para sequências 2160p quando comparado a implementações sem PDE. Ao acumular o  $MV_{Cost}$  antes da SAD, propostas utilizando um multiplexador e um Carry-Save Adder (CSA) foram analizadas. Comparado ao caso que acumula o  $MV_{Cost}$ após a SAD, reduções média de 17.51% e 5.05% foram obtidas ao utilizar um multiplexador, considerando as implementações do HEVC Model (HM) e do x265 respectivamente. As comparações também mostraram que utilizar o CSA é a melhor solução em termos de energia total, com reduções adicionais de 1.94% (na implementação do HM) e de 2.27% (no x265) quando comparado com a implementação do multiplexador.

**Palavras-chave:** *High Efficiency Video Coding*, Estimação de Movimento Inteira, Soma das Diferenças Absolutas, Eliminação Parcial de Distorções.

## LIST OF ABBREVIATIONS AND ACRONYMS

ABS Absolute operation

ADC Analog-to-Digital Converter

AMP Asymmetric Motion Partition

AMVP Advanced Motion Vector Prediction

AV1 Alliance for Open Media Video 1

AOMedia Alliance for Open Media

ASIC Application Specific Integrated Circuit

AVC Advanced Video Coding

BD-BR Bjøntegaard Delta Bit-rate

BD-PSNR Bjøntegaard Delta Peak Signal-to-Noise Ratio

BMA Block-Matching Algorithm

CABAC Context-adaptive Binary Arithmetic Coding

CAVLC Context-Adaptive Variable-Length Coding

CBB Candidate Block Buffer

CMOS Complementary Metal Oxide Semiconductor

CSA Carry-Save Adder

CTC Common Test Conditions

CTU Coding Tree Unit

CU Coding Unit

DCT Discrete Cosine Transform

DPB Decoded Picture Buffer

FHD Full High-Definition

FIR Finite impulse response

FiS First Search

FME Fractional Motion Estimation

FPGA Field-Programmable Gate Array

Fps Frames per second

FS Full Search

GPP General Purpose Processor

HD High-Definition

HEVC High Efficiency Video Coding

HM HEVC Test Model

HS Hexagon Search

IME Integer Motion Estimation

IP Internet Protocol

ITU-R International Telecommunication Union Radiocommunication Sector

JCT-VC Joint Collaborative Team on Video Coding

JPEG Joint Photographic Experts Group

JVET Joint Video Experts Team

ME Motion Estimation

MOS Metal Oxide Semiconductor

MSB Most Significant Bit

MSE Mean-Squared Error

MV Motion Vector

$MV_{Cost}$  Motion Vector Cost

MVP Motion Vector Predictor

OBB Original Block Buffer

PCM Pulse Code Modulation

PDE Partial Distortion Elimination

Pixel Picture element

PLE Physical Layout Estimation

PSNR Peak Signal-to-Noise Ratio

PU Prediction Unit

QoS Quality of Service

QP Quantization Parameter

$RD_{Cost}$  Rate-Distortion Cost

RDO Rate-Distortion Optimization

RGB Red, Green, Blue

RMD Rough Mode Decision

RQT Residual Quadtree

RS Raster Search

RTL Register-transfer Level

SAD Sum of Absolute Differences

SATD Sum of Absolute Transformed Differences

SDF Standard Delay Format

SEA Successive Elimination Algorithm

SMP Symmetric Motion Partition

SS Star Search

SSE Sum of Squared Errors

TCF Toggle Count Format

TU Transform Unit

TZS Test Zone Search

UHD Ultra High-Definition

UMH Uneven Multi-Hexagon

UVG Ultra Video Group

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VTM Versatile Video Coding Test Model

VVC Versatile Video Coding

WPP Wavefront Parallel Processing

YCbCr Luminance, Chrominance Blue, Chrominance Red

ZB Zettabyte

# LIST OF FIGURES

| Figure 1.1 Time percentage of each stage in the video encoding process               | 17  |

|--------------------------------------------------------------------------------------|-----|

| Figure 2.1 Simplified scheme of encoding and decoding in video transmission          | 21  |

| Figure 2.2 Fundamental concepts of digital videos.                                   |     |

| Figure 2.3 Hybrid structure used in HEVC                                             |     |

| Figure 2.4 Example of the partitioning scheme in HEVC.                               |     |

| Figure 2.5 Generic search in a previously coded frame.                               |     |

| Figure 2.6 Search shapes for the TZS.                                                |     |

| Figure 2.7 Search shapes for the HS.                                                 |     |

| Figure 2.8 FME fractional pixels window for a 4×4 PU                                 |     |

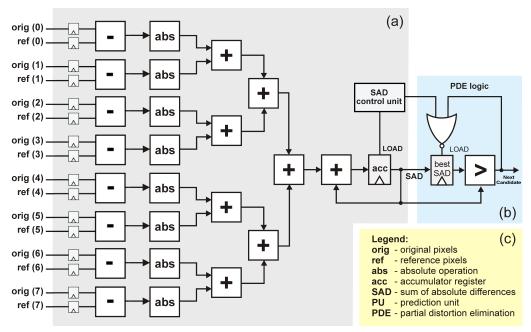

| Figure 2.9 8×8 SAD architecture.                                                     |     |

| Figure 2.10 Short-circuit current for an inverter gate.                              |     |

| Figure 2.11 Sources of leakage currents, in a CMOS inverter gate                     |     |

| Figure 3.1 Vanne et al. proposed 3-stage SAD architecture                            | 50  |

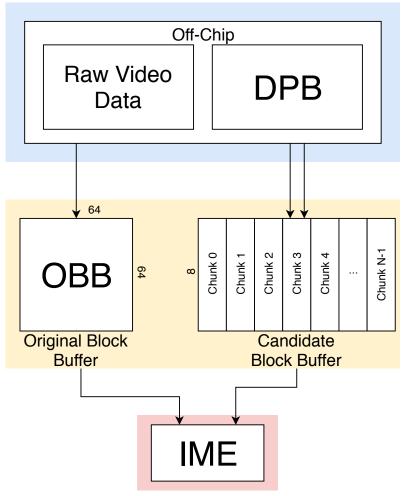

| Figure 4.1 Methodology used to obtain accurate power results for video applications  | s60 |

| Figure 4.2 Generic model of the architectures in this work                           | 63  |

| Figure 5.1 Flow chart of solutions for calculating distortion                        | 66  |

| Figure 5.2 (a) 8×1 SAD Architecture. (b) PDE logic module with an added NOR          |     |

| gate for the best SAD register load operation.                                       | 69  |

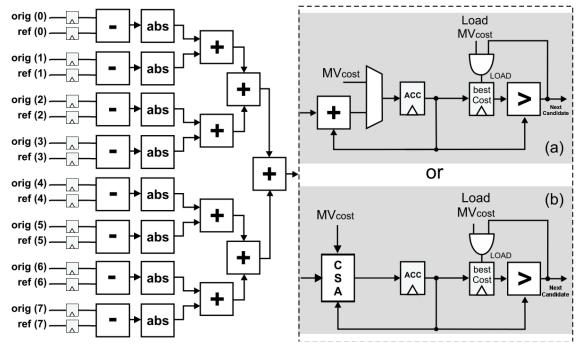

| Figure 5.3 Architectures for the calculation of the total distortion cost, consider- |     |

| ing a $MV_{Cost}$ -aware approach, accumulating $MV_{Cost}$ before SAD with (a) a    |     |

| multiplexer or (b) a Carry-Save Adder                                                | 76  |

| Figure 5.4 Cycles analysis with candidate reordering approach                        | 77  |

| Figure 5.5 Memory model.                                                             |     |

| Figure 5.6 Proposed memory buffer for HS                                             | 80  |

| Figure 5.7 Proposed memory buffer for TZS                                            | 81  |

| Figure 6.1 Throughput analysis performed in (SILVEIRA et al., 2017)                  | 90  |

# LIST OF TABLES

| Table 2.1 Popular display resolutions.                                                        | 20  |

|-----------------------------------------------------------------------------------------------|-----|

| Table 2.2 Partition sizes employed in each prediction stage, for each CU size                 | 27  |

| Table 3.1 Characteristics of Related Works.                                                   | 55  |

| Table 4.1 Video sequences considered in the analysis                                          | 57  |

| Table 4.2 Chunk model for estimating PDE for SAD                                              | 58  |

| Table 4.3 Number of accumulations required to calculate SAD for every PU parti-               |     |

| tion in HEVC, for an 8×1 SAD architecture.                                                    | 62  |

| Table 5.1 Number of 8×1 SAD calculations for different BMAs (QP=32) and BD-                   |     |

| BR increase of the HS (using TZS as anchor).                                                  | 65  |

| Table 5.2 Example case of comparison between standard and PDE approaches of                   |     |

| $MV_{Cost}$ -Oblivion implementations, for an $8\times8$ PU.                                  | 68  |

| Table 5.3 BD-BR percentages of encoding a video without considering the $MV_{Cost}$           |     |

|                                                                                               | 71  |

| Table 5.4 Example case of comparison between standard and PDE approach of a                   | - 4 |

| $MV_{Cost}$ -Aware implementation, with accumulation after SAD, for an 8×8 PU                 | 74  |

| Table 5.5 Example case of comparison between standard and PDE approach of a                   | 7.5 |

| $MV_{Cost}$ -Aware implementation, with accumulation before SAD, for an 8×8 PU                | /5  |

| Table 6.1 Reordered candidates using the HS BMA                                               | 84  |

| Table 6.2 Number of cycles for the HEVC Hexagon Search algorithm execution                    |     |

| using the baseline SAD and with PDE optimization.                                             | 85  |

| Table 6.3 Number of cycles for the HEVC Hexagon Search algorithm with PDE                     |     |

|                                                                                               | 86  |

| Table 6.4 Cycles requirements of different approaches of including $MV_{Cost}$ , using        |     |

| HM                                                                                            | 87  |

| Table 6.5 Cycles requirements of different approaches of including $MV_{Cost}$ , using        |     |

| x265                                                                                          |     |

| Table 6.6 Configurations used to achieve different SAD computation targets                    | 90  |

| Table 6.7 Power and energy/operation synthesis results for the 8×1 SAD architecture @ 300MHz. | .91 |

| Table 6.8 SAD Average energy results for processing 30 frames of FHD and UHD                  |     |

| video sequences using x265.                                                                   | 92  |

| Table 6.9 Power results and energy reductions of the proposed $MV_{Cost}$ -aware ar-          |     |

| chitectures @ 300 MHz.                                                                        | 93  |

# CONTENTS

| 1 INTRODUCTION                                                 | 14 |

|----------------------------------------------------------------|----|

| 2 BACKGROUND                                                   | 19 |

| 2.1 Fundamentals of Video Coding                               | 19 |

| 2.2 Color Space and Sub-Sampling                               | 20 |

| 2.3 Quality Metrics                                            |    |

| 2.4 Data Redundancies                                          |    |

| 2.5 High Efficiency Video Coding                               | 24 |

| 2.5.1 Intra-frame Prediction                                   |    |

| 2.5.2 Transform and Quantization                               |    |

| 2.5.3 Entropy Coding                                           |    |

| 2.5.4 Encoder implementations                                  |    |

| 2.5.4.1 HEVC Test Model Reference Software                     |    |

| 2.5.4.2 Efficient implementations of the software encoder      |    |

| 2.6 Emerging Video Codecs                                      |    |

| 2.7 Inter-frame prediction                                     |    |

| 2.7.1 Integer Motion Estimation                                |    |

| 2.7.1.1 Full Search                                            |    |

| 2.7.1.2 Test Zone Search.                                      |    |

| 2.7.1.3 Hexagon Search                                         |    |

| 2.7.1.4 Alternative BMAs                                       |    |

| 2.7.2 Fractional Motion Estimation                             |    |

| 2.7.3 Metrics for Block Similarity                             |    |

| 2.7.3.1 Sum of Absolute Differences.                           |    |

| 2.7.3.1 Sum of Absolute Differences                            |    |

| 2.7.3.3 Sum of Squared Errors                                  |    |

| 2.7.4 Motion Vector Cost                                       |    |

| 2.8 Partial Distortion Elimination in SAD                      |    |

| 2.9 Power Dissipation in CMOS Circuits                         |    |

|                                                                |    |

| 2.9.1 Dynamic Power                                            |    |

| 2.9.1.1 Switching Power                                        |    |

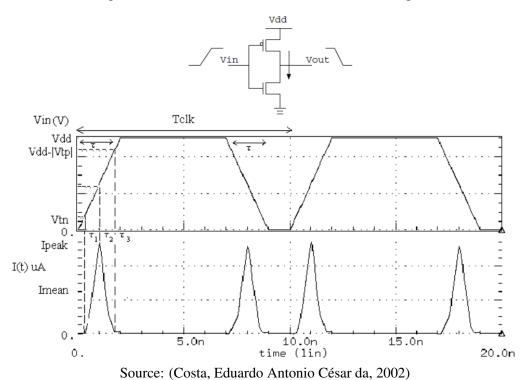

| 2.9.1.2 Short-Circuit Power                                    |    |

| 2.9.2 Static Power                                             |    |

| 2.9.3 Total Power                                              |    |

| 3 RELATED WORKS                                                |    |

| 3.1 SAD and SATD works                                         |    |

| 3.2 IME/ME works                                               |    |

| 3.3 PDE Works                                                  |    |

| 3.4 Literature Summary                                         |    |

| 4 METHODOLOGY                                                  |    |

| 4.1 BD-BR analysis implementations using the software encoders |    |

| 4.2 Cycles count                                               |    |

| 4.3 Power Estimation Methodology for ASIC Design Flow          |    |

| 4.4 SAD Input Vector Acquisition                               |    |

| 4.5 Description of the Architectures                           |    |

| 5 ANALYSIS AND ARCHITECTURE DESIGN                             |    |

| 5.1 Choice of Block-Matching Algorithm                         |    |

| 5.2 Partial Distortion Elimination Proposals                   |    |

| 5.2.1 $MV_{Cost}$ -Oblivious Implementation                    | 67 |

| 5.2.2 Compression impacts of disregarding $MV_{Cost}$ in the total distortion cost | .70 |

|------------------------------------------------------------------------------------|-----|

| 5.2.3 $MV_{Cost}$ -Aware Implementation                                            | .72 |

| 5.2.3.1 $MV_{Cost}$ accumulation after SAD                                         | .72 |

| 5.2.3.2 <i>MV<sub>Cost</sub></i> accumulation before SAD                           |     |

| 5.3 Candidate Reordering                                                           | .76 |

| 5.4 Memory Organization                                                            | .77 |

| 6 RESULTS AND DISCUSSIONS                                                          | .83 |

| 6.1 PDE Cycles Results                                                             | .83 |

| 6.1.1 $MV_{Cost}$ -oblivious                                                       |     |

| $6.1.2~MV_{Cost}$ -aware                                                           | .87 |

| 6.2 Determination of the target frequency                                          | .88 |

| 6.3 Power and Energy Results                                                       |     |

| 6.3.1 $MV_{Cost}$ -oblivious                                                       | .91 |

| $6.3.2~MV_{Cost}$ -aware                                                           |     |

| 7 CONCLUSION                                                                       |     |

| REFERENCES                                                                         | .96 |

#### 1 INTRODUCTION

The recent advances in semiconductor technology have allowed for the evolution of several different applications. These improvements were accompanied and enabled an increase of the demand for more sophisticated services. Multimedia applications are among the main categories that have evolved in the latest years and, within that range, digital videos have received remarkable importance, as it can be seen from the increased resolutions that have been hitting the market. In addition to that, real-time video content has become more popularized, such as video broadcasting, like Twitch or Youtube. Such services need to work as smoothly as possible to fulfill the Quality of Service (QoS) demands. These increases are further supported by recent (as of February 2019) Cisco market research results (CISCO, 2019), some of which predict that video traffic will represent 82% of all IP traffic by 2022, a 7% increase of what was observed in 2017 (75%). This is aggravated by the fact that the annual IP traffic will likely increase and reach 4.8 ZB (Zettabytes) per year by 2022 – this value was around 1.5 ZB in 2017. Therefore, there is an urgent need for optimizing video applications, in order to alleviate the effects of their growth.

This issue becomes even more significant when we consider embedded devices, e.g. smartphones, tablets, camcorders. Dealing with video applications in systems that depend on limited battery resources is a challenging task, mainly because of the increased requirements of such services, which implies more energy consumption. Moreover, the same predictions from Cisco (CISCO, 2019) indicate that smartphone traffic will exceed PC traffic by 2022: the former will account for 41% of the total IP traffic, while the latter will represent only 19%. More generally speaking, wireless and mobile devices will account for 71% of the total IP traffic by 2022. Therefore, with ever-increasing resolutions in video applications and the increasing share they will represent in the near future, embedded systems will tend to have a smaller battery life. Thus, taking power dissipation and energy into account when developing video applications is of utmost importance to overcome such issues.

Handling digital videos in their uncompressed form requires a huge amount of resources, whether to store or transmit them, becoming prohibitive when dealing with high resolution videos. The storage and transmission requirements, in bytes and  $\frac{bytes}{s}$ , respectively, of uncoded videos, are given by equations 1.1 and 1.2, where W and H respectively denote the width and height of the video sequence, N refers to the represen-

tation, in bytes, of each pixel, F refers to the frame-rate – in frames per second (fps) –, and t denotes the time duration of the sequence, in seconds.

$$Size = W \cdot H \cdot N \cdot F \cdot t$$

[bytes] (1.1)

$$BitRate = \frac{Size}{t}$$

[\frac{bytes}{s}] (1.2)

As a concrete example, we can consider the Ultra High-Definition 4K (UHD 4K) (3840×2160 pixels) video sequence – which is a resolution that is becoming increasingly popular –, recorded at a frame-rate of 30 frames per second (fps), with each of its pixels being represented by 3 bytes (to form the three color channels). A 10-minute video with these specifications would require more than 410 GB to be stored. In order to transmit this video for real-time streaming or broadcasting applications, we would require a bit-rate of more than 710 MB/s. These values become even higher when considering that the International Telecommunication Union Radiocommunication Sector (ITU-R) recommendation for UHD Television (UHDTV) states that resolutions should be increased in both spatial and temporal axes (ITU-R, 2015). Hence, higher frame rates, such as 120 fps, which would quadruplicate the results of the previous example, have to be supported. Thus, due to the prohibitive values of dealing with uncompressed videos, there is an evident need for video compression, in order to alleviate these huge requirements.

Video compression is based on finding redundant information, through several methods, in video frames, and then suppressing most of these redundancies to minimize the number of bits required to represent a video sequence. The main goal of video compression is to make the required storage size and transmission rates more feasible.

However, finding redundant information and taking significant advantage of them is a costly task that demands a significant amount of computational resources. This occurs because modern video encoders perform numerous time-consuming and computing-demanding operations to efficiently compress data, which increases the time and energy required. Aggravated by the increasing demands for higher resolutions and frame-rates, video compression has been receiving major attention in academic and industrial studies.

High Efficiency Video Coding (HEVC) (ITU-T, 2013) is a video coding standard developed by the Joint Collaborative Team on Video Coding (JCT-VC), as a solution for the increasing demands for higher resolution videos. HEVC is the sucessor of the H.264/AVC (Advanced Video Coding) (ITU-T, 2003), and its goal is to double the

compression efficiency, for the same video quality, when compared to its predecessor (SULLIVAN et al., 2012). In practice, however, HEVC manages to achieve an average compression of 39.3% when compared to H.264/AVC (GROIS et al., 2013). These advances became possible due to more well-structured and flexible block partitioning (KIM et al., 2012), complex algorithms, advanced motion vector predictions, and the support for larger block sizes.

The improvements achieved by these new proposals also led to an increase in the computational effort of HEVC: encoders compliant with this standard are 1.2 - 3.2× more complex when compared to H.264/AVC-compliant encoders (GRELLERT; BAMPI; ZATT, 2016). Thus, although it compresses videos better than H.264/AVC, HEVC has brought an additional issue, especially for embedded devices, due to the higher energy requirements to encode videos in this standard.

The increased effort required to compress videos represents an additional matter to be considered when dealing with the embedded devices, such as the ones previously cited. The limited battery life demands the encoding task to be executed in the most efficient manner. Processor manufacturers, such as Qualcomm, have recently realized that using simple general purpose processors (GPPs) for video applications would not be efficient to tackle these processing requirements (QUALCOMM, 2014). Therefore, there has been a growing tendency for using dedicated hardware architectures for video compression.

Along with other techniques, such as clock and data gating, designing dedicated architectures is one of the main strategies to mitigate power, energy and timing issues, as they are optimally designed solely for specific applications. Application Specific Integrated Circuits (ASICs) and Field-Programmable Gate Arrays (FPGAs) are two platforms for implementing dedicated architectures. ASICs are designed for specific domains, and represent the class of circuits that contrast the most from software solutions running on GPPs. The use of FPGAs may represent a good balance standing between the spectre of GPPs and ASICs. However, when energy-efficiency is the main design restriction to take into account, designing architectures in ASICs for dedicated execution of certain key compute-intensive algorithms is still the best approach (SCHMITZ; AL-HASHIMI; ELES, 2004).

Motion Estimation (ME) is the most costly step of the HEVC standard, in terms of time. This step is responsible for finding temporal redundancies in video sequences, in order to decrease the bitstream size at the output of the encoder. To take advantage of

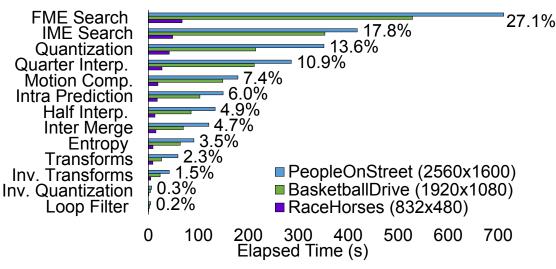

most of these redundancies, ME has to be executed several times for each frame in the video sequence. ME is split into two different stages: Integer ME (IME) and Fractional ME (FME). Figure 1.1 shows an analysis for different video sequences performed in (GRELLERT; BAMPI; ZATT, 2016), using the reference software for HEVC – HEVC Test Model (HM) (MCCANN et al., 2013) –, showing that IME and FME are responsible for a large portion of the execution time in the encoding process for the HEVC standard. Considering the ME includes the process of IME, FME, Half and Quarter Interpolations, this analysis shows that it represents about 60.1% of the total encoding process. This value is further validated by (BOSSEN et al., 2012), which also presents a value close to 60% for the ME process.

Figure 1.1: Time percentage of each stage in the video encoding process.

Source: (GRELLERT; BAMPI; ZATT, 2016)

The ME stage also represents a bottleneck in terms of power. According to (BA-HARI; ARSLAN; ERDOGAN, 2009), about 77% of the total power was consumed by the ME module of the video encoder analyzed in their study.

In the IME stage, the first step of ME, the encoder attempts to find temporal redundancies by measuring similarity between the block being encoded (original) and blocks (candidates) from previously encoded frames. This similarity is usually measured by using the Sum of Absolute Differences (SAD) metric, along with the Motion Vector Cost  $(MV_{Cost})$  – the cost, in bits, of the current motion vector pointing to the candidate block.

Some techniques are used to decrease the number of cycles required in the SAD calculation, such as the Partial Distortion Elimination (PDE) (CHOI; JEONG, 2009; SEI-DEL; BRäSCHER; GüNTZEL, 2015). This technique consists in an early-termination of the SAD calculation, which eliminates cycles of useless candidates in the IME step. How-

ever, related works found in the literature mostly consider algorithms that are unfeasible to work in real encoders. Also, works regarding this technique do not take the  $MV_{Cost}$  into account, which leads to compression efficiency degradation and reduced optimization results with respect to the reference HEVC implementation.

Considering the aforementioned issues and the additional ones brought by HEVC, the proposal of this M.Sc. Dissertation is to make a deep analysis in the possible ways to employ PDE techniques along with the  $MV_{Cost}$ , mainly by initializing the SAD value with the  $MV_{Cost}$  to decrease the cycles requirements even more than conventional PDE usage. Additionally, by using  $MV_{Cost}$ , improved compression efficiency results were obtained, which are also presented in this Dissertation.

The main contributions of this work are the following:

- Comparison, in terms of SAD calls and BD-BR, between two important Block Matching Algorithms (BMA) from HEVC-compliant encoders: Test Zone Search (TZS) and Hexagon Search (HS);

- Use of the standard PDE technique in the state-of-the-art HEVC standard and analysis of its impact in 1080p and 2160p video sequences;

- Analysis of the use of PDE along with the  $MV_{Cost}$  leading to more precise results;

- Compression efficiency results regarding the use of the  $MV_{Cost}$  in the total cost of a block when compared to the cost using only SAD, for HEVC encoders;

- New technique that improves the PDE by including the  $MV_{Cost}$ , considering IME algorithms in HEVC standard;

- Two different ways of including the  $MV_{Cost}$  in the SAD architecture along with an adder tree using a Carry-Save Adder (CSA), and independently, with a multiplexer.

This document is structured as follows: Chapter 2 presents a detailed background on the main concepts regarding video coding, quality metrics, power dissipation and more; Chapter 3 details some related works found in the literature that address similar topics regarding SAD, ME and PDE implementations; Chapter 4 presents the methodology used, describing the tools and methods employed for obtaining the reported results; Chapter 5 presents all the PDE analyses proposed in this work, a candidate reordering and the memory design; Chapter 6 presents the cycles, power and energy results, describing and justifying them; and Chapter 7 concludes the report, by summarizing the contributions of the work, and highlighting possible future paths for further research on this topic.

#### 2 BACKGROUND

In order to understand the technical details of the remaining chapters, the introduction of some of the basic related concepts is essential. This chapter details the topics related to the scope of this work, including terms related to video coding, motion estimation, sum of absolute differences, power dissipation and more.

## 2.1 Fundamentals of Video Coding

The entire digital video process begins when a real-life scene is obtained by a capturing device, e.g. digital video camera, camcorder, etc, through the use of image sensors. These sensors collect light photons, producing an electrical charge – proportional to the number of photons collected – that will further be converted to digital signals by using an analog-to-digital converter (ADC) and produce images (RICHARDSON, 2003). Digital videos are a set of digital images captured sequentially with a high degree of temporal proximity, taking advantage of the limitations of the human vision, which will interpret sequential images as real moving scenes. Each image that composes a digital video is denoted as a frame.

More specifically, a digital image is represented by a rectangular matrix of color elements. This matrix is mapped to an exhibition device, in which each of its elements represents a brightness or color information of a small region of the exhibition device. Each of these small regions is referred to as a picture element (pixel).

Usually, digital videos need to be encoded in a minimum frame-rate to optimize user experience, high enough for the human brain not to perceive the video as individual images. Frame-rate is usually represented in frames per second (fps). Typical values are 30, 60 and 120 fps, the last of which is usually employed in 4K video sequences (ITU-R, 2015).

Several different display resolutions are considered in this work. These resolutions define the number of pixels in each dimension, and they are defined in a width×height form. Table 2.1 presents a set of possible display resolutions and their respective notations employed in this work, for clarification purposes.

A digital video is in its raw form when it is first produced. Due to the fact that working with raw videos is an unfeasible task, as already mentioned, video coding techniques must be applied, which entails the operation of a video encoder and a decoder. The

Table 2.1: Popular display resolutions.

| Width × Height     | Notation |

|--------------------|----------|

| 416×240            | 240p     |

| $832 \times 480$   | 480p     |

| $1280 \times 720$  | 720p     |

| $1920 \times 1080$ | 1080p    |

| 3840×2160          | 2160p    |

Source: The Author.

video encoder is responsible for applying compression techniques and transforming a raw video in a sequence of bits – referred to as a video bitstream – according to a specific video standard. Then, the video is combined with other syntax elements at the network layers, to be further sent by a transmitter. That way, generally speaking, a station can receive the data, extract the encoded video bitstream from the network layers and process this bitstream with a decoder that must support the same standard for which the bitstream was generated. This process regenerates the video, which can be displayed or stored for future uses. This process is illustrated in Figure 2.1.

The video coding standard defines only the specifications for which the decoder has to comply. Hence, the encoder can be freely implemented in different ways, by applying different algorithms and in varied hardware platforms, as long as the output bitstream generated by the encoder complies to the standard. In other words, the encoded video bitstream must be able to be processed by any standard-compliant decoder.

## 2.2 Color Space and Sub-Sampling

Every pixel on a digital video frame can be represented by three color components. A common color space to represent digital images is RGB (Red, Green, Blue). RGB employs three different matrices to represent the three colors, whose choice is based on the three primary colors detected by the human visual system.

A common color space used in video coding, however, is the YCbCr. This color space is split into Y, which is the luminance (luma) component, and two chrominance (chroma) components Cb and Cr, which denote, respectively, the blue component relative to the green component, and the red component relative to the green component. YCbCr is more suitable for video compression due to the fact that the chroma information is totally separated from the luma component. This allows for distinct compression techniques to

Encoder HD

Source: The Author

Figure 2.1: Simplified scheme of encoding and decoding in video transmission.

be applied for each of them separately (DINIZ, 2009).

This distinction in compression techniques is important given that the human eye is more sensitive to the luma component than to chroma. Therefore, slightly decreasing the representation of the chroma matrix, for example, would decrease the total size of a video without majorly impacting the image visually. This is denoted as color subsampling. Among the several color sub-sampling possibilities, a few of them stand out. 4:2:0 is the most employed one for video compression using the HEVC standard, which consists of using one Cb and one Cr sample for each set of four Luma samples, which, in other words, means that there is an horizontal and vertical sub-sampling in both the Cb and Cr components. 4:2:2 is another possibility to be used, which refers to a subsampling in the vertical axis only. Lastly, 4:4:4 refers to no sub-sampling being employed (RICHARDSON, 2003).

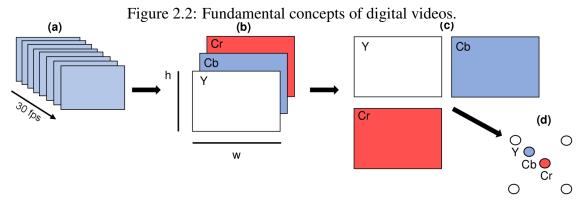

Some of the concepts presented so far are shown in Figure 2.2, in which the concepts of temporal resolution (for a 30 fps video sequence) (a), spatial resolution (b), color space (c) – considering the aforementioned YCbCr color space – and color sub-sampling

(d) are illustrated.

Source: Adapted from (BUBOLZ, 2018)

# 2.3 Quality Metrics

Defining the quality of a video is a rather complex task. Many existing metrics attempt to objectively measure video quality, given that most subjective criteria are hard to measure. The most straightforward objective way is by comparing the pixels of the original frame with the generated pixels after the decoding process, which is mostly useful for determining the fidelity of the reconstruction of an image. The most accepted metric, however, is the Peak Signal-to-Noise Ratio (PSNR) (GHANBARI, 2003). The equation for calculating PSNR is shown in 2.1.

$$PSNR_{dB} = 20 \cdot \log_{10} \left( \frac{MAX}{\sqrt{MSE}} \right) \tag{2.1}$$

In Equation 2.1, MAX denotes the maximum representation value of a sample, which equals  $2^N - 1$ , where N is the number of bits required to represent one sample. MSE refers to the Mean-Squared Error, defined in Equation 2.2, where m and n are the number of pixels in the vertical and horizontal directions of the frame, respectively, and  $O_{i,j}$  and  $R_{i,j}$  denote the positions within the original and reconstructed frames.

$$MSE = \frac{1}{m \cdot n} \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} (O_{i,j} - R_{i,j})^2$$

(2.2)

Based on the PSNR and on the bit-rate value of an encoded video, Gisle Bjønte-gaard (BJONTEGAARD, 2001) proposed a model to measure coding efficiency between two different video compressors (encoders). This proposal was based on approximating a rate-distortion (R-D) curve given by the set of bit-rate and PSNR values, from which

a third order logarithmic polynomial fitting has been proposed. This principle generated two metrics: Bjøntegaard delta bit-rate (BD-BR) and Bjøntegaard delta PSNR (BD-PSNR) – both of which are widely used for comparing two models. BD-BR represents an average bit rate difference, measured in %, over the range of four different PSNR values, in a BR vs. PSNR curve. BD-PSNR is the reverse, and denotes the average PSNR difference, measured in %, over the range of four different bit-rate values, in a PSNR vs. BR curve.

#### 2.4 Data Redundancies

Video coding is mainly based on reducing the amount of redundant data in video sequences. In other words, data that are not relevant for the video representation are discarded. Data compression algorithms focus on finding these redundancies, which appear from correlations or repetitions in the video sequence, and exploit them. The four redundancies explored by video codecs are presented below:

- Spatial Redundancy: this mainly refers to correlations and similarities between neighboring or spatially distributed pixels in the same frame. This redundancy occurs due to the fact that spatially close pixels have a tendency of presenting similar values. This redundancy is mainly tackled in the intra-frame prediction stage of the video encoding process;

- Temporal Redundancy: this is the kind of redundancy that costs the most to be explored in modern encoders. It is based on the fact that objects tend to slightly displace from where they originally were in previous frames of a video sequence. Therefore, it would not be necessary to purely encode an entire block of pixels if there is a block very similar to it in a previously encoded frame. This is targeted by the inter-frame prediction, which is one of the most time-consuming tasks in the encoding process (GONZALEZ; WOODS, 2003; AGOSTINI, 2007; GRELLERT; BAMPI; ZATT, 2016);

- Entropic Redundancy: this redundancy is related to the occurrence probability of the coded symbols. It does not have a direct relation to the video content itself, but with the way data is represented by the standard. This is mainly based on representing the most frequent information of a video sequence by using symbols, generating a smaller number of bits in its respective representation;

• Psychovisual Redundancy: it is responsible for exploiting the human visual system limitations – as stated in Section 2.2 regarding color sub-sampling –, by decreasing the least relevant information of an image (MONTEIRO; SANTOS, 2013).

## 2.5 High Efficiency Video Coding

High Efficiency Video Coding (HEVC) (ITU-T, 2013) is a popular video coding standard, focused on targeting higher resolution videos than its predecessor H.264/AVC (Advanced Video Coding) (ITU-T, 2003). HEVC obtains an average compression efficiency of 39.3% (GROIS et al., 2013), for the same video quality, when compared to H.264/AVC, which became possible due to more complex structures and block partitioning (KIM et al., 2012). As an example of its higher complexity, H.264/AVC works with the concept of macroblocks, whose maximum supported size is 16×16, whereas HEVC supports blocks of up to 64×64. Hence, the compression improvements of HEVC led to an increase of 1.2 - 3.2 × in the computational effort to encode videos, when compared to H.264/AVC (GRELLERT; BAMPI; ZATT, 2016). This complexity growth tends to lead to higher time to encode videos and, therefore, higher energy consumption.

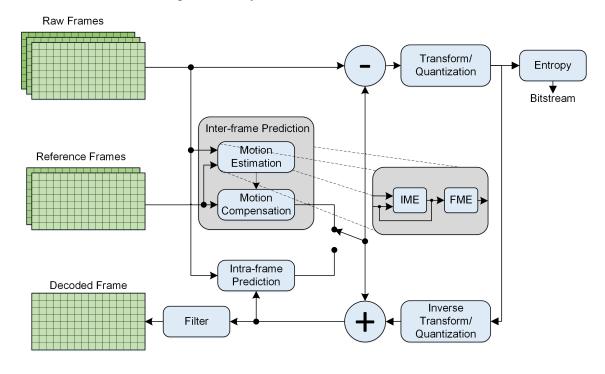

Even though several innovations have been introduced by HEVC, this standard still employs a well-established hybrid structure (HABIBI, 1974; FORCHHEIMER, 1981) in its encoder, which has been used since H.261 (ITU-T, 1993). The hybrid term mainly indicates that the encoder uses several different techniques, such as predictions, transforms, quantization, entropy coding, to encode videos. The encoder has an implementation of the decoder within its own functioning, in order to use the locally decoded frames as reference frames – in the same manner that any other separate and dedicated decoder will eventually proceed. This structure is presented in Figure 2.3.

The process starts by splitting each frame of the video sequence to be encoded in blocks called Coding Tree Units (CTUs). The CTU size is fixed for the whole encoding process, and HEVC-compliant encoders usually define this size as  $64 \times 64$ . Each CTU of the frame to be encoded is applied in the stages of the presented hybrid diagram from Figure 2.3.

The blocks are used as input for the inter and intra-frame prediction stages, in order to exploit temporal and spatial redundancies. Based on decisions from the encoder – by choosing between intra or inter-prediction – the encoder generates a predicted block, which is subtracted from the CTU, producing a residual block. The residue serves as an

Figure 2.3: Hybrid structure used in HEVC.

Source: The Author

input for the transform and quantization stages, which discards the most irrelevant information for our visual system. The quantization stage is usually the step that introduces losses to the encoder. The quantized output is sent to the entropy stage, which applies statistical algorithms to generate the output bitstream, to either store or transmit it. The encoded block also needs to be decoded in the encoding scheme – hence the "hybrid" terminology – by applying inverse quantization and inverse transform functions in the encoder, so that the encoded frame can be recovered and stored to be used as reference frame for encoding other frames. These inverse operations are needed because some predictions use information of previously coded frames to find the redundancies in the current frames, so the previously encoded frames need to be ready to be analyzed.

The HEVC standard supports complex data structures apart from CTUs. Each CTU can be encoded in several distinct ways by splitting it into smaller squared blocks, denoted as Coding Units (CUs) in a quad-tree partitioning scheme, and their final partitioning is decided by the use of Rate-Distortion Optimization (RDO), which defines a metric, namely Rate-Distortion Cost  $(RD_{Cost})$ , given by Equation 2.3. In this formula, Distortion refers to a similarity metric (which will be explained later in Section 2.7.3;  $\lambda_{mode}$  and  $R_{mode}$  refer to the Lagrange multiplier and the cost in bits of the specific mode being used, respectively (GRELLERT, 2018). It should be noted that, in order to determine the number of bits and obtain  $R_{mode}$ , it is necessary to go through the stages of

transform, quantization and entropy (GRELLERT, 2018).

$$RD_{Cost} = Distortion + \lambda_{mode} \cdot R_{mode}$$

(2.3)

HEVC supports CU sizes of 8×8, 16×16, 32×32 and 64×64. When applying the prediction modes, CUs are further split into Prediction Units (PUs). This gives more flexibility to an encoder, given that objects in a CU may be having different behaviors close to each other, so applying different partitioning schemes and different prediction choices may lead to better results overall. The PUs can be categorized into Symmetric Motion Partitions (SMPs) and Asymmetric Motion Partitions (AMPs), each of which has four possible partitioning schemes. Figure 2.4 shows an example of a CTU being split to the PU level, highlighting the SMP and AMP PU types for a 32×32 CU size.

CTU CU 64 32 PU Inter-frame **SMPs** Prediction 16x32 16x16 32x16 32x32 Intra-frame **AMPs** Prediction 32x8/32x24 32x8/32x24 8x32/24x32 8x32/24x32

Figure 2.4: Example of the partitioning scheme in HEVC.

Source: The Author

The number of PU partitions available for a CU depends on its size and the prediction mode. Table 2.2 shows the partitions for each inter and intra-prediction stages of

HEVC, referring to D when the partition is disabled and E when it is enabled.

Mode CU  $2N \times 2N$  $2N \times N$  $N \times 2N$  $N \times N$  $2N \times nU$  $2N \times nD$  $nL \times 2N$  $nR \times 2N$ 64×64 Е D D  $D^*$ D D D D  $32\times32$ E  $D^*$ D D D D D D Intra 16×16 Ε D  $D^*$ D D D D D  $8 \times 8$ E D D Ε D D D D Ε  $64 \times 64$ Ε Ε Е D\* Ε Ε E  $D^*$ Ε  $32\times32$ Ε Ε Ε Ε Ε Ε Inter Ε Ε Е Ε 16×16 Ε  $D^*$ Ε E Ε  $8 \times 8$ Ε Ε D D D D D

Table 2.2: Partition sizes employed in each prediction stage, for each CU size.

Source: The Author, adapted from (SILVA, 2014)

In Table 2.2, 2N refers to the CU dimension – hence, N equals half of it. For example, the N×2N PU of a  $16\times16$  CU refers to the  $8\times16$  PU. It should also be noted that N×N is disabled for  $8\times8$  CUs. The reason to that decision, according to (MCCANN et al., 2013), is to reduce bandwidth requirements.

Despite splitting CUs into PUs, the encoder also divides them into Transform Units (TUs), for transform and quantization steps to be applied to the residual block. The different partitions are evaluated so that the encoder can choose which partitioning models achieve a final smaller video bitstream with the smallest quality degradation possible. Ideally, encoders would need to apply intra and inter-frame partitioning algorithms for every possible PU partition in every CU, and test all possible TUs for each of these combinations. Nevertheless, the intense memory accesses and the demanding required computation – which increase the encoding time and energy spent per frame to be encoded – usually lead to encoders employing heuristics for some of the partitions not to be evaluated in some iterations, while obtaining acceptable compression results. These heuristic decisions are left to the encoder developer, to determine whether the PU will be using an intra or an inter-frame partition, and of which type and size of CTU, CUs, PUs and TUs partitions will be employed.

The following subsections briefly describe the intra-prediction, transform, quantization and entropy stages of the HEVC encoding process. The inter-prediction process is described in a subsection of its own, given that this is the main focus of this work.

<sup>\*</sup> Enabled if minimum CU size is greater than 8×8

#### 2.5.1 Intra-frame Prediction

The intra-frame prediction stage of HEVC is responsible for finding spatial redundancies in the encoding process. The sizes supported for this stage were presented in Table 2.2.

Given that it focuses on redundancies occurring spatially, i.e., in neighboring patterns of the same frame, the intra-prediction uses a rationale similar to image compressing algorithms, such as the ones used by the Joint Photographic Experts Group (JPEG) (PENNEBAKER; MITCHELL, 1992).

In HEVC, there are 35 different intra-prediction methods, 33 of which are denoted as directional modes, being mostly useful for repeating patterns on frames, like straight or diagonal lines. Another mode available is the DC, which is based on repeating the average of the samples in the whole block. The remaining one is the planar mode, which is based on repeating information from more than one border.

The HEVC standard defines that not every PU size should evaluate every possible intra-prediction mode, due to the increased amount of computations that would be required. Therefore, the standard defines that only a subset of modes will be evaluated for each PU size, accordingly. This is performed by a heuristical algorithm denoted as Rough Mode Decision (RMD) (SILVA, 2014).

## 2.5.2 Transform and Quantization

Transform and quantization stages are the two processes that manipulate the residual block produced by the prediction modes.

The transform stage is responsible for translating the blocks to the frequency domain, so that more efficient quantization can be performed. Encoders mostly employ the Discrete Cosine Transform (DCT) on this step. Additionally, transforms can be applied to a variety of block sizes, which are equivalent to the TUs previously mentioned. A Residual Quadtree (RQT) partitioning scheme is employed for each CU in the CTU quadtree, generating TUs which can range from  $4\times4$  to  $32\times32$ .

The quantization process is applied right after the transform stage, and introduces losses to the encoder by discarding frequencies not so relevant to the human vision. The frequency range to be discarded is proportional to a parameter called Quantization Parameter (QP). A higher QP implies that more frequencies will be discarded, hence quality

losses and compression gains will occur. Analyses for HEVC standard are usually run with QPs 22, 27, 32 and 37, as stated by the Common Test Conditions (CTC) (SHAR-MAN; SUEHRING, 2018). The runs with these 4 QPs generate the four points required by the BD-BR and BD-PSNR metrics.

In addition to the transform and quantization stages which will generate blocks for the entropy stage, the encoder also performs inverse quantization and inverse transform stages, to retrieve the original encoded block. These stages are simply inverted versions of the transform and quantization stages previously described.

## 2.5.3 Entropy Coding

This stage is responsible for properly generating the compressed bitstream to the output of the encoder. This process takes advantage of statistical redundancies – the probability of occurrence of symbols –, applying data compression techniques.

HEVC applies a compression technique denoted as Context-Adaptive Binary Arithmetic Coding (CABAC). This algorithm was also used in H.264/AVC, but not every profile of the previous standard supported it, given that it required more processing. In simpler profiles of H.264/AVC, Context-Adaptive Variable-Length Coding (CAVLC) was employed instead.

## 2.5.4 Encoder implementations

This section briefly describes some encoder implementations of the HEVC standard, mainly focusing on HEVC Test Model (HM) (MCCANN et al., 2013) and x265 (MULTICOREWARE, 2019a). There are other alternative implementations available on the Internet, some of which are briefly described in this section; however, the literature mostly utilizes these two for analyses and comparisons. Some emerging encoders apart from HEVC are described in Section 2.6.

#### 2.5.4.1 HEVC Test Model Reference Software

The Joint Collaborative Team on Video Coding (JCT-VC) maintains a reference HEVC software – HEVC Test Model (HM) (MCCANN et al., 2013) – to be used for research analysis, which contains the main stages presented in the hybrid structure from

Figure 2.3. The software is written in C++ programming language.

The main goal of HM is to provide a basis upon which experiments can be conducted, by making it easier to verify the coding performance of algorithms and proposals. HM is not meant to be a fast or efficient implementation, but it is the most recommended environment for experiments to be performed.

HM has an extensive documentation on every supported parameter, each of which can be manipulated for analysis. The implementation includes the encoder and the decoder, both compliant to the HEVC standard. As of the time of writing this work, HM is in version 16.20.

#### 2.5.4.2 Efficient implementations of the software encoder

Other implementations of HEVC-compliant encoders can be found, apart from HM. Most of these implementations have faster execution in their default presets when compared to HM.

x265 is an open source project for a fast HEVC encoder, led by MulticoreWare, a provider of video software libraries (MULTICOREWARE, 2019b). The implementation is mainly written in C++ programming language, just as in HM. This is a faster version which uses less partitioning structures and less complex algorithms, in its default preset. Even though the default version is faster than the one in HM, x265 supports the following presets for execution:

- Ultrafast;

- Superfast;

- Veryfast;

- Faster;

- Fast;

- Medium (default);

- Slow:

- Slower;

- Veryslow;

- Placebo.

These high-level presets determine the values of encoding parameters in the x265 software. These encoding parameters include the CTU size, the minimum CU size, faster

modes for inter and intra-prediction, limitations on the number of reference frames to be used, and so on.

x265 supports Wavefront Parallel Processing (WPP) (CHI et al., 2012), which allows for parallel execution of rows of CTUs, without major impacts on the overall quality. Moreover, some parts of its code are written with Assembly instructions, making it even faster and, therefore, convenient, for testing and analyzing. This encoder is considered in some works in the literature, such as (HU et al., 2014; YIN; ZHANG; GAO, 2015; HUANG et al., 2018; LIU; WANG; LI, 2018), due to it being closer to real-time implementations when compared to HM.

HEVC Open Mpeg Encoder (HOMER) (CASAL, 2019) is another alternative for efficient implementations. It is an open-source, real-time and multiplatform video encoder, developed by Juan Casal. The encoder includes every prediction and transform sizes, supports parallelism using WPP and applies every possible intra-frame prediction mode. The encoder does not apply inter-frame prediction for SMPs or AMPs, which reduces encoding complexity. There were no papers found in the literature that present HEVC results using the HOMER encoder.

Kvazaar (VIITANEN et al., 2016a) is an open-source HEVC encoder, developed in C programming language. It is developed by the Ultra Video Group (UVG) (GROUP, 2018). Its main goal is to achieve real-time coding with an efficiency close to HM. Kvazaar is employed in some papers in the literature, such as (VIITANEN et al., 2015; LEMMETTI et al., 2016; VIITANEN et al., 2016b), but none of them focus on PDE solutions, which is the scope of this work.

## 2.6 Emerging Video Codecs

Other standards apart from HEVC can be found. Among the most popular ones is an encoder software from the group Alliance for Open Media (AOMedia), called AOMedia Video 1 (AV1) (RIVAZ; HAUGHTON, 2019), which is an open and royalty-free video coding standard (MEDIA, 2019). Governing members of the AOMedia include Amazon, Apple, ARM, Google, Facebook, and others. However, only HEVC encoders will be employed in this work, given that AV1 is not considered in the related works that have been found. Moreover, primary analyses performed with the encoder indicated that its default implementation was much slower, given its higher focus on achieving an optimal bit-rate, which would make the analysis much more time-consuming.

Lastly, there is another video standard, which is shaping up to be an evolution of HEVC. Versatile Video Coding (VVC) (BROSS; CHEN; LIU, 2018) is a video coding standard recently developed by the Joint Video Experts Team (JVET) in 2018. VVC aims to achieve an average of 50% in the compression efficiency when compared to HEVC, and its innovations tend to bring even more computational effort for VVC-compliant encoders. Even though this standard is still in development, primary implementations – VVC Test Model (VTM) (BROSS; CHEN; LIU, 2018) – have already been released and are constantly being updated. However, this standard was not considered in this work given that the standard and its reference software are still in process of being stabilized, differently from HEVC and HM, which are already well-developed.

# 2.7 Inter-frame prediction

Inter-frame prediction is the stage responsible for exploiting temporal redundancies, as mentioned in Section 2.4. The lack of movement and the high frame-rate values usually favor the inter-frame prediction in achieving good compression results. In HEVC, the inter-prediction determines four modes for a PU to be encoded: inter, SKIP, Merge and Pulse Code Modulation (PCM).

When a PU is set to SKIP mode, the encoder has defined that the best choice is to not send residual information to the next stages of the encoding process. This occurs mainly when no movement has been detected in the block being analyzed. The chosen PUs in this mode are always squared blocks. Given that no residual is sent, this mode results in considerable compression gains (SILVA, 2014).

In the Merge mode, the motion parameters of the current PU being encoded are generated based on the information from neighbors, both spatial and temporal. Therefore, the decoder only needs a flag indicating that the mode is Merge and the PU index, so that its neighbors can be obtained and the block can be generated.

The PCM mode consists in sending the raw pixels of the block – instead of a residual one – to the bitstream, which harms the overall compression of the video. However, even though this is defined in the HEVC standard, this mode is not used in the default preset of both HM and x265.

The inter mode is the main one in the inter-prediction stage. It defines that a search should be performed in possibly more than one reference frame (previously encoded frame) to find a block similar to the one being encoded. The main part of this stage

is the Motion Estimation (ME). In the encoder implementation, the inter-frame prediction performs a loop through the PU partitions and through several reference frames – specified by the encoder implementation – in which the predictions will be performed. The interframe prediction performs two different prediction types, namely uni- and bi-prediction, to both of which the Motion Estimation (ME) is applied.

Motion Estimation (ME) is essentially the stage responsible for resolving the temporal redundancies in a video sequence, when inter mode is applied. ME finds the most similar block compared to the one being encoded. Thus, the information needed to be sent to the output of an encoder is just the difference between both blocks (namely, the block of residuals) and a vector pointing to the best matching block – Motion Vector (MV) – so that the decoder has sufficient information, along with the previously decoded frames, to recover the original block. The ME is split into two subsequent stages: Integer Motion Estimation (IME) and Fractional Motion Estimation (FME). These two modules are explained in a more detailed manner in the following subsections, with a special focus on the IME module, given that this is the main encoding stage which is dealt with in this work.

#### 2.7.1 Integer Motion Estimation

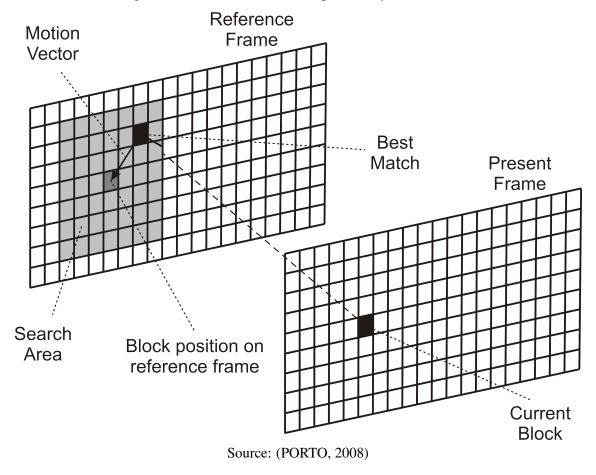

Integer Motion Estimation (IME) is the first step of the ME and finds the best matching block between PUs in two different frames (current and reference), using only integer-pixel displacement vectors to compare blocks, by applying a block-matching algorithm (BMA) to the blocks being encoded in the current frame. This search algorithm defines a pattern of positions – represented by motion vectors with integer-pixel x- and y-components – in which the most similar block will be searched in the reference frame. The BMA is only applied in a given search area of the frame, which consists of a window typically smaller than the frame itself, because image patterns tend to slightly displace from the area where they were in a previous frame. Figure 2.5 generically presents the concepts involved in the IME.

Encoders usually define that a BMA will start in a position whose vector is defined by a stage called Advanced Motion Vector Prediction (AMVP). This stage obtains the resulting vectors from ME executions of previously encoded CUs, and checks which of them is the best one to start the search for the current block being encoded. More specifically, a subset of vectors from spatial neighbors – above-left, left, below-left, above

Figure 2.5: Generic search in a previously coded frame.

and above-right –, along with temporal neighbors, such as the vector from the co-located block, will decide the starting point of the BMA.

Many different BMAs have been proposed and are employed in current encoder implementations. The following subsections present some of the main BMAs mentioned in the literature.

# 2.7.1.1 Full Search

The Full Search (FS) is the most naïve BMA implementation in the literature. FS applies the search for the most similar block by displacing to every pixel in the search window, and it always finds the best possible matching block contained in the search window. For that reason, FS obtains an optimal result in temporal redundancy within the search window, resulting in a smaller bitstream at the encoder output.

The number of candidates evaluated by FS is equal, in magnitude, to the area, in pixels, of the search window, given that these are all the possible integer displacements. Due to the large number of candidates being tested, FS requires the higher number of

memory accesses and calculations among all the search algorithms. For that reason, realtime implementations employ other solutions and search heuristics, so that the search is performed for a smaller number of motion vector displacement candidates, while still attempting to find residual blocks very similar to the best possible within the search window considered.

Even though this algorithm is mostly not suitable for real-time implementations, FS has the advantage of not being data-dependent. In other words, all candidates to be evaluated are known from the moment the start position is found, so pre-fetching mechanisms to gather block data can be applied. As it will be seen in the next subsections, the other presented BMAs all depend on block data from previous iterations of the search algorithm being employed.

HM reference software employs the FS algorithm in the bi-prediction stage of the ME stage, by default. The x265 software does not use FS in any of the high-level presets; placebo, which is its most complex preset, uses Star Search (SS), whose behavior will be explained later.

#### 2.7.1.2 Test Zone Search

Test Zone Search (TZS) is the main BMA employed by the HM reference software. TZS represents a better trade-off between time and quality, i.e., even though it does not always find the optimal block inside the search window, it ends up performing a much smaller amount of block comparisons when compared to FS, making it less time-consuming.

The default configuration of TZS is based on a diamond-shaped search, and it is split into four subsequent stages (CRISTANI, 2014):

- Search Vector Initialization: this stage checks whether the colocalized vector pointing to the colocalized candidate block from the reference frame or the vector resulting from the IME iteration of the 2N×2N partition are better than the current start vector, which was chosen by the AMVP stage. The start search vector is then set as the best one out of the three. Sometimes, these vectors may already have been evaluated, so the encoder performs in the most optimal way to not check these vectors more than once;

- First Search (FiS): in this stage, the main diamond-shaped search is performed, starting from the position defined from the first step. The diamond pattern checks

four, eight or sixteen candidates, depending on the number of iterations it requires, which is incremented after each diamond step. FiS ends when the algorithm does not find any better candidates for three iterations. Basically, HM implements a loop with a variable denoted as iDist, and this variable is squared at each iteration, increasing in powers of two. This value indicates the distance of the diamond shape from the current center. The higher the value iDist is, the more candidates are evaluated, with a maximum of sixteen candidates per iteration;

- Raster Search (RS): this step searches through the entire search area with a step of pixels between each candidate defined by a variable denoted as *iRaster*. Also, this stage only executes if the vector generated so far by the algorithm is larger than the same value defined by *iRaster*. This variable is set to 5 in the default preset of the encoder. This stage can also be seen as a more generic case of the FS BMA. A RS execution with a step of 1 would imply just in the execution of the FS. This step, just as FS, is also fully independent on its own, so the candidates can be evaluated in parallel, if enough resources are available to perform that;

- **Refinement Search**: the last stage also performs a diamond-shaped search, just like in FiS. However, it performs some iterations of that same algorithm which is already composed of numerous iterations. This step, as well as the whole IME stage, stops when no better candidates have been found in an entire iteration. The best motion vector from this stage is chosen as the global motion vector of the IME execution, and it is ready for the FME to be applied.

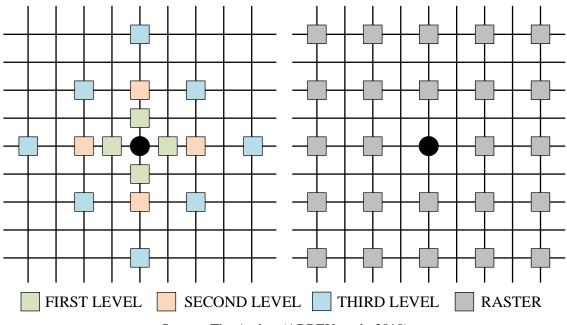

These stages are illustrated in Figure 2.7.1.2 in a simplistic way, highlighting the possible diamond and raster patterns, with a vector starting from the decision in the search vector initialization step.

The diamond shape from TZS may also be replaced by a squared shape, by varying the presets in the HM software. Moreover, several other additional stages may be applied to enhance the block search. In other words, the TZS algorithm can be seen as a template, in which different combinations may be used in each of its steps. The x265 software also implements an algorithm that follows the same stages of the TZS, namely Star Search (SS). This algorithm is executed in the Slow, Slower, Veryslow and Placebo versions of x265. There is a small variation in the Placebo version, however, given that the ME Range parameter – related to the size of the search window, which has been previously explained – is 92, whereas it is defined as 57 for the remaining presets. This specially makes the execution of RS even more costly, given that its number of candidates is proportional to

Figure 2.6: Search shapes for the TZS.

Source: The Author (ABREU et al., 2018)

the number of pixels in the search window.

## 2.7.1.3 Hexagon Search

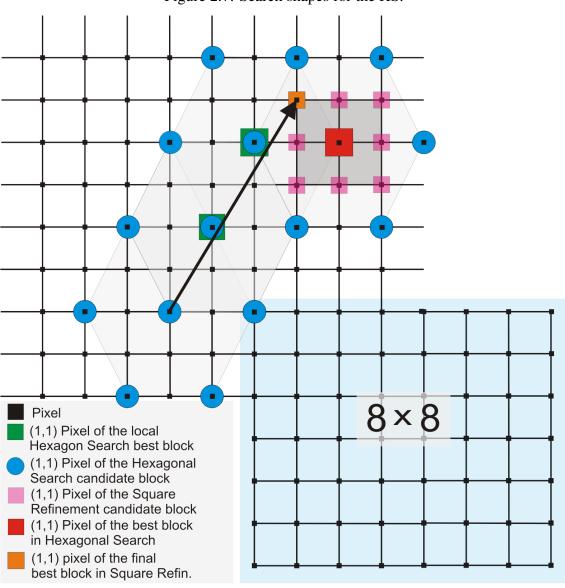

Hexagon Search (HS) is the BMA implemented in the medium (default) preset of x265. This algorithm follows a hexagon-shaped pattern, and it has a simpler execution flow than TZS, which is one of the reasons why x265 is so much faster than HM, since IME represents a large portion of the total execution time. HS has three stages, which are described below:

- **Search Vector Initialization**: this stage works similarly to the Search Vector Initialization in the TZS algorithm, only differing in the number of candidates evaluated to decide the initial center of the search;

- **Hexagon**: this step performs a six-point search in a hexagon-shaped format around the center of the search, considering the initial center defined by the previous step. Whenever there is a candidate more similar to the block being encoded than the one in the center, the new center is set as the vector associated with that new candidate. Then, the iteration is applied again, starting from the new center of the search. This stage stops when none of the candidates are better than the current center. The x265 software applies an optimization to this stage: starting from the second iteration of the hexagon search, only three candidates need to be evaluated instead of six, since

the three remaining points will always have been evaluated in the previous iteration;

• Square Refinement: after the Hexagon step defines the best candidate, an 8-point square refinement is applied around that point. The final vector value is defined by the best candidate evaluated at this stage. If none of the candidates are better than the current center, then the center defined by the previous step is the best vector.

Figure 2.7 illustrates the whole process of the HS algorithm, considering an  $8\times8$  PU, in which four iterations of the Hexagon are performed. In the last one, no candidates were more similar to the block being encoded than the center, so the square refinement was applied, resulting in a better block found in one of its eight candidates.

Figure 2.7: Search shapes for the HS.

Source: (SILVEIRA et al., 2017)

It should be noted that, for both TZS and HS, the decision of which blocks to

compare heavily depends on the previous stage, as most of the steps start from the best current vector of a previous one. This severely harms pipeline implementations, possibly resulting in pipeline stalls, due to the fact that the decision on the next candidate to be gathered is still executing.

### 2.7.1.4 Alternative BMAs

Apart from the main BMAs presented in the previous subsections, and from the few BMAs proposals that will be seen in Chapter 3, there are some other BMA implementations in both HM and x265 encoder softwares. These will be briefly explained in the following items:

- **Diamond Search**: this is the BMA employed in the ultrafast preset of the x265 encoder. This pattern simply evaluates four candidates, i.e., above, right, left and below, all of them with a distance of one pixel from the original block, and iterates through this evaluation several times, until similarity conditions are met, or until the search hits the search window borders;

- Uneven Multi-Hexagon (UMH) Search: this is implemented in the x265, and it is an adaptation of the BMA used in x264 the x265 equivalent for H.264/AVC. UMH has a rather complex flow: it starts with a refinement of its predictors, contains a few early-termination mechanisms, uses an adaptive search range based on the variability of the MV candidates, and also uses a shape similar to a hexagon;

- Successive Elimination Algorithm (SEA): also implemented in x265, this BMA is very similar to FS, but attempting to perform it faster, applying different metrics than usual;

- Selective TZS: this is a version of TZS with its main stages, but with weaker early termination restrictions, ending the execution earlier when compared to normal TZS. This is implemented in HM as an alternative to TZS, but it is not used by default.

### 2.7.2 Fractional Motion Estimation

Fractional Motion Estimation (FME) is applied after the IME and it is responsible for finding the best match at the fractional-pixel level, starting from the most similar block found in the IME. Since the frames are formed only by integer pixels, FME requires the

use of an interpolator to estimate fractional pixels positioned between the integer pixels of the image. FME is responsible for increasing image quality in video sequences due to the fact that real-life patterns most frequently move at a rate that is not a good match to the integer-pixel displacement between two simultaneous video captures.

HEVC defines 48 possible candidates to be compared in the FME: 8 half-precision and 40 quarter-precision candidates. Fig. 2.8 presents the set of fractional points needed to gather all the information regarding the 48 fractional blocks. In this figure, green positions correspond to integer pixels, blue positions correspond to half-precision pixels and white positions correspond to quarter-precision pixels. Half and quarter-precision pixels are generated by interpolation using 7-taps and 8-taps FIR filters (RABINER; GOLD, 1975), depending on the specific point. The highlighted partition shows the 48 possible points to which comparisons will be performed.

Figure 2.8: FME fractional pixels window for a  $4\times4$  PU.

Source: The Author

In x265 and HM, only a subset of these candidates are evaluated. In both encoders, only 8 half-precision and 8 quarter-precision candidates are evaluated. The execution first evaluates the 8 half precision pixels, and based on the best one, the 8 quarter precision candidates surrounding the best half precision candidate are evaluated.

## 2.7.3 Metrics for Block Similarity

Several metrics can be applied to determine the degree of similarity between two blocks. They differ from each other in ease of implementation, efficiency and result accuracy, i.e. how precisely they can define the similarity between the blocks. The main metrics used to estimate block similarity in video codecs are shown in the next subsections.

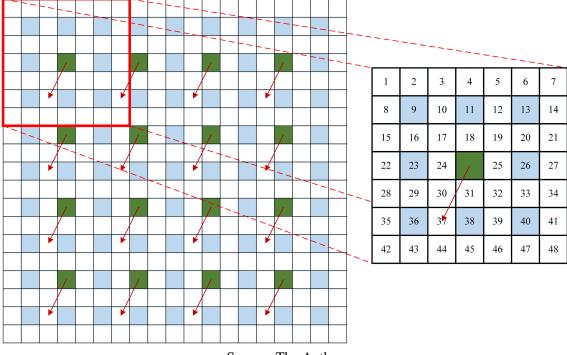

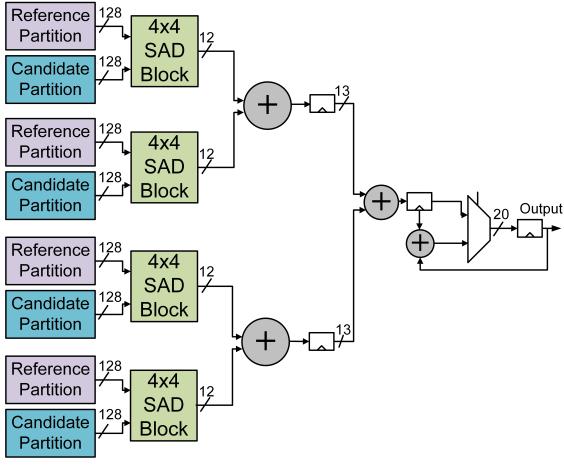

## 2.7.3.1 Sum of Absolute Differences

Sum of Absolute Differences (SAD) is the simplest similarity metric used in the video encoding process and it is applied by calculating the differences between the colocalized pixels of a current and a candidate block, performing an absolute operation in these differences, and then adding the values. SAD is employed in the IME and is also one of the most used metrics in the video encoding process, representing, on average, 22.4% of the encoding time in the HM reference software (ABREU et al., 2017). The complete formula is given by 2.4, in which O and R denote the current and the candidate blocks, respectively; m and n refer to the width and height of the blocks (correspondent to the shape of the PU being considered).

$$SAD = \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} |O_{i,j} - R_{i,j}|$$

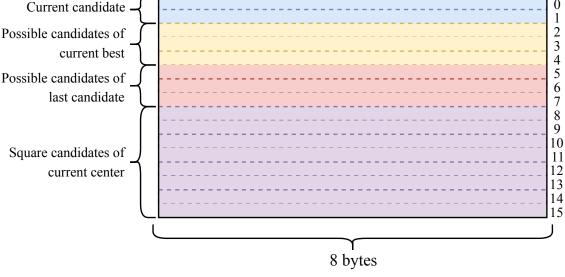

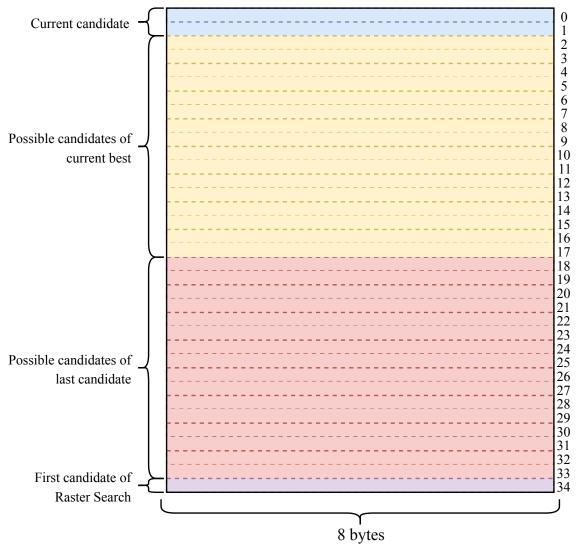

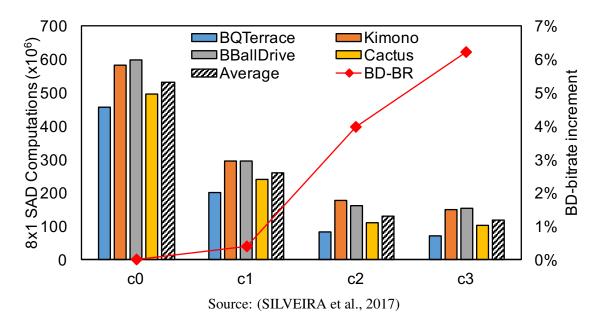

(2.4)