### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA GRADUATE PROGRAM ON MICROELECTRONICS

SANDRO BINSFELD FERREIRA

Design of a SAW-Less CMOS Discrete-Time Receiver for Bluetooth Low Energy

> Thesis presented in partial fulfillment of the requirements for the degree of Doctor in Microlectronics

Prof. Dr. Sergio Bampi Advisor

Prof. Dr. Robert Bogdan Staszewski Co-Advisor

Porto Alegre, Setember 2016

Ferreira, Sandro Binsfeld

Design of a SAW-Less CMOS Discrete-Time Receiver for Bluetooth Low Energy / Sandro Binsfeld Ferreira. - Porto Alegre: PGMICRO of UFRGS, 2016.

103 f.: il.

Thesis (Ph.D.) – Universidade Federal do Rio Grande do Sul. Graduate Program on Microelectronics, Porto Alegre, BR– RS, 2016. Advisor: Sergio Bampi; Coadvisor: Robert Bogdan Staszewski.

1. CMOS. 2. Bluetooth Low Energy. 3. Discrete-time receiver. 4. Switched Capacitor. I. Bampi, Sergio. II. Staszewski, Robert Bogdan. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Rui Vicente Oppermann Vice Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenadora do PGMICRO: Prof<sup>a</sup>. Fernanda Gusmão Lima Kastensmidt Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

To my wife Suse.

## ACKNOWLEDGMENTS

This work was not only a result of circuit simulations, but also of uncountable minutes of computer screen contemplation as well as several enlightening discussions in coffee rooms both in Brazil and in The Netherlands.

I would like to thank CAPES - Brazilian Federal Agency for R&D Support of the Brazil Ministry of Education for facilitating my experience in The Netherlands.

I would also like to give special thanks to:

My two homes during this time: the Federal University of Rio Grande do Sul, UFRGS, and the Technical University of Delft, TUDelft.

My Advisor, Prof. Dr. Sergio Bampi, for believing in me and for patiently but strongly motivating my experience abroad.

My Co-Advisor, Prof. Dr. Robert Bogdan Staszewski, for this huge challenge he presented to me, also helping me with tools and ideas to overcome it.

Iman Madadi and Massoud Tohidian, for teaching me the *nuts and bolts* of discrete time receivers.

Augusto Ximenes, for the long and grateful technical discussions between the EWI building and Delft Train Station.

Feng-Wei Kuo and TSMC for the support in the physical implementation and measurements part of the design.

Marion de Vlieger and Antoon Frehe for all the help at TUDelft.

My colleagues from LAB110 at UFRGS, and EWI at TUDelft. NSCAD friends.

Design of a SAW-Less CMOS Discrete-Time Receiver for Bluetooth Low Energy

### ABSTRACT

Personal mobile communications and the Internet of Things increased the complexity of radio frequency front-end design, in particular due to the requirements for energy autonomy over long periods, which translates into very hard low-power constraints. Bluetooth Low Energy is a new version of the Bluetooth Standard specified to answer to this recent market need. In the receiver part of the design, discrete-time implementations appear as a new hardly explored possibility to reduce power, benefiting from CMOS technology scaling and adding flexibility to the front-end design. Integration is another important point and traditionally external parts of the design like filters and matching networks, need to be part of the integrated circuit as much as possible. The present work implements a surface acoustic wave (SAW)-less fully discrete-time front-end receiver for Bluetooth Low Energy. The design uses band-pass switched capacitor passive filters recently introduced and a careful choice of sampling rates and anti-aliasing filters to develop a SAW-less ultra low power receiver architecture with state-of-the-art performance. Architectural and block-level strategies associated with a discrete-time design are explained in detail in a top-down approach. The design is implemented in TSMC 28nm Low Power CMOS. Measurement results show a performance of 6.5 dB noise figure including internal matching network and switch, and -19 dBm IIP3 for a power cost of 2.75 mW.

**Keywords:** CMOS, Bluetooth Low Energy, discrete-time receiver, switched capacitor.

# Projeto de um receptor em tempo discreto CMOS para *Bluetooth Low Energy* sem filtro externo de seleção de banda

### RESUMO

Comunicações móveis e a Internet das Coisas adicionaram complexidade ao projeto de circuitos de rádio frequência, principalmente devido à necessidade de autonomia de bateria por longos períodos. Em consequência, ocasionando requisitos rígidos de baixa potência. Bluetooth Low Energy é uma nova versão do protocolo Bluetooth destinada a atender esta recente demanda de Mercado. No projeto da parte analógica do receptor, novas técnicas de projeto em tempo discreto aparecem como uma possibilidade de reduzir o consumo de potência pouco explorada, que se beneficia da modernização das tecnologias CMOS e adiciona flexibilidade ao projeto do receptor. Integração é outro ponto importante e componentes externos ao receptor como filtros e redes de casamento agora necessitam fazer parte do circuito integrado de forma a reduzir os custos. O presente trabalho se insere neste contexto, com o desenvolvimento de um receptor para Bluetooth Low Energy totalmente em tempo discreto e sem filtros externos. O projeto utiliza filtros passa-faixas passivos implementados usando capacitores chaveados e escolha criteriosa de taxas de amostragem e filtros anti-aliasing para implementar uma arquitetura de tempo discreto sem filtros externos de baixíssimo consumo e com desempenho equiparável ao estado da arte em receptores para Bluetooth Low Energy. A arquitetura inovadora e as técnicas adotadas no projeto dos blocos em tempo discreto são apresentadas detalhadamente a partir do nível sistêmico. O projeto foi realizado em tecnologia de 28nm CMOS Low Power. Resultados de medida mostram que o receptor apresenta 6.5 dB de figura de ruído com rede de casamento e chaveamento integrado, e -19 dBm de IIP3 com um consumo total de 2.75 mW.

**Palavras-chave:** CMOS, *Bluetooth Low Energy*, receptor de tempo discreto, capacitor chaveado.

## LIST OF SYMBOLS

| $\alpha$            | $\alpha = gm/gd0$                            |

|---------------------|----------------------------------------------|

| $\alpha_n, \beta_n$ | capacitor charge ratios                      |

| $\gamma$            | excess noise factor                          |

| $\gamma_M$          | mixer linear time-varying coefficient        |

| ω                   | angular frequency                            |

| au                  | time constant                                |

| $\varphi_n$         | clock signal n                               |

| $A_i$               | gain of block <i>i</i>                       |

| $a_n$               | linearity coefficient                        |

| В                   | noise equivalent bandwidth                   |

| Bw                  | bandwidth of a signal                        |

| $C_H$               | history capacitor of a discrete-time filter  |

| $C_R$               | rotating capacitor of a discrete-time filter |

| Fi                  | noise factor of block i                      |

| $f_s$               | sampling frequency                           |

| $f_{LO}$            | local oscillator frequency                   |

| $G_i$               | available power gain of block <i>i</i>       |

| k                   | Boltzmann constant                           |

| $K_f$               | flicker noise factor                         |

| L                   | MOS channel length                           |

| $P_n$               | component power <i>n</i>                     |

| Q                   | quality factor                               |

| $q_{in}[n]$         | charge packet                                |

| $R_{sw}$            | switch resistance                            |

| $S_{ij}$            | S-parameter                                  |

|                     |                                              |

- *T* absolute temperature

- $v_n$  component voltage n

- $V_T$  threshold voltage

- $V_{ds}$  MOS drain-source voltage

- $V_{gs}$  MOS gate-source voltage

- $v_{in}$  input voltage

- $v_{out}$  output voltage

- W MOS channel width

- $Z_0$  filter input impedance

- $Z_{ij}$  Z-parameter

- $Z_n$  impedance n

## LIST OF ACRONYMS AND ABBREVIATIONS

| ADC  | Analog-to-Digital Converter             |

|------|-----------------------------------------|

| BER  | Bit-Error-Rate                          |

| BLE  | Bluetooth Low-Energy                    |

| BT   | Bandwidth-bit Period Product            |

| CMFB | Common-mode Feedback                    |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| COB  | Chip-on-board                           |

| CS   | Charge Sharing                          |

| СТ   | Continuous Time                         |

| CW   | Continuous-wave                         |

| DCO  | Digital Controlled Oscillator           |

| DR   | Dynamic Range                           |

| DT   | Discrete-Time                           |

| F    | Noise Factor                            |

| FIR  | Finite Impulse Response                 |

| GFSK | Gaussian Frequency Shift Keying         |

| IF   | Intermediate Frequency                  |

| IIR  | Infinite Impulse Response               |

| IM2  | Second Order Intermodulation Tone       |

| IM3  | Third Order Intermodulation Tone        |

| IoT  | Internet of Things                      |

| IP2  | Second Order Intercept Point            |

| IP3  | Third Order Intercept Point             |

| LMV  | LNA-Mixer-VCO                           |

| LNA    | Low Noise Amplifier                                |

|--------|----------------------------------------------------|

| LNTA   | Low Noise Transconductance Amplifier               |

| LO     | Local Oscillator                                   |

| LSB    | Lower Side Band                                    |

| LTV    | Linear Time-Varying                                |

| MDS    | Minimum Detectable Signal                          |

| MOM    | Metal-oxide-metal                                  |

| NF     | Noise Figure                                       |

| OOB    | Out-of-Band                                        |

| P1dB   | 1 dB compression point                             |

| PAC    | Periodic AC Analysis                               |

| PCB    | Printed circuit board                              |

| PDK    | Process Design Kit                                 |

| PER    | Packet Error Rate                                  |

| PNOISE | Periodic Noise Analysis                            |

| PSS    | Periodic Steady State Analysis                     |

| PVT    | Process, Voltage and Temperature                   |

| QN     | Quantization Noise                                 |

| RF     | Radio Frequency                                    |

| SAR    | Successive Approximation Register                  |

| SAW    | Surface Acoustic Wave                              |

| SC     | Switched Capacitor                                 |

| SDR    | Software Defined Radio                             |

| SNR    | Signal-to-Noise Ratio                              |

| TDD    | Time Division Duplexing                            |

| TIA    | Trans-Impedance Amplifier                          |

| TSMC   | Taiwan Semiconductor Manufacturing Company Limited |

| WIS    | Windowed Integration Sampler                       |

| WLAN   | Wireless Local Area Network                        |

|        |                                                    |

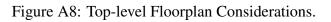

## **LIST OF FIGURES**

| 2.1  | Typical nonlinear system.                                            | 20 |

|------|----------------------------------------------------------------------|----|

| 2.2  | Combination of harmonics for the modeled system                      | 21 |

| 2.3  | Output power of fundamental and IM3 versus input power               | 22 |

| 2.4  | Cascaded system.                                                     | 24 |

| 2.5  | Direct conversion architecture.                                      | 25 |

| 2.6  | Heterodyne architecture.                                             | 26 |

| 2.7  | Sliding IF architecture                                              | 26 |

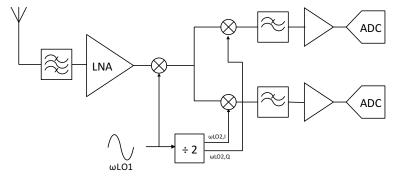

| 2.8  | Image-reject architectures.                                          | 27 |

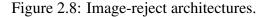

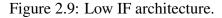

| 2.9  | Low IF architecture.                                                 | 28 |

| 2.10 | Bluetooth discrete-time receiver presented by Texas Instruments      | 28 |

| 2.11 | Wideband discrete-time receiver.                                     | 28 |

| 2.12 | (a) Voltage sampling principle. (b) Clock waveform.                  | 29 |

| 2.13 | (a) Charge sampling principle. (b) Clock waveform.                   | 29 |

| 2.14 | 50 % duty-cycle charge sampling transfer function. ( $Matlab^{TM}$ ) | 31 |

| 2.15 | IIR discrete-time implementation.                                    | 32 |

| 2.16 | IIR transfer function. ( <i>Matlab</i> )                             | 33 |

| 2.17 | IIR transfer function. ( <i>Matlab</i> )                             | 33 |

| 2.18 | FIR DT implementation.                                               | 34 |

| 2.19 | FIR transfer function. (Matlab)                                      | 34 |

| 2.20 | (a) Sliding-IF BLE receiver for Zigbee and Bluetooth. (b) RF front-  |    |

|      | end receiver with push-pull mixer.                                   | 35 |

| 2.21 | (a) Sliding-IF BLE receiver for biotelemetry application. (b) RF     |    |

|      | front-end detail.                                                    | 36 |

| 2.22 | BLE receiver using LMV front-end.                                    | 36 |

| 2.23 | Quadrature LNA detail                                                | 37 |

| 2.24 | (a) BLE transceiver without LNA. (b) Details of passive conventional |    |

|      | mixer                                                                | 37 |

| 2.25 | (a) Integrated switch BLE transceiver. (b) Detail of LNA and PA      |    |

|      | antenna matching.                                                    | 38 |

| 3.1  | Bluetooth Low Energy spectrum.                                       | 41 |

| 3.2  | BLE sensitivity requirements.                                        | 42 |

| 3.3  | Interference performance test.                                       | 42 |

| 3.4  | BB filter requirements.                                              | 43 |

| 3.5  | IF filter requirements                                               | 43 |

| 3.6  | BLE intermodulation requirements.                                    | 43 |

| 3.7  | Blocking sensitivity at low gain.                                    | 44 |

| 3.8        | BLE out-of-band blocking                                                            | 45  |

|------------|-------------------------------------------------------------------------------------|-----|

| 3.9        | BLE phase noise requirement.                                                        | 46  |

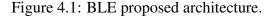

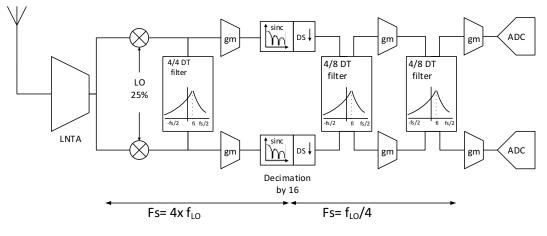

| 4.1        | BLE proposed architecture.                                                          | 48  |

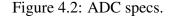

| 4.2        | ADC specs.                                                                          | 48  |

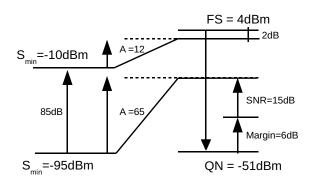

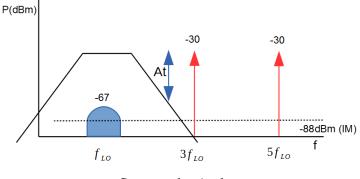

| 4.3        | Front-end aliasing due to mixer sampling                                            | 50  |

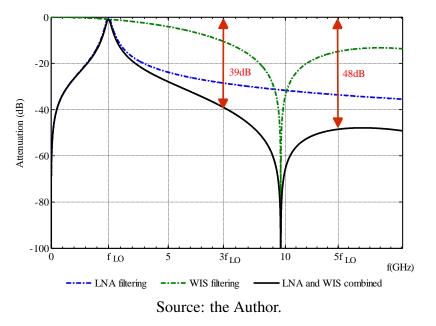

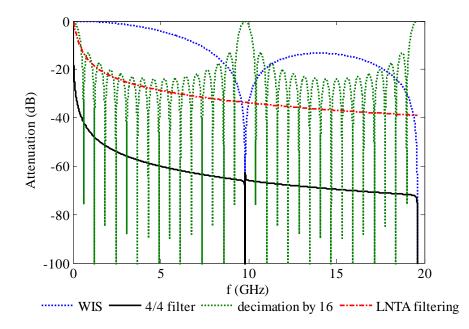

| 4.4        | LNTA front-end filtering.                                                           | 51  |

| 4.5        | Combined LNTA selectivity and charge sampling WIS filter effect.                    | 50  |

|            | (Matlab)                                                                            | 52  |

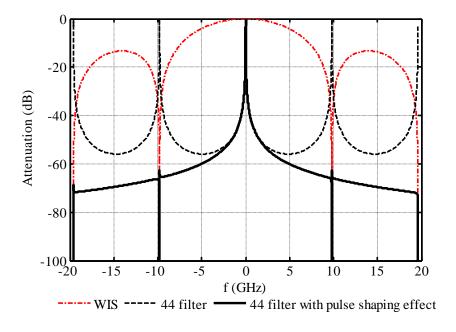

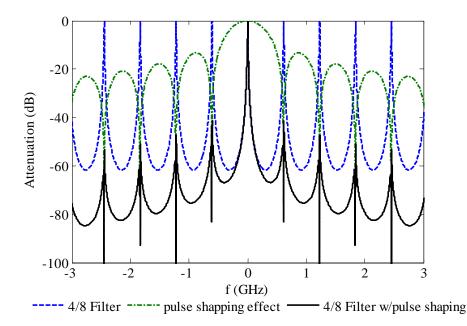

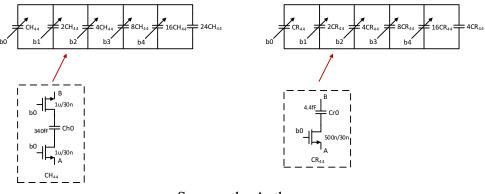

| 4.6        | Pulse shaping effect in the 4/4 filter transfer function. ( <i>Matlab</i> )         | 53  |

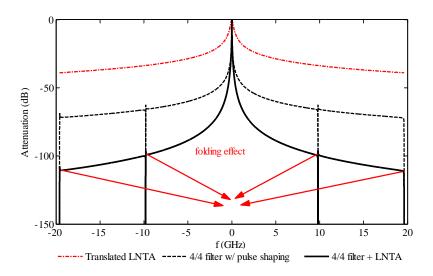

| 4.7        | Full-rate front filtering effect. (Matlab)                                          | 53  |

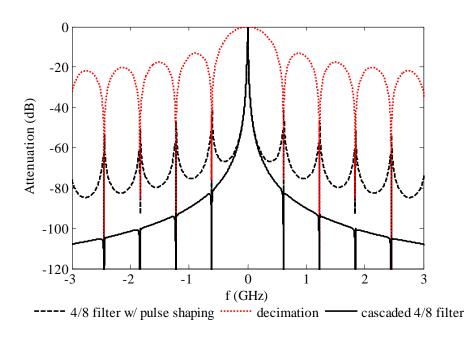

| 4.8        | Filter 4/8 with pulse shaping effect. ( <i>Matlab</i> )                             | 54  |

| 4.9        | Filter 4/8 with pulse shaping effect and decimation. ( <i>Matlab</i> )              | 55  |

| 4.10       | Anti-aliasing protection FIR filter implemented by clock decimation                 |     |

|            | by 16. ( <i>Matlab</i> )                                                            | 55  |

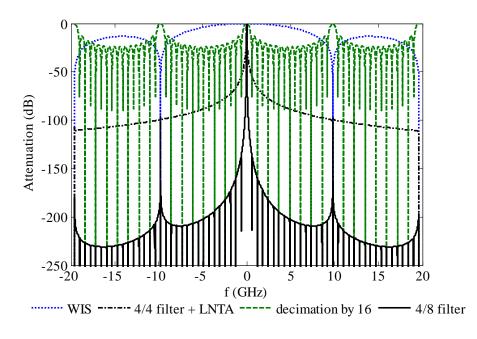

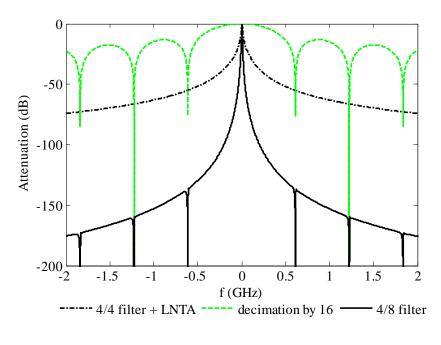

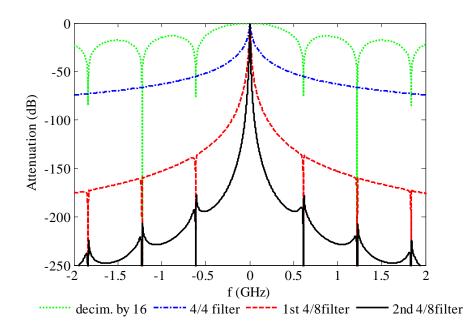

| 4.11       | IF complex filtering. (Matlab)                                                      | 56  |

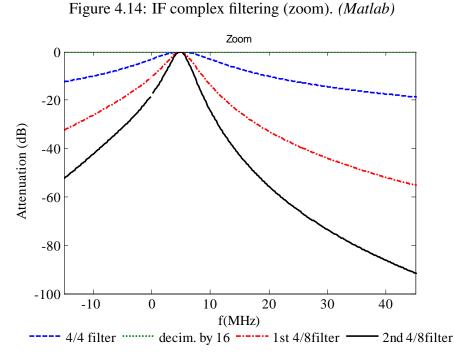

| 4.12       | IF complex filtering - zoom. (Matlab)                                               | 57  |

| 4.13       | Cascaded IF complex filtering in the complete receiver chain. (Matlab)              |     |

| 4.14       | IF complex filtering (zoom). (Matlab)                                               | 58  |

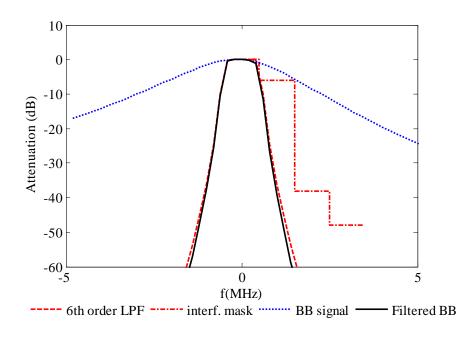

| 4.15       | Baseband filtering. (Matlab)                                                        | 58  |

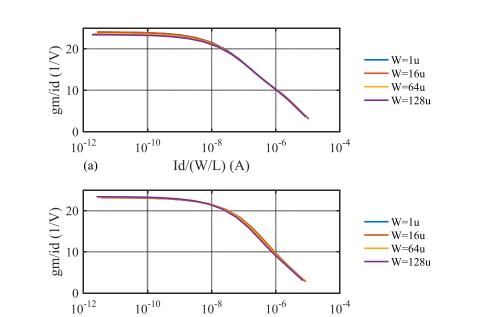

| 5.1        | (a) NMOS - $gm/Id$ vs $i$ (L=30 nm, $V_{ds}$ =0.5 V) (b) PMOS - $gm/Id$             |     |

|            | vs <i>i</i> (L=30 nm, $V_{ds}$ =0.5 V)                                              | 61  |

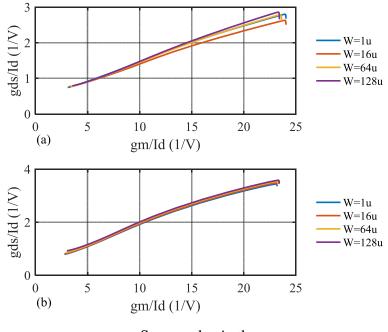

| 5.2        | (a) NMOS - $gds/Id$ vs $gm/Id$ (L=30 nm, $V_{ds}$ =0.5 V) (b) PMOS -                |     |

|            | $gds/Id \text{ vs } gm/Id \text{ (L=30 nm, } V_{ds} = 0.5 \text{ V}).$              | 61  |

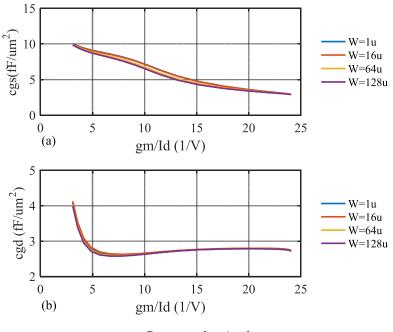

| 5.3        | (a) NMOS - Cgs capacitance vs $gm/Id$ (L=30 nm, $V_{ds}$ =0.5 V) (b)                | ( ) |

|            | NMOS Cgd capacitance vs $gm/Id$ (L=30 nm, $V_{ds}$ =0.5 V)                          | 62  |

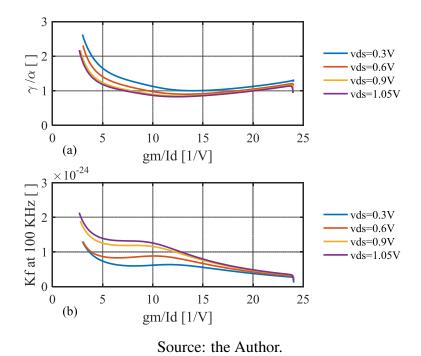

| 5.4        | (a) NMOS - thermal noise coefficient vs $gm/Id$ (L=30 nm, W=2.4                     |     |

|            | um) (b) NMOS flicker noise coefficient vs $gm/Id$ (L=30 nm, W=2.4 um).              | 62  |

| 5.5        | Switch resistance of regular $V_T$ and low $V_T$ NMOS device in conduc-             | 02  |

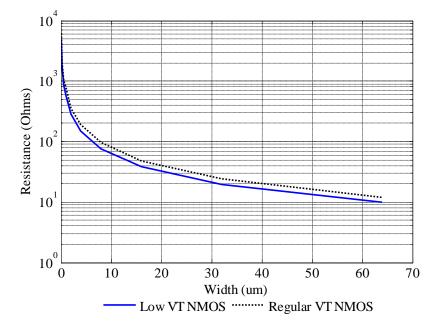

| 5.5        | tion $(Vgs = 1.05 \text{ V}, Vds = 0.1 \text{ V}, \text{L} = 30 \text{ nm})$ .      | 63  |

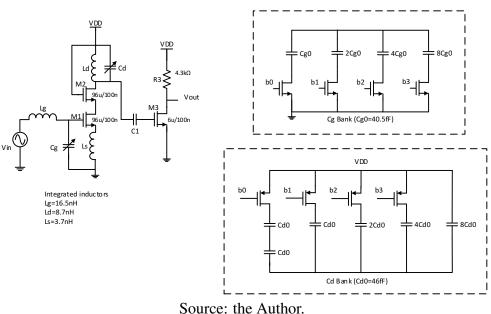

| 5.6        | Schematics of LNTA and trimming capacitors                                          | 64  |

| 5.7        | e i                                                                                 | 64  |

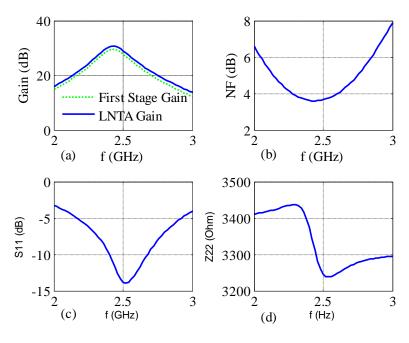

| 5.8        | LNTA electrical simulation results: (a) gain; (b) NF; (c) $S_{11}$ ; (d) $Z_{22}$ . | 65  |

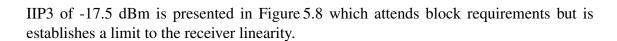

| 5.8<br>5.9 | LNTA input referred IIP3.                                                           | 65  |

|            | LNTA input and output transient.                                                    | 66  |

| 5.10       | LNTA gain and S11 corners.                                                          |     |

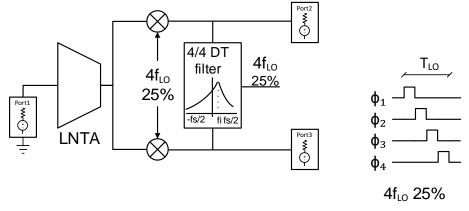

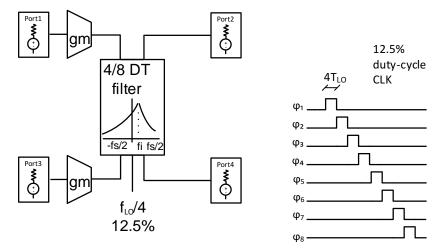

| 5.11       | Quadrature sampling mixer.                                                          | 67  |

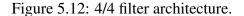

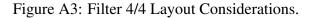

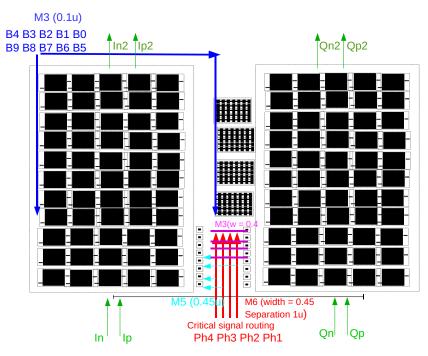

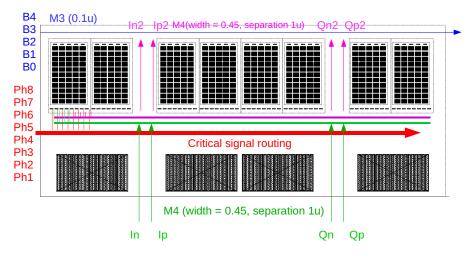

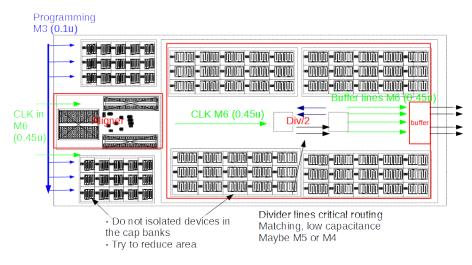

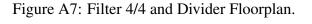

| 5.12       | 4/4 filter architecture.                                                            | 68  |

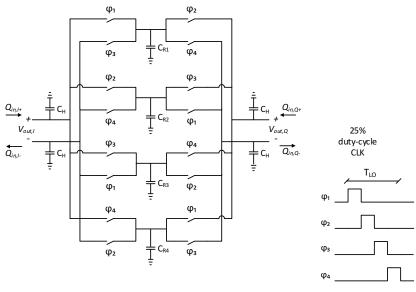

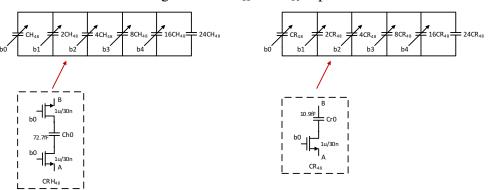

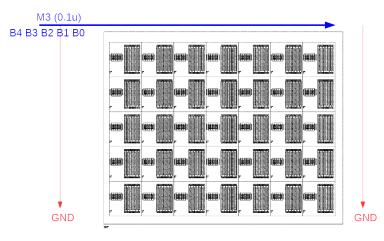

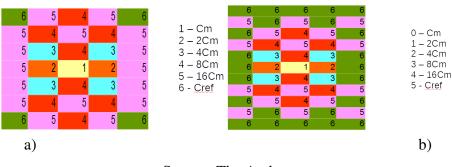

| 5.13       | $C_H$ and $C_R$ capacitor banks.                                                    | 69  |

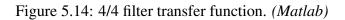

| 5.14       | 4/4 filter transfer function. ( <i>Matlab</i> )                                     | 70  |

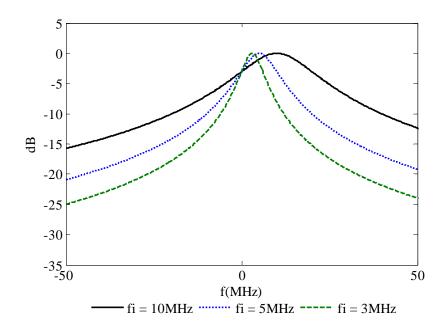

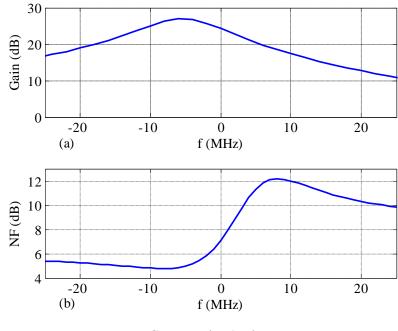

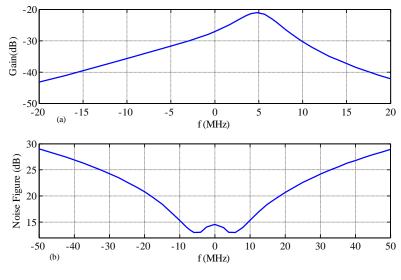

| 5.15       | Filter 4/4: (a) gain response; (b) noise figure.                                    | 71  |

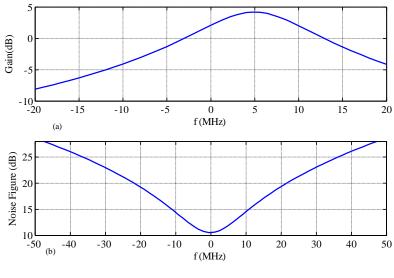

| 5.16       | Full-rate Operation Section schematics.                                             | 72  |

| 5.17       | Full-rate Operation Section simplified testbench.                                   | 72  |

| 5.18       | Full-rate Operation Section (a) gain; (b) noise figure.                             | 73  |

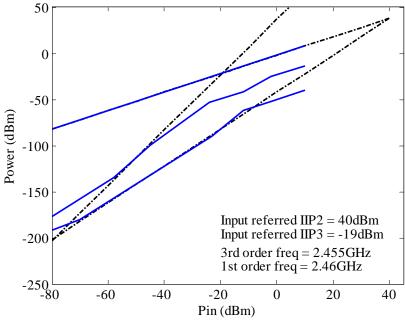

| 5.19       | Full-rate Operation Section input referred IIP2 and IIP3.                           | 73  |

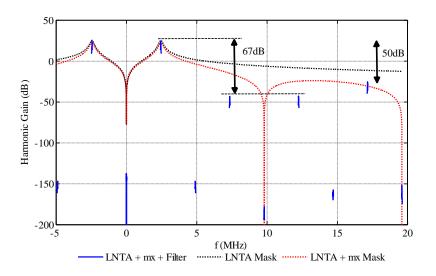

| 5.20       | Full-rate Operation Section translation gain.                                       | 74  |

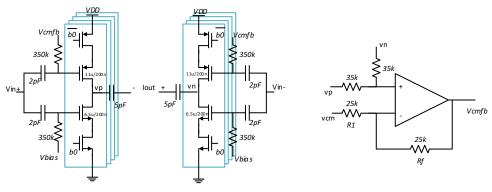

| 5.21       | Gm cell schematics.                                                                 | 75  |

| 5.22       | Gm cell stability analysis.                                                         | 75  |

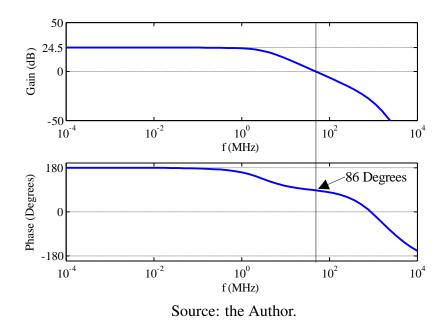

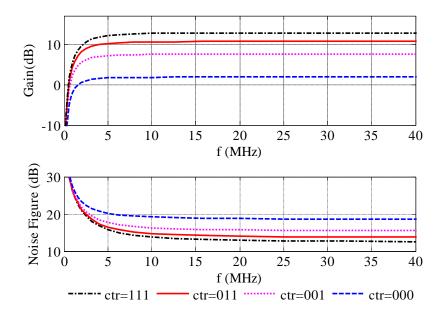

| 5.23 | Gm cell gain and noise figure.                                       | 76 |

|------|----------------------------------------------------------------------|----|

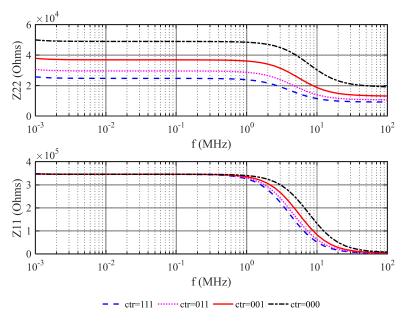

| 5.24 | Gm cell $Z_{11}$ and $Z_{22}$ .                                      | 76 |

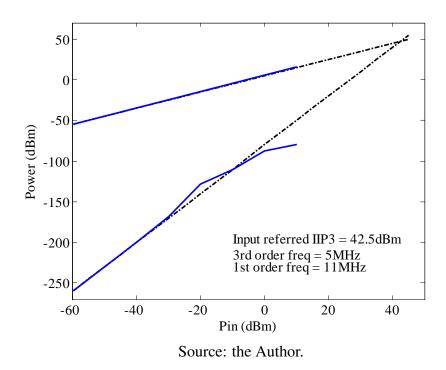

| 5.25 | Gm cell IIP3                                                         | 77 |

| 5.26 |                                                                      | 77 |

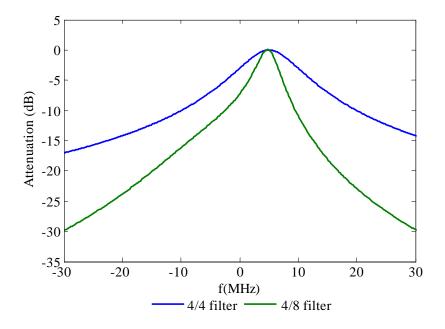

| 5.27 | Comparison between 4/4 and 4/8 filter transfer functions. (Matlab) . | 78 |

| 5.28 | $C_H$ and $C_R$ capacitor banks.                                     | 78 |

| 5.29 | Filter 4/8: (a) gain; (b) noise figure.                              | 79 |

| 5.30 | Combined Gm and filter 4/8 simplified testbench.                     | 79 |

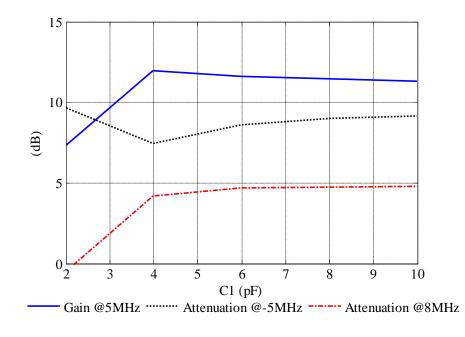

| 5.31 | Gm decoupling capacitor impact.                                      | 80 |

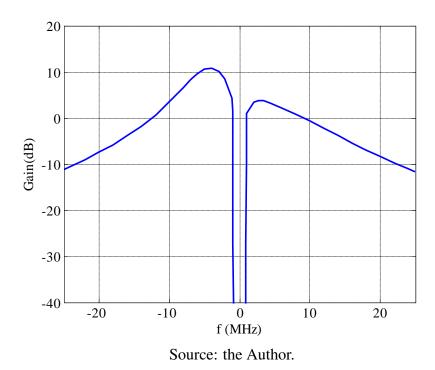

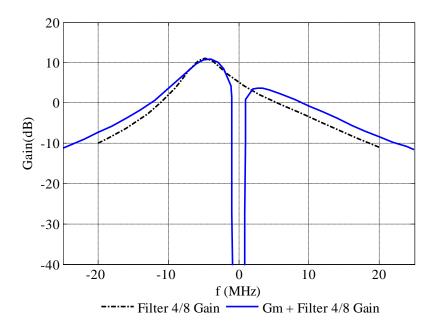

| 5.32 | Combined Gm and filter 4/8 Gain                                      | 80 |

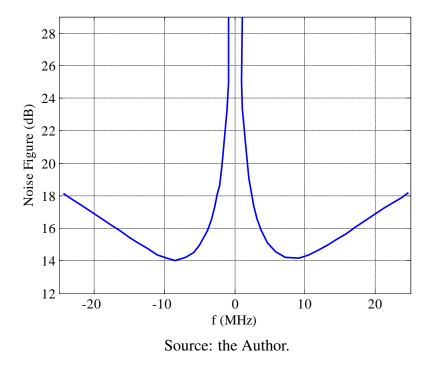

| 5.33 | Combined Gm and filter 4/8 Noise Figure                              | 81 |

| 5.34 | Reduction in filter 4/8 quality factor due to Gm output impedance    |    |

|      | reduction.                                                           | 81 |

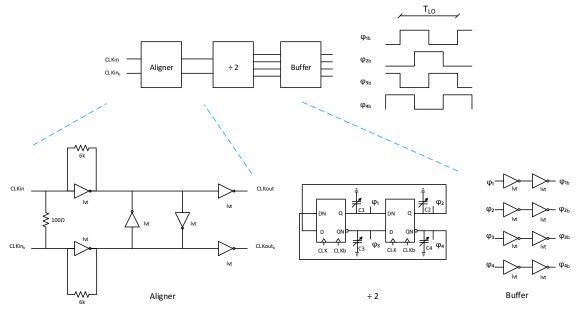

| 5.35 | High speed 50 % clock generation.                                    | 82 |

| 5.36 | Customized D latch schematics.                                       | 82 |

| 5.37 | 25 % duty-cycle generation logic.                                    | 83 |

| 5.38 | Phase noise after 25 % duty-cycle clock generation                   | 83 |

| 5.39 | Phase noise corners.                                                 | 84 |

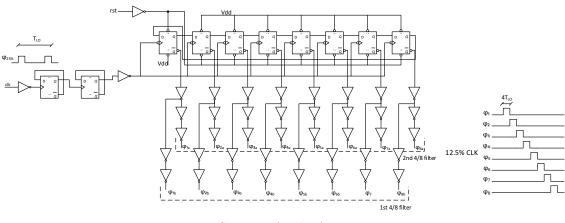

| 5.40 | Generation of 12.5 % duty-cycle signals.                             | 85 |

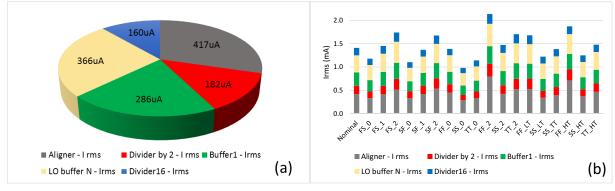

| 5.41 | Divider current consumption breakdown.                               | 85 |

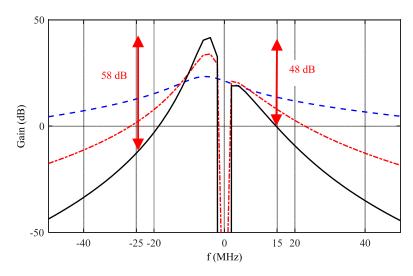

| 5.42 | Top-level gain.                                                      | 86 |

| 5.43 | Top-level noise figure.                                              | 86 |

| 5.44 | 1                                                                    | 87 |

| 5.45 | Chip micrograph.                                                     | 88 |

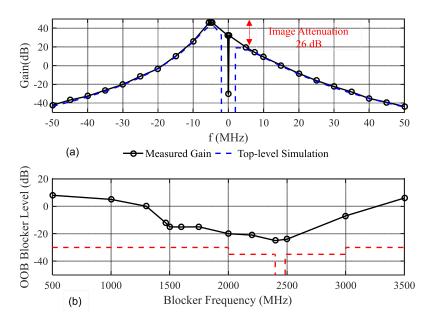

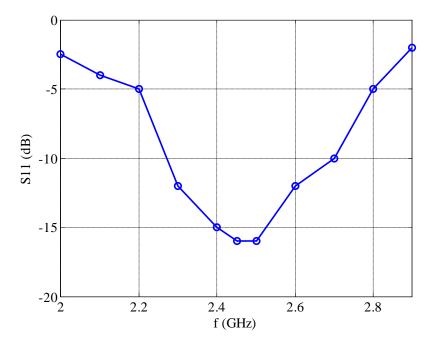

| 5.46 | (a) Measured receiver transfer function. (b) Measured OOB blocking   |    |

|      | test                                                                 | 88 |

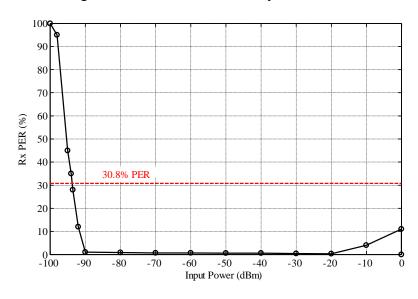

| 5.47 | Receiver sensitivity measurement.                                    | 89 |

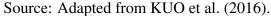

| 5.48 | (a) Measured channel gain and image attenuation. (b) Measured        |    |

|      | channel IIP3 and noise figure                                        | 89 |

| 5.49 |                                                                      | 90 |

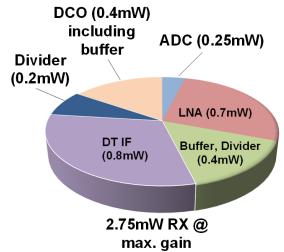

| 5.50 | Typical measured power consumption breakdown of the implemented      |    |

|      | receiver                                                             | 90 |

## LIST OF TABLES

| 2.1        | Comparison of state-of-the-art Bluetooth Low Energy receivers pre-<br>viously published.      | 39 |

|------------|-----------------------------------------------------------------------------------------------|----|

| 3.1<br>3.2 | BLE specifications                                                                            |    |

| 4.1<br>4.2 | DT receiver system-level requirements.                                                        |    |

| 5.1<br>5.2 | Gm cell gain and noise figure programming at 5 MHz                                            |    |

| 5.3        | Performance summary and comparison with state-of-the-art Blue-<br>tooth Low Energy receivers. | 91 |

## CONTENTS

| 1 IN  |                                                     | 17 |

|-------|-----------------------------------------------------|----|

| 1.1   | Organization of this Thesis                         | 18 |

| 2 R   | F RECEIVER BASIC CONCEPTS                           | 19 |

| 2.1   | Receiver Figures                                    | 19 |

| 2.1.1 | Noise Figure and Noise Factor                       | 19 |

| 2.1.2 | Sensitivity                                         | 19 |

| 2.1.3 | Maximum Input Signal and Dynamic Range              | 20 |

| 2.1.4 | Gain, Linearity and Noise Factor of Cascaded Stages | 23 |

| 2.2   | Receiver Architectures                              | 24 |

| 2.2.1 | Direct Conversion Receiver                          | 24 |

| 2.2.2 | Heterodyne Receiver                                 | 25 |

| 2.2.3 | Sliding IF Architecture                             | 26 |

| 2.2.4 | Image-Reject Architecture                           | 26 |

| 2.2.5 | Low-IF and High-IF Architectures                    | 27 |

| 2.3   | Discrete-Time Receivers                             | 27 |

| 2.3.1 | Sampling Mixer                                      | 29 |

| 2.3.2 | Infinite Impulse Response Filter                    | 31 |

| 2.3.3 | Finite Impulse Response Filter                      | 32 |

| 2.4   | State of the Art in BLE Receiver Design             | 35 |

| 2.5   | Summary                                             | 38 |

| 3 B   | LUETOOTH LOW ENERGY RECEIVER REQUIREMENTS           | 40 |

| 3.1   | System-Level Considerations                         | 41 |

| 3.1.1 | Sensitivity                                         | 41 |

| 3.1.2 | Linearity                                           | 41 |

| 3.2   | Summary                                             | 46 |

| 4 P   | ROPOSED RECEIVER ARCHITECTURE                       | 47 |

| 4.1   | System-Level Figures                                | 47 |

| 4.2   | Receiver Architecture                               | 50 |

| 4.2.1 | Full-rate Operation                                 | 50 |

| 4.2.2 | IF Filtering at Decimated Clock                     | 52 |

| 4.3   | Top-level Signal Flow                               | 56 |

| 4.4   | Summary                                             | 57 |

| 5 E                        | DESIGN AND MEASUREMENT RESULTS                   | 60                   |

|----------------------------|--------------------------------------------------|----------------------|

| 5.1                        | Block level Design                               | 60                   |

| 5.1.1                      | LNTA                                             | 60                   |

| 5.1.2                      | Sampling Mixer                                   | 66                   |

| 5.1.3                      | 4/4 IQ Filter Design                             | 67                   |

| 5.1.4                      | Full-rate Operation Section                      | 71                   |

| 5.1.5                      | Gm Cell                                          | 74                   |

| 5.1.6                      | 4/8 IQ Filter Design                             | 75                   |

| 5.1.7                      | Clock Generation                                 | 80                   |

| 5.1.8                      | Top Level Simulation Results                     | 84                   |

| 5.2                        | Physical Implementation and Measurements Results | 86                   |

| 5.3                        | Summary                                          | 90                   |

|                            | CONCLUSIONS                                      | 92                   |

| 6.1<br>6.2                 | Summary of Contributions                         | 92                   |

| 6.2                        |                                                  | 92<br>93<br>94       |

| 6.2<br>REFI                | Recommendations for Future Work                  | 92<br>93             |

| 6.2<br>REFI<br>LIST        | Recommendations for Future Work                  | 92<br>93<br>94       |

| 6.2<br>REFI<br>LIST<br>PUB | Recommendations for Future Work                  | 92<br>93<br>94<br>98 |

### 1 INTRODUCTION

From an analog and radio-frequency (RF) design point of view, power consumption has not always been the main constraint. Design of communication transceiver front-ends has been mainly defined by performance (NILSSON; SVENSSON, 2014). To complicate the matter, integrated circuit fabrication processes, mainly complementary metal-oxidesemiconductor (CMOS), are developed for digital applications that dominate the market. In this sense, analog and RF circuits have also to adapt to these sometimes inadequate process technologies.

Digital applications, on the other hand, have long been focusing on low power constraints in order to reduce costs of cooling, power, and to extend battery life as well.

These scenario has been slowly changing due to personal mobile communications need of longer battery time and more recently to the advent of the Internet of Things (IoT) concept. Several standards have emerged or enhanced in order to attend this recent need of low power wireless applications. Consequently, it has also become a big concern for analog and RF designers nowadays.

Low power and connectivity among intelligent devices are envisioned for the IoT. To support this, standards are designed for low data rates, low-complexity modulation schemes, and short link distances to achieve power-battery operation (HUANG, 2014). Bluetooth Smart<sup>TM</sup>, also known as Bluetooth Low Energy (BLE), and Zigbee  $3.0^{TM}$  are new popular standard versions specified to address this recent developed market. Several proprietary short-range radio solutions were also introduced, e.g. ANT+<sup>TM</sup>, and NIKE+<sup>TM</sup> (Nordic Semiconductor, 2010, 2008; Texas Instruments, 2015).

In the analog and RF design, this reduction of power consumption for IoT is usually obtained using different strategies, either system-level or block-level oriented. On the system-level side, event-driven operation modes are usually available in the new standards and the transceiver can be turned off or waked up for immediate or intermittent operation, with an average reduction of power consumption. On the block-level side, high performance analog intensive architectures now target less demanding specifications, also at low power. Operation at low-voltage supply and digitally-assisted analog circuits are common strategies.

Cost is another important issue in this low power wireless market, and it is strongly associated with integration. Not only technology processes optimized for low power digital are mainly used, but also traditionally external components like highly selective band-pass filters, matching networks, and duplexers have now to be integrated adding complexity to the RF design (MIRZAEI; DARABI; MURPHY, 2011; MASUCH; DELGADO-RESTITUTO, 2013; MADADI et al., 2015; PRUMMEL et al., 2015).

Recently, discrete-time (DT) transceiver implementations have being on the rise mainly associated with high performance and flexible Software Defined Radio (SDR) applica-

tions (ABIDI, 2007; MUHAMMAD et al., 2004, 2005). DT processing offers flexible tuning of filters by sampling rate adjustment with better control of filter corners when compared to continuous time processing (NIKOLIC; BORIVOJE, 2011). When implemented with passive switched-capacitor filters that do not have active elements, it also benefits from CMOS scaling, and its performance is mainly determined by the proper sizing of MOS switches (NIKOLIC; BORIVOJE, 2011). Nevertheless, discrete-time strategies have not been well explored for low power receiver applications yet.

The present work is well inserted in this context. This thesis presents the development of the first SAW (Surface Acoustic Wave)-less discrete-time (DT) Bluetooth Low Energy (BLE) receiver, with very competitive specifications for low power applications. The design was developed, implemented, and tested in TSMC 28nm CMOS.

#### **1.1** Organization of this Thesis

Chapter 2 starts with a brief review of receiver concepts. Basic and advanced architectures trade-offs are discussed with a special emphasis on the discrete-time approach. state-of-the-art receivers for Bluetooth Low Energy are presented to enable the discussion of the requirements for the discrete-time BLE receiver which is the focus of this work.

BLE receiver system-level requirements are discussed in Chapter 3.

The architecture of the receiver is presented in Chapter 4 where block level requirements to achieve a state-of-the-art BLE receiver are developed. The main strategies adopted in the discrete-time signal processing are presented in detail, such as anti-aliasing strategies, out-of-band linearity protection and analog decimation.

In Chapter 5, the block-level circuits are presented with emphasis on the discrete-time band-pass charge-sharing filters. Block-level simulations and top-level measurements verify that the proposed solution surpass BLE standard specifications.

Finally, Chapter 6 summarizes the work and presents conclusions and future work perspectives.

## 2 RF RECEIVER BASIC CONCEPTS

This chapter starts with a quick review of top-level receiver design constraints moving next to basic and more advanced receiver architectures and finally presents some solutions already published targeting low power receivers mainly for Bluetooth Low Energy.

#### 2.1 **Receiver Figures**

For a top-level design of a RF receiver, some requirements have to be considered from the very beginning. This section concentrates on reviewing basic parameters involved in the receiver design, namely:

- Noise Figure

- Sensitivity

- Maximum input signal

- Dynamic Range

#### 2.1.1 Noise Figure and Noise Factor

Noise Factor (F) is defined as the ratio between the signal-to-noise ratio (SNR) at the input and the signal-to-noise ratio at the output. It characterizes how much noise was added by a specific block or system (Eq. 2.1).

$$F = \frac{SNR_{in}}{SNR_{out}} \tag{2.1}$$

Noise Figure (NF) is the Noise Factor expressed in decibels (dB), Eq. 2.2.

$$NF = 10\log_{10}(F)$$

(2.2)

#### 2.1.2 Sensitivity

Sensitivity of an RF receiver is defined as the *minimum detectable signal* (MDS) that a system can perceive with acceptable signal-to-noise ratio (RAZAVI, 2012). Since  $SNR_{in}$  can be given by the ratio between input power ( $P_{sig}$ ) and input noise power given by kTB, where k is the Boltzmann constant, T is the absolute temperature in Kelvin and B is the noise equivalent bandwidth, Eq. 2.1 can also be presented as Eq. 2.3.

$$F = \frac{P_{sig}/(kTB)}{SNR_{out}}$$

(2.3)

Sensitivity is given by Eq. 2.4 when the minimum  $SNR_{out}$  necessary for baseband detection is considered.

$$S = P_{sig,min} = F.SNR_{out,min}.kTB$$

(2.4)

#### 2.1.3 Maximum Input Signal and Dynamic Range

The *maximum input signal* that can be accepted by a system is limited by system linearity requirements. The difference between the maximum input signal and MDS is defined as *dynamic range* (DR).

#### 2.1.3.1 Linearity

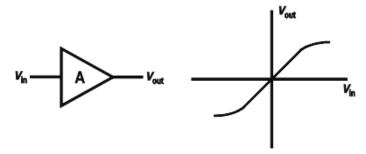

In an ideal (linear) system, the output is linearly related to the input. In real systems, however, circuits are usually nonlinear to a certain extent. The example below helps to better understand the linearity requirements of a system. The system illustrated in Figure 2.1 presents a typical nonlinear memory-less behavior that can be represented by a truncated power expansion series (Eq. 2.5) (ROGERS; PLETT, 2003).

$$v_{out} = a_0 + a_1 v_{in} + a_2 v_{in}^2 + a_3 v_{in}^3$$

(2.5)

In the equation,  $v_{in}$  corresponds to the system input voltage,  $v_{out}$  to the output voltage and  $a_0$ ,  $a_1$ ,  $a_2$  and  $a_3$  are coefficients that characterize system linearity. In receivers, the output curve is usually compressed as shown in Figure 2.1 and consequently  $a_3$  assumes a negative value.

Source: The Author.

A common way to measure linearity is through a test denominated *two-tone test*. In this test, two signals with different angular frequencies are presented to a system, such as the amplifier in Figure 2.1 (Eq. 2.5).

$$v_{in} = v_1 \cos \omega_1 t + v_2 \cos \omega_2 t \tag{2.6}$$

Eq. 2.7 is obtained when signal  $v_{in}$  is applied to the transfer function given by Eq. 2.5.

$$v_{out} = a_0 + a_1(v_1 \cos \omega_1 t + v_2 \cos \omega_2 t) + a_2(v_1 \cos \omega_1 t + v_2 \cos \omega_2 t)^2 + a_3(...)^3 \quad (2.7)$$

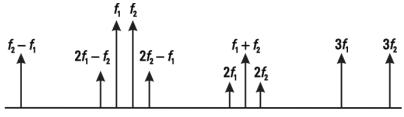

After simplification using trigonometric identities in Eq. 2.7, many different frequency components appear, such as: DC (zero frequency component),  $\omega_1$ ,  $\omega_2$ ,  $\omega_1 \pm \omega_2$ ,  $\omega_2 \pm \omega_1$ ,  $3\omega_1$ ,  $3\omega_2$ ,  $2\omega_1 \pm \omega_2$ ,  $2\omega_2 \pm \omega_1$ .

In Eq. 2.7, second order terms generate components at *DC*, second harmonics and the combination of input frequencies:  $\omega_2 \pm \omega_1$ . For instance:

$$(v_1\cos\omega_1 t + v_2\cos\omega_2 t)^2 = \frac{v_1^2}{2} + \frac{v_2^2}{2} + \frac{v_1^2}{2}\cos 2\omega_1 t + \frac{v_2^2}{2}\cos 2\omega_2 t + v_1v_2\cos(\omega_1 \pm \omega_2)t \quad (2.8)$$

Third order terms generate components in the fundamental frequency, third harmonics and the combination of frequencies:  $2\omega_1 \pm \omega_2$  and  $2\omega_2 \pm \omega_1$ .

$$(v_1 \cos \omega_1 t + v_2 \cos \omega_2 t)^3 = v_1 \left(\frac{3}{4}v_1^2 + \frac{3}{2}v_2^2\right) \cos \omega_1 t + v_2 \left(\frac{3}{4}v_2^2 + \frac{3}{2}v_1^2\right) \cos \omega_2 t$$

$$+\frac{3}{4}v_1^2v_2\cos(2\omega_1\pm\omega_2)t + \frac{3}{4}v_1v_2^2\cos(2\omega_2\pm\omega_1)t + \frac{v_1^3}{4}\cos 3\omega_1t + \frac{v_2^3}{4}\cos 3\omega_2t \quad (2.9)$$

Of particular interest are the fundamental frequency and the third order combination of frequencies because they are close to the fundamental and can appear inside the frequency band of a receiver. Figure 2.2 shows the second harmonics in black and the third harmonics in gray at the output of the modeled system.

Figure 2.2: Combination of harmonics for the modeled system.

Source: Adapted from (ROGERS; PLETT, 2003).

#### 2.1.3.2 Third Order Intercept Point

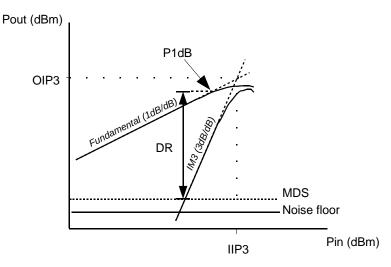

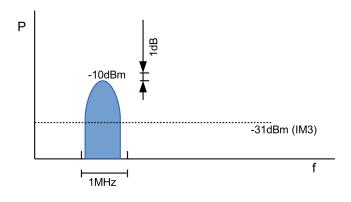

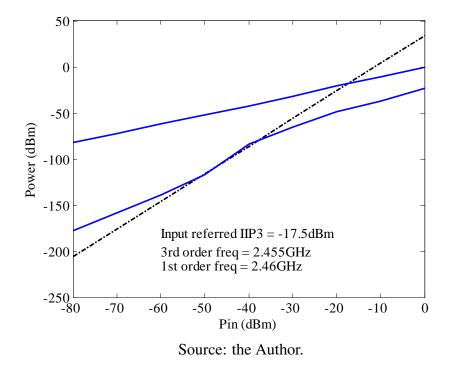

By varying the amplitude of the input signals in a two-tone test, the fundamental output and the intermodulation output power can be plot as a function of the input power resulting in a graph such as presented in Figure 2.3. From the plot, the *third order intercept point* (IP3), a theoretical extrapolation point where the amplitude of the intermodulation tones  $(2\omega_1 - \omega_2 \text{ and } 2\omega_2 - \omega_1)$  are equal to the amplitudes of the fundamental tones is established.

With two tones of same amplitude  $v_1 = v_2 = v_i$ , the sum of the components of Eq. 2.6 that appear in the fundamental frequency is given by 2.10 (ROGERS; PLETT, 2003).

$$v_{fund} = a_1 v_i + \frac{9}{4} a_3 v_i^3 \tag{2.10}$$

The component amplitudes that appear at the third order intermodulation tones (IM3) are given by Eq. 2.11.

$$v_{IM3} = \frac{3}{4}a_3v_i^3 \tag{2.11}$$

IP3 extrapolation point can be calculated when the linear component of Eq. 2.10 is equal to the IM3 component of Eq. 2.11. It is important to observe that as presented from the beginning  $v_{IP3}$  is defined in peak voltage values.

$$v_{fund} = v_{IM3} \Rightarrow \alpha_1 v_i = \frac{3}{4} a_3 v_i^3 \Rightarrow v_{IP3} = v_i = \sqrt{\frac{4a_1}{3|a_3|}}$$

(2.12)

In Figure 2.3, it can be observed that the slope of the fundamental line is 1 dB/dB while the slope of the IM3 line is 3 dB/dB. The extrapolation point defines both *input 3rd* order intercept point (IIP3) and output 3rd order intercept point (OIP3).

Figure 2.3: Output power of fundamental and IM3 versus input power.

Source: the Author.

Linearity figures are usually measured in dBm, or decibel referred to 1 mW (Eq. 2.13).

$$P_{dBm} = 10 \log_{10}(P_W / 1 \ mW) \tag{2.13}$$

#### 2.1.3.3 1dB Compression Point

Figure 2.3 also shows the definition of MDS (sensitivity), dynamic range and 1 dB compression point (P1dB) that defines the dynamic range.

P1dB is defined as the point where the power level at the output is 1 dB compressed. The definition of compression point establishes the use of one tone instead of two tones. The fundamental components are given by Eq. 2.14.

$$v_{fund} = \alpha_1 v_i + \frac{3}{4} a_3 v_i^3 \tag{2.14}$$

When compared to Eq. 2.10 the result is slightly different and the measurements usually do not match when compression point is calculated through both methods. The (*one-tone*) compression point can be calculated by Eq. 2.15.

$$v_{1dB} = \sqrt{0.145 \frac{a_1}{|a_3|}} \tag{2.15}$$

*P1dB* compression point and *IIP3* are related. Eq. 2.16 can be easily obtained through equations 2.12 and 2.15.

$$IIP3 \cong P1dB + 9.6 \tag{2.16}$$

It is important to emphasize that while Eq. 2.12 was obtained in a two-tone test, Eq. 2.15 was obtained in a one-tone test. Consequently, this approximation holds only if only one-tone is producing the distortion during signal compression. In a two-tone test it is not possible to observe both results at the same time<sup>1</sup>.

#### 2.1.3.4 Second Order Intercept Point

Second order intercept point (IP2) is also of interest, specially when working with direct conversion or low IF (Intermediate Frequency) receivers because the second order products appear at DC or at low frequencies  $(\omega_2 - \omega_1)$ .

From Eq. 2.8, it is easy to show that DC component amplitudes due to the second order intermodulation tones (IM2) are given by Eq. 2.17, since  $v_i = v_1 = v_2$ .

$$v_{IM2} = a v_i^2 \tag{2.17}$$

Consequently, the slope would be 2 dB/dB in a plot like Figure 2.3 and  $v_{IP2}$  can be solved as Eq. 2.18. IIP2 is usually tens of decibels higher than IIP3.

$$v_{fund} = v_{IM2} \Rightarrow a_1 v_i = a_2 v_i^2 \Rightarrow v_{IP2} = \frac{a_1}{a_2}$$

(2.18)

#### 2.1.4 Gain, Linearity and Noise Factor of Cascaded Stages

The first stage in a receiver is the main responsible for the overall system noise factor. When it comes to linearity, on the other hand, first stages have less impact. Consequently, in receiver design it is very important to know where to put effort in improving linearity or noise factor.

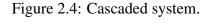

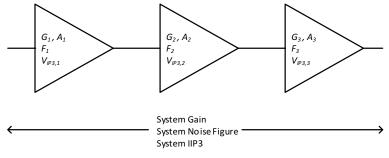

Figure 2.4 shows a system of cascaded amplifiers. In the figure,  $F_i$ ,  $G_i$ ,  $A_i$  and  $v_{IP3,i}$  are noise factor, available power gain, gain and IIP3 of block *i*. Cascaded gain is defined by Eq. 2.19 and total noise factor (*F*) is given by the relation known as Friis equation (Eq. 2.20).

$$G = G_1 G_2 G_3 \tag{2.19}$$

$$F = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \dots$$

(2.20)

In Eq. 2.20, G is the available power gain and it takes into account both matching and the difference between source and load impedances of each block. In this sense, it is different than the traditional power gain defined by Eq.2.21 when equal input and output impedances are considered not accounting for matching.

$$powergain = A_1^2 \tag{2.21}$$

The worst case IIP3 of such a system is given by Eq. 2.22. Good linearity is represented by higher IP3 values. Consequently, if the stages at the front of the receiver chain have higher gains then latter stages are more critical in terms of linearity.

<sup>&</sup>lt;sup>1</sup>Some simulation tools make this measurement possible since they can use one tone that produces distortion and one tone that does not. It is an analysis of large signal usually using *Harmonic Balance method* performed together with a small signal analysis. Cadence SpectreR $F^{TM}$  analysis *PSS* and *PAC* used together can provide this result. Nevertheless, this type of measurement is only valid for receivers.

$$\frac{1}{v_{IIP3}^2} = \frac{1}{v_{IP3,1}^2} + \frac{A_1^2}{v_{IP3,2}^2} + \frac{A_1^2 A_2^2}{v_{IP3,3}^2} \dots$$

(2.22)

In fact, Eq. 2.22 is an approximation. More precise calculations or simulations must be performed to better predict the overall system IIP3 (RAZAVI, 2012). The result predicted by the equation is more pessimistic and consequently implies in a larger design effort.

Source: the Author.

Although equations 2.20 and 2.22 were initially developed for amplifiers, they are also valid for mixers and filters and are readily applicable in the receiver design. For this calculation in the mixer case, the mixing or frequency translation effect have to be also considered.

#### 2.2 Receiver Architectures

This section reviews traditional and modern receiver architectures focusing on a brief discussion about the advantages and disadvantages of each topology.

#### 2.2.1 Direct Conversion Receiver

A direct conversion architecture (Figure 2.5) is characterized by a direct translation of the received signal to baseband in a single step. The first block in the receiver chain is denominated *low noise amplifier* (LNA) and is the main responsible for the noise figure of the system, as discussed in Section 2.1.4. Therefore, it needs to provide moderate gain while introducing little noise. The output of the LNA is downconverted directly to the baseband by the quadrature mixer. The highest gain in the receiver chain is provided by the baseband amplifier. The baseband amplifier usually has programmable gain and offset correction circuits due to requisites of the dynamic range of the analog-to-digital converter (ADC) and to the offset voltage introduced by the mixer circuit. Frequency generated by the local oscillator (LO) or synthesizer is at the center of the channel and must cover the complete frequency range.

The main advantages of this architecture are (TUTTLEBEE, 2002):

- low complexity, suitable for integrated circuit realization ;

- reduced number of blocks (when compared to the multiple conversion architecture to be presented following);

- simple filtering requirements.

Some disadvantages are:

- quality in-phase and quadrature signal generation is necessary over the complete frequency range;

- balanced mixers are necessary in order to better reject the oscillator fundamental frequency at the output and to reduce oscillator leakage to the input<sup>2</sup>;

- the second order distortion product falls *in-band*;

- 1/f noise can not be eliminated and may become a severe noise problem.

Figure 2.5: Direct conversion architecture.

Source: the Author.

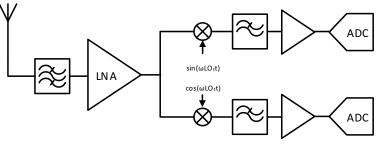

#### 2.2.2 Heterodyne Receiver

In a heterodyne architecture, the received signal is translated to the baseband in multiple steps, originating intermediate frequencies. This approach minimizes some of the problems presented by the direct conversion, such as *LO self mixing* and second order distortion but it adds complexity to the system, and usually increases power consumption. A possible implementation of an heterodyne architecture is presented in Figure 2.6 (RAZAVI, 2012).

Its main advantages are:

- better selectivity (a channel filter is added after the first mixer);

- gain is distributed over several amplifiers in different frequency bands, which leads to an easier implementation;

- the first mixer is not a quadrature mixer.

Its main disadvantages are:

- high complexity: many blocks and consequent higher power consumption;

- more local oscillator signals have to be generated;

- highly selective IF filters are required to remove signal image, making it hard to obtain single chip realizations.

<sup>&</sup>lt;sup>2</sup>Local oscillator leakage to the input of the mixer can be reflected by the LNA, the antenna or by external obstacles returning back to the antenna, being amplified by the LNA and downconverted back to a DC component that is *in band* in this architecture. This *time varying* DC offset caused by *self-mixing* is a typical problem of the direct conversion architecture (TUTTLEBEE, 2002; RAZAVI, 2012).

In a heterodyne architecture, the second mixer can be implemented digitally with stronger requirements for the ADC or using analog components with additional requisites for the synthesizer, and additional filters as well.

Source: the Author.

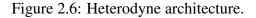

#### 2.2.3 Sliding IF Architecture

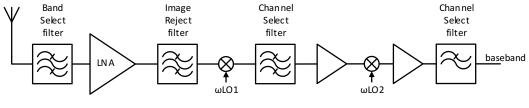

Recently, sliding IF architectures have been adopted as a means to simplify receiver design of multiple conversion architectures using only one synthesizer (RAZAVI, 2012; LIU et al., 2014). They use frequency division in order to generate different clocks, emulating different local oscillators. As a consequence, the first IF frequency varies according to the selected channel. This characteristic can be observed in Figure 2.7.

The main advantages of this architecture are:

- the first mixer is not a quadrature mixer;

- only one local oscillator is required;

- no problem of second order distortion or 1/f noise.

The main disadvantage is the high complexity of the architecture.

Figure 2.7: Sliding IF architecture .

Source: the Author.

#### 2.2.4 Image-Reject Architecture

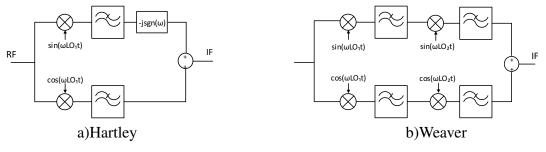

The need for a filter to remove image in a heterodyne receiver makes it generally unsuitable to integrated circuit implementation. Alternative implementations make use of different strategies to cancel image without the need of high performance filtering, like *Hartley* and *Weaver* architecture presented in Figure 2.8a and 2.8b respectively(RAZAVI, 2012).

Hartley architecture uses a Hilbert filter to eliminate the image, while Weaver architecture needs two different quadrature local oscillators to achieve image cancellation. In both cases,  $LO_1$  can have tough requirements because of the quadrature implementation at a higher frequency. The implementation of a Hilbert filter, though traditional in analog design, may present some difficulties in CMOS due to resistors and capacitors mismatches (RAZAVI, 2012).

Source: the Author.

#### 2.2.5 Low-IF and High-IF Architectures

Low-IF and high-IF architectures are alternatives that combine advantages both from direct conversion and heterodyne architectures. In a low-IF receiver, the IF is chosen as half the bandwidth of the signal (RAZAVI, 2012), while high-IF have IF bigger than signal bandwidth. Low-IF or high-IF architectures reduce requirements of image rejection. Image rejection will be partly performed in the digital domain, after analog-to-digital conversion. Additionaly, since it does not convert the signal directly to baseband it avoids problems with DC offset, flicker noise and IP2.

Its main advantages are:

- less DC Offset problems;

- lower complexity than the heterodyne approach.

Its main disadvantages are

- need of a better image rejection when compared with direct conversion architectures;

- higher ADC sampling rate is required.

### 2.3 Discrete-Time Receivers

The feasibility of discrete-time (DT) receiver architectures has been presented in several applications, e.g. Bluetooth (STASZEWSKI et al., 2004), GSM (MUHAMMAD et al., 2005), WLAN (JAKONIS et al., 2005), and SDR (BAGHERI et al., 2006a). They offer several advantages when compared to continuous time (CT) receivers, mainly when implemented in new deep sub-micron technologies, e.g. due to the excellent component matching of capacitors and the possible implementation of programmability to compensate for process, voltage and temperature (PVT) variations (RU; KLUMPERINK; NAUTA, 2007).

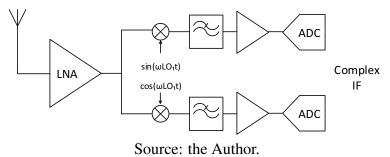

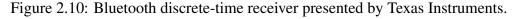

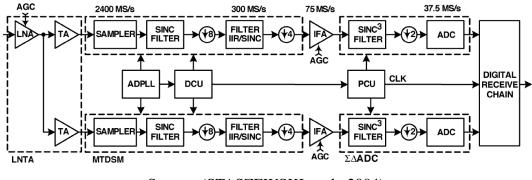

Figures 2.10 and 2.11 present a commercial and an academic discrete-time receiver proposed (STASZEWSKI et al., 2004; BAGHERI et al., 2006a). In the first architecture, the signal is directly subsampled after amplification by a low noise transconductance amplifier (LNTA) and, in the second structure it is downconverted by an analog high linearity mixer after LNA amplification. The main difference between the two architectures is the interface between LNA/LNTA and sampler/mixer. The adoption of a current input and current output in the sampler insert additional filtering due to the windowing effect that is detailed in the next sections. In both cases, filter processing is performed in the discrete-time domain after downconversion.

Source: (STASZEWSKI et al., 2004).

Figure 2.11: Wideband discrete-time receiver.

Source: (BAGHERI et al., 2006a).

The functional blocks typically adopted in DT receivers for downconversion and filtering are sampling mixers, finite impulse response (FIR) filters, and infinite impulse response (IIR) filters. Below, these blocks are briefly described.

#### 2.3.1 Sampling Mixer

In the first DT architecture presented in this section (Figure 2.10), a sampler is adopted for the downconversion instead of a traditional active mixer. In DT receivers, RF sampling is performed in voltage or in charge domain, in both cases using a subsampling technique since Nyquist sampling is usually not feasible. Both voltage sampling and charge sampling cases were analyzed in detail in (XU; YUAN, 2000).

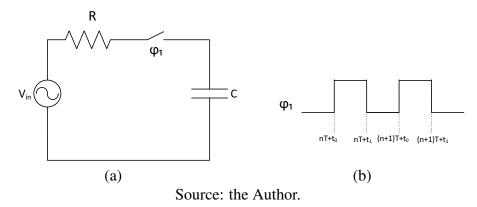

The structure of the voltage sampling mixer is presented in Figure 2.12. The time needed to acquire the voltage sample depends on a time constant  $\tau = RC$ . The product between the time constant and the frequency of the sampled signal ( $\tau\omega$ ) has to be minimized to reduce the group delay introduced by the circuit (should be less than 0.1 according to (XU; YUAN, 2000)). The circuit requires a trade off since a small sampling capacitance reduces the group delay but increases the error voltage due to the clock feedthrough (EICHENBERGER; GUGGENBUHL, 1991).

Figure 2.12: (a) Voltage sampling principle. (b) Clock waveform.

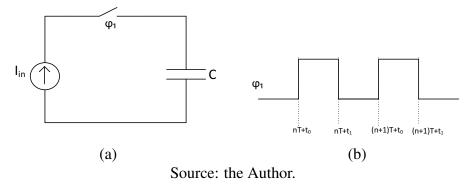

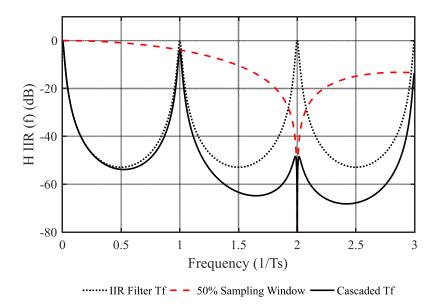

The charge sampling approach is presented in Figure 2.13. The charge  $q_{in}$  is integrated over the capacitor C from  $t_0$  to  $t_1$  in the *sample phase*, to be *hold* until the end of the period. Charge sampled in the previous interval can be discharged during a reset phase, as presented in (XU; YUAN, 2000), or added to the charge stored in the capacitor during previous samples, as presented in Figure 2.13.

Figure 2.13: (a) Charge sampling principle. (b) Clock waveform.

To analyze the charge sampling process, we start with the definition of a discrete-time series of the voltage over the capacitor at time n (Eq. 2.23), as proposed in (NIKOLIC; BORIVOJE, 2011):

$$v_{out}[n] = \frac{q_{in}[n]}{C} + v_{out}[n-1]$$

(2.23)

$$q_{in}[n] = \int_{nT+t_0}^{nT+t_1} i(t) dt$$

(2.24)

where  $q_{in}[n]$  is the charge packet created at the sampling time *n* and *T* is the sampling period.

The charge packet  $q_{in}[n]$  can also be represented as a continuous-time convolution between the input signal i(t) and a windowing function p(t) that shapes the sampling pulses and acts as a continuous-time filter (Eq. 2.25 and 2.26).

$$q_{in}[n] = \int_{nT}^{nT+\delta T} i(\tau) p\left((nT+\delta T) - \tau\right) d\tau$$

(2.25)

$$p(t) = \begin{cases} \frac{1}{\delta T}, & if \ 0 \le t \le \delta T \\ 0, & otherwise \end{cases}$$

(2.26)

where  $\delta T = t_1 - t_0$ , and amplitude  $\frac{1}{\delta T}$  of the filter is used to normalize its DC gain to 0 dB.

In the frequency domain, the transfer function in modulus of the windowing filter is:

$$|H_p(\omega)| = \frac{\sin\left(\frac{\omega\delta T}{2}\right)}{\frac{\omega\delta T}{2}} = \operatorname{sinc}\left(\frac{\omega\delta T}{2}\right)$$

(2.27)

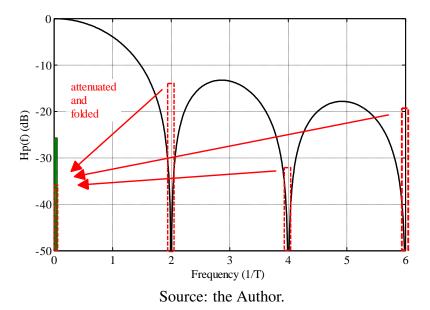

Figure 2.14 shows the transfer function (Eq. 2.27) obtained when  $\delta T$  is chosen as 50 % of the sampling period. In the figure, it is possible to observe that there is a built-in anti-aliasing effect characterized by a strong attenuation at even multiples of the sampling frequency 1/T. This anti-aliasing effect is not observed in voltage sampling.

Besides being attenuated by the windowed integration sampler (WIS), signals at these nulls are also folded to DC (BAGHERI et al., 2006; TOHIDIAN; MADADI; STASZEWSKI, 2014).

Besides the built-in anti-alisiasing filter effect, charge sampling offers several advantages over voltage sampling in newer technologies (XU; YUAN, 2000, 2005), such as:

- linear phase shift and constant group delay (also sampling capacitor can be designed to minimize clock feedthrough independently of group delay);

- thermal noise is reduced since it is shaped by the sampling window;

- error from charge sampling due to jitter does not increase at higher frequencies.

Figure 2.14: 50 % duty-cycle charge sampling transfer function. ( $Matlab^{TM}$ )

#### 2.3.2 Infinite Impulse Response Filter

In the charge sampling circuit presented in Figure 2.13, there is both a discrete-time integrator and a sampler circuit. The discrete-time integrator can also be modeled as a running sum of the input charge packets over time.

Consider  $q_H[n]$  the total charge contained by the capacitor  $C_H$  at the sample time *n*.

$$q_H[n] = q_H[n-1] + q_{in}[n]$$

(2.28)

The transfer function of the ideal discrete-time integrator in the z-domain is given by :

$$\frac{Q_H(z)}{Q_{in}(z)} = \frac{1}{1 - z^{-1}} \tag{2.29}$$

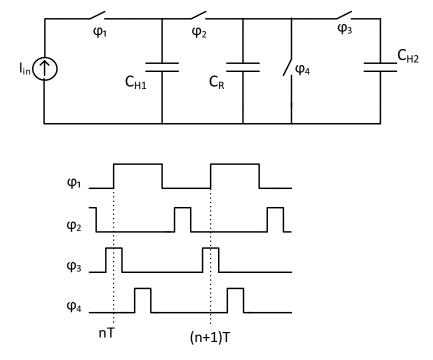

As presented in Figure 2.15 adapted from (NIKOLIC; BORIVOJE, 2011), a generic IIR filter can be implemented as a cascade of two discrete-time lossy-integrators. The term 'lossy' is adopted because part of the charge originally residing in  $C_H$  intentionally 'leaks' to  $C_R$  in the next phase.

The first DT lossy-integrator is formed by  $C_{H1}$  and  $C_R$ , with the transfer function given by:

$$\frac{Q_{H1}(z)}{Q_{in}(z)} = \frac{1}{1 - \alpha_1 z^{-1}}$$

(2.30)

where  $\alpha_1 = C_{H1}/(C_{H1} + C_R)$  represents the charge ratio kept in  $C_{H1}$  and  $\beta_1 = C_R/(C_{H1} + C_R)$  is the ratio of the charge transferred (by the *lossy* integration in the process) to  $C_R$  in  $\varphi_2$ .

And the second DT lossy-integrator is formed by  $C_R$  and  $C_{H2}$ , with transfer function given by:

$$\frac{Q_{H2}(z)}{Q_R(z)} = \frac{1}{1 - \alpha_2 z^{-1}}$$

(2.31)

Figure 2.15: IIR discrete-time implementation.

Source: the Author.

where  $\alpha_2 = C_{H2}/(C_{H2} + C_R)$  is the charge ratio transferred from  $C_R$  to  $C_{H2}$  in  $\varphi_4$ .

As shown in the complete circuit (Figure 2.15), charge is first transferred from  $C_{H1}$  to  $C_R$ , and subsequently transferred from  $C_R$  to  $C_{H2}$ . During phase  $\varphi_3$ , the intermediate charge in  $C_R$  is removed.

The complete transfer function of this IIR filter, without considering the charge sampling effect created by  $\varphi_1$  (presented in Section 2.3.1), is given by:

$$\frac{V_{H2}(z)}{Q_{in}(z)} = \frac{\beta_1/C_{H2}}{(1 - \alpha_1 z^{-1})(1 - \alpha_2 z^{-1})}$$

(2.32)

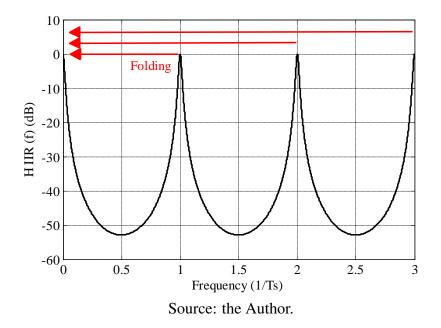

Figure 2.16 presents the normalized IIR filter transfer function (Eq. 2.32). The transfer function presented in the figure is ideal and does not include the pulse shape effect. Since it is a discrete-time filter, the transfer function of this low pass filter is repeated with the period of the sampling rate  $(1/T_s)$ , as presented in the figure. Based on the Nyquist sampling theory, sampling a continuous time signal will fold components at multiples of the sampling rate to DC, as shown in the the figure.

The attenuation of the filter at  $0.5/T_S$  is given by:

$$Atten_{1/2} = 20 \log_{10} \left( \frac{C_R^2}{(C_R + 2C_{H1}) (C_R + 2C_{H2})} \right)$$

(2.33)

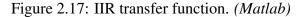

When the pulse sampling effect is considered in the 50% duty-cycle case proposed in Figure 2.15, there is a strong attenuation of the even replicas of the signal as can be observed in Figure 2.17.

#### 2.3.3 Finite Impulse Response Filter

A finite impulse response (FIR) filter can be used to implement a decimation filter, typically used in a multirate DT receiver as an anti-aliasing filter for the process of down-

Figure 2.16: IIR transfer function. (Matlab)

Source: the Author.

sampling.

The simplest realization is an N-stage FIR filter with uniform tap weights (BAGHERI et al., 2006b; KARVONEN, 2006), where N corresponds to the decimation factor.

$$H_2(z) = \frac{1 - z^{-N}}{1 - z^{-1}} = 1 + z^{-1} + z^{-2} + \dots + z^{-(N-1)}$$

(2.34)

Figure 2.18 presents a simplified implementation of a FIR filter, also known as a moving-average filter in this case. In the circuit, three charge samples are integrated in

the capacitor C. The charge is removed from the capacitor at phase  $\varphi_3$  after read in phase  $\varphi_2$ , implementing a 3-stage FIR filter.

Figure 2.18: FIR DT implementation.

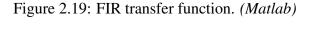

The transfer function of the 3-stage FIR decimation filter is presented in Figure 2.19. In the plot, the nulls at multiples of  $f_s/N$ , implement the anti-aliasing filter and define the stopbands. The folding and the window sampling effect are also illustrated in the figure.

Source: the Author.

#### 2.4 State of the Art in BLE Receiver Design

This section discusses receiver architectures recently presented for low power applications in 2.4 GHz targeting BLE Standard.

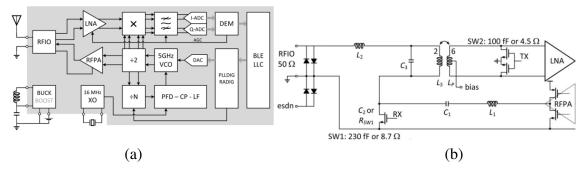

Initially, two sliding-IF receivers are presented in Figures 2.20 and 2.21. As presented before, both alternatives adopt a real (non-quadrature) mixer for the first stage to reduce power as well as a traditional common-source cascoded LNA for the first stage filtering and input matching.

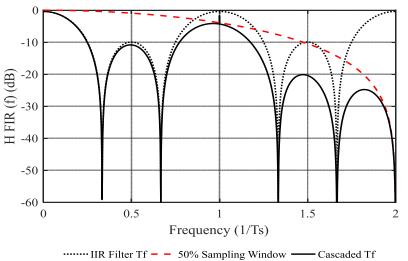

The first approach (LIU et al., 2013) uses a push-pull active mixer with single input and differential output and  $f_{LO} = f_{RF} * 4/5$ , with a consequent bigger IF and better image rejection. The second approach (WONG et al., 2012) adopts a Gilbert-cell mixer with one input tied to AC ground, and a consequent 6 dB loss in gain, and  $f_{LO} = f_{RF} * 16/17$ . Both receivers use complex IQ passive mixers for the frequency translation to baseband, but with some differences. The first approach uses a 25 % duty-cycle LO, and the second receiver uses a 50 % duty-cycle LO mixer that is pre-amplified by an IF buffer. Both receivers also adopt an analog programmable buffer with filtering and DC offset correction for the baseband amplification. The receivers consume 3.6 mW and 6.5 mW of power respectively with roughly the same performance, as presented in Table 2.1 at the end of this section.

Figure 2.20: (a) Sliding-IF BLE receiver for Zigbee and Bluetooth. (b) RF front-end receiver with push-pull mixer.

Source: (LIU et al., 2013).

(b)

(a)

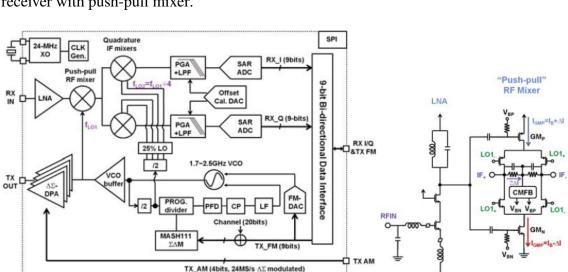

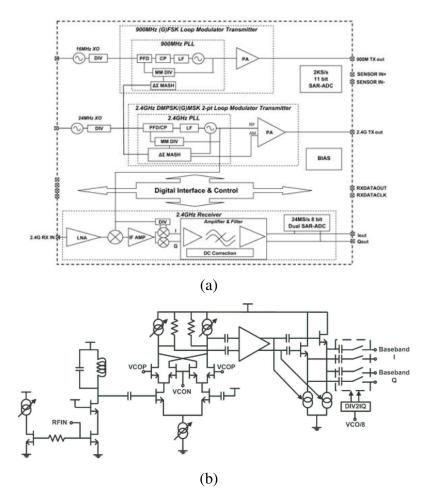

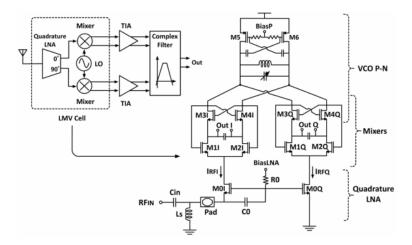

Figure 2.22 proposes a Low IF receiver that uses an LNA-Mixer-VCO (LMV) approach for first stage (SELVAKUMAR; ZARGHAM; LISCIDINI, 2015). Two main strategies are applied in this receiver in order to reduce the power consumption: quadrature LNA is implemented to allow for a simpler non-quadrature VCO, and current supply is reused by LNA, mixer and VCO. Finally, the low IF signal is amplified by transimpedance amplifiers (TIA) and filtered by a complex filter centered in 2 MHz. The result is an impressive sub-1 mW power consumption with an acceptable NF of 15 dB, since BLE requires 19 dB for a -80 dBm sensitivity target (Table 2.1).

Figure 2.21: (a) Sliding-IF BLE receiver for biotelemetry application. (b) RF front-end detail.

Source: (WONG et al., 2012); (WONG et al., 2013).

Figure 2.22: BLE receiver using LMV front-end.

Source: (SELVAKUMAR; ZARGHAM; LISCIDINI, 2015).

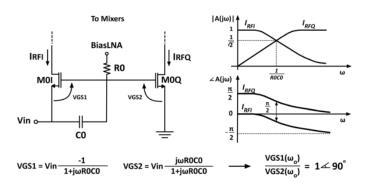

The quadrature LNA of the LMV receiver is detailed in Figure 2.23. It is a commonsource, common-gate single-input, with an RC passive  $90^{\circ}$  phase shifter. The matching between I and Q is sensitive to process variations.

Figure 2.23: Quadrature LNA detail.

Source: (SELVAKUMAR; ZARGHAM; LISCIDINI, 2015).

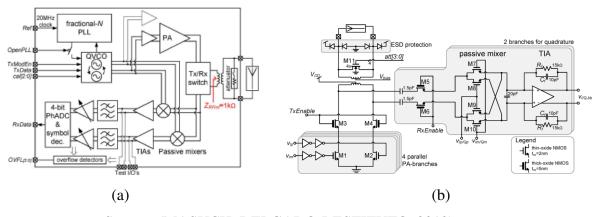

In order to reduce costs, newer BLE approaches aim at integration of the transceiver switch as well as the input matching. Figure 2.24 presents a receiver differential input, an internal transformer and no LNA. Since noise and sensitivity requirements of BLE standard are not challenging, it is possible to achieve 16.5 dB of noise figure without LNA and at a 1.1 mW of power consumption. The integration of the switch and matching is facilitated by TX and RX internal switches that are used to uncouple receiver and transmitter during the Time Division Duplexing (TDD) operation of the standard. The receiver implements a direct conversion strategy using quadrature passive mixers. A 4-bit phasedomain ADC is used for the GFSK demodulation. The overall performance is comparable to the low-IF receiver presented in Figure 2.23 (Table2.1).

Source: (MASUCH; DELGADO-RESTITUTO, 2013).

The last analyzed receiver also integrates the switch, but using a single-input approach (Figure 2.25). The differential LNA is connected to the single input through an internal

passive balun. A switch is placed before the LNA to disconnect it from the input during the transmission. In receiver operation, there is also a switch to disconnect the PA. A differential common-source cascoded LNA is followed by a quadrature mixer using a switched transconductance design in a direct conversion topology. Baseband amplification is implemented using conventional AGC with DC offset-correction. The receiver presents good performance but at a higher power consumption cost when compared to the other analyzed architectures (Table2.1).

Figure 2.25: (a) Integrated switch BLE transceiver. (b) Detail of LNA and PA antenna matching.

Source: (PRUMMEL et al., 2015).

Table 2.1 presents the main figures of the continuous-time BLE receivers analyzed. They offer a good trade-off between power and performance, except for (PRUMMEL et al., 2015) that was chosen also because of the integrated switch.

## 2.5 Summary

This chapter reviewed the main receiver system-level figures such as noise figure, compression point, IIP2, IIP3 and gain. Basic and more advanced receiver architectures were also reviewed with their advantages and disadvantages briefly discussed. Discrete-time receiver techniques were reviewed in more detail to prepare for the receiver development in Chapter 4. For comparison, system-level figures of recently published low power receivers were also presented. As it can be observed in this brief comparison, discrete-time architectures have not been well-explored for BLE applications yet. It indicates that research is still needed in this area.

Zigbee+BLE BLE BLE BLE BLE Standard +MBAN +MBAN Technology 90n 55n 0.12u 0.13u 0.13u (1.0V) 0.25/1/0.97 1 Data rate (MBPS) 1 1 1 Noise Figure (dB)  $\sim 6*$ 6 15.1 16.5 6 IIP3 (dBm) -2.9 -19 --15.8 -Image Reject (dB) 30.5 35 ---100/-98/-96 -84.9 Sensitivity (dBm) -94.5 -96.5 -81.4

11.2\*\*

11.2

DC

2.9

NO

(b)

6.5

6.5/6.7

Sliding IF

2.9

YES

(c)

0.6

0.6

Low IF

0.7

YES

(d)

1.1

1.1

No LNA

2.1

NO

(e)

| Table 2.1: | Comparison | of | state-of-the-art | Bluetooth | Low | Energy | receivers | previously |

|------------|------------|----|------------------|-----------|-----|--------|-----------|------------|

| published. |            |    |                  |           |     |        |           |            |

\* Estimated from paper results. \*\*complete receiver front-end, ADCs, synthesizer, baseband and microprocessor.

3.8

15.2/3.8/3.9

Sliding IF

1.6

YES

(a)

Consumption (mW)

E Efficiency (nJ/b)

Architecture

Rx area (mm<sup>2</sup>)

External components

Reference

(a) (LIU et al., 2013) (b)(PRUMMEL et al., 2015) (c) (WONG et al., 2012)

(d) (SELVAKUMAR; ZARGHAM; LISCIDINI, 2015) (e) (MASUCH; DELGADO-RESTITUTO, 2013)

Source: the Author.

# **3 BLUETOOTH LOW ENERGY RECEIVER REQUIREMENTS**

This chapter describes system-level requirements for a Bluetooth Low Energy receiver (Bluetooth Special Interest Group, 2010). Relaxed Bluetooth specifications were developed for the core system package denominated Bluetooth Low Energy in order to reduce power consumption when compared to the basic rate. Main differences are increased channel separation and reduction in interference performance and out-of-band blocking specifications.

The main receiver specifications for BLE are presented in Table 3.1. These specifications are discussed in more detail in the following sections.

| Preliminary specs          |                                                         |                     |  |  |

|----------------------------|---------------------------------------------------------|---------------------|--|--|

| BW                         | From literature references                              | 1 MHz               |  |  |

| Frequency range            |                                                         | 2400.0 - 2483.5 MHz |  |  |

| $1.SNR_{out}$              | From literature references                              | 21 dB               |  |  |

| 2. Sensitivity             | Required BER of 0.1 %                                   | -70 dBm             |  |  |

| 3.Interference performance | Co-channel interference (C/I)                           | 21 dB               |  |  |

|                            | Adjacent (1 MHz) interference                           | 15 dB               |  |  |

|                            | Adjacent (2 MHz) interference                           | -17 dB              |  |  |

|                            | Adjacent (¿= 3 MHz) interference                        | -27 dB              |  |  |

|                            | Image frequency Interference                            | -9 dB               |  |  |

|                            | Adjacent (1 MHz) interference to in-band image          | -15 dB              |  |  |

| 4. Out of band Blocking    | Interfering signal frequency                            |                     |  |  |

|                            | 30 MHz – 2000 MHz                                       | -30 dBm             |  |  |

|                            | 2003 – 2399 MHz                                         | -35 dBm             |  |  |

|                            | 2484 – 2997 MHz                                         | -35 dBm             |  |  |

|                            | 3000 MHz – 12.75 GHz                                    | -30 dBm             |  |  |

| 5. Intermodulation         | (F0) signal is 6 dB over sensitivity                    |                     |  |  |

|                            | (F1) sine wave                                          | -50 dBm             |  |  |

|                            | (F2) bluetooth signal ( $-F2-F1-=3, 4, 5 \text{ MHz}$ ) | -50 dBm             |  |  |

| 6. Maximum input           |                                                         | -10 dBm             |  |  |

Table 3.1: BLE specifications.

Source: the Author.

## **3.1** System-Level Considerations

### 3.1.1 Sensitivity

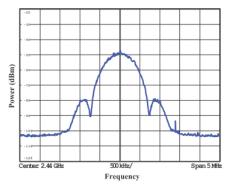

Proposed sensitivity of -70 dBm was specified for short distance application and reduced power consumption and, therefore is not challenging. BLE uses Gaussian Frequency Shift Keying (GFSK) modulation, with a bandwidth-bit period product (BT) of 0.5 and a modulation index of 0.45 to 0.55. Its spectrum is presented in Figure 3.1 (ATAC et al., 2012).

Figure 3.1: Bluetooth Low Energy spectrum.

Source: ATAC et al. (2012)

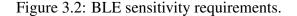

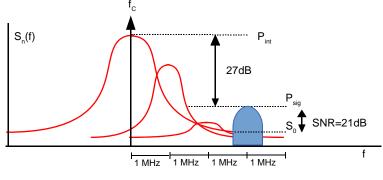

According to (SCHIPHORST; HOEKSEMA; SLUMP, 2002), typical demodulation  $SNR_{out}$  for BLE may vary from 21 dB down to 15 dB. The best reported baseband demodulator indicates a minimum SNR of 11dB for the Bit-Error-Rate (BER) required by the standard of 0.1 % (SCHIPHORST; HOEKSEMA; SLUMP, 2003). Considering 21 dB required  $SNR_{out}$  and a bandwidth (B) of 1 MHz, noise floor and the (worst case) required NF are -114 dBm and 23 dB (Eq. 3.1 and 3.2) at 300 K.

$$Noise floor = KTB = -114 \, \mathrm{dBm}(1 \,\mathrm{MHz}) \tag{3.1}$$

$$NF = S - KTB - SNR_{out} = 23 \, \mathrm{dB} \tag{3.2}$$

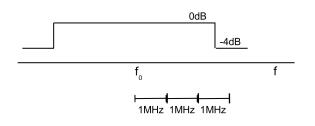

Figure 3.2 presents an ideal scenario with no interferers. Channel separation for BLE is relaxed to 2 MHz while it was previously 1 MHz for high performance Bluetooth.

High gain requirement depends on Analog-to-Digital Converter specification and will be discussed ahead.

## 3.1.2 Linearity

Linearity is established by the standard in terms of interference performance, out-ofband blocking, intermodulation, and maximum input by BLE standard (Bluetooth Special Interest Group, 2010).

#### 3.1.2.1 Interference Performance

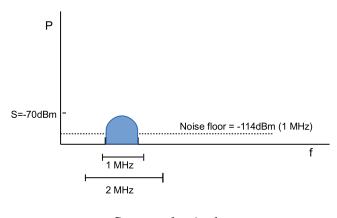

Figure 3.3 presents graphically the worst interferers scenario defined by the standard in Table 3.1 (Bluetooth Special Interest Group, 2010; ATAC et al., 2012). During the

Source: the Author.

interference performance test, a Bluetooth signal 3 dB higher than the sensitivity needs to be demodulated with a BER of 0.1 % in the presence of interferers defined by the mask.

Figure 3.3: Interference performance test.

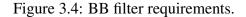

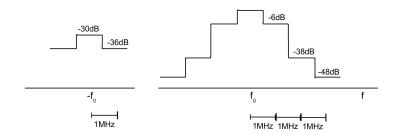

The main idea behind this test is to attenuate the blockers in order not to saturate the ADC. For the baseband filter requirements, a possible solution is to establish a filter mask that attenuates the blocker to the co-channel interference allowed by the standard, resulting in the mask presented in Figure 3.4 (ATAC et al., 2012). These requirements are very challenging for a low-power analog baseband filter and a minimum of six order low-pass filter would be needed. In the figure, the mask for the image filter is also presented on the left.

For an heterodyne receiver, or more specifically, a low IF receiver, the requirements for the IF filtering can be relaxed. It is still important to ensure that the interferers allowed by the standard in Figure 3.3 do not saturate the ADC.

Considering a maximum input of 0 dBm at the ADC, we can calculate the required attenuation of the IF filter using the equation 3.3. The test does not need to be performed using the maximum receiver gain. Consequently, part of the interferers dynamic range can be absorbed by the ADC, with a more relaxed filter mask. Adopting a gain of 44 dB for the calculation, the filter mask shown in Figure 3.5 is obtained.

$$At = P_{out(ADC)} - (P_{int} + gain)$$

(3.3)

Source: the Author.

where  $P_{out(ADC)}$  is the power delivered to the ADC,  $P_{int}$  is the allowed interferer power presented in Figure 3.3, *gain* is the receiver gain used during the test.

In this case, before a downconversion to baseband, a complex signal is available and no image filter is required.

Source: the Author.

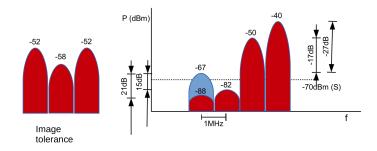

#### 3.1.2.2 Intermodulation

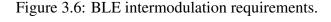

According to the BLE standard, intermodulation is tested with the signal 6 dB higher than the sensitivity. One pure tone and a Bluetooth signal at -50 dBm are tested for intermodulation as shown in Figure 3.6.

$P_{IM3}$  and  $P_{IM2}$  limits are defined at the same level as the acceptable noise in the

channel in a test to detect a signal 6 dB higher than sensitivity (Eq. 3.4).

$$P_{IM3} = P_{IM2} = S + 6 - S/N_{out} \tag{3.4}$$

Considering the sensitivity proposed by the standard and the  $SNR_{out}$  of 21 dB, system requirements are defined by the equations 3.5 and 3.6.

$$P_{IIP3} = \frac{3P_{interf} - P_{IM3}}{2} = -32.5 \,\mathrm{dBm} \tag{3.5}$$

$$P_{IIP2} = 2P_{interf} - P_{IM2} = -15 \,\mathrm{dBm} \tag{3.6}$$

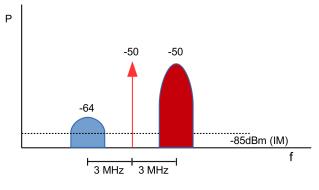

#### 3.1.2.3 Maximum Input

Under low gain assumptions, blocking conditions can be considered as a compression point equal to the maximum acceptable signal proposed by the standard (Figure 3.7),  $P_{1dB} = -10 \text{ dBm+1 dB}$ . Resulting in a *low gain* IIP3 definition,  $P_{IIP3} = P_{1dB} + 9.6 = 0.6 \text{ dBm}$ .

Source: the Author.

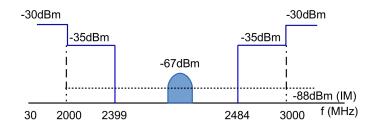

### 3.1.2.4 Out-of-band Blocking

Out-of-band (OOB) blocking is mainly defined in the system by IF filtering and LNA. The BLE standard also defines the required signal for the blocking test as 3 dB above sensitivity at the central frequency of 2440 MHz, as presented with the filter mask in Fig.3.8.

To analyze the compression due to the blockers, we can start from the output signal at the carrier frequency given by Eq. 3.7 (from analysis in Section 2.1.3.1).

$$v_{out} = \left(a_1 v_1 + a_3 \frac{3}{4} v_1^3 + a_3 \frac{3}{2} v_1 v_{interf}^2\right) \cos \omega_1 t \tag{3.7}$$

where  $v_1$  is the carrier and  $v_{interf} = v_2$  is the blocker defined by the mask.

The second term in Eq.3.7 can be ignored since the carrier is much smaller than the blocker, and we can estimate the compression (or reduction) in the gain due to the blocker as:

Source: the Author.

$$\Delta gain \simeq 1 - \frac{3}{2} \frac{|a_3|}{a_1} v_{interf}^2 \tag{3.8}$$

Using the definition of  $v_{IIP3}$  given by Eq. 2.12, and the definition of decibel, it is easy to show that:

$$\Delta gain_{(dB)} \simeq 10 \log_{10} \left( 1 - 2.10^{\left( P_{interf} - P_{IIP3} \right)/10} \right)$$

(3.9)

Considering a margin of 5 dB for compression in the -35 dBm mask to define the compression point ( $P_{1dB}$ ),  $P_{IIP3}$  can be estimated as (Eq.2.16):

$$P_{IIP3} = -35 \, dBm + 5 \, dB(margin) + 9.6 \, dB = -20.4 \, dBm$$

(3.10)

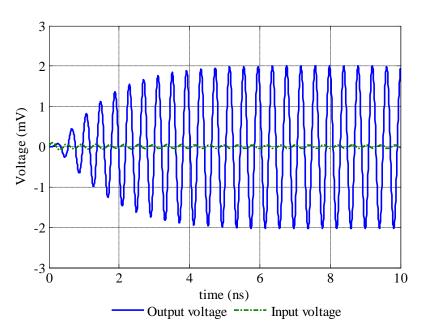

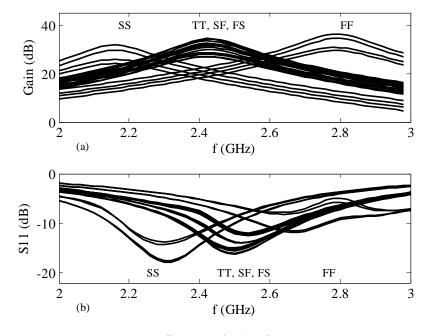

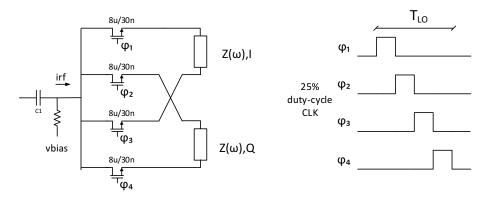

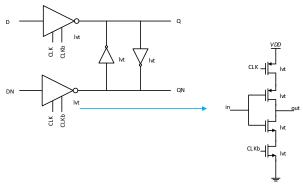

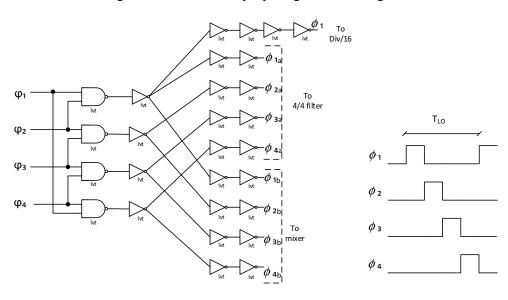

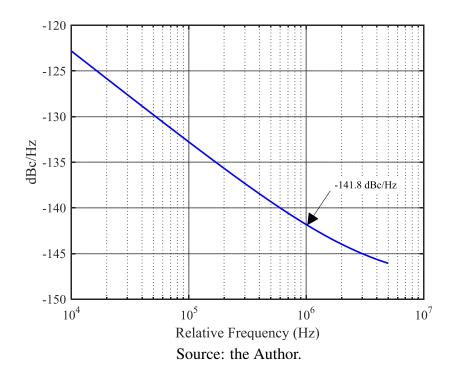

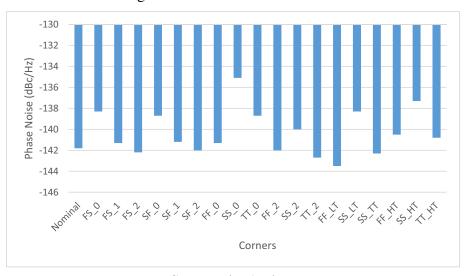

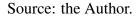

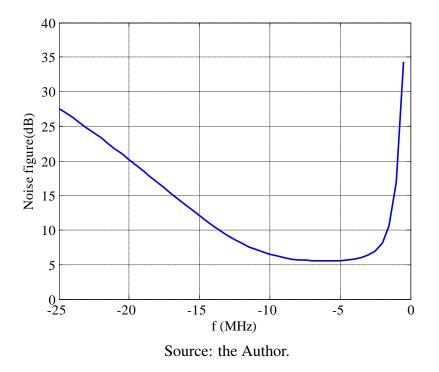

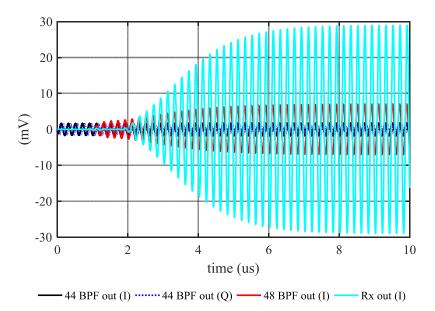

A  $P_{IIP3}$  of -20.4 dBm resulting in an acceptable degradation of 0.3 dB in the gain from Eq.3.9.  $P_{IIP3}$  estimated by Eq.3.10 is a conservative value since LNA filtering and external were not considered in the analysis.