# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO

ANTONIO AUGUSTO DA FONTOURA

# Design Automation for Avionic Reconfiguration Schemes and Schedulability Analysis

Thesis presented in partial fulfillment of the requirements for the degree of Master of Computer Science

Advisor: Prof. Dr. Edison Pignaton de Freitas

Porto Alegre May 2022 da Fontoura, Antonio Augusto

Design Automation for Avionic Reconfiguration Schemes and Schedulability Analysis / Antonio Augusto da Fontoura. – Porto Alegre: PPGC da UFRGS, 2022.

81 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Computação, Porto Alegre, BR– RS, 2022. Advisor: Edison Pignaton de Freitas.

1. Reconfiguration. 2. Avionic Systems. 3. Distributed Real Time Embedded Systems. 4. Schedulability Analysis. 5. Model Checking. 6. Design Automation. I. Pignaton de Freitas, Edison. II. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL Reitor: Prof. Carlos André Bulhões Vice-Reitora: Prof<sup>a</sup>. Patricia Pranke Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas Coordenador do PPGC: Prof. Claudio Rosito Jung Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

"Luck Is What Happens When Preparation Meets Opportunity." — SENECA

## AGRADECIMENTOS

Meus sinceros agradecimentos a todos que de alguma forma contribuíram para o desenvolvimento deste trabalho e que contribuíram com o meu crescimento profissional e pessoal durante esses anos dedicados ao mestrado.

Ao meu orientador, Prof. Dr. Edison Pignaton de Freitas, pela oportunidade e pela confiança depositada em mim. Agradeço pela disponibilidade em responder meus questionamentos, pela paciência, pela troca de experiências e a dedicação em ensinar de forma clara e didática contribuíram muito para meu aprendizado e crescimento.

Aos coatores do artigo previamente publicado, Francisco Assis Moreira do Nascimento e Simin Nadjm-Tehrani, que trouxeram valiosas contribuições ao trabalho.

À universidade por fornecer meios para que alunos que já estão no mercado de trabalho possam realizar seus estudos.

À minha família, em especial à minha esposa, por me apoiar e me incentivar sempre.

## ABSTRACT

Reconfigurable avionics systems can tolerate faults by moving functionalities from failed components to another available system component. This work proposes a distributed reconfigurable architecture for application migration from failed modules to working ones. The feasible system reconfiguration states are determined off-line to provide the expected configuration in foreseen situations. Scheduling analysis is used to determine feasible configurations evaluating specific temporal properties. A case study is used to show the application of the presented approach as a proof of concept. Finally a design automation framework proof-of-concept is implemented and a thoroughly analysis on different algorithms is performed to demonstrate its functionality and flexibility.

**Keywords:** Reconfiguration. Avionic Systems. Distributed Real Time Embedded Systems. Schedulability Analysis. Model Checking. Design Automation.

# Automação de Projeto para Esquemas de Reconfiguração de Aviônicos e Análise de Escalonabilidade

## **RESUMO**

Os sistemas aviônicos reconfiguráveis podem tolerar falhas movendo funcionalidades de componentes com falha para outro componente de sistema disponível. Este trabalho propõe uma arquitetura reconfigurável distribuída para migração de aplicativos de módulos com falha para módulos em funcionamento. Os estados viáveis de reconfiguração do sistema são determinados de forma prévia, ainda na fase de design, para fornecer a configuração necessária nas situações previstas. A análise de escalonabilidade é usada para determinar se os estados provenientes das novas configurações são viáveis avaliando propriedades temporais específicas. Um estudo de caso é usado para mostrar a aplicação da abordagem apresentada como prova de conceito. Por fim, uma prova de conceito do framework de automação de design é implementada e uma análise com diferentes algoritmos é realizada para demonstrar sua funcionalidade e flexibilidade.

**Palavras-chave:** Reconfiguração, Systemas Aviônicos, Systemas Embarcados de Tempo Real Distribuídos, Análise de Escalonabilidade, Model Checking, Automação de Design.

# LIST OF ABBREVIATIONS AND ACRONYMS

- AADL Architecture Analysis and Design Language

- AMP Asymmetric Multi-Processing

- APEX Application Executive

- ARINC Aeronautical Radio, Incorporated

- DAL Design assurance level

- EDF Earliest Deadline First

- EMF Eclipse Modeling Framework

- FAA Federal Aviation Administration

- FDAL Function design assurance level

- FHA Function Hazard Analysis

- FIFO First in First Out

- FPS Fixed Priority Scheduling

- GRM Global Resource Manager

- HDG Hierarchical Dependency Graph

- HMI Human Machine Interface

- IDAL Item design assurance level

- IMA Integrated Modular Avionics

- KPI Key performance indicators

- LRM Local resource manager

- LTA Labeled Timed Automata

- MRO Maintenance, Repair and Overhaul

- PDI Parameter Data Item

- PDIRM PDI Resource Manager

- PPS Priority preemptive scheduling

- QoS Quality of Service

- RMC Resource Manager Client

- RMU Resource Manager Unit

- RSD Reconfiguration States Diagram

- RTOS Real-Time Operating System

- SAE Society of Automotive Engineers

- SLOC Software lines of code

- WCET Worst-case execution time

- OS Operating System

# LIST OF FIGURES

| Figure 3.1  | Reconfigurable System Architecture                                   | .21 |

|-------------|----------------------------------------------------------------------|-----|

| Figure 3.2  | Design Flow Overview                                                 | .24 |

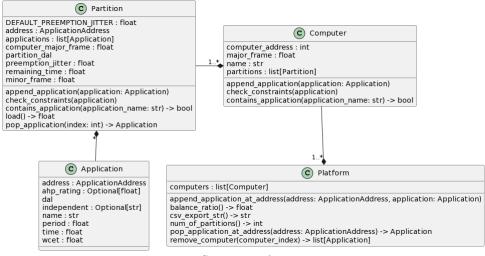

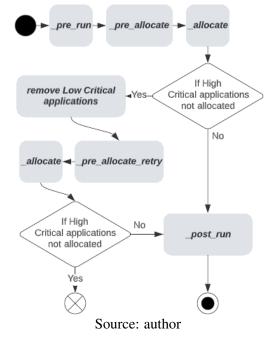

| Figure 3.3  | Platform Meta-model                                                  | .25 |

| Figure 3.4  | A Platform in AADL                                                   | .26 |

| Figure 3.5  | An Application in AADL                                               | .28 |

|             | Example of Hierarchical Dependency Graph                             |     |

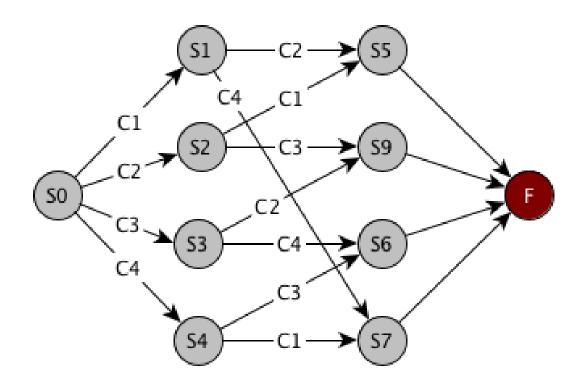

| Figure 3.7  | An Example of Reconfiguration States Diagram                         | .32 |

| Figure 3.8  | Initial System Dependencies                                          | .48 |

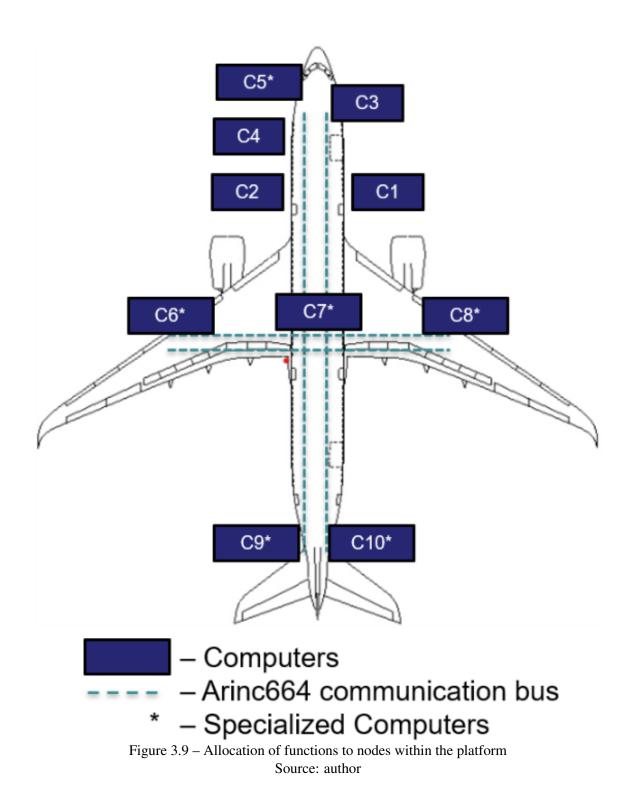

| Figure 3.9  | Allocation of functions to nodes within the platform                 | .49 |

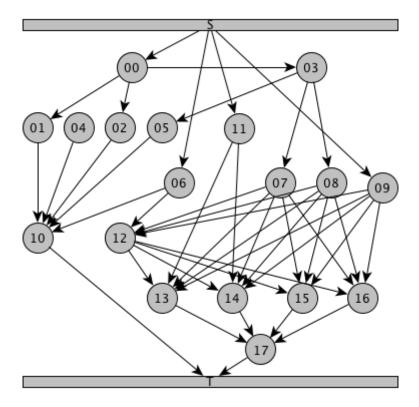

| Figure 3.10 | ) HDG for case study                                                 | .50 |

|             | 1 RSD for case study                                                 |     |

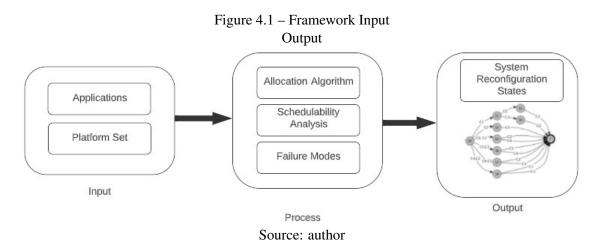

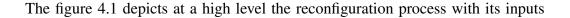

| Figure 4.1  | Framework Input Output                                               | .52 |

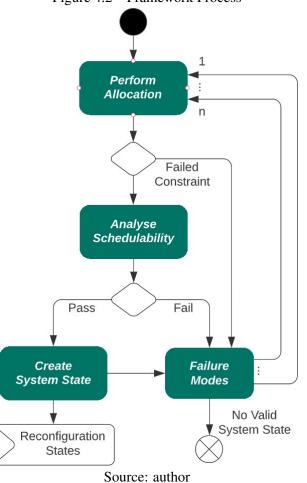

|             | Framework Process                                                    |     |

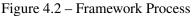

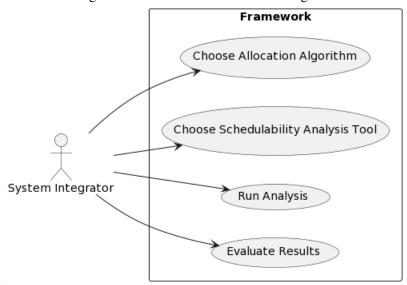

| Figure 4.3  | Framework Use Case Diagram                                           | .56 |

| Figure 4.4  | Platform Class Diagram                                               | .57 |

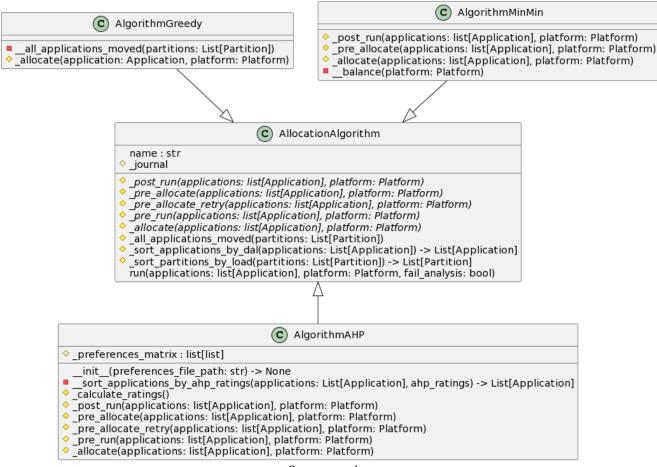

| Figure 4.5  | Allocation Algorithms Class Diagram                                  | .58 |

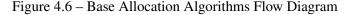

|             | Base Allocation Algorithms Flow Diagram                              |     |

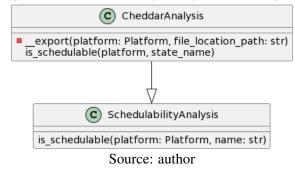

| Figure 4.7  | Schedulability Analysis Class Diagram                                | .59 |

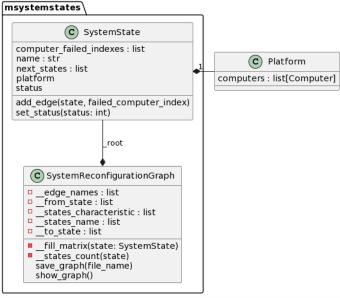

| Figure 4.8  | Reconfiguration (System) States Class Diagram                        | .59 |

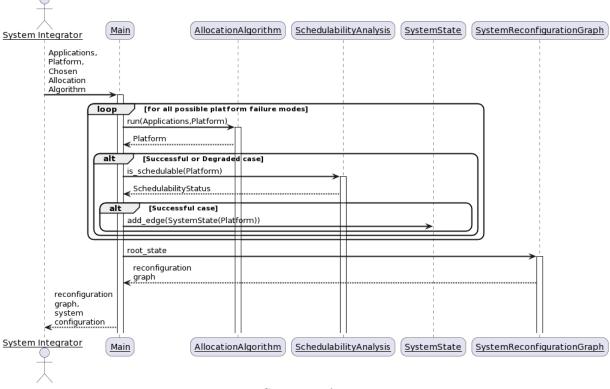

|             | Framework Sequence Diagram                                           |     |

| Figure 5.1  | Average Remaining Failure Rate Budget                                | .67 |

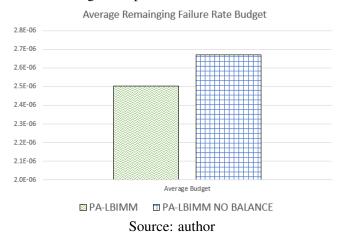

| Figure 5.2  | Reconfiguration Graph - AHP with no balance mechanism                | .68 |

|             | Reconfiguration Graph - PA-LBIMM                                     |     |

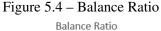

| Figure 5.4  | Balance Ratio                                                        | .69 |

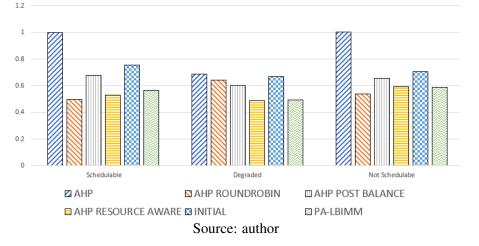

| Figure 5.5  | Failure rate budget comparison for PA-LBIMM balanced and unbalanced  | .70 |

|             | Reconfiguration Graph - AHP Based With Resource Aware Balance        |     |

|             | egy                                                                  | .70 |

|             | Reconfiguration Graph - AHP Based With Round Robin Balance Strategy. |     |

| -           | Reconfiguration Graph - Initial Algorithm                            |     |

|             |                                                                      |     |

# LIST OF TABLES

| Table 3.1 | Partition durations (in ms)                           | .27 |

|-----------|-------------------------------------------------------|-----|

| Table 3.2 | Threads properties for application                    | .28 |

| Table 3.3 | Allocation matrix (partial)                           | .34 |

| Table 3.4 | Function Hazard Analysis (Continue on the next pages) | .39 |

| Table 3.5 | Software items properties for case study              | .47 |

| Table 3.6 | Case study platform properties                        | .48 |

| Table 4.1 | Numerical saaty preferences                           | .65 |

| Table 5.1 | Output System - Functions Failure Rate                | .67 |

# CONTENTS

| 1 INTRODUCTION                                          | 12 |

|---------------------------------------------------------|----|

| 2 CONCEPTS AND RELATED WORKS                            | 15 |

| 2.1 Concepts                                            | 15 |

| 2.1.1 Schedulability Analysis                           | 15 |

| 2.1.2 Formal verification and model checking            | 15 |

| 2.1.3 Mixed Criticality systems                         | 15 |

| 2.1.4 Integrated Modular Avionics and ARINC653          | 16 |

| 2.1.5 Failure Conditions and Severity Classification    |    |

| 2.1.6 Terms                                             | 17 |

| 2.2 Related Works                                       |    |

| 3 SYSTEM RECONFIGURATION APPROACH                       | 21 |

| 3.1 Reconfigurable System Architecture                  | 21 |

| 3.2 Reconfiguration Approach                            | 23 |

| 3.2.1 Design Flow                                       | 24 |

| 3.2.2 Avionics System Specification                     | 25 |

| 3.2.2.1 Platform                                        | 25 |

| 3.2.2.2 Application                                     | 27 |

| 3.2.2.3 Properties                                      |    |

| 3.2.3 Implementation Modeling                           | 30 |

| 3.2.4 Design Constraints                                | 30 |

| 3.2.5 Formal Verification                               | 30 |

| 3.2.6 Reconfiguration States Diagram                    | 31 |

| 3.2.7 Deployment Model                                  | 33 |

| 3.2.8 Design Automation Algorithms                      | 33 |

| 3.2.8.1 Mapping, Allocation, and Scheduling             | 33 |

| 3.2.8.2 Build the Reconfiguration States Diagram        | 35 |

| 3.3 CASE STUDY                                          | 36 |

| 4 RESOURCE ALLOCATION AND SYSTEM RECONFIGURATION FRAME- |    |

| WORK                                                    | 52 |

| 4.1 Output Analysis                                     | 54 |

| 4.2 Allocation Algorithms                               |    |

| 4.3 Software Design                                     | 56 |

|                                                         | 60 |

| 4.5 Allocation Algorithms                               |    |

| 4.5.1 PA-LBIMM Algorithm Adaptations                    |    |

| 4.5.2 AHP Algorithm                                     |    |

| 5 RESULTS                                               |    |

| 6 CONCLUSION                                            |    |

| REFERENCES                                              |    |

| APPENDIX A — RESUMO EXPANDIDO                           | 79 |

# **1 INTRODUCTION**

Reconfiguration of distributed real-time embedded systems consists of changing or modifying subsystems and/or subsystem configurations to better serve a certain purpose (JÖZWIAK; NEDJAH, 2009). In an avionics system, mode changes are naturally used to adapt to changing operational flight conditions. While modes are predetermined, their realization can be through reconfigurations. Reconfiguration can be applied to tolerate faults that could cause the loss of a certain critical function in response to an external environmental change or under the request of a system user or even to a timed event in an application. The survey by Löfwenmark et al. (LÖFWENMARK; NADJM-TEHRANI, 2018) shows that fault-tolerant architectures continue to be an important area of research, and combining fault tolerance with timing guarantees is still unresolved, e.g. in presence of multicore architectures.

When a system component fails, a reconfigurable avionics platform moves the functionalities, which were allocated previously in the failed component, into another available system component. Such a reconfiguration scheme, in addition to enhancing reliability, can also be beneficial in terms of evolution capability throughout the aircraft life cycle.

The lifespan of commercial aircraft has been increasing from the end of the 20th century to the present 21st-century (JIANG, 2013) and has now reached stability. Additionally, the Maintenance, Repair, and Overhaul (MRO) market is expected to produce a strong future demand as worldwide military Air Forces decide to upgrade legacy aircraft rather than procuring new platforms (BALIS; BERENSON; JOVOVIC, 2013), which gives military fleets an increased service life. In Brazil, for instance, a recent overhaul has brought a 70s vintage fleet the ability to extend its service life beyond 2020 (Airforce Technology, 2009).

Aircraft projects, either new platforms or overhauled, have increased the development time and thereby the costs substantially in recent years. Avionics technology obsolescence occurring earlier than the aircraft airframe lifespan is also a cause of the MRO market trend. The reconfiguration flexibility can partially alleviate such problems. Early deliveries with basic capabilities can be performed and more advanced functionalities can be incorporated into the system by changing the configuration.

Given the above-described landscape, this work proposes a distributed reconfigurable architecture in which a global agent and local agents cooperate to oversee that applications transition from failed modules to working ones. The feasible reconfigurations determined offline are stored in the system to be used by the agents, which then keep the computers in a previously defined configuration in a foreseen situation.

The reconfiguration of one subsystem does not affect the rest of the system in any way. In other words, the original specified real-time constraints would still be satisfied. The sequence of necessary steps for the completion of a reconfiguration must be atomic, in the sense that they should entirely succeed or be discarded. In the case where a reconfiguration is aborted, the avionics system operation must not be affected in any way. In either case, it is important to highlight that we assume that the failures occur one at a time.

Having a successful transition to reconfigured state due to a failure does not guarantee the feasibility of such a state. Therefore is clear the need for final verification to assess the correctness of the real-time systems set to perform the desired function. For that purpose, the schedulability analysis is used to check if every task in the system will meet its timing constraints.

Different approaches can be used to perform that verification. Model checking (BAIER; KATOEN, 2008) can be used to determine the feasible reconfigurations, taking into account all possible sequences of necessary steps. From a specification, provided in Architecture Analysis and Design Language (AADL) (FEILER; GLUCH, 2012), one of the proposed approaches includes the creation of a network of automata (LARSEN; PETTERSSON; YI, 1997), representing the timing aspects of an avionics system, to perform schedulability analysis of each possible reconfiguration. This is done by evaluating specific temporal logic properties on the timed trace of the avionics system tasks and observing their deadlines. Alternatively, the scheduling simulation approach is also used by applying the scheduling algorithms during a period to compute the schedule of the system (SINGHOFF et al., 2009).

The schedulability analysis ensures the predictability of the system after each reconfiguration and facilitates airworthiness approval by the certification authorities.

Taking into consideration that systems are getting exponentially more complex every year (AVSI, 2009b). During the 1980s a typical airplane project had less than 1 million software lines of code (SLOC), while from the 2000s onwards that number exploded. For instance, the reported SLOC for the F35 program was around 24 million (AVSI, 2009a). This scenario urges for more abstractions and design automation during development. Software applications engineers should be focused on their scope, as they are not able to cope with the always increasing complexity of the underlying computer systems and their design constraints. During this work, the proposed design automation is implemented in a form of a framework proof-of-concept.

The main contributions of this work are:

- a modeling approach where fault models augmenting the AADL specifications are combined with the reconfiguration logic to formally represent fault tolerance by transitions in a reconfiguration state space;

- a method to evaluate alternative reconfiguration strategies to find suitable configurations that satisfy timing requirements and provide the highest degree of fault tolerance in the considered space;

- Verification through schedulability analysis;

- Design automation framework proof-of-concept.

The structure of this work is as follows. Chapter 2 presents related work and basic concepts. Chapter 3 the system reconfiguration approach and its underlying system architecture. Additionally, a representative avionics case study is presented, including a summary of how the design constraints are derived and preliminary reconfiguration results using model checking as the schedulability analysis method. Chapter 4 presents a detailed description of the proposed automation framework. Chapter 5 provides the result analysis from the framework output considering the proposed case study. The conclusions are reported in Chapter 6, providing also directions for future work.

#### **2 CONCEPTS AND RELATED WORKS**

#### 2.1 Concepts

### 2.1.1 Schedulability Analysis

The schedulability analysis is a process to evaluate if the time requirements of a real-time system are met. It checks if the tasks execution times and periodicity are not violated in run-time.

Schedulability test and the theory foundations were introduced in the 1970s (LIU; LAYLAND, 1973), and it brings several ways to perform the actual analyses, such as feasibility test and scheduling simulations.

## 2.1.2 Formal verification and model checking

Formal verification means having a mathematical model of a system and a method of proof to verify that the specified proprieties are satisfied (MCMILLAN, 1993). It is a form of design verification and its goal is to avoid design revision and run-time failure by identifying errors early in the design process.

Model checking is a subset of the formal verification. in this approach the system model is expressed in a finite state machine, and specifications are written in a specialized language call a propositional temporal logic. An efficient search procedure is used to determine automatically if the specification are satisfied by the transition system. It can be used for instance to perform schedulability tests of real-time systems.

#### **2.1.3 Mixed Criticality systems**

A Mixed-Criticality system is a system that can run different functions from different criticality levels, safety-critical or non-critical, in the same platform. For instance, a brake system for cars and a media center for audio and navigation. One is much more important (critical) than the other, however, the driver expects both of them to be fully functional in his vehicle.

#### 2.1.4 Integrated Modular Avionics and ARINC653

Integrated Modular Avionics (IMA) is a proposed architecture to simplify the development and certification efforts for the software of avionics systems. The first reported use of such an approach dates from the early 1990s (PRISAZNUK, 1992), first introduced Boeing 777 project (MORGAN, 1991), and it is widely used in the aerospace industry, for both, commercial and military aircraft.

The ARINC653 standard brings the software specification for space and time partitioning. It was first adopted in 1997 and rapidly accepted by the main players in the industry (PRISAZNUK, 2008). It became the foundation to build mixed-criticality applications on top of the same processing unit by providing a common basis for testing and qualifying each software item, besides specifying a standard interface called APplication EXecutive (APEX), which decouples the operating systems to the applications.

In a system that applies ARINC653 and IMA approaches, the concept of partition is introduced. A partition provides an isolated environment for software applications to run. It contains its own memory space which can not be accessed directly by a different partition. In addition, it has a dedicated time slot, so that any application running in another partition overruns, it won't affect other software applications time constraint.

#### 2.1.5 Failure Conditions and Severity Classification

A condition affecting either the airplane or its occupants, which is caused by one or more failures or errors (Federal Aviation Administration, 2011).

As defined by Advisory Circular 23.1309-1E from the Federal Aviation Administration (FAA), failure conditions may be classified according to their severity as follows:

- No safety effect: Failure conditions that would not affect safety.

- **Minor**: Failure conditions that would not significantly reduce airplane safety and involve crew actions that are within their capabilities. Some physical discomfort to passengers or cabin crew

- **Major**: Failure conditions that would reduce the capability of the airplane or the ability of the crew to cope with adverse operating conditions to the extent that there would be a significant reduction in safety margins or functional capabilities. Possibly including injuries.

- **Hazardous**: Failure conditions that would reduce the capability of the airplane or the ability of the crew to cope with adverse operating conditions. Serious or fatal injury to an occupant other than the flight crew.

- **Catastrophic**: Failure conditions that are expected to result in multiple fatalities of the occupants, or incapacitation or fatal injury to a flight crewmember normally with the loss of the airplane.

# 2.1.6 Terms

This section starts with the introduction of important terms used throughout this work. *Function* is defined as an intended behavior of a product based on a defined set of requirements regardless of implementation; *Item* as a hardware or software element having bounded and well-defined interfaces; *System* as a combination of inter-related items arranged to perform a specific function(s); and, *Application* as a software instance of a function or a part of a function.

Following the D-178 standard (RTCA, 2012), software development terms are used: *Software Item* as software component or module (a part of a complete "software system"). *Parameter Data Item (PDI)* as a set of data that, when in the form of a *Parameter Data Item File*, influences the behavior of the software without modifying the *Executable Object Code* and that is managed as a separate configuration item (examples include databases and configuration tables); *Partitioning* as a technique for providing isolation between software components to contain and/or isolate faults; and, *Software Partition* as the process of separating software components, usually with the express purpose of isolating one or more attributes of the software, to prevent specific interactions and cross-coupling interference.

### 2.2 Related Works

Housseyni et al. (HOUSSEYNI et al., 2018) propose a multi-agent reconfiguration approach in a distributed real-time system with energy harvesting constraints. The objective is to optimize global Quality of Service (QoS) measured in terms of deadline success ratio, the degree of criticality, and energy harvesting.

Five different agents are defined, one global coordinator and four locals for each

subsystem. The local agents are responsible to assess the sub-system feasibility according to the proposed reconfiguration. Such an approach makes possible independent local reconfiguration as well as coordinated global ones. Three strategies are applied for tasks adaptation depending on the reconfiguration environment and the task constraints: Decomposition, which decomposes software tasks and migrates their branches from a faulty processor to a non-faulty one; degradation, which modifies scheduling mode; and removal, which deletes branches or tasks.

The results showed a higher success ratio in meeting deadlines in comparison to other non-multiagent approaches.

In an avionics environment, all failure modes are identified in the development stage during the safety assessment process, therefore all possible reconfigurations can be analyzed prior to the system implementation causing the multiagent solution to be simplified as fewer local agents are necessary However, the proposed strategy of decomposing tasks is hard to achieve due to the high demands from aerospace software certification processes such as the DO-178C (GIGANTE; PASCARELLA, 2012), especially in software with the highest degree of criticality. Moreover, in an avionics environment, all failure modes are usually identified in the development stage and analyzed in the safety assessment process. Therefore, all possible reconfigurations can be analyzed before the system implementation, making the multi-agent solution suitable for including fewer local agents as needed. The work by Housseyni et al. (HOUSSEYNI et al., 2018) did not address how the reconfiguration process affects time-critical tasks with hard deadlines as our approach does.

Cui et al. (CUI; SHI; WANG, 2018) suggest a decentralized reconfiguration technique, applying a concept called backward reconfiguration. A global component is responsible to assess the system reconfiguration state. The decentralization causes the system to adapt faster to the identified fault in a certain computer module or communication bus, but it increases the complexity of every node in the system. The avionics software development process dictates that unnecessary complexity is to be avoided due to the high development cost implied for highly critical applications. Moreover, a local reconfiguration can lead to effects encountered in heuristic algorithms such as *hill climbing* (KLEINBERG; TARDOS, 2005). Also, *local maxima* (KLEINBERG; TARDOS, 2005) could mean the system has recovered from a component fault but could end up in a failure state if a less critical node fails, bringing the overall probability of failure to an undesirable level. Zhou et al. (ZHOU et al., 2013) propose a framework to support the reconfiguration of avionic applications that adopt the distributed IMA architecture. In the proposed framework, an action model conforming to the Behavioral Annex of AADL (FEILER; GLUCH, 2012) is built to represent the sequence of all the steps required to perform a given application reconfiguration, aiming at fault tolerance. This behavioral model in AADL is then used to compute the total execution time required for the completion of the reconfiguration, as a sum of the execution times required for each step. The work does not include further steps linking this computed total time to application constraints or schedulability analysis. In addition, the model assumes that all steps are performed in sequence, when in fact, some steps can be executed in parallel. In our proposed approach, schedulability analysis is used to determine the feasible reconfigurations, considering all possible sequences of necessary steps.

Fohler et al. (FOHLER et al., 2018) describe a similar approach for a reconfigurable avionics system. Their work also includes more than one agent: a global, called Global Resource Manager (GRM), and a local, called local resource manager (LRM). The authors provide an independent local reconfiguration with no changes in other system units whatsoever. However, the paper does not include an analysis showing that erroneous outcomes of any reconfiguration attempt will not affect system timing.

Atitallah et al. (ATITALLAH et al., 2018) propose a converged unified environment for the simulation and test domains as well as the verification and validation of an avionics system focusing on reconfigurable architectures. Field programmable gate arrays (FPGAs) are used in the system under test and in the test benches to accomplish a unified development environment to reduce cost and time-to-market. Design Constraints were taking in consideration when exploiting the main criterias of reconfigurable circuits in terms of performance, flexibility and dynamicity. The proposed approach in this work also targets system verification supporting the design and verification phases of the product development. However it explores in more details the timeliness assurance of the system in all identified scenarios, taking in consideration the certification aspects.

Montano et al. (MONTANO; MCDERMID, 2008) present an approach to solving the complex combinatorial problem of IMA reconfiguration in real-time whilst providing support for the pilot's involvement by employing automatic generation of explanations of reconfiguration actions. The approach is based on Explanation-based Constraint Programming. The paper bring a very interesting discussion on if and how the pilots should be involved in the reconfiguration process. However it goes beyond the scope of this work, taking additional inputs such as operational scenario, operational modes, mission objectives.

Porcarelli et al. (PORCARELLI et al., 2004) describe a framework providing fault tolerance of component-based applications by detecting failures through monitoring and by recovering through system reconfiguration. The framework is based on Lira, a distributed agent infrastructure for remote control and reconfiguration, and a decision maker for selecting suitable new configurations. The proposed solution is based on run-time calculations using online evaluation of a stochastic dependability model which represents the whole system. The model, created at run time, depends on a set of pre-specified reconfiguration policies, on the requirements of the application and on the system status at the reconfiguration time. This strategy is hard to employ in avionics contexts with certification, specially when events triggering the reconfiguration are unanticipated and the new system state is evaluated in run time. This work focus on evaluating the possible failure modes and valid reconfiguration, in which the real time constraints can be assessed within a degrades system state.

Hollow et al. (HOLLOW; MCDERMID; NICHOLSON, 2000) focus on the reallocation problem and propose a fitness function to be applied in conjunction with a search algorithm to find possible system states which can still fulfill the system requirements. However, the proposed solution does not include the means to confirm whether the new system schedule is still feasible. Our work proposes model checking of all possible results to assure timeliness.

Annighofer et al. (ANNIGHOFER; THIELECKE, 2012), tackles the task mapping problem through a multi-objective mathematical optimization to perform software and hardware mapping within a distributed IMA architecture while designing avionic systems. Resource allocation is a well-studied area in cloud computing also (GONG et al., 2019). Where it deals mostly with proprieties such as bandwidth control and QoS. What they miss is to evaluate how the such algorithm behaves when faced with a cascading set of computer item failures.

## **3 SYSTEM RECONFIGURATION APPROACH**

#### 3.1 Reconfigurable System Architecture

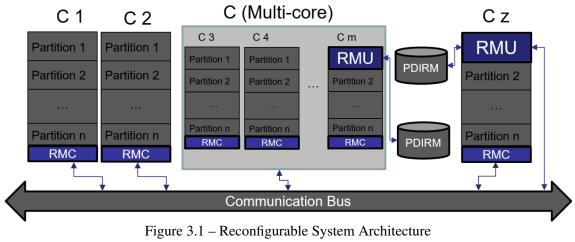

Figure 3.1 illustrates the proposed reconfigurable architecture, where C1, C2, and C3 represent processing units. They are the basic units in which faults are modeled. A basic unit is called *System Item*, or just *Item*.

Source: author

To perform the reconfiguration, three main components are proposed in the reconfigurable architecture:

- Resource Manager Unit (RMU): acts upon system items failure and triggers system reconfiguration according to a previously offline determined reconfiguration mapping;

- Resource Manager Client (RMC): assess reconfiguration request concerning erroneous item failure detection by the RMU and manages each processing unit's reconfiguration state. It is present on every processor on the platform throughout the system as part of our reconfiguration approach;

- PDI Resource Manager (PDIRM): contains the information about all processing unit schedules in every system state possible during successive reconfiguration and item failures.

The proposed reconfigurable architecture takes into consideration single core computers (for instance, C1 and C2 in Figure 3.1) and Asymmetric Multi-Processing (AMP) computers (for instance, C3 in Figure 3.1). For the AMP solution, every single core has an RMC to provide health monitoring and reconfiguration execution.

A typical reconfiguration would be triggered by the RMU if it identifies a failure in the system. Therefore, a system health monitoring mechanism should be implemented within the RMU context. The need for the RMC is to prevent the loss of a critical system function due to an erroneous RMU reconfiguration. An unnecessary state transition or even a partial reconfiguration, could create a scenario where a critical software item is not present in the new running system. For that reason, the RMC must evaluate if the reason the reconfiguration was triggered is confirmed, by an additional health monitoring. With the absence of the RMC, the RMU would be an evident system single point of failure.

Having that in mind, a few assumptions must be taken. A reconfiguration must be atomic, the system is either completely in the new state or reject the trigger. To decrease the reconfiguration complexity, it is assumed that all processing units in the system involved in critical functions are synchronized at each partition. In case of reconfiguration, the new system schedule is activated synchronously throughout the modules, avoiding communication mismatches.

Both health monitoring, from RMU and RMC, are not subject of study of this work.

Memory is not a critical resource in modern computers. On the other hand, memory access time management can pose a challenge in system timing analysis. The communication bus is a time-constrained resource and should be well managed as it is shared between several processing units.

The proposed architecture follows the basic DO-297 principles such as space and temporal isolation. The partition within each computer or core is bounded to its resource by the ARINC 653 compliant operating system. The Operating System (OS) guarantees a certain partition in a certain computer to be run in a predefined time slot with no preemption even though there is no process assigned to it. All the processes inside the partition, on the other hand, are subject to a preemptive policy, the rate monotonic in this study.

In a reconfiguration scenario, transmitting big blocks of data to be loaded in a remote module at runtime saturates the communication bus and eventually affects functionalities that were not directly affected by the triggering failure. Therefore, in the proposed system architecture, all software items (for instance, executable object code) planned to be allocated to a certain computer in any of the possible feasible reconfigurations previously determined are stored in the target memory in advance, instead of being transferred at runtime as usually proposed in earlier works (BIEBER et al., 2009). In a typical AR- INC 653 software, this is implemented by defining different schedules for each processing unit.

The RMC manages the schedule selection. When a new reconfiguration is triggered, the RMU sends the schedule that every processing unit must be configured to. Every RMC impacted by the reconfiguration must first confirm the trigger and request the health status of the failed component directly from the client associated with it, with no RMU intervention. If the failure is not confirmed, the schedule change is aborted, and the RMC keeps the processing unit in the latest state. However, if the failure is confirmed, a new schedule is configured to be active in the next processing unit major cycle absorbing the functionalities from failed components.

The applications must be designed to tolerate the worst case in which its status remains in failure until it is reconfigured to a new processing unit.

The RMU's responsibility is then to monitor the platform's overall health status. The failure modes identified in runtime are mapped to a certain transition in the reconfiguration state diagram stored in the PDIRM. The database gives the exact state to which the system must be reconfigured and keep running as expected. The new indicated configuration is sent to all involved processing units.

The communication bus is a deterministic Ethernet and a realization of the AR-INC 664 part 7. The end systems include dedicated hardware to handle A664 traffic and the network topology is set to comply with the latency requirements of each application. Annighofer et al. (ANNIGHOEFER; REIF; THIELECK, 2014) propose an algorithm to generate aircraft data and communication network topologies, taking into account message flows and network component characteristics. The algorithm presented here could be used to complement, in terms of data communication efficiency, the work presented here.

## **3.2 Reconfiguration Approach**

In the next subsections, the proposed reconfiguration approach is detailed, by presenting the design flow, the meta-models to capture the avionics system specification, as well as, the implementation and deployment information for the feasible reconfigurations. The adopted algorithms are also described and illustrated.

#### 3.2.1 Design Flow

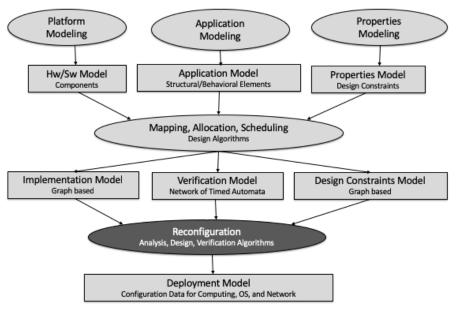

Figure 3.2 shows the design flow of the proposed approach to system reconfiguration, which starts by modeling the platform, the application to be deployed on the platform, and the properties, as design constraints to be satisfied by any valid implementation of the specified system. The main focus of this work is reconfiguration (highlighted in Figure 3.2).

Figure 3.2 – Design Flow Overview Source: author

For the platform, application, and properties modeling, AADL (FEILER; GLUCH, 2012) is adopted since it is already a well-studied format for the specification of avionics systems (ZHANG; WANG; LIU, 2016). Next, it is shown how AADL resources are used in the modeling process, which includes processors with partitions, representing a virtual processor with a specific fixed time slack to perform some action, memories, buses, and devices for the platform modeling; intercommunicating processes with threads inside and interconnected utilizing ports for application modeling; and, property sets for the design constraints modeling.

Using model transformations, an AADL specification is transformed into models conforming to the proposed meta-models, described in the next subsections. On these models, a mapping, allocation, and scheduling algorithm is applied, which determines which software items will be mapped into each hardware item from the platform, allocated to each available partition, and scheduled at specific time steps. All the information generated by the design algorithms is annotated in the implementation, verification, and design constraint models to be used by the reconfiguration algorithms, which produce a deployment model with the necessary data to perform the system reconfigurations at runtime.

# 3.2.2 Avionics System Specification

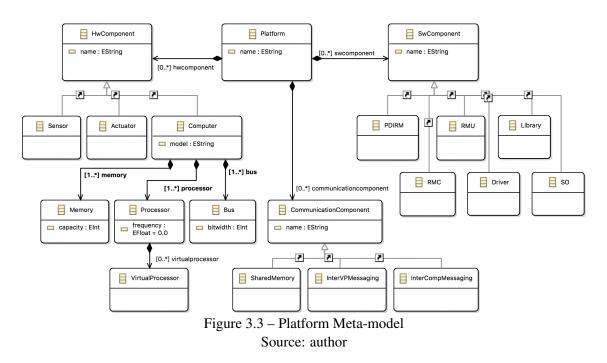

In this proposal, an avionics system is specified using Platform and Application models, conforming to the meta-models described in the following. The meta-models were created by using the EMF (Eclipse Modeling Framework) based modeling tool, available in the Eclipse version 4.3.7a Oxygen. The AADL models were created using the OSATE, version 2.3.5, modeling tool from CMU-SEI (OSATE, ).

#### 3.2.2.1 Platform

consists of hardware and software components, as well as, communication buses (see Figure 3.3). A hardware component has one or more computers (mono or multicores), and each computer can have many partitions.

A software component can be an RMU or an RMC, which are responsible for the

reconfiguration actions in the avionics system. A software component can also be an OS, a reusable library, a driver, or the source code for the implementation of a given system function.

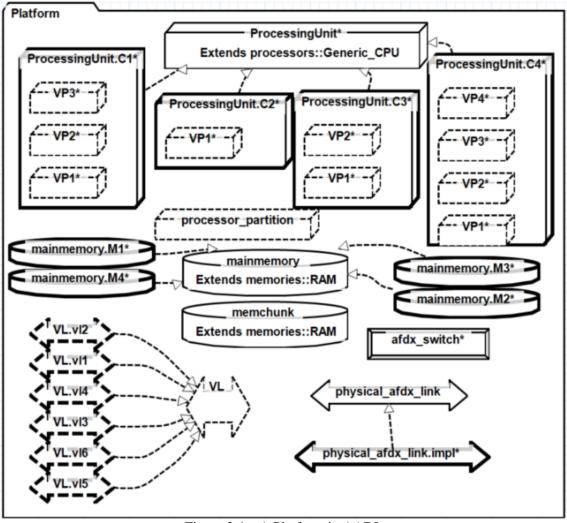

A communication bus can be modeled in AADL as shared memory when the communication occurs inside the same partition of a computer; as an inter-virtual processor messaging, when the communication is between two different partitions at the same processor; or as an interprocessor messaging when the communication involves two different computers in the platform. Figure 3.4 shows an example of a Platform in AADL containing four processors C1, C2, C3, and C4, each one with three, one, two, and four partitions, respectively.

Figure 3.4 – A Platform in AADL Source: author

Figure 3.4 shows an ARINC 664 compliant bus with six virtual links to implement the communication between the computers, and memory components. Table 3.1 presents

**C2 C3 C4 C1** M. frame: 20 ms M. frame: 10 ms M. frame: 10 ms M. frame: 20 ms RAM: 256 Kb RAM: 256 Kb RAM: 256 Kb RAM: 256 Kb Flash: 1 Mb Flash: 1 Mb Flash: 1 Mb Flash: 1 Mb  $V\overline{P2}$ VP1 VP1 VP2 VP2 VP3 VP1 VP3 VP1 VP4 10 10 5 5 5 5 4 6 6 4

the specified properties for the processing units in the example presented in Figure 3.4.

Table 3.1 – Partition durations (in ms)

Source: author

As shown in Table 3.1, each computer has a major frame (in milliseconds), indicating how much time all partition executions take, memory capacities, and the time slot of each virtual processor (also in milliseconds). Other design properties can also be specified in the AADL model, such as the latency of the virtual links, which were set as 1 ms in this example, the size and width of the memory components, etc.

#### 3.2.2.2 Application

An application consist of one or more software item. It fulfills a system function of part of a system function.

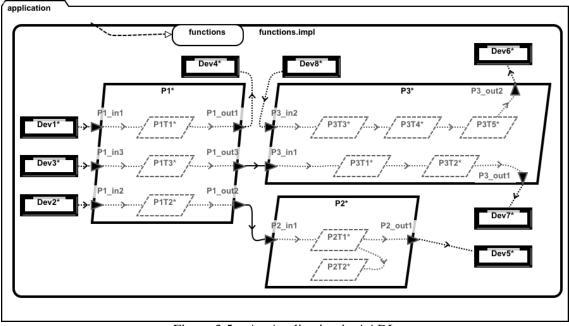

A software item can be a process, a thread, or a device, where a process is a group of threads. For each thread, it is possible to have the source code of the program to be executed. These concepts in the Application meta-model allow specifying an application hierarchically. Figure 3.5 shows an example of an application in AADL, in which there are three processes P1, P2, and P3, which have three, two, and five threads, respectively.

The data flow between the devices, processes, and threads is specified through ports and connections between them and determines the dependencies between the software items. Thus, in the example in Figure 3.5, the process P1 has threads P1T1, P1T2, and P1T3, which have no dependencies between them and therefore can run concurrently. Unlike the P3 process, where there are dependencies between the P3T3, P3T4, and P3T5, which requires their sequential execution.

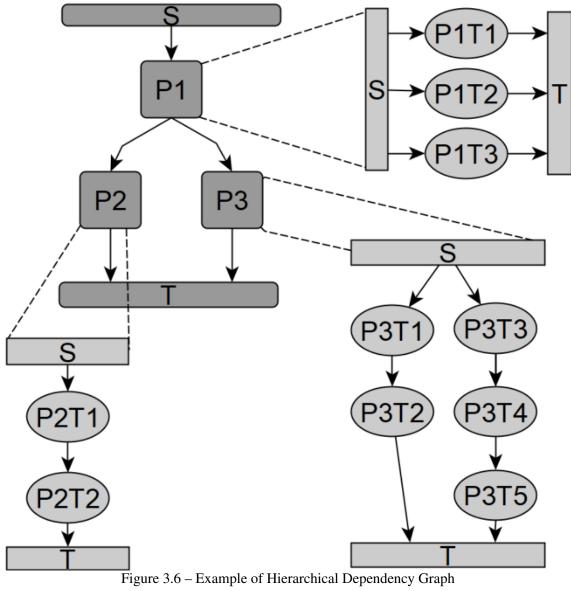

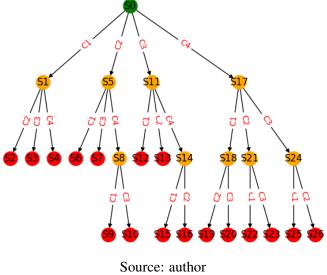

These dependencies are captured by a Directed Acyclic Graph (KLEINBERG; TARDOS, 2005) that is called Hierarchical Dependency Graph (HDG), where the nodes represent the software items and the edges represent data flow and also control flow dependencies between the nodes. Figure 3.6 presents the HDG corresponding to the application in Figure 3.5.

Figure 3.5 – An Application in AADL Source: author

In the HDG in Figure 3.6, there are three nodes in the higher level representing the processes in the application and ten nodes in the lower level of the hierarchy for the threads. In the properties model, for each thread, the following is captured: the specified period, deadline, worst-case execution time (WCET), and necessary memory, given by the designer in the AADL modeling. Table 3.2 shows the specified properties for the application in Figure 3.5.

| Prop.         |    | P1 |    | P2 |    | P3 |    |    |    |    |  |

|---------------|----|----|----|----|----|----|----|----|----|----|--|

|               | T1 | T2 | T3 | T1 | T2 | T1 | T2 | T3 | T4 | T5 |  |

| Period (ms)   | 20 | 20 | 20 | 20 | 20 | 30 | 30 | 40 | 40 | 40 |  |

| Deadline (ms) | 20 | 20 | 20 | 20 | 20 | 30 | 30 | 40 | 40 | 40 |  |

| WCET (ms)     | 4  | 4  | 4  | 2  | 2  | 4  | 4  | 4  | 4  | 4  |  |

| Memory (Kb)   | 90 | 50 | 30 | 40 | 70 | 90 | 80 | 60 | 50 | 95 |  |

Table 3.2 – Threads properties for application

Source: author

As shown in Table 3.2, thread T1 of process P1 has specified period, deadline, WCET, and demanded memory given by 20ms, 20ms, 4 ms, and 90Kb, respectively.

# 3.2.2.3 Properties

Modelling properties allows capturing the design constraints specified by the designer that must be satisfied by any valid implementation for the system. A Property can

Source: author

represent criticality, priority, period, deadline (soft and hard), and dissimilarity characteristics of elements in the models, conforming to the proposed meta-models.

#### **3.2.3 Implementation Modeling**

The Implementation meta-model defines how to model the design decisions that are taken during the execution of the design algorithms and by the designer. It captures the mapping, allocation, and scheduling information that is produced by the design tools.

#### **3.2.4 Design Constraints**

The Design Constraint meta-model defines how to associate the properties of the system specification to the properties in the implementation model, which is generated by the design process. A Design Constraint associates a property to a given design item or multiple items. For instance, it is possible to pre-allocate a specific software item to a specific virtual processor and to specify the WCET of each thread.

#### **3.2.5 Formal Verification**

To perform model checking of some specific properties, specified as temporal logic expressions, a network of timed automata must be generated from the system specification. The Verification meta-model defines how to model such network of timed automata as a Labeled Timed Automata (LTA) System (BAIER; KATOEN, 2008), which can then be expressed as concepts introduced by the UPPAAL model checking tool (LARSEN; PETTERSSON; YI, 1997). An LTA System consists of Declarations and one or more LTA Templates, which represent the automata. The states are modeled as LTA locations and the state transitions as LTA transitions, which are represented by LTA edge sources and LTA edges targets. Each transition can be annotated with the guard, update, selection, and synchronization expressions. The guard's expression must be satisfied for the transition to be enabled. When an enabled transition occurs the corresponding update expression is executed, which can modify the values of some specified variables. The synchronization expression allows two automata to synchronize and the transitions at both automata are simultaneously triggered. From the platform, application, and property models and the corresponding HDG, the network of automata is automatically generated, based on the framework for schedulability analysis proposed by David et al. (DAVID et al., 2009). According to this framework, a resource automaton for each processor partition and a task automaton for each of the process threads are instantiated.

Each one of the task automata starts in an initial state where it keeps waiting until all other tasks that it depends on finish their execution and then sends a request to the resource automaton, corresponding to the processor partition in which the task was allocated. The resource automaton models some specified scheduling policy, that can be Earliest Deadline First (EDF), Fixed Priority Scheduling (FPS), or First In First Out (FIFO), by managing a tasks queue. When the task execution is concluded, the corresponding resource automaton notifies it by a finished signal.

At each task automaton, there is a transition from the Ready state to an Error state when the elapsed time is greater than the task deadline, which means that the specified design constraint was not satisfied. Thus, to perform the schedulability analysis of the system, the following temporal logic expression is checked on the generated network of automata, using the UPPAAL model checker: A[] for all (i : t\_id) not Task(i).Error. This expression means that, for all possible execution paths, no task automaton reaches the Error state.

When the model checker concludes that this property is valid, all the specified deadline constraints are satisfied, i. e., it has found a feasible mapping, allocation, and scheduling reconfiguration for the application on the given platform.

#### **3.2.6 Reconfiguration States Diagram**

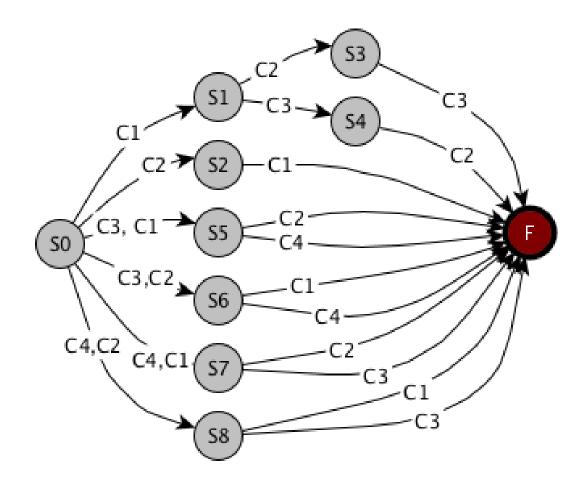

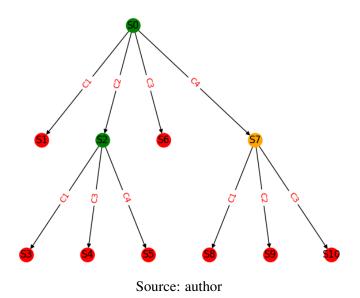

The Reconfiguration States Diagram (RSD) represents the possible feasible reconfigurations as states, and the state transitions as the valid transformation from a currently feasible reconfiguration to a next feasible reconfiguration, which can tolerate some fault in each system component, indicated as a label at the corresponding state transition. Figure 3.7 shows an example of a reconfiguration states diagram.

At the initial state S0, the system is operating normally, according to an initial mapping, allocation, and scheduling algorithm, which considers the specified properties of the system. The state transition from S0 to S1, labeled C1, indicates that when component C1 fails, the system has a feasible reconfiguration, represented by the S1 state,

Figure 3.7 – An Example of Reconfiguration States Diagram Source: author

which tolerates the fault. When in state S1 and component C2 fails, the system can be reconfigured according to state S3. The system has no feasible reconfiguration from state S3 when component C3 fails, which is represented by state transition from S3 to F (Fail state), labeled with C3. The transitions from S0 to S2 and from S2 to F indicate that after component C2 fails a fault in C1 cannot be tolerated by the system. Note that the appearance of two-component failures on one transition is a way of abbreviating the graph. Failures happen one at a time and are dealt with through one reconfiguration, as stated in Chapter 1.

#### **3.2.7 Deployment Model**

The Deployment meta-model defines how to capture the necessary information to perform the reconfigurations of the system. Each configuration determines how each design item will be deployed, associating elements of the system specification to elements of the platform, as well as, all the necessary design information.

#### **3.2.8 Design Automation Algorithms**

The design automation process for the proposed reconfiguration approach includes algorithms to build the Reconfiguration Diagram, perform mapping, allocation, and scheduling, generate intermediate files for schedulability analysis, and generate the Deployment Model for each given reconfiguration. The next subsections describe each of these algorithms.

#### 3.2.8.1 Mapping, Allocation, and Scheduling

The algorithms that build the implementation model and the deployed model are given a current platform, system, and properties model as follows.

First, a list of tasks with their properties, for example, the period, the deadline, and the WCET are created. Then, the hierarchical dependencies graph is generated from the AADL application model. A list of available computers and their virtual processors with corresponding properties are created from the platform and properties models.

By means of a depth-first traversal in the hierarchical dependency graph, starting from the begin node, each task is visited and mapped into an available computer, and allocated into one of their virtual processors, which should satisfy the specified design constraints. This step produces an allocation matrix, containing the information to be used by the algorithm for the schedulability analysis. It also instantiates a corresponding deployment model to be used when building the reconfiguration states diagram, described in the next subsection. Table 3.3 shows the allocation matrix produced from the platform and the application models, shown in Figures 3.4 and 3.5, respectively, and platform and application properties listed in Tables 3.1 and 3.2, respectively.

|                |      | C1   |             | C2   | C    | 23   | C4   |      |      |      |  |

|----------------|------|------|-------------|------|------|------|------|------|------|------|--|

| VPs            | VP1  | VP2  | VP3         | VP1  | VP1  | VP2  | VP1  | VP2  | VP3  | VP4  |  |

| None           | P1T1 | P1T2 | P1T3        | P3T1 | -    | -    | -    | -    | -    | -    |  |

| fails          |      |      | P2T1        | P3T2 |      |      |      |      |      |      |  |

|                |      |      | P2T2        | P3T4 |      |      |      |      |      |      |  |

|                |      |      | P3T3        | P3T5 |      |      |      |      |      |      |  |

| C1             | X    | X    | X           | P1T1 | P1T3 | P3T3 | -    | -    | -    | -    |  |

| fails          |      |      |             | P1T2 | P2T1 |      |      |      |      |      |  |

|                |      |      |             | P3T1 | P2T2 |      |      |      |      |      |  |

|                |      |      |             | P3T2 | P3T5 |      |      |      |      |      |  |

|                |      |      |             | P3T4 |      |      |      |      |      |      |  |

| C2             | P1T1 | P1T2 | P1T3        | Х    | P3T2 | P3T1 | -    | -    | -    | -    |  |

| fails          |      |      | P2T1        |      | P3T5 | P3T4 |      |      |      |      |  |

|                |      |      | P2T2        |      |      |      |      |      |      |      |  |

|                |      |      | P3T3        |      |      |      |      |      |      |      |  |

| C1,            | X    | X    | X           | X    | P2T1 | P1T3 | P1T1 | P1T2 | P3T2 | P3T1 |  |

| C2             |      |      |             |      | P2T2 | P3T3 |      |      |      |      |  |

| fail           |      |      |             |      | P3T5 | P3T4 |      |      |      |      |  |

|                |      |      |             |      |      |      |      |      |      |      |  |

|                |      |      |             |      |      |      |      |      |      |      |  |

| C1,            | Х    | X    | Х           | P1T1 | X    | X    | P1T3 | P3T5 | P2T1 | P3T3 |  |

| C3             |      |      |             | P1T2 |      |      |      |      | P2T2 |      |  |

| fail           |      |      |             | P3T1 |      |      |      |      |      |      |  |

|                |      |      |             | P3T2 |      |      |      |      |      |      |  |

|                |      |      |             | P3T4 |      |      |      |      |      |      |  |

| C2,            | Х    | X    | Х           | X    | P3T2 | P3T1 | P1T1 | P1T2 | P1T3 | P2T1 |  |

| C1             |      |      | <i>P3T3</i> |      | P3T5 | P3T4 |      |      |      | P2T2 |  |

| fail           |      |      |             |      |      |      |      |      |      |      |  |

|                |      | •••  |             | •••  | •••  | •••  | •••  |      | •••  |      |  |

| Source: author |      |      |             |      |      |      |      |      |      |      |  |

Table 3.3 – Allocation matrix (partial)

As shown in Table 3.3, when no computer fails, threads T1, T2, T3 of process P1, threads T1 and T2 of process P2, and thread T3 of process P2 are mapped to the computer C1 and allocated on its virtual processors VP1, VP2, VP3, which are the first ones avail-

able with enough time slot and memory resources to execute the corresponding threads. When C1 fails, the threads from C1 can migrate to C2 and C3, which has available virtual processors with enough time and resources. After that, if C2 fails, its threads can further migrate to C3 and C4. However, when C3 fails, the threads P3T3, P3T4, and P3T5 in VP2 of C3 cannot be mapped into any computer, and so there is no feasible reconfiguration that could tolerate this fault in C3 at this point. Figure 3.7 shows the Reconfigurable States Diagram that will be generated based on this allocation matrix.

# 3.2.8.2 Build the Reconfiguration States Diagram

represents all possible feasible reconfigurations, starting from the initial valid implementation of a system and going to each possible feasible reconfiguration that can mask the fault in each system component. The corresponding algorithm is shown in Algorithm 1:

- At line 1, the generation of the initial deployment model consists of, for each element from the application model, a mapping to an element from the platform model determined by the design tool or by the system designer. This step will produce the initial state S0 in the Reconfiguration States Diagram.

- In line 2, the algorithm starts from a source state (Ss) as the initial state S0.

- The entire algorithm (lines 3-38) will repeat until all existing states are marked, and this occurs when all the created states were considered by the algorithm.

- At each iteration of the Algorithm 1, the possible failure of some computers *Ci* is considered (lines 5-32) and for each possible feasible reconfiguration (*schedulable*, according to the model checking verification), a new target state (*St*) is created and a transition from *Ss* to *St* is created (lines 20-25), or

- If there is no feasible reconfiguration a transition from *Ss* to an error state (*Serror*) is created (lines 27 and 30).

- A new Deployment model is built for each newly created target state (line 21), according to the current mappings.

- At lines 8-10, a SwItem<sub>p</sub> is mapped into Cj if it is compatible with Cj, i.e., if there is no SwItem<sub>q</sub> already mapped to Cj, which would conflict with SwItem<sub>p</sub>. The conflict between software items can be specified in the Properties model by the designer. A SwItem<sub>p</sub> can also be mapped into Cj if there is a free partition available in Cj.

This algorithm produces a Reconfiguration States Diagram, where each state represents a feasible reconfiguration, and each transition, labeled Ci, from a state Ss to St indicates that if the system is currently configured as determined by the Deployment model associated with state Ss and the computer Ci fails then the system tolerates the fault and goes to a new configuration given by the Deployment model associated to state St. In the case where St is at a failure state, the entire system fails since the fault could not be tolerated.

#### **3.3 CASE STUDY**

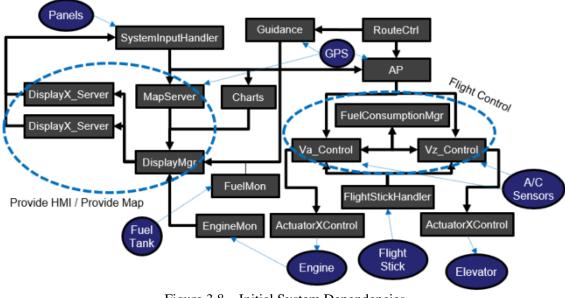

To evaluate the proposed approach for avionics systems development, a case study is proposed bringing examples from the avionics industry. A top-down approach is chosen as recommended by the ARP4754 (SAE, 2010), defining at first the system functions and subsystem functions:

- Flight Control

- Flight Control

- Fuel Management

- Provide Auto Pilot

- Provide Navigation

- Guidance

- Route Control

- Provide Map

- Provide Charts

### • Provide Human Machine Interaction (HMI)

- Screen Monitoring (display symbology)

- System Control

- Provide input for flight control

- Provide System monitoring

- Fuel Monitoring

- Engine Monitoring

The system functions are the highest level definitions in a system and specify its basic functionalities. From this definition, the breakdown is performed for the system realization.

In order to determine the criticality and therefore the certification efforts of the bottom-level system items, the Function Hazard Analysis (FHA) is performed. The FHA is a systematic, comprehensive examination of the airplane and system functions to identify potential minor, major, hazardous, and catastrophic failure conditions that may arise as a result of a malfunction or a failure to function. The loss of, or undetected erroneous flight control, for instance, can cause the loss of the aircraft giving the severity classification as catastrophic. On the other hand, the loss of the Map provider functionality causes a slight increase in crew workload which gives a Minor in the classification. Table 3.4 shows the complete analysis performed for this case study.

| Γ    | Data: Platform, Application, and Properties models                        |

|------|---------------------------------------------------------------------------|

| F    | Result: Reconfiguration States Diagram                                    |

|      | S0 = generate initial Deployment;                                         |

|      | Ss = S0;                                                                  |

| 3 r  | epeat                                                                     |

| 4    | repeat                                                                    |

| 5    | for each $Ci$ in the current Deployment and $Ci$ failed do                |

| 6    | for each SwItem_p not yet mapped do                                       |

| 7    | <b>for</b> each $Cj$ in the current Deployment and $Cj \neq Ci$ <b>do</b> |

| 8    | if $(is\_compatible(Cj)$ or $has\_free\_partition(Cj)$ ) then             |

| 9    | $SwItem_p$ is mapped to $Cj$ ;                                            |

| 10   | end                                                                       |

| 11   | if there is $SwItem_q$ in $Cj$ which is not critical or it was            |

|      | affected by the fault at Ci then                                          |

| 12   | unmap $SwItem_q$ from $Cj$ ;                                              |

| 13   | map $SwItem_p$ to $Cj$ ;                                                  |

| 14   | end                                                                       |

| 15   | end                                                                       |

| 16   | end                                                                       |

| 17   | if there is no unmapped critical $SwItem_p$ then                          |

| 18   | build Verification model based on current mappings;                       |

| 19   | perform Model Checking on Verification model;                             |

| 20   | if schedulable then                                                       |

| 21   | St = generate a new Deployment model from current                         |

|      | mappings;                                                                 |

| 22   | create a transition from $Ss$ to $St$ with label $Ci$ ;                   |

| 23   | if there is unmapped non-critical SwItem <sub>p</sub> then                |

| 24   | Mark St as Degraded                                                       |

| 25   | Ss = St;                                                                  |

| 26   | else                                                                      |

| 27   | create transition from $Ss$ to $Serror$ with label $Ci$ ;                 |

| 28   | end                                                                       |

| 29   | else                                                                      |

| 30   | create a transition from $Ss$ to $Serror$ with label $Ci$ ;               |

| 31   | end                                                                       |

| 32   | end                                                                       |

| 33   | <b>until</b> no new state St was created;                                 |

| 34   | mark $Ss$ as done;                                                        |

| 35   | if (there is any non-marked state Snm) then                               |

| 36   | Ss = Snm;                                                                 |

| 37   | end                                                                       |

| 38 U | ntil all states are marked;                                               |

|      | Algorithm 1: Build Reconfiguration States Diagram                         |

Algorithm 1: Build Reconfiguration States Diagram

| Function          | Sub Function       | Failure<br>Condition                         | Flight<br>Phase                 | Effect                                                                                    | Failure<br>Condition<br>Severity<br>Classification | Function<br>Design<br>Assurance<br>Level |

|-------------------|--------------------|----------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------|

|                   |                    | Loss of<br>Flight Control                    | Landing/<br>Take-off/<br>Flight | Aircraft Loss                                                                             | Catastrophic                                       | FDAL A                                   |

|                   | Flight<br>Control  | Undetected<br>Erroneous<br>Flight Control    | Landing/<br>Take-off/<br>Flight | Aircraft Loss                                                                             | Catastrophic                                       | FDAL A                                   |

| Elight            |                    | Loss of<br>Fuel Management                   | Flight                          | Significant increase of crew workload                                                     | Major                                              | FDAL C                                   |

| Flight<br>Control | Fuel<br>Management | Undetectable<br>Erroneous<br>Fuel Management | Flight                          | Mitigation: Fuel Monitoring<br>After Mitigation: Significant<br>increase of crew workload | Major                                              | FDAL C                                   |

|                   |                    | Loss of Auto Pilot                           | Landing                         | Significant increase of crew workload                                                     | Major                                              | FDAL C                                   |

Table 3.4 – Function Hazard Analysis (Continue on the next pages)

| Provide<br>Auto Pilot | Provide<br>Auto Pilot | Undetectable<br>Erroneous<br>Auto Pilot | Landing                         | Aircraft Loss                                                                                | Catastrophic | FDAL A |

|-----------------------|-----------------------|-----------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------|--------------|--------|

|                       |                       | Loss of Guidance                        | Landing/<br>Take-off/<br>Flight | Significant increase of crew workload                                                        | Major        | FDAL C |

|                       | Guidance              | Undetectable<br>Erroneous<br>Guidance   | Landing/<br>Take-off/<br>Flight | Higher workload such that the crew<br>could not be relied upon to perform<br>tasks accuratly | Hazardous    | FDAL B |

|                       |                       | Loss of<br>Route Control                | Landing/<br>Flight              | Significant increase of crew workload                                                        | Major        | FDAL C |

| Provide<br>Navigation | Route Control | Undetectable<br>Erroneous<br>Route Control   | Landing/<br>Flight              | Mitigation: Guidance Functionality<br>can provide monitoring capability<br>for an eventual erroneous route<br>configuration<br>After Mitigation: Significant<br>reduction in safety margins<br>Significant increase of<br>crew workload | Major | FDAL C |

|-----------------------|---------------|----------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

|                       |               | Loss of Map Source                           | Flight                          | Slight increase in crew workload                                                                                                                                                                                                        | Minor | FDAL D |

|                       | Provide Map   | Undetectable<br>Erroneous<br>Map Information | Flight                          | Mitigation: Map not to be used<br>as the main navigation source<br>After mitigation: Slight increase<br>in crew workload                                                                                                                | Minor | FDAL D |

|                       |               | Loss of<br>Charts Source                     | Landing/<br>Take-off/<br>Flight | Slight increase in crew workload                                                                                                                                                                                                        | Minor | FDAL D |

| Provide Human          |                                                                     | 1                                                                                                | 1                     | 1                                                                                            | 1            | 1      |

|------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------|--------------|--------|

| Machine<br>Interaction | Provide Charts                                                      | Undetectable<br>Erroneous                                                                        | Landing/<br>Take-off/ | Mitigation: Chart not to be used<br>as the main approach guide                               | Minor        | FDAL D |

|                        |                                                                     | Provide Charts                                                                                   | Flight                | After mitigation: Slight increase in crew workload                                           |              |        |

|                        |                                                                     | Loss of Screen<br>Flight Critical<br>Data Monitoring<br>(display symbology)                      | Landing/<br>Take-off  | Higher workload such that the crew<br>could not be relied upon to perform<br>tasks accuratly | Hazardous    | FDAL B |

|                        | Screen Flight<br>Critical Data<br>Monitoring<br>(display symbology) | Undetectable<br>Erroneous<br>Flight Critical<br>Data Screen<br>Monitoring<br>(display symbology) | Landing/<br>Take-off  | Aircraft Loss                                                                                | Catastrophic | FDAL A |

|                        |                                                                     | Loss of Screen<br>non-Critical<br>Data Monitoring<br>(display symbology)                         | Landing/<br>Take-off  | Slight increase in crew workload                                                             | Minor        | FDAL D |

| Screen<br>non-Critical<br>Data Monitoring<br>(display symbology) | Undetectable<br>Erroneous<br>non-Critical<br>Data Screen<br>Monitoring<br>(display symbology) | Landing/<br>Take-off             | Slight increase in crew workload                                                             | Minor        | FDAL D |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------|--------------|--------|

| System Control                                                   | Loss of<br>System Control<br>Undetectable                                                     | Landing/<br>Take-off<br>Landing/ | Higher workload such that the crew<br>could not be relied upon to perform<br>tasks accuratly | Hazardous    | FDAL B |

|                                                                  | Erroneous<br>System Control                                                                   | Take-off                         | Aircraft Loss                                                                                | Catastrophic | FDAL A |

|                                                                  | Loss of input<br>for flight<br>control                                                        | Landing/<br>Take-off/<br>Flight  | Aircraft Loss                                                                                | Catastrophic | FDAL A |

| Provide input<br>for flight<br>control                           | Undetectable<br>Erroneous<br>input for flight control                                         | Landing/<br>Take-off/<br>Flight  | Aircraft Loss                                                                                | Catastrophic | FDAL A |

|                 | Loss of Fuel<br>Monitoring                   | Flight               | Significant reduction in<br>safety margins<br>Significant increase of<br>crew workload                                             | Major     | FDAL C |

|-----------------|----------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|

| Fuel Monitoring | Undetectable<br>Erroneous<br>Fuel Monitoring | Flight               | Large reduction in safety margins<br>Higher workload such that the crew<br>could not be relied upon to perform<br>tasks accuratly  | Hazardous | FDAL B |

|                 | Loss of Engine<br>Monitoring                 | Landing/<br>Take-off | Large reduction in safety margins<br>Higher workload such that the crew<br>could not be relied upon to perform<br>tasks accurately | Hazardous | FDAL B |

| Provide<br>System |                   |                                                |                      | Large reduction in safety margins                                      |           |        |

|-------------------|-------------------|------------------------------------------------|----------------------|------------------------------------------------------------------------|-----------|--------|

| monitoring        | Engine Monitoring | Undetectable<br>Erroneous<br>Engine Monitoring | Landing/<br>Take-off | Higher workload such that the crew could not be relied upon to perform | Hazardous | FDAL B |

|                   |                   |                                                |                      | tasks accurately                                                       |           |        |

Source: author

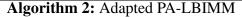

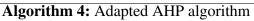

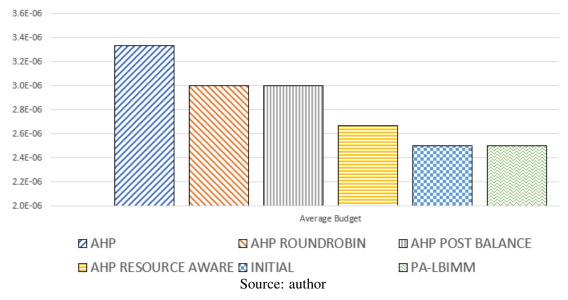

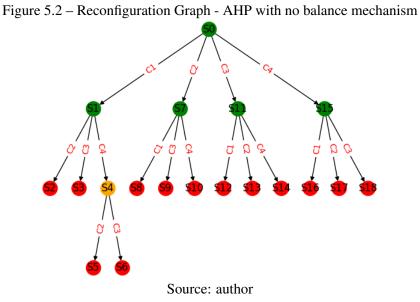

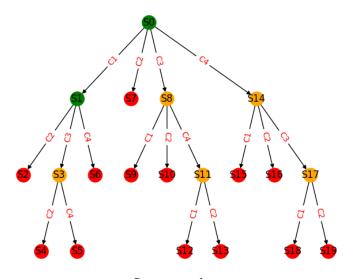

The worst failure condition for Flight Control, for instance, is aircraft loss which can be classified as catastrophic according to the ARP 4761 (SAE, 1996). Such classification implies the function design assurance level (FDAL) to be A. This enforces the group of items that realize the flight control to be developed at the highest level of assurance. While the functions related to minor events must comply at least to level D which is the second lowest on a scale from E to A.