# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA CURSO DE ENGENHARIA DE COMPUTAÇÃO

#### GABRIEL LUCA NAZAR

QR Decomposition Algorithms for MIMO Systems: Impact on Computational Effort and Hardware Implementations

Trabalho de Diplomação.

Prof. Dr. Luigi Carro Orientador

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Carlos Alexandre Netto

Vice-Reitor: Prof. Rui Vicente Oppermann

Pró-Reitora de Graduação: Profa. Valquiria Link Bassani Diretor do Instituto de Informática: Prof. Flávio Rech Wagner

Coordenador do ECP: Prof. Gilson Inácio Wirth

Bibliotecária-Chefe do Instituto de Informática: Beatriz Regina Bastos Haro

#### **ACKNOWLEDGEMENTS**

I would like to thank Christina Gimmler and Prof. Dr.-Ing. Norbert Wehn, from TU Kaiserslautern, for the support and guidance during my stay in Germany. I would also like to thank Prof. Dr. Luigi Carro for being my advisor on this work after my return to Brazil.

And last but not least, I would like to thank my family and friends for the support. And one very special thank to Bianca for always believing in me.

## **CONTENTS**

| LIST (      | OF ABBREVIATIONS AND ACRONYMS                               | 6  |

|-------------|-------------------------------------------------------------|----|

| LIST (      | OF FIGURES                                                  | 7  |

| LIST (      | OF TABLES                                                   | 9  |

| <b>RESU</b> | IMO                                                         | 10 |

|             | RACT                                                        |    |

| 1 IN        | ITRODUCTION                                                 | 12 |

| 1.1         | Context and Motivation                                      | 12 |

| 1.2         | Contributions                                               | 12 |

| 1.3         | Report Structure                                            |    |

| 2 C         | OMMUNICATION CHAIN MODEL                                    | 14 |

| 2.1         | Channel model                                               |    |

| 2.2         | The Sphere Decoding algorithm                               | 15 |

| 2.2.1       | The usage of the QR decomposition                           |    |

| 2.2.2       | Sphere Shrinking                                            |    |

| 3 Q         | R DECOMPOSITION ALGORITHM                                   | 20 |

| 3.1         | The Gram-Schmidt process                                    | 20 |

| 3.2         | Modified Gram-Schmidt process                               | 21 |

| 3.3         | Sorted QR Decomposition                                     |    |

| 3.4         | MMSE Pre-processing                                         |    |

| 3.4.1       | Bias subtraction                                            |    |

| 4 S         | MULATION CHAIN AND RESULTS                                  |    |

| 4.1         | Simulation parameters                                       |    |

| 4.2         | Simulation results                                          |    |

| 4.2.1       | Effect of the quantization of the output                    |    |

| 4.2.2       | Effect of a Newton-Raphson iteration                        |    |

| 4.2.3       | Amount of bits necessary for 2×2 and 4×4 systems            |    |

| 4.2.4       | Effects of the sorted QR decomposition and sphere shrinking |    |

| 4.2.5       | Effects of the usage of the norm update method              |    |

| 4.2.6       | Comparison of different bias subtraction methods for MMSE   |    |

| 4.2.7       | Reduced sphere radii for MMSE-SQRD                          |    |

| 4.2.8       | Comparison between ES and IS with reduced sphere            |    |

| 4.2.9       | Effects of error in the $\sigma$ estimation for MMSE        |    |

| 4.2.10      | MMSE-SQRD with constant $\sigma$                            |    |

| 4.3         | Simulation results summary                                  |    |

|             | ARDWARE ARCHITECTURES                                       |    |

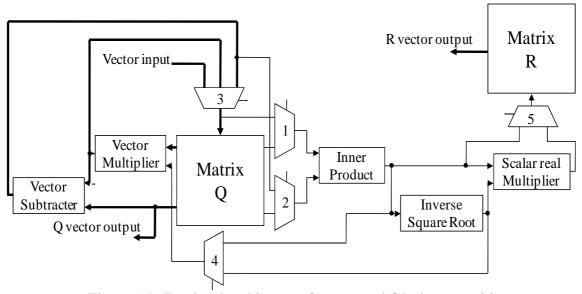

| 5.1         | Unsorted QR Decomposition                                   |    |

| 5.1.1       | Complex multiplier                                          |    |

| 5.1.2       | Adder/Subtracter                                            |    |

| 5.1.3       | Inner product                                               | 51 |

| 5.1.4       | Inverse square root                       | 52 |

|-------------|-------------------------------------------|----|

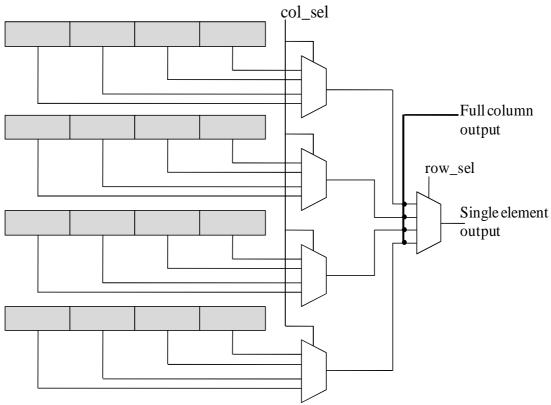

| 5.1.5       | Vector operations                         | 55 |

| 5.1.6       | Matrices storage                          | 55 |

| 5.1.7       | Top level architecture                    | 55 |

| 5.1.8       | Finite state machine                      | 56 |

| 5.2         | Sorted QR Decomposition                   | 57 |

| 5.2.1       | Matrix storage elements                   | 57 |

| 5.2.2       | Top level architecture                    | 58 |

| 5.2.3       | Finite state machine for SQRD             | 58 |

| 5.3         | MMSE Sorted QR Decomposition              | 59 |

| 5.3.1       | Storage element for the modified Q matrix | 59 |

| 5.3.2       | Top level architecture                    |    |

| <b>5.4</b>  | Reduced order matrices                    | 60 |

| 6 H         | ARDWARE IMPLEMENTATION RESULTS            | 62 |

| 6.1         | Timing results                            | 62 |

| 6.1.1       | Real time requirements                    | 63 |

| 6.2         | Area results                              | 63 |

| 6.2.1       | FPGA area results                         | 63 |

| 6.2.2       | ASIC area results                         | 65 |

| 6.3         | Comparison with high-level synthesis      | 66 |

| 7 C         | CONCLUSIONS                               | 69 |

| REFE        | RENCES                                    | 70 |

| <b>APPE</b> | ENDIX                                     | 72 |

#### LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application Specific Integrated Circuit

BCJR Bahl, Cocke, Jelinek and Raviv

CS Constant Sphere

ES Early Subtraction

FER Frame Error Rate

FPGA Field-Programmable Gate Array

FSM Finite State Machine

IS Intermediate Subtraction

LDPC Low-Density Parity Check

LLR Logarithmic Likelihood Ratio

LS Late Subtraction

LUT Look-Up Table

MAP Maximum A-Posteriori

MIMO Multiple Input Multiple Output

MMSE Minimum Mean-Square Error

NR Newton-Raphson NU Norm Update

OSS Ordered Sphere Shrinking

PED Partial Euclidean Distance

QAM Quadrature Amplitude Modulation

SISO Soft Input Soft Output SNR Signal-to-Noise Ratio

SQRD Sorted QR Decomposition

SS Sphere Shrinking

VHDL Very-high-speed integrated circuit Hardware Description Language

# **LIST OF FIGURES**

| Figure 2.1: System model                                                              | . 14 |

|---------------------------------------------------------------------------------------|------|

| Figure 2.2: Tree search for a system with 4-QAM and 4×4 antennas                      |      |

| Figure 2.3: Sphere shrinking example for a 4×4 antennas system with 4-QAM             |      |

| Figure 3.1: Gram-Schmidt process for two vectors                                      |      |

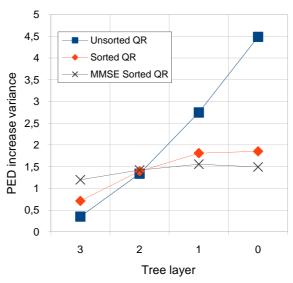

| Figure 3.2: Average PED increase and average number of visited nodes per layer for    |      |

| 4×4 system, with 16-QAM and a SNR of 12dB                                             |      |

| Figure 3.3: Average PED increase variance per layer for a 4×4 system, with 16-QAM     | I    |

| and a SNR of 12dB                                                                     |      |

| Figure 3.4: Receiver modified for SQRD usage                                          | . 27 |

| Figure 3.5: Average PED increase and average number of visited nodes per layer for    | a    |

| 4×4 system, with 16-QAM and a SNR of 12dB                                             | . 28 |

| Figure 3.6: Average PED increase variance per layer for a 4×4 system, with 16-QAM     | I    |

| and a SNR of 12dB                                                                     |      |

| Figure 4.1: Effect of the quantization of the output in a 4×4 antennas system         | . 32 |

| Figure 4.2: FER improvement due the use of one Newton-Raphson iteration               | . 33 |

| Figure 4.3: Different amounts of fractional bits in a 4×4 antennas system             | . 34 |

| Figure 4.4: Different amounts of integer bits in a 4×4 antennas system                |      |

| Figure 4.5: Different amounts of fractional bits in a 2×2 antennas system             | . 35 |

| Figure 4.6: Different amounts of integer bits in a 2×2 antennas system                |      |

| Figure 4.7: FER for different algorithms with floating point in a 4×4 antennas system |      |

| Figure 4.8: Average amount of visited nodes with floating point and 4×4 antennas      |      |

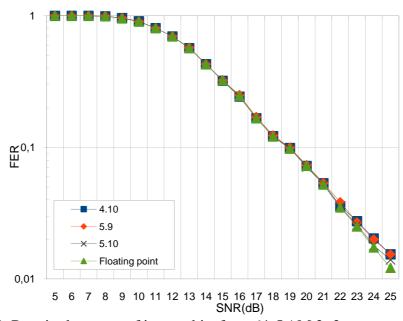

| Figure 4.9: FER for different number formats using the norm update (NU) technique.    |      |

| Figure 4.10: FER for different bias subtraction techniques                            |      |

| Figure 4.11: Average amount of visited nodes for different bias subtraction technique |      |

|                                                                                       | _    |

| Figure 4.12: FER for different sphere radii in using early bias subtraction           |      |

| Figure 4.13: Visited nodes for different sphere radii in using early bias subtraction |      |

| Figure 4.14: FER for different sphere radii in using intermediate bias subtraction    | . 42 |

| Figure 4.15: Visited nodes for different sphere radii in using intermediate bias      |      |

| subtraction                                                                           | . 42 |

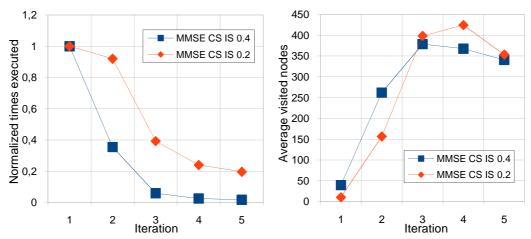

| Figure 4.16: Normalized executions and average visited nodes for each big loop        |      |

| iteration with 13dB and different constant sphere radii                               |      |

| Figure 4.17: FER for each bias subtraction method with its minimum sphere radius      |      |

| Figure 4.18: Visited nodes for each bias subtraction method with its minimum sphere   |      |

| radius                                                                                |      |

| Figure 4.19: FER for full fixed point systems with sigma estimation error             |      |

| Figure 4.20: Average amount of visited nodes for full fixed point systems with sigma  |      |

| estimation error                                                                      |      |

| Figure 4.21: FER for MMSE-ES with different constant $\sigma$ values                  | . 47 |

| Figure 4.22: Average visited nodes for MMSE-ES with different constant $\sigma$ values | 47 |

|----------------------------------------------------------------------------------------|----|

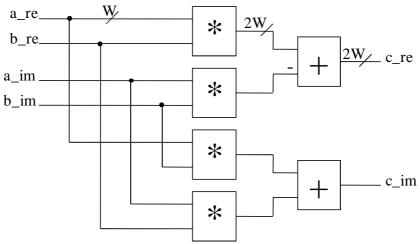

| Figure 5.1: Complex multiplier schematic                                               | 50 |

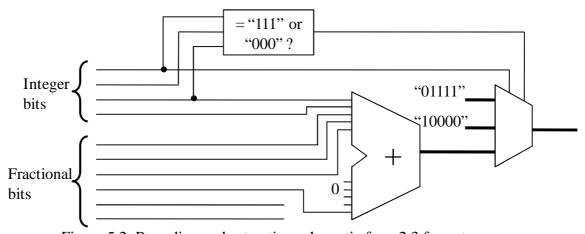

| Figure 5.2: Rounding and saturation schematic for a 2.3 format                         | 50 |

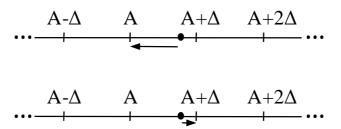

| Figure 5.3: Comparison of truncation (top) and rounding (bottom)                       | 51 |

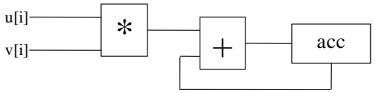

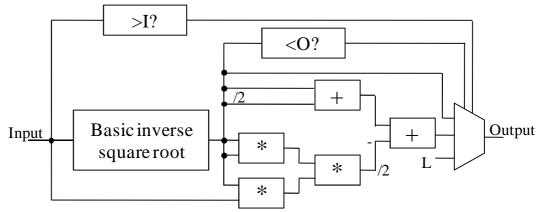

| Figure 5.4: Sequential inner product block                                             | 52 |

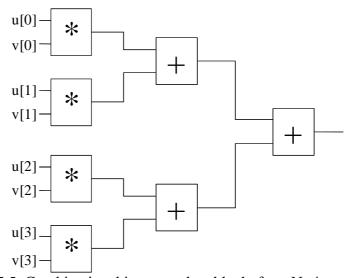

| Figure 5.5: Combinational inner product block, for a N=4 system                        | 52 |

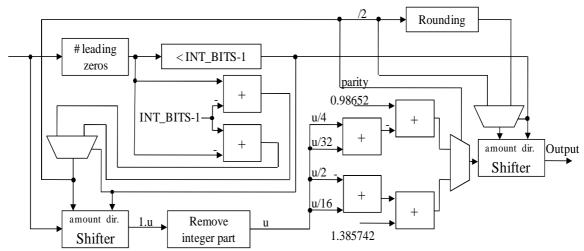

| Figure 5.6: Inverse square root approximation hardware structure                       | 53 |

| Figure 5.7: Inverse square root with improved approximation and overflow check         | 54 |

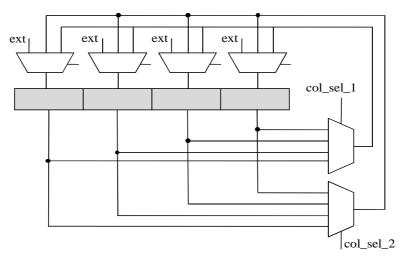

| Figure 5.8: Basic matrix storage block                                                 | 55 |

| Figure 5.9: Top level architecture for unsorted QR decomposition                       | 56 |

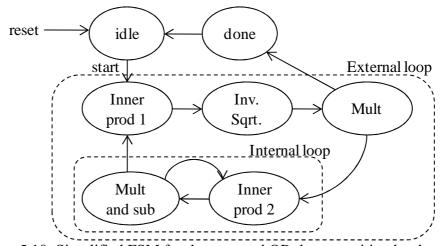

| Figure 5.10: Simplified FSM for the unsorted QR decomposition hardware                 | 57 |

| Figure 5.11: Swapping hardware for one row                                             | 58 |

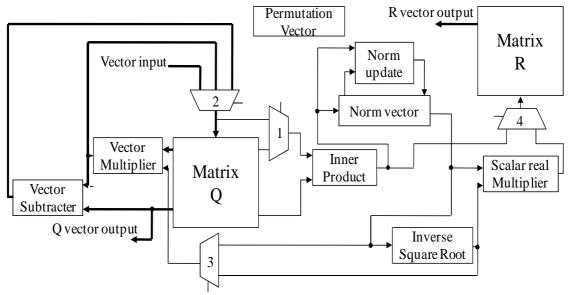

| Figure 5.12: Top level architecture for sorted QR decomposition                        | 58 |

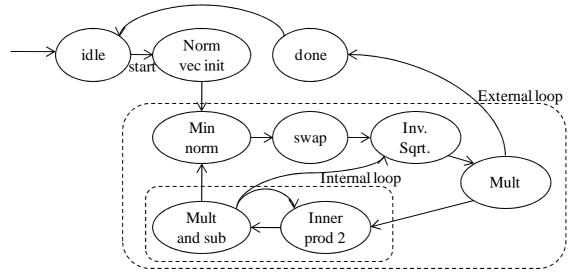

| Figure 5.13: Simplified FSM to perform the SQRD algorithm                              | 59 |

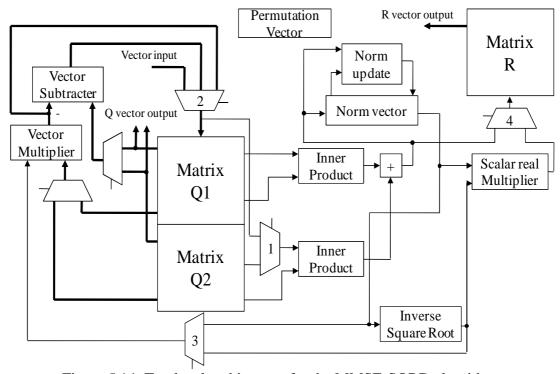

| Figure 5.14: Top level architecture for the MMSE-SQRD algorithm                        | 60 |

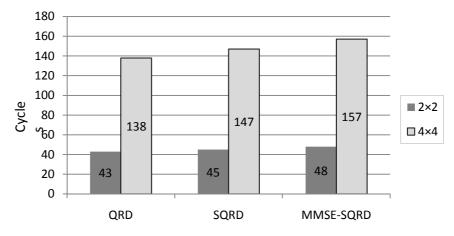

| Figure 6.1: Amount of cycles for each QR decomposition version                         | 62 |

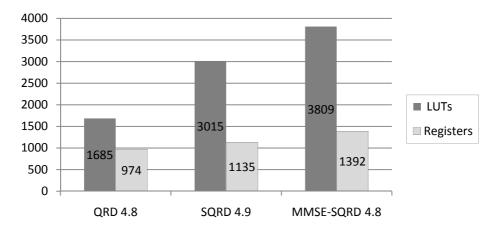

| Figure 6.2: Slice LUTs and registers for different algorithms in FPGA                  | 64 |

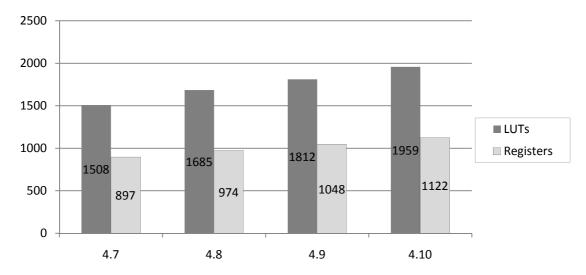

| Figure 6.3: FPGA area results for QRD using different number formats                   | 64 |

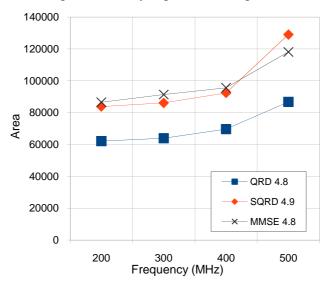

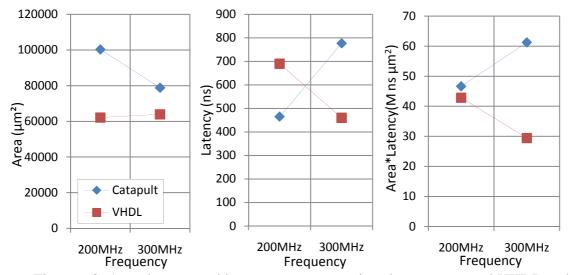

| Figure 6.4: ASIC area results for different algorithm versions and clock frequencies   | 65 |

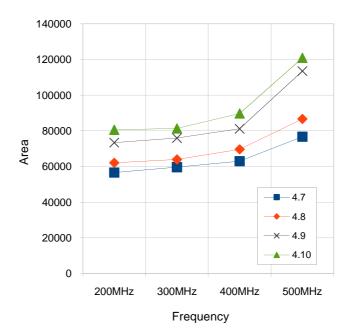

| Figure 6.5: ASIC area results for QRD using different number formats and clock         |    |

| frequencies                                                                            | 66 |

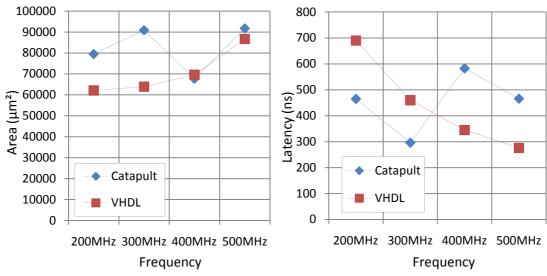

| Figure 6.6: Comparison between Catapult and manual VHDL implementations                | 67 |

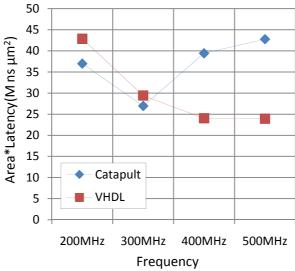

| Figure 6.7: Latency-area product for Catapult and manual VHDL implementations, in      |    |

| millions of ns.µm <sup>2</sup>                                                         | 67 |

| Figure 6.8: Area, latency and latency×area comparison between manual VHDL and          |    |

| Catapult versions synthesized with Synopsys DC                                         | 68 |

|                                                                                        |    |

## **LIST OF TABLES**

| Table 4.1: Default parameters for simulations                   | 32 |

|-----------------------------------------------------------------|----|

| Table 4.2: Parameters for simulations in Figure 4.1             | 33 |

| Table 4.3: Parameters for simulations in Figure 4.2             | 33 |

| Table 4.4: Parameters for simulations in Figure 4.3             | 34 |

| Table 4.5: Parameters for simulations in Figure 4.4             | 35 |

| Table 4.6: Parameters for simulations in Figure 4.5             |    |

| Table 4.7: Parameters for simulations in Figure 4.6             | 36 |

| Table 4.8: Parameters for simulations in Figures 4.7 and 4.8    | 38 |

| Table 4.9: Parameters for simulations in Figure 4.9             |    |

| Table 4.10: Parameters for simulations in Figures 4.10 and 4.11 | 40 |

| Table 4.11: Parameters for simulations in Figures 4.12 and 4.13 |    |

| Table 4.12: Parameters for simulations in Figures 4.14 and 4.15 | 43 |

| Table 4.13: Parameters for simulations in Figures 4.17 and 4.18 | 44 |

| Table 4.14: Parameters for simulations in Figures 4.19 and 4.20 |    |

| Table 4.15: Parameters for simulations in Figures 4.21 and 4.22 |    |

# Algoritmos de decomposição QR para sistemas MIMO: Impacto no esforço computacional e implementações de hardware

#### **RESUMO**

Dentre as abordagens para se atingir altas taxas de transmissão em sistemas de comunicação sem fio, uma se destaca como muito promissora: sistemas de múltiplas antenas (ou Multiple Input Multiple Output – MIMO), nos quais a informação é transmitida e recebida por mais de uma antena. Tais sistemas podem atingir altas taxas de transmissão usando, entre outras possibilidades, algoritmos de *sphere decoding* para decodificar os símbolos MIMO recebidos.

Para diversos algoritmos para detecção MIMO, tal como sphere decoding, uma variação do algoritmo de Fincke-Pohst (FINCKE, 1985), é necessário ter um hardware eficiente de decomposição QR, uma vez que esse é utilizado cada vez que a resposta impulsiva do canal modifica-se significativamente. E para obter-se uma implementação eficiente é necessário utilizar uma representação com ponto fixo para as matrizes, tanto por motivos de área quanto de latência.

Evidentemente, a perda de precisão resultante do uso de ponto fixo introduz erros nas matrizes calculadas, e é provável que isso leve a um aumento na taxa de erros de quadros (FER). Um dos propósitos deste trabalho é determinar a quantidade mínima de bits necessária para manter esse aumento suficientemente baixo. Este trabalho também avalia a redução no esforço computacional para execução de detecção MIMO por algoritmos baseados em busca em árvore resultante do uso de versões melhoradas do algoritmo de decomposição QR. Mais especificamente, a sorted QR decomposition (SQRD) e a minimum mean-square error SQRD são avaliadas.

O outro propósito deste trabalho é projetar arquiteturas de hardware capazes de computar a decomposição QR e suas variações para matrizes pequenas, tipicamente de 2ª e 4ª ordem. Também é importante obter uma descrição em VHDL desse hardware e comparar resultados de área e latência das diferentes versões.

Palavras-Chave: Decomposição QR, SQRD, MMSE-SQRD, Sphere Decoding.

#### **ABSTRACT**

Among the approaches to achieve high data rates in wireless systems, one rises as very promising: multiple-antenna systems (or Multiple Input Multiple Output – MIMO), in which the information is transmitted and received by multiple antennas. Such systems can achieve high data rates with using, among other possible choices, sphere decoding algorithms to decode the received MIMO symbols.

For many algorithms used for MIMO detection, such as sphere decoding, a variation of the Fincke-Pohst Algorithm (FINCKE, 1985), it is required to have an efficient QR decomposition hardware, since it is used each time the channel impulse response changes significantly. And to achieve an efficient hardware implementation it is necessary to use a fixed point representation for the matrices, both for area and latency purposes.

Evidently, the loss in precision resultant from fixed point precision introduces errors in the output matrices, and this is likely to lead to an increase in the frame error rate (FER). One of the purposes of this work is to determine the minimum amount of bits both for fractional and integer parts that are necessary to keep this increase sufficiently low. This work also evaluates the complexity reduction resultant from improved versions of the QR decomposition in tree-based search algorithms. More specifically, the sorted QR decomposition (SQRD) and the minimum mean-square error SQRD are evaluated.

The other main purpose of this work is to come up with hardware architectures capable of computing the QR decomposition and its improved versions (SQRD and MMSE-SQRD) for small matrices, typically of 2<sup>nd</sup> and 4<sup>th</sup> order. It is also important to have a fully functional VHDL description of this hardware and compare the different versions regarding area and latency.

**Keywords:** QR decomposition, SQRD, MMSE-SQRD, Sphere Decoding.

#### 1 INTRODUCTION

#### 1.1 Context and Motivation

Devices such as smart phones, laptops and other similar mobile communication gadgets are becoming growingly common. The applications heterogeneity is also increasing, since such devices can be used from applications as simple as sending text messages or reading e-mail up until watching live video streams. Many of these applications, especially those involving multimedia streams, require high data rates to be performed with satisfactory quality. Therefore, there is an increasing demand for devices able to transmit and receive efficiently at high speed and better techniques are required to increase spectral efficiency, while reducing error rates and decoding complexity.

In order to reach the expected data rates for future wireless systems, multiple-input multiple-output (MIMO) systems rise as one of the most promising techniques (GIMMLER, 2007), (LUETHI, 2008). In MIMO systems, multiple transmit antennas send MIMO symbols over the channel in the same frequency band, which are received also by multiple antennas. Such systems are especially attractive due to their high spectral efficiency (TELATAR, 1999). On the other hand, these systems have the drawback of increased complexity in the receiver, since it is responsible for determining which modulation symbol was sent by each transmit antenna.

Many different algorithms can be used to reduce the complexity of detecting MIMO symbols, such as sphere decoding and successive interference cancellation. For many of these algorithms, the QR decomposition is a critical operation to ensure a good quality of the successive decoding steps. Also, improved versions of the QR decomposition can be used to further improve the detection quality, reducing frame error rates or computational effort, depending on the detection algorithm used (WÜBBEN, 2001), (MENNENGA, 2009). A number of different QR decomposition architectures were proposed in other works, such as (SALMELA, 2008) and (LUETHI, 2008). In these works, however, the results are presented regarding the architecture itself, not addressing the overall system performance.

#### 1.2 Contributions

The extended versions of the QR decomposition evaluated, namely the sorted QR decomposition (SQRD) and the minimum mean-square error SQRD (MMSE-SQRD) can reduce the total computational effort associated with detecting a MIMO symbol, when tree-search based algorithms are used (MENNENGA, 2009). However, the actual reduction that can be achieved must still be measured and compared for each different version, concerning the complete communication chain. Also, the cost of using these algorithms must be evaluated, regarding increase in area and decomposition latency.

Therefore, in this work the computational effort and error rates of different versions of the QR decomposition are measured using a communication chain model. In order to obtain a fixed point implementation that is sufficiently precise, the error rates of different quantizations is also analysed.

A new QR decomposition hardware architecture is presented. The proposed architecture is extended to perform the SQRD and MMSE-SQRD. The implementation results are presented, regarding total area and latency, which is compared to the requirements of a real system's real time requirements. The results are also compared to those obtained from a high-level synthesis tool, the Mentor Graphics Catapult C.

#### 1.3 Report Structure

The remainder of this report is structured as follows. Chapter 2 presents the communication chain model and briefly describes each of its components. Chapter 3 describes the chosen QR decomposition algorithm and the investigated improvements. Chapter 4 explains the different simulation parameters and presents several simulation results. In chapter 5 the QR decomposition hardware architectures are presented and each of the required components is described. Chapter 6 analyses the area and timing results of the hardware implementations for FPGAs and ASICs. Finally, chapter 7 presents the conclusions.

#### 2 COMMUNICATION CHAIN MODEL

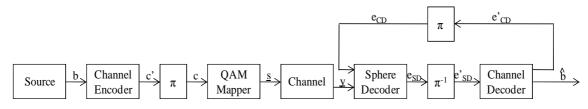

In order to evaluate the functionality and the results obtained from modifications applied to the system, a communication chain model is required. The used model consists of: source, channel encoder, interleaver, QAM mapper, channel, sphere decoder, de-interleaver and channel decoder.

Figure 2.1 shows the basic chain. The source generates a random bit sequence  $\mathbf{b}$ , in which each bit has an equal probability of being 1 or 0. This generated sequence is the input of the channel encoder, which can use many different algorithms, such as LDPC or convolutional codes. Since the evaluation of such algorithms is not in the scope of this work, only the latter is used. The used convolutional code has 64 states, and it is non-systematic, non-recursive and uses the Maxlog MAP (BCJR) algorithm. The encoded sequence  $\mathbf{c}'$  is then interleaved. The interleaved sequence  $\mathbf{c}$  is then mapped into a complex QAM symbols vector  $\mathbf{s}$  by the QAM mapper, and then transmitted by  $N_T$  antennas over a noisy channel with Rayleigh fading, to be received by  $N_R$  antennas.

The received sequence  $\mathbf{y}$  is then decoded by the sphere decoder, de-interleaved and then decoded by the channel decoder. This process is repeated iteratively, in the called big loop iterations. During this process, the sphere and channel decoders exchange logarithmic likelihood ratios (LLRs), which express the belief of each decoder for each bit being 1 or 0. The extrinsic information vector  $\mathbf{e}_{SD}$ , generated by the sphere decoder, is de-interleaved and then decoded by the channel decoder, which has two outputs: the  $\hat{\mathbf{b}}$  bit vector, and the extrinsic information vector  $\mathbf{e}'_{CD}$ . The latter is interleaved and used by the sphere decoder in the next big loop iteration. Both decoders are called softinput soft-output (SISO) decoders.

Figure 2.1: System model

#### 2.1 Channel model

The channel model describes how the transmitted symbols are modified before the reception. Typically it involves the addition of noise and, for the multiple antennas case, the multiplication by a channel impulse response matrix **H**.

When compared to the one used in (GIMMLER, 2007), one important change was made in the channel model. Instead of

$$y = \sqrt{\frac{SNR}{N_T}} H s + n \tag{2.1}$$

was used the model

$$y = \sqrt{\frac{1}{N_T}} Hs + \frac{n}{\sqrt{SNR}}$$

(2.2)

$\mathbf{y}: N_R \times 1$ , received symbol vector

$\mathbf{H}: \mathbf{N}_{\mathbf{R}} \times \mathbf{N}_{\mathbf{T}}$ , complex channel matrix

$\mathbf{s}: N_T \times 1$ , transmitted symbol vector

$\mathbf{n}: N_R \times 1$ , additive gaussian complex noise

This means that, instead of scaling the **H** matrix with the signal to noise ratio, the noise vector is divided by this same ratio. With this change we get a more predictable range for the values in **H**, since it is no longer scaled by the SNR. The other main difference caused by this change is the alteration of the sphere radius (SIMHA S, 2009), being much smaller than in (GIMMLER, 2007).

The **H** matrix and the noise vector  $\mathbf{n}$  are both constituted of complex random values, with mean zero and unit variance. In the rest of this work it is assumed that  $N_R = N_T = N$ .

#### 2.2 The Sphere Decoding algorithm

The sphere decoder has the purpose of determining the logarithmic likelihood ratio  $L_D$  of each bit  $b_j$  in the received complex vector  $\mathbf{y}$ . This numbers form a vector which represents the belief of the sphere decoder for each bit being 1 or 0.

$$L_D(b_j) = \ln \frac{P(b_j = 0)}{P(b_j = 1)}$$

(2.3)

This means that, if  $L_D(b_j) > 0$ , the hard-decision is  $b_j = 0$  and it is  $b_j = 1$  if  $L_D(b_j) < 0$ . Accordingly, if  $L_D(b_j) = 0$ , no information can be extracted, as  $P(b_j = 0) = P(b_j = 1)$ .

To determine the probability of each bit being 1 or 0, a search has to be performed through the solution space, where the distances between the received vector and the possible solutions in the discrete QAM constellation are considered. Assuming that the receiver knows the channel matrix  $\mathbf{H}$ , the squared Euclidean distance between the received  $\mathbf{y}$  vector and each possible solution vector  $\mathbf{s}$  is:

$$d(s) = \left\| y - Hs \right\|^2 \tag{2.4}$$

This distance is then updated with the logarithmic probabilities for each bit calculated in the previous big loop iteration by the channel decoder, and the sphere decoder then tries to find the symbol vector which results in the minimum distance:

$$\min(d(s) - \sum_{j} \log P(b_j)) \tag{2.5}$$

Where  $P(b_j)$  denotes the probability of the  $j^{th}$  bit having the value that was assumed for it in s. In other words, the purpose of this operation is to reduce the distance of the symbols that the channel decoder agrees with. However, these logarithmic probabilities are not used in this work. Instead, logarithmic likelihood ratios (LLRs) are used to approximate this value. The search performed by the sphere decoder then becomes:

$$\min(d(s) + \sum_{j} LLR(a_{j}, b_{j}))$$

(2.6)

where  $a_j$  is the a-priori information received from the channel decoder. The straightforward approach to find these minimum values is to try all possible values for s. However, it is clear that the computational effort required to analyse each possible s vector makes this approach very ineffective. For example, in a system with  $4\times4$  antennas and a 16-QAM constellation, we would have  $16^4 = 65536$  possibilities. A variation of the Fincke-Pohst algorithm can be used to reduce this problem, analyzing through a tree search only the elements that reside inside a sphere of a given radius. This reduces the search space and makes it possible to recursively calculate the squared Euclidean distance using partial Euclidean distances (PEDs). In order to do so, the equation for the distance needs to be modified, using the QR decomposition of matrix  $\mathbf{H}$ . This will be further discussed in section 2.2.1.

The output of the sphere decoder is also logarithmic likelihood ratios. They are calculated, however, as the difference of the minimum distance for this bit being 1 and 0:

$$\Lambda_j = \min 1_j - \min 0_j \tag{2.7}$$

These values keep the properties described for the L<sub>D</sub> values in equation 2.3.

Because during the big loop iterations only the new information discovered by the sphere decoder should be sent forward to the channel decoder, the added a-priori information  $a_j$  of bit  $b_j$  must be subtracted from the difference of the minima vectors, to form the output  $\mathbf{e}_{SD}$ .

$$e_{SD_i} = \Lambda_i - a_i \tag{2.8}$$

Since  $\Lambda_j$  is calculated as the mentioned difference, the a-priori information must be added in a manner that maintains the property in equation 2.9, so that its subtraction effectively removes its value from the result:

$$LLR(a_i, b_i = 1) - LLR(a_i, b_i = 0) = a_i$$

(2.9)

Therefore, the purpose of the LLR function in equation 2.6 is to transform the  $a_j$  values received in a vector which respects the property in 2.9. Several different implementations for this function are discussed in (GIMMLER, 2007). In this work, the version used adds only the a-priori information of bits that are 1:

$$LLR(a_{j},b_{j}) = \begin{cases} a_{j},b_{j} = 1\\ 0,b_{j} = 0 \end{cases}$$

(2.10)

#### 2.2.1 The usage of the QR decomposition

In order to simplify the calculation of the distance between the received vector and other constellation point vectors, the QR decomposition can be employed:

$$d(s) = ||y - Hs||^2 (2.11)$$

$$d(s) = ||y - QRs||^2 (2.12)$$

$$d(s) = ||Q^{H} y - Rs||^{2}$$

(2.13)

The QR decomposition of a matrix  $\mathbf{H}$  is a mathematical operation that generates two matrices, namely  $\mathbf{Q}$  and  $\mathbf{R}$ , which have the following properties:

- i) The columns of  $\mathbf{Q}$  are orthogonal (or *orthonormal*). That means the inner product of any two columns of  $\mathbf{Q}$  is zero, and the inner product of a column with itself is one (for the orthonormal case). From this fact derives the useful property that the inverse of  $\mathbf{Q}$  is its transpose (or Hermitian transpose, if  $\mathbf{Q}$  is complex).

- ii)  $\mathbf{R}$  is an upper-triangular matrix. That means that any element under the main diagonal is zero.

- iii) Finally, the product of **Q** and **R** must be **H**.

$$H = QR \tag{2.14}$$

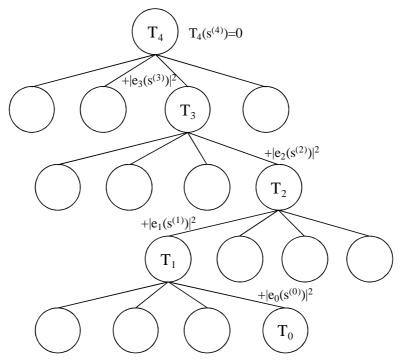

Using these definitions, a tree search can then occur in a tree with N+1 levels, with each level after the first standing for one element of the solution vector **s** and with each node having M children, where M is the number of possible constellation points in the used QAM modulation, as in Figure 2.2.

Figure 2.2: Tree search for a system with 4-QAM and 4×4 antennas

Starting at the root with a PED  $T_N(s^{(N)}) = 0$ , it is possible do build the tree downwards calculating the distances  $T_i(s^{(i)})$  recursively. Once a leaf node is reached, its distance  $T_0(s^{(0)})$  is actually the distance for the whole symbol sequence that connects it to root node. The a-priori information from the previous big loop iteration can also be added during process.

The partial Euclidean distances  $T_i(s^{(i)})$  are calculated recursively with the equation:

$$T_i(s^{(i)}) = T_{i+1}(s^{(i+1)}) + |e_i(s^{(i)})|^2$$

(2.15)

The partial increases  $|e_i(s^{(i)})|^2$ , already adding the a-priori information for the relevant bits, are obtained with:

$$\left| e_i(s^{(i)}) \right|^2 = \left| \hat{y}_i - \sum_{j=i}^{N-1} R_{ij} s_j \right|^2 + \sum_k LLR(a_k, b_k)$$

(2.16)

$$\hat{\mathbf{y}} = Q^H \mathbf{y} \tag{2.17}$$

Where k iterates the bits which form the current symbol  $s_i$ . To emphasize the effect of  $s_i$  in the partial Euclidean distance increase, equation 2.16 can be rewritten as:

$$\left| e_i(s^{(i)}) \right|^2 = \left| b_{i+1}(s^{(i+1)}) - R_{i,i}s_i \right|^2 + \sum_k LLR(a_k, b_k)$$

(2.18)

$$b_{i+1}(s^{(i+1)}) = \hat{y}_i - \sum_{j=i+1}^{N-1} R_{i,j} s_j$$

(2.19)

Note that equation 2.19 is equal for all brother nodes.

The sphere radius can be applied during this search: an intermediary node with a high PED can have its whole sub-tree excluded from the search, reducing the amount of evaluated possibilities and saving computational time.

#### 2.2.2 Sphere Shrinking

One important improvement that can be applied to the sphere decoding algorithm is sphere shrinking. The main purpose of this technique is to reduce the amount of visited nodes by reducing the sphere radius as the tree search proceeds.

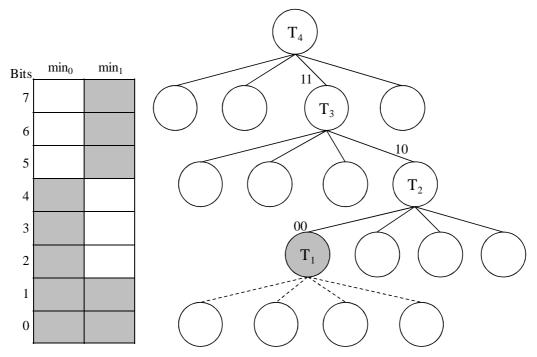

At any given stage of the tree search, it is possible to determine the maximum value of the distance of a leaf node that may cause an alteration in the minima vectors. The sphere shrinking radius SSR is equal to the largest value currently in a minima vector, since that any distance larger than this will not modify any position in the vectors and is, therefore, irrelevant for the output. Thus, if a node reaches this value at any point of the search, one can know that the entire sub-tree below it is irrelevant – which is the same as redefining the sphere radius. Evidently, if the initial radius ISR is smaller than this new value, it is kept.

$$SR = \min(ISR, SSR) \tag{2.20}$$

$$SSR = \max(\max(\min_{0}), \max(\min_{1}))$$

(2.21)

At this point, however, it is important to consider the manner in which the a-priori information is added, as it can be negative. This means that an intermediate node which lies outside the sphere can have a final point (or leaf node) under it which would cause an update in a minima vector, since negative a-priori information can cause the distance of a given branch in the tree to actually decrease as the search proceeds, provided it overcomes the positive PED. Even though this may occur with considerable frequency, its influence in the final error rates is not significant.

Among the LLR functions presented in (GIMMLER, 2007), one ensures that the apriori information is always positive (equation 2.22), which does not happen when equation 2.10 is used. However, equation 2.10 has other advantages: the amount of additions done is only the half of equation 2.22 and it needs to visit fewer nodes to achieve the same FER performance (GIMMLER, 2007).

$$LLR(a_{j},b_{j}) = \begin{cases} a_{j},b_{j} = 1 \land a_{j} \ge 0\\ -a_{j},b_{j} = 0 \land a_{j} < 0\\ 0, otherwise \end{cases}$$

(2.22)

Other improvements can be applied to the sphere shrinking. As the search proceeds down the tree, decisions are made for the value of each bit. This means that leaf nodes reached in the current sub-tree cannot affect the minima of the other value for the already decided bits. Hence, the definition of the SSR in equation 2.21 can be further improved to consider only the minima of the chosen values for the bits that lie upwards in the tree. Bits that are still to have their values chosen down the tree must have both minima considered. Figure 2.3 illustrates this for a system with 4×4 antennas and 4-QAM. Consider that the tree search is currently in the gray node, labelled T<sub>1</sub>, and needs to evaluate whether it is inside the sphere or not. The first six bits of the sequence already have their values defined, and therefore only those values can have their minima changed. The last two, on the other hand, are still undefined. For this reason, only the minima in gray need to be considered to determine the current radius, as they are the only ones that are eligible to be changed. The maximum value in the gray painted positions will be used as the sphere radius.

Figure 2.3: Sphere shrinking example for a 4×4 antennas system with 4-QAM

The last improvement of the sphere shrinking to be considered in this work is the ordering of the child nodes. This is called *ordered sphere shrinking*. The idea is to always choose the node with the smallest PED as the first candidate when descending the tree. This is a greedy algorithm used to obtain quickly leaf nodes with reasonably small distances and hence speed-up the shrinkage of the tree, further reducing the average amount of visited nodes.

#### 3 QR DECOMPOSITION ALGORITHM

The QR decomposition of a matrix **H** is defined as the matrices **Q** and **R**, where **Q** has orthonormal columns, **R** is upper-triangular and **H**=**QR**. There are many different algorithms to compute the QR decomposition, such as using the Gram-Schmidt process, Householder reflections or Givens rotations and variations (GOLLUB, 1996). In this work, the Gram-Schmidt process is used, due to its simplicity and vast use in previous works, such as (SALMELA, 2008), (WÜBBEN, 2001) and (LUETHI, 2008).

#### 3.1 The Gram-Schmidt process

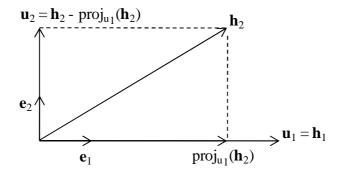

The Gram-Schmidt process initially orthogonalizes a set of vectors by subtracting the projection of one on the other. Figure 3.1 shows the process for two vectors.

Figure 3.1: Gram-Schmidt process for two vectors

To perform the process, the definitions of inner product and vector projection are necessary. Since we are working in an Euclidean space, the inner product of two vectors  $\mathbf{h}$  and  $\mathbf{u}$  is defined as the dot product:

$$\langle h, u \rangle = h[1]u[1] + h[2]u[2] + \dots + h[N]u[N]$$

(3.1)

If the vectors are complex, which is the case here, a slight alteration in this equation is necessary, where *conj* denotes the complex conjugate of a number:

$$\langle h, u \rangle = conj(h[1]).u[1] + conj(h[2]).u[2] + ... + conj(h[N]).u[N]$$

(3.2)

The projection of a vector  $\mathbf{h}$  on a vector  $\mathbf{u}$  can be defined as:

$$proj_{u}(h) = \frac{\langle u, h \rangle}{\langle u, u \rangle} u$$

(3.3)

Given these definitions, the Gram-Schmidt process is computed as follows, iteratively subtracting the projection of each vector on the others:

$$u_{1} = h_{1}$$

$$u_{2} = h_{2} - proj_{u1}(h_{2})$$

$$u_{3} = h_{3} - proj_{u1}(h_{3}) - proj_{u2}(h_{3})$$

$$\vdots$$

$$u_{k} = h_{k} - \sum_{i=1}^{k-1} proj_{uj}(h_{k})$$

(3.4)

We can consider that the vectors  $\mathbf{h}_k$  are the columns of the input matrix  $\mathbf{H} = (\mathbf{h}_1, \mathbf{h}_2, \dots, \mathbf{h}_N)$ , which were transformed into a set of orthogonal vectors  $\mathbf{u}_k$ . This set of vectors can be then transformed into an orthonormal set by dividing each element by its own modulus:

$$e_k = \frac{u_k}{\|u_k\|} \tag{3.5}$$

Since the inner product of two vectors is directly proportional to the norm of each vector, and the inner product of a vector with itself is its squared norm, the projections in equation 3.4 can be rewritten as:

$$proj_{u_{j}}(h_{k}) = \frac{\left\langle u_{j}, h_{k} \right\rangle}{\left\| u_{j} \right\|^{2}} u_{j} = \frac{\left\langle u_{j}, h_{k} \right\rangle}{\left\| u_{j} \right\|} e_{j} = \left\langle e_{j}, h_{k} \right\rangle e_{j}$$

(3.6)

Equation 3.4 can be rewritten using equation 3.6, the fact that  $\langle e_i, h_i \rangle e_i = u_i$ , since  $e_i$  has norm 1 and is collinear to  $u_i$ , and isolating the elements  $\mathbf{h}_k$ :

$$h_{1} = \langle e_{1}, h_{1} \rangle e_{1}$$

$$h_{2} = \langle e_{1}, h_{2} \rangle e_{1} + \langle e_{2}, h_{2} \rangle e_{2}$$

$$h_{3} = \langle e_{1}, h_{3} \rangle e_{1} + \langle e_{2}, h_{3} \rangle e_{2} + \langle e_{3}, h_{3} \rangle e_{3}$$

$$\vdots$$

$$h_{k} = \sum_{j=1}^{k} \langle e_{j}, h_{k} \rangle e_{j}$$

(3.7)

Rewriting the above equations in matrices results in:

$$H = (e_1 \mid e_2 \mid \dots \mid e_N) \begin{pmatrix} \langle e_1, h_1 \rangle & \langle e_1, h_2 \rangle & \dots & \langle e_1, h_N \rangle \\ 0 & \langle e_2, h_2 \rangle & \dots & \langle e_2, h_N \rangle \\ 0 & 0 & \ddots & \vdots \\ \vdots & \vdots & 0 & \langle e_N, h_N \rangle \end{pmatrix}$$

(3.8)

As the vectors  $\mathbf{e}_k$  are orthonormal and the second matrix in the above product is upper triangular, it can be seen that the first and second matrices in the right hand side of equation 3.8 are, respectively,  $\mathbf{Q}$  and  $\mathbf{R}$ .

#### 3.2 Modified Gram-Schmidt process

The direct application of the Gram-Schmidt process in a system with finite precision (such as any computational system) yields poor results. More specifically, the

orthogonality of the columns of **Q** is seriously damaged as the precision is reduced (GOLLUB, 1996).

These results can be improved by an alteration in the ordering in which the calculations are done, resulting in the algorithm called Modified Gram-Schmidt (MGS) (GOLLUB, 1996), which calculates, at each iteration of its external loop, one column of the **Q** matrix and one row of the **R** matrix.

Let  ${\bf H}$  denote the input matrix,  ${\bf h}_k$  denote the  $k^{th}$  column of  ${\bf H}$  and  ${{\bf q}_k}^H$  denote the Hermitian transpose of  $\mathbf{q}_k$ . A pseudo-code for this algorithm is:

```

R = 0

for k=0:N-1

R(k, k) = || \mathbf{h}_k ||

\mathbf{q}_k = \mathbf{h}_k / R(k, k)

for j=k+1:N-1

R(k, j) = q_k^H. h_i

\mathbf{h}_{i} = \mathbf{h}_{i} - \mathbf{q}_{k} . R(k, j)

end

end

```

Algorithm 1: Modified Gram-Schmidt Process (MGS)

This version of the algorithm, however, has some visible hardware implementation issues. First, it requires the calculation of the norm of a vector, which implies the need of a square root hardware. Second, there is the need for a division hardware. And, if this vector division operation is ever to be parallelized, then many instances of this hardware would be required.

One approach to avoid these implementation issues is presented at (SALMELA, 2008). Instead of calculating the norm of the vector, the inverse square root is calculated directly. This allows the replacement of the divisions by multiplications. The actual square root, necessary to form the main diagonal of the **R** matrix, can be calculated using the mathematical property:

$$\sqrt{x} = x^{1/2} = xx^{-1/2} = x\frac{1}{\sqrt{x}}$$

(3.9)

This means that multiplying the input and the output of the inverse square root hardware results in the square root of the input. The gain in area from this alteration can be even larger if an approximation hardware is used, rather than an exact one, to calculate the inverse square root. The hardware used for this purpose is further discussed and presented in chapter 5. However, in order to keep this approximation close enough to the correct result, numeric methods such as the Newton-Raphson method can be used.

Given a function f(y), its derivative f'(y) and an initial guess for a root  $y_0$ , the Newton-Raphson method can be used to improve this guess, iteratively finding a better root approximation (PRESS, 1992):

$$y_{i+1} = y_i - \frac{f(y_i)}{f'(y_i)}$$

(3.10)

The equation for the inverse square root must then be rewritten:

$$\frac{1}{\sqrt{x}} = y \tag{3.11}$$

$$\frac{1}{v^2} = x \tag{3.12}$$

Then the function f(y) must be defined in a way that when f(y) = 0, y =  $1/\sqrt{x}$ :

$$f(y) = \frac{1}{y^2} - x \tag{3.13}$$

Its derivative is:

$$f'(y) = \frac{-2}{y^3} \tag{3.14}$$

By applying 3.13 and 3.14 to 3.10, equation 3.15 is obtained:

$$y_{i+1} = y_i + \frac{y_i}{2} - \frac{y_i^3 x}{2}$$

(3.15)

This equation can be applied iteratively to make y a better approximation of the inverse square root of x. In this work, only one iteration was considered.

Let isqrt\_i and isqrt\_o denote, respectively, the input and the output of the inverse square root hardware. The again modified algorithm, now using the inverse square root and multiplications, becomes:

$$\begin{aligned} & \mathbf{for} \ \mathbf{k}{=}0\text{:}N{-}1 \\ & \text{isqrt}\_\mathbf{i} = \mathbf{h_k}^H.\ \mathbf{h_k} \\ & \text{isqrt}\_\mathbf{o} = 1/\sqrt{\text{isqrt}\_\mathbf{i}} \\ & R(k,k) = \text{isqrt}\_\mathbf{i}.\text{isqrt}\_\mathbf{o} \\ & \mathbf{q_k} = \mathbf{h_k}.\text{isqrt}\_\mathbf{o} \\ & \mathbf{for} \ \mathbf{j}{=}\mathbf{k}{+}1\text{:}N{-}1 \\ & R(k,j) = \mathbf{q_k}^H.\ \mathbf{h_j} \\ & \mathbf{h_j} = \mathbf{h_j} - \mathbf{q_k}.\ R(k,j) \\ & \mathbf{end} \\ & \mathbf{end} \end{aligned}$$

Algorithm 2: MGS modified for hardware implementation

This algorithm has yet the undesired property that the input matrix  $\mathbf{H}$  is altered during its execution and therefore it would need to be copied by the hardware to an internal memory. However, after the  $k^{th}$  column of  $\mathbf{Q}$  is calculated, the  $k^{th}$  column of the

copy of  $\mathbf{H}$  is no longer used. For this reason, also as suggested in (GOLLUB, 1996), this code can be further improved with the merge of this copy of the input matrix and  $\mathbf{Q}$ . Therefore, Algorithm 3 is also functional, given that  $\mathbf{Q}$  is initialized with the input matrix:

```

R = 0; Q = H

\mathbf{for} \ k=0:N-1

isqrt\_i = \mathbf{q_k}^H. \ \mathbf{q_k}

isqrt\_o = 1/\sqrt{isqrt\_i}

R(k, k) = isqrt\_i.isqrt\_o

\mathbf{q_k} = Q(0:N-1, k).isqrt\_o

\mathbf{for} \ j=k+1:N-1

R(k, j) = \mathbf{q_k}^H. \ \mathbf{q_j}

\mathbf{q_j} = \mathbf{q_j} - \mathbf{q_k} \ . \ R(k, j)

\mathbf{end}

```

Algorithm 3: MGS with improved memory usage

#### 3.3 Sorted QR Decomposition

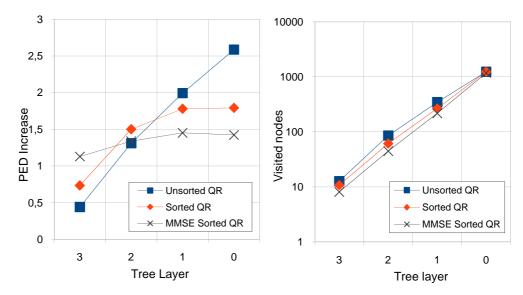

The order in which the transmitted signals are evaluated can affect the performance of the sphere decoding algorithm (STUDER, 2008). This order can be modified using the sorted QR decomposition (SQRD) algorithm.

The intent of the SQRD is to sort the elements of main diagonal of  $\mathbf{R}$ ,  $\mathbf{R}_{k,k}$ , decreasingly in the order of evaluation of the sphere decoding algorithm, i.e. from the bottom right corner to the top left corner. The benefits of doing so can be seen in equation 2.18: the larger  $\mathbf{R}_{k,k}$  is, the more different will the PED increases of each brother node be, as  $\mathbf{R}_{k,k}$  can amplify the value of  $s_i$  and thus improve the range of the search. This effectively increases the average PED and average PED variance in the layers closer to the root, which will result in more branches reaching the sphere radius in the top layers and therefore being left out of the search.

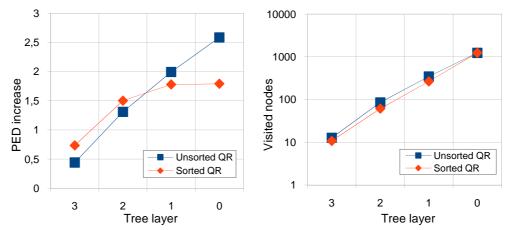

Figure 3.2: Average PED increase and average number of visited nodes per layer for a 4×4 system, with 16-QAM and a SNR of 12dB

Figure 3.3: Average PED increase variance per layer for a 4×4 system, with 16-QAM and a SNR of 12dB

Also, as we get closer to the leaf nodes, the PED increases become smaller than those of the unsorted QR decomposition system. This leads to the evaluation of almost the same amount of leaf nodes, which are the ones that actually define the output. Figure 3.2 shows the average partial Euclidean distance and amount of visited nodes per tree layer for a 4×4 16-QAM system with 12dB of SNR. Figure 3.3 shows the average variance. Both variations use a constant sphere radius of 0.8 and present similar frame error rates.

The SQRD algorithm used in this work is based on the one presented in (WÜBBEN, 2001). As the elements  $\mathbf{R}_{k,k}$  are calculated in the inverse order of their usage in the sphere decoder, the algorithm tries to minimize each element it calculates. Inspecting Algorithm 3, one can realize that these elements are calculated from the norm of the columns of  $\mathbf{Q}$ , which was initialized with the input matrix. This SQRD algorithm chooses, before calculating each  $\mathbf{R}_{k,k}$ , the column of  $\mathbf{Q}$  with the smallest norm and swaps it with the  $k^{th}$  column. The same exchange is done in  $\mathbf{R}$  and  $\mathbf{p}$ , which is the permutation vector. It is initialized with 0, 1, ..., N-1 and in the end of the computation it will have a record of the swaps that were done.

```

\begin{split} R = 0; & Q = H \\ \textbf{for } k = 0 : N - 1 \\ & i = arg \min_{j = k: N - 1} \parallel \mathbf{q}_j \parallel^2 \\ & \text{Exchange columns } k \text{ and } i \text{ in } Q, R \text{ and } p \\ & R(k, \, k) = \parallel \mathbf{q}_k \parallel \\ & \mathbf{q}_k = \mathbf{q}_k \, / \, R(k, \, k) \\ & \textbf{for } j = k + 1 : N - 1 \\ & R(k, \, j) = \mathbf{q}_k \overset{H}{\cdot} \cdot \mathbf{q}_j \\ & \mathbf{q}_j = \mathbf{q}_j - \mathbf{q}_k . R(k, \, j) \\ & \textbf{end} \\ & \textbf{end} \end{split}

```

Algorithm 4: Sorted QR decomposition (SQRD)

It is important to note that the ordering obtained by Algorithm 4 is an approximation, rather than the exact optimal ordering. For simplicity, the algorithm is presented with the original mathematical definitions of Algorithm 1.

In Algorithm 4, however, it is clear that the addition of sorting to the algorithm is expensive. It involves calculating the squared norm (inner product with itself) of the  $k^{th}$  vector and all vectors to the right of it at each iteration, instead of only the squared norm of the  $k^{th}$  vector. In a 4×4 system, for example, this means that 6 extra squared norm calculations are to be done.

However, Algorithm 4 can be improved to calculate the norm of each column of  $\mathbf{Q}$  only once, and then only update this value as the projections are subtracted in the inner loop (WÜBBEN, 2003). This is done with a norm vector, which contains the squared norm of each column of  $\mathbf{Q}$ . Let *conj* denotes the complex conjugate of a number. The SQRD algorithm using the norm update method becomes:

```

R = 0; Q = H

for k=0:N-1

norm(k) = ||\mathbf{q}_k||^2

end

for k=0:N-1

i = arg \min_{j=k:N-1} norm(j)

Exchange columns k and i in Q, R, p and norm

R(k, k) = ||\mathbf{q}_k||

\mathbf{q}_k = \mathbf{q}_k / R(k, k)

for j=k+1:N-1

R(k, j) = \mathbf{q}_k^H. \mathbf{q}_j

\mathbf{q}_j = \mathbf{q}_j - \mathbf{q}_k.R(k, j)

norm(j) = norm(j) - conj(R(k, j)).R(k, j)

end

end

```

Algorithm 5: Improved sorted QR decomposition (SQRD)

With this improvement, the amount of inner products to be calculated remains the same as in the unsorted QR decomposition, and the complexity increase is reduced to the ordering and norm updating steps.

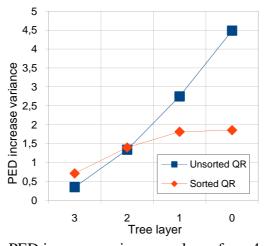

The **p** vector obtained after the computation of the SQRD is necessary to reorder the output, so that it matches the values expected by the channel decoder, as shown in Figure 3.4. The a-priori information obtained from the channel decoder also needs to be reordered to match the new sorting of the transmit antennas.

Figure 3.4: Receiver modified for SQRD usage

#### 3.4 MMSE Pre-processing

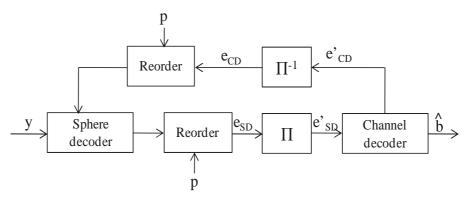

As the SQRD algorithm, the minimum mean squared error (MMSE) pre-processing was initially developed to be used with linear decoders (WÜBBEN, 2003). For those detectors, as the name suggests, it is used to reduce the probability of errors, as is the SQRD algorithm. The same modification happens when this technique is brought to sphere decoders, i.e. it can be used to reduce the amount of visited nodes (MENNENGA, 2009). It can also be coupled with the SQRD algorithm, thus achieving further complexity reductions. Also as occurs with SQRD, the MMSE pre-processing reduces the average amount of visited nodes by increasing the average PED and the average PED increase variance in the top layers, allowing bad branches to be pruned earlier in the tree, as shown in Figures 3.5 and 3.6.

The MMSE pre-processing is done using an extended  $(N_T+N_R) \times N_T$  matrix as the input. In our particular case, the input matrix dimensions become  $2N\times N$ . Let  $I_N$  denote the N-order identity matrix and  $\sigma$  denote the standard deviation of the noise vector. The modified matrices then become:

$$H' = \begin{bmatrix} H \\ \sigma I_N \end{bmatrix} = Q'R' = \begin{bmatrix} Q_1 \\ Q_2 \end{bmatrix} R' \tag{3.16}$$

Where  $Q_1$  and  $Q_2$  are square matrices of order N.

It is important to note at this point that, from equation 3.16,  $\sigma I_N = Q_2 R'$ . From this comes that:

$$R^{-1} = \frac{1}{\sigma} Q_2 \tag{3.17}$$

This means that  $Q_2$  is the scaled inverse of R'. Since R' is an upper-triangular matrix, so is  $Q_2$ . This property will be used during the hardware architecture design.

The value of  $\sigma$  for the used channel model (equation 2.2) is associated with the signal to noise ratio. Since the **n** vector has a standard deviation of 1 and it is scaled by the inverse square root of the SNR, the noise standard deviation is:

$$\sigma = \frac{1}{\sqrt{SNR}} \tag{3.18}$$

Figure 3.5: Average PED increase and average number of visited nodes per layer for a 4×4 system, with 16-QAM and a SNR of 12dB

Figure 3.6: Average PED increase variance per layer for a 4×4 system, with 16-QAM and a SNR of 12dB

Aside from the different size and initialization of  $\mathbf{Q}$ , the algorithm to perform the MMSE-SQRD is almost equal to that of the original SQRD. The main difference is that not all rows of  $\mathbf{Q}$  are swapped, only the first N+i. In order to match the extended output matrix  $\mathbf{Q}$ , the received vector  $\mathbf{y}$  also needs to be modified, becoming  $\mathbf{y}^* = [\mathbf{y} \ 0_N]^T$ , where  $0_N$  denotes the N-order zero vector. This way, the resulting vector becomes:

$$\hat{y}' = Q'^{H}.y' = Q_{1}^{H}.y \tag{3.19}$$

The  $\hat{y}'$  vector has the same dimension of the original  $\hat{y}$  vector and is then used in the same way by the sphere decoder.

The algorithm to perform the SQRD in the modified matrices is:

$$\begin{split} R &= 0; \, Q_1 = H; \, Q_2 = \sigma I_N; \, p = [0, \, 1, \, ..., \, N\text{-}1] \\ & \textbf{for } k\text{=}0\text{:}N\text{-}1 \\ & \textbf{norm}(k) = \parallel \mathbf{q}_k \parallel^2 \\ & \textbf{end} \\ & \textbf{for } k\text{=}0\text{:}N\text{-}1 \\ & i = \arg\min_{j=k:N-1} \text{norm}(j) \\ & \text{Exchange columns } k \text{ and } i \text{ in } R, \, p \text{ and norm and the first } N\text{+}i \text{ rows of } Q \\ & R(k, \, k) = \parallel \mathbf{q}_k \parallel \\ & \mathbf{q}_k = \mathbf{q}_k \, / \, R(k, \, k) \\ & \textbf{for } j \text{=} k\text{+}1\text{:}N\text{-}1 \\ & R(k, \, j) = \mathbf{q}_k \, ^H . \, \mathbf{q}_j \\ & \mathbf{q}_j = \mathbf{q}_j - \mathbf{q}_k . R(k, \, j) \\ & \text{norm}(j) = \text{norm}(j) - conj(R(k, \, j)).R(k, \, j) \\ & \textbf{end} \\ & \textbf{end} \end{split}$$

Algorithm 6: Sorted QR decomposition with MMSE pre-processing

#### 3.4.1 Bias subtraction

As a result from the mentioned alterations in the matrices and vectors, the MMSE pre-processing introduces a bias in the distance calculation metrics (MENNENGA, 2009):

$$||y'-H's||^2 = ||y-Hs||^2 + \sigma^2 ||s||^2$$

(3.20)

This bias must be subtracted from the distance calculated by the sphere decoder in order to avoid an increase in the error rates. There are many different ways to do so, and in this work, three different approaches were evaluated.

Aside from the bias, the distances themselves are modified by the MMSE algorithm, which means that the optimal values for the sphere radius that are used with the other QRD algorithms may not apply directly in this case, and are also likely to be different for each norm subtraction method. Further analysis and simulation results on this matter can be found in chapter 4.

#### 3.4.1.1 Late subtraction

One of the possible approaches is to subtract the bias as late as possible. This means that the sphere decoding is executed completely ignoring the bias and then it is subtracted only when the LLRs are calculated:

$$\Lambda_{j} = (\min 1_{j} - bias 1_{j}) - (\min 0_{j} - bias 0_{j})$$

(3.21)

This approach has, however, some disadvantages. First, it is necessary to keep track of the bias that was introduced in each bit when the minimum distance for it being 0 or

1 was found, which requires two extra vectors. Second, the minima vectors update is done with biased distances. Since the bias is the norm of the s vector, multiplied by  $\sigma$ , this creates a preference for points that are closer to the origin of the QAM constellation, which will have reflections in the resultant error rates.

#### 3.4.1.2 Early subtraction

As the distances are calculated recursively by the algorithm, so can the bias subtraction be done. The module of the s vector can be separated into the module of each individual symbol, and this value can be subtracted directly as the PEDs are calculated. The unbiased PEDs are calculated with:

$$\left| e_i(s^{(i)}) \right|^2 = \left| \hat{y}_i - \sum_{j=i}^{N-1} R_{ij} s_j \right|^2 + \sum_k LLR(a_k, b_k) - \sigma^2 |s_i|^2$$

(3.22)

The advantages of this approach are that, since the subtraction is done as early as possible, the system is entirely bias-free. Also, it requires no extra storage elements. However, it has a tendency of visiting more nodes than the other approaches, since the bias is always positive and therefore the PEDs obtained with this method are always smaller. On the other hand, this may mean that smaller sphere radii are acceptable when using early subtraction.

#### 3.4.1.3 Intermediate subtraction

This method is an attempt to take the main advantages of the two others. In order to avoid a preference for points closer to the origin, the bias must be subtracted before the minima vectors are updated. However, to reduce the amount of visited nodes, the bias must be subtracted after the PEDs are compared to the sphere radius. With these two restrictions, the only sphere decoder step to perform the bias subtractions is when a leaf node is reached, before the minima update.

To do so, whenever a leaf node is reached, the sphere decoder must calculate the bias associated with the symbols in the path towards the tree root and then subtract it from the distance associated with the point that was reached. The unbiased distance is then used to update the minima vectors.

This approach requires no extra storage elements when using a constant sphere radius. However, when sphere shrinking is used, the minima vectors are used to dynamically determine the sphere radius. Since the PEDs are still biased and the minima are not, this causes the comparison of a biased distance with an unbiased sphere radius, resulting in the early exclusion of many relevant branches from the tree. To avoid this problem, auxiliary vectors are necessary to keep the biased minima vectors. These vectors are used to determine the sphere radius and the unbiased ones to calculate the LLRs in the end of the execution.

#### 4 SIMULATION CHAIN AND RESULTS

The model described in chapter 2 was entirely coded as a C++ simulation model, using the IT++ library for vector and matrix handling. The main purpose of this model was to analyse the effects that the changes in the QR decomposition algorithm would have in the resultant FER and computational effort.

To evaluate this changes, the QR decomposition algorithm was coded with the ac\_fixed and ac\_complex data types, provided with Mentor Graphics' Catapult. These types allow the definition of the amount of integer and fractional bits, signedness, rounding and saturation. The rest of the chain remained with floating point precision. With this approach it is possible to evaluate the isolated effects of the fixed point precision in the QR decomposition, since the rest of the system remains equal.

In most graphs, the result with floating point QR decomposition is also plotted, for comparison reasons. The format x.y denotes x integer bits, including the sign bit, and y fractional bits for fixed point implementations.

#### 4.1 Simulation parameters

There are many different parameters that define each simulation. Regarding the communication chain as a whole, there are the amount of different QAM symbols (and the according amount of bits represented by each symbol), the size of the frame word, the amount of transmit and receive antennas (as mentioned, these two numbers are considered always the same in this work), the signal to noise ratios to be simulated and the amount big loop iterations to be executed. Considering simulation-only parameters, the most important is used to define the end of the simulation. The parameter used was a limit of frame errors, typically 50, 100 or 150. However, aside from this frame error limit, there was also a limit of frames sent, which in all cases was 100000.

Another important fact is that early-stopping is used to accelerate the simulation. This means that if the output is correct before the last big loop iteration, the process is finished and the chain moves to the next frame.

Concerning the sphere decoder itself, the main parameters are the sphere radius to be used and the usage of sphere shrinking, as discussed in chapter 2.

As for the QR decomposition, the most important parameters are the amount of integer and fractional bits and the usage or not of saturation and rounding. Another important parameter is the usage or not of a Newton-Raphson iteration at the output of the approximation inverse square root hardware. This has a huge influence in the resulting FER.

Some of these parameters are kept equal in all simulations, since they are not a part of the scope of analysis. It is used 5 big loop iterations and an initial sphere radius of

0.8, which is sufficient to allow a small loss (SIMHA S, 2009), unless stated otherwise. Also the equation for addition of a-priori information is not changed. All fixed point operations were executed with rounding and saturation. The use of rounding means that the quantization of the input matrix and the reduction of the output of the multipliers consider the most significant bit left out of the result. If this bit is 1, then 1 is added to the least significant bit of the result. The use of saturation means that, whenever an overflow would happen, the result is replaced with the largest number possible in the used representation format. Unless stated otherwise, the values in table 4.1 are the ones used in the simulations.

| Parameter             | Value    |

|-----------------------|----------|

| Initial sphere radius | 0.8      |

| M (QAM Symbols)       | 16       |

| Frame word size       | 994 bits |

| Big loop iterations   | 5        |

| Sent frames limit     | 100000   |

Table 4.1: Default parameters for simulations

#### 4.2 Simulation results

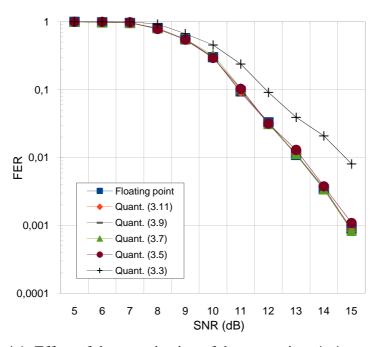

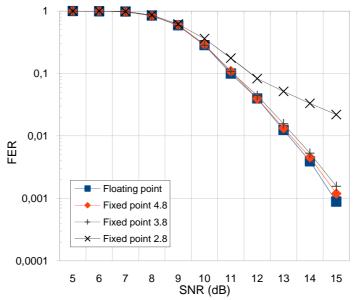

#### 4.2.1 Effect of the quantization of the output

The effect of a fixed point output can be analysed isolated from the effect of the whole algorithm running with fixed point precision. This allows the determination of how many bits are needed in the output. The full floating point algorithm was executed and then the output's precision was limited according to different amounts of bits. However, these amounts are not necessarily related to the amount of bits necessary in the internal calculations.

Figure 4.1: Effect of the quantization of the output in a  $4\times4$  antennas system

| Table 4.2:  | <b>Parameters</b> | for | simul  | lations | in  | Figure   | 4.1 | 1 |

|-------------|-------------------|-----|--------|---------|-----|----------|-----|---|

| 1 4010 1.2. | 1 didilictors     | 101 | billiu | lations | 111 | 1 15 uic |     |   |

| Parameter          | Value |

|--------------------|-------|

| Number of antennas | 4     |

| Frame errors limit | 50    |

In Figure 4.1 it is possible to see that 3 integer bits and 5 fractional bits are enough to represent the output without significant increase in the FER, compared to the floating point output. However, when the number of fractional bits is further reduced to 3, this increase becomes much greater.

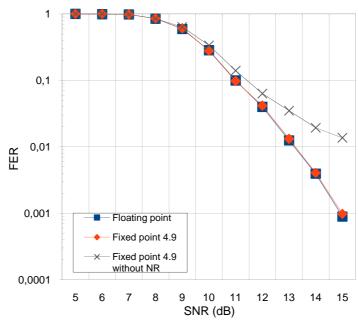

#### 4.2.2 Effect of a Newton-Raphson iteration

The application of Newton-Raphson iterations is a well known method for improving the approximation of a function. One single iteration is used here to improve the output of the inverse square root approximation hardware. Figure 4.2 shows the FER gain resultant from this, using a fixed point unsorted QR decomposition, compared to the floating point version.

Figure 4.2: FER improvement due the use of one Newton-Raphson iteration

Table 4.3: Parameters for simulations in Figure 4.2

| Parameter          | Value |

|--------------------|-------|

| Number of antennas | 4     |

| Number format      | 4.9   |

| Frame errors limit | 100   |

As the FER is significantly increased when the Newton-Raphson iteration is not used, all further simulations using fixed point formats consider that this optimization is activated.

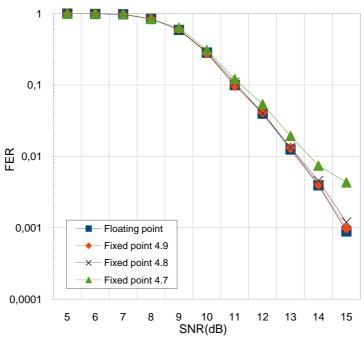

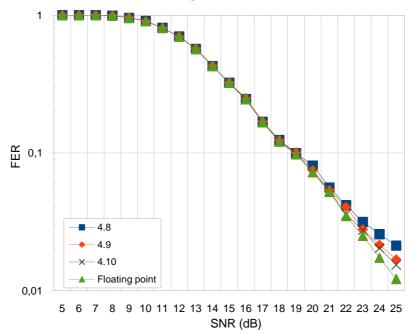

#### 4.2.3 Amount of bits necessary for 2×2 and 4×4 systems

As the system to be developed requires satisfactory performance with both  $2\times2$  and  $4\times4$  antennas, one must analyse the minimum amount of bits required for the integer and fractional parts of both systems. Sections 4.2.3.1 to 4.2.3.4 analyse separately how many bits are required for each part of both system configurations, considering 16-QAM modulation. Section 4.2.3.5 analyses the required precision for a system targeting both configurations.

#### 4.2.3.1 Amount of fractional bits for $4\times4$ antennas

To obtain the minimum amount of fractional bits necessary to introduce only a tolerable FER in a 4×4 antennas system, different formats were tested.

Figure 4.3: Different amounts of fractional bits in a 4×4 antennas system

ParameterValueNumber of antennas4Frame errors limit100

Table 4.4: Parameters for simulations in Figure 4.3

Simulations started with 9 fractional bits, value which was further decreased until the introduced FER became significant. As can be seen in Figure 4.3, 8 fractional bits are enough to introduce little increase to the FER.

#### 4.2.3.2 Amount of integer bits for $4\times4$ antennas

As was done for the fractional bits, different amounts of integer bits were tested decreasingly until the introduced FER became too large.

Figure 4.4: Different amounts of integer bits in a 4×4 antennas system

Table 4.5: Parameters for simulations in Figure 4.4

| Parameter          | Value |

|--------------------|-------|

| Number of antennas | 4     |

| Frame errors limit | 100   |

As can be seen in Figure 4.4, the introduced FER with 3 integer bits could still be considered tolerable. With 2 integer bits, the FER introduced is too large for any real application.

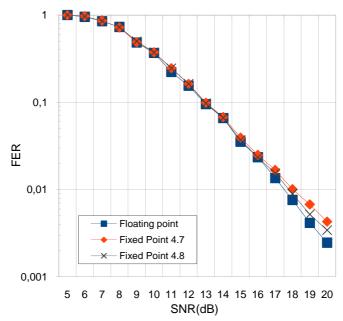

#### 4.2.3.3 Amount of fractional bits for $2\times 2$ antennas

As for  $4\times4$  antennas, the analysis for the optimal fixed point format was done for a  $2\times2$  antennas system.

Figure 4.5: Different amounts of fractional bits in a  $2\times2$  antennas system

| Table 4.6: Parameters | for | simul | lations | in | Figure 4 | .5 |

|-----------------------|-----|-------|---------|----|----------|----|

|                       |     |       |         |    |          |    |

| Parameter          | Value |

|--------------------|-------|

| Number of antennas | 2     |

| Frame errors limit | 150   |

As shown in Figure 4.5, the system exhibits satisfactory behaviour with 8 fractional bits. The degradation with 7 fractional bits can be considered tolerable, depending on the application.

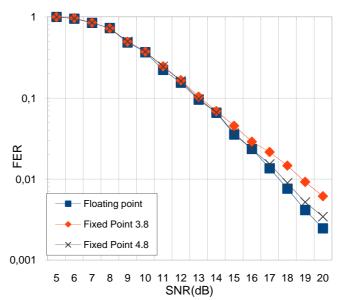

#### 4.2.3.4 Amount of integer bits for $2\times 2$ antennas

The same approach was applied to the amount of integer bits in a  $2\times 2$  antennas system.

Figure 4.6: Different amounts of integer bits in a  $2\times2$  antennas system

Table 4.7: Parameters for simulations in Figure 4.6

| Parameter          | Value |

|--------------------|-------|

| Number of antennas | 2     |

| Frame errors limit | 150   |

Figure 4.6 shows that it is required to have 4 integer bits in a  $2\times2$  antennas system in order to not introduce a large degradation, compared to the floating point implementation.

#### 4.2.3.5 Total amount of bits

For the 4×4 system, it was determined that 3 integer and 8 fractional bits are enough. However, for the 2×2 system, 4 integer and 7 or 8 (according to application specifications) fractional bits are required. Therefore, a QR decomposition hardware that is intended for both systems should have 4 integer and 8 fractional bits to ensure a tolerable loss in precision for all cases. It is important to emphasize that this results are valid specifically for the 16-QAM modulation used. For higher order constellations, more bits may be required.

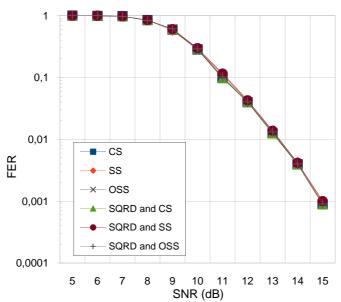

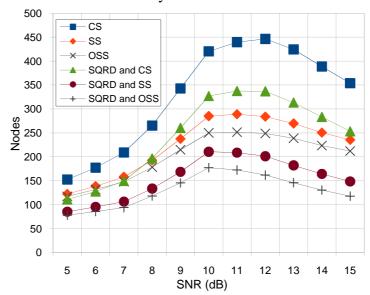

### 4.2.4 Effects of the sorted QR decomposition and sphere shrinking

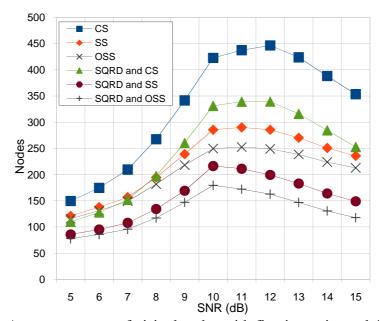

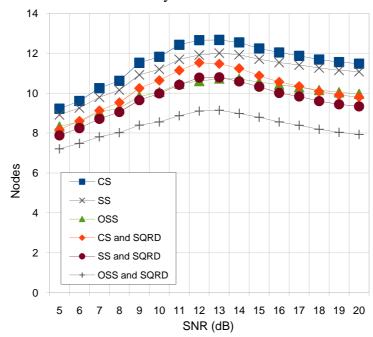

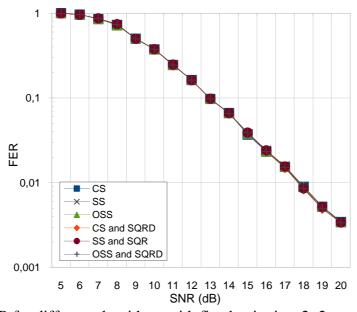

The intent of the SQRD algorithm is to reduce the amount of visited nodes, as is the intent of sphere shrinking (SS). For this reason, in the following sections, the average amount of visited nodes is also plotted. These graphs consider only intermediate nodes the lie inside the sphere. The FER graphs are also plotted to analyse the effects of this alterations, since they may introduce significant increase in the loss, due to the fact that the a-priori information can be negative.

The combination of these techniques was also simulated, i.e. SQRD with SS and with ordered sphere shrinking (OSS). These algorithms are expected to combine their gains in the amount of visited nodes, especially when SQRD is used with OSS, as the increase of the variance in the top layers allows very good branches to be found very quickly, further accelerating the shrinkage of the sphere. The simulations in this section use the original SQRD algorithm (Algorithm 4).

### 4.2.4.1 Results for $4\times4$ antennas

All combinations between SQRD, SS, OSS and CS (constant sphere) were simulated with floating point precision at first, to analyse the effects of these combinations without the errors introduced by the fixed point quantization. The results with  $2\times2$  antennas and also with the 4.8 fixed point format are similar and can be found in the Appendix.

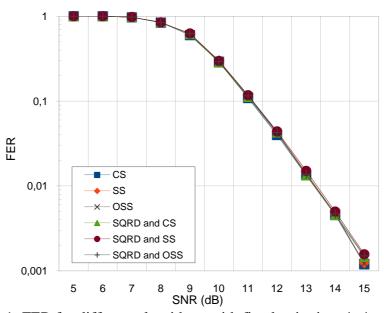

Figure 4.7: FER for different algorithms with floating point in a 4×4 antennas system

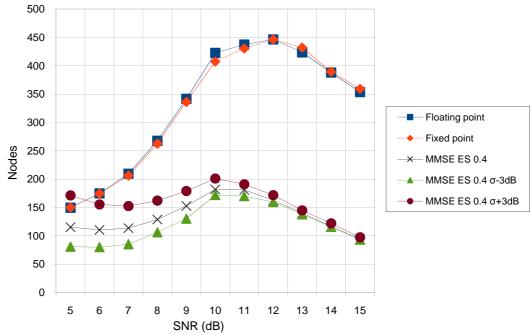

Figure 4.7 shows that there was no significant change in the frame error rate with any combination of the algorithms. This confirms the fact that the possible negative apriori information can be neglected when using sphere shrinking. As for the average amount of visited nodes in Figure 4.8, the results confirm that the usage of sorted QR decomposition have significant impact. Also, sphere shrinking and ordered sphere shrinking can further reduce this number, and this reduction effectively stacks with that of the SQRD.

Figure 4.8: Average amount of visited nodes with floating point and 4×4 antennas

Table 4.8: Parameters for simulations in Figures 4.7 and 4.8

| Parameter          | Value          |

|--------------------|----------------|

| Number of antennas | 4              |

| Frame errors limit | 100            |

| Number format      | Floating point |

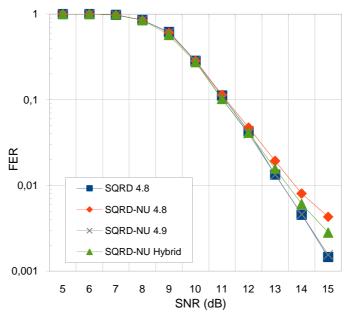

### 4.2.5 Effects of the usage of the norm update method

Algorithm 5, presented in chapter 3, reduces the complexity increase caused by the sorting of the columns in the input matrix by updating the norms contained in the norm vector instead of recalculating them at each iteration. This alteration, however, has side effects in the precision of the output when dealing with fixed point representations.

Figure 4.9: FER for different number formats using the norm update (NU) technique

| Parameter          | Value       |

|--------------------|-------------|

| Number of antennas | 4           |

| Frame errors limit | 100         |

| Number format      | Fixed point |

Table 4.9: Parameters for simulations in Figure 4.9

Figure 4.9 shows that the 4.8 bits format is indeed no longer sufficient to accurately perform the algorithm. On the other hand, it also shows that the addition of one single fractional bit eliminates this issue, reaching practically the same FER of the original SQRD algorithm. The necessity of this extra bit is due to the accumulated error in the norm vector, since the norm update used adds more quantization error at each iteration, thus having great effects especially in the last columns calculated. For this reason, a hybrid architecture was also tested, having 9 fractional bits only in the norm vector and in the norm update path. The results, however, were only intermediary, not close enough to the ones obtained with a full 4.9 hardware. Hence, and also due to the increased complexity of dealing with different representation formats in the same hardware, this option is excluded from further analysis.

This problem is not observed in 2×2 antennas systems, since the norm update hardware is used only once and the quantization error accumulated does not become significant.

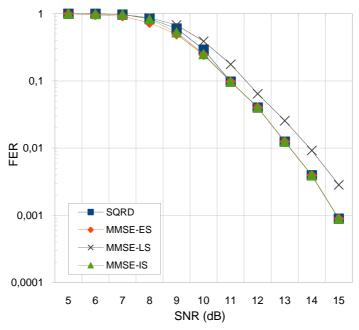

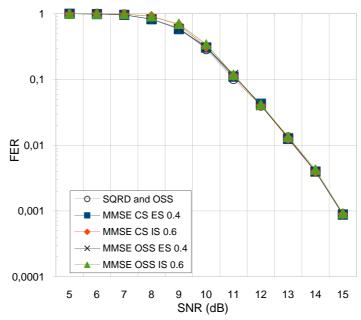

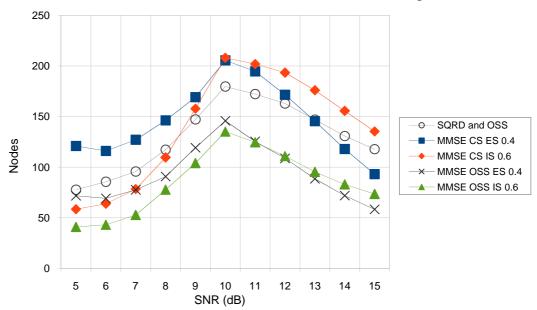

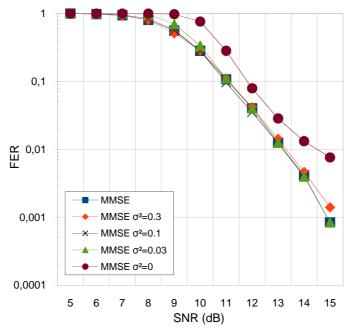

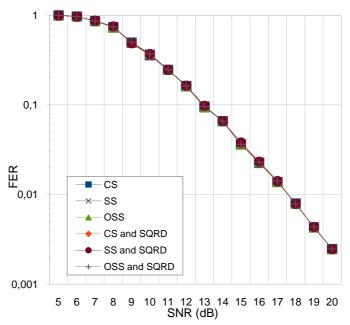

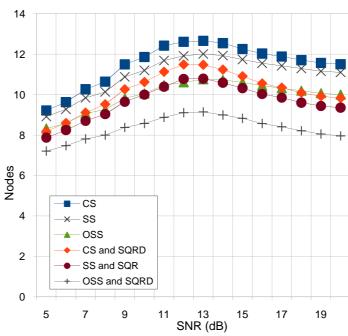

### 4.2.6 Comparison of different bias subtraction methods for MMSE

In order to eliminate (or reduce) the increase in the error rates caused by the usage of MMSE pre-processing, different methods for subtracting the introduced bias in the metrics were presented: namely, late subtraction (LS), early subtraction (ES) and intermediate subtraction (IS). In this section, the FER and average amount of visited nodes with each method is compared. The results obtained with the original SQRD are also plotted for comparison.

Figure 4.10: FER for different bias subtraction techniques

Figure 4.11: Average amount of visited nodes for different bias subtraction techniques

|                    | E     |

|--------------------|-------|

| Parameter          | Value |

| Number of antennas | 4     |

| Frame errors limit | 100   |

Table 4.10: Parameters for simulations in Figures 4.10 and 4.11

Floating point

Figure 4.10 shows that, as expected, the late subtraction method is not suitable for our case, due to the significant increase in the frame error rate. For this reason, it is excluded from further simulations. Also, as can be seen in Figure 4.11, the early subtraction method presents no gain in the amount of visited nodes, when compared to the original SQRD algorithm. On the other hand, the intermediate subtraction method has almost identical FER when compared to the original SQRD and the MMSE-ES algorithms and still achieves an amount of visited nodes which is comparable to that of the MMSE-LS method. All these simulations, however, consider a constant sphere radius of 0.8.

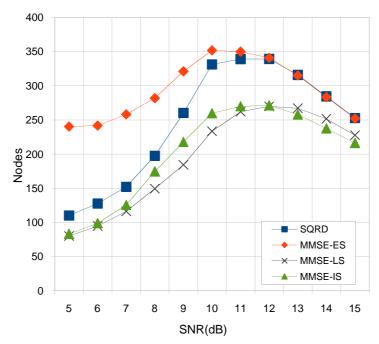

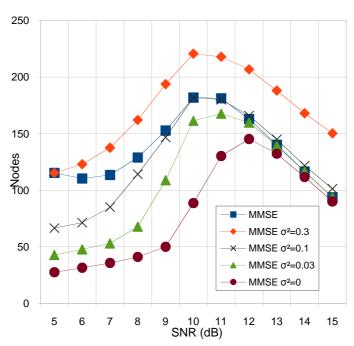

### 4.2.7 Reduced sphere radii for MMSE-SQRD

Number format

Since the distance metrics are modified by the MMSE-SQRD algorithm, new optimal values for the sphere radius, i.e. the smallest value that causes no significant increase in the error rates, are to be found. Also, it is likely that each subtraction method has a different optimal sphere radius.

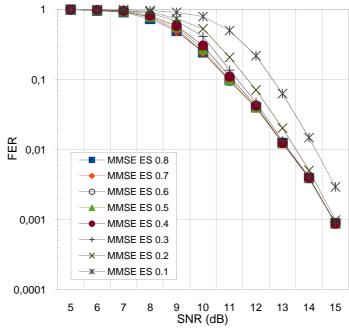

Figure 4.12 shows the FER associated with different constant sphere radii, using the early subtraction method and Figure 4.13 shows the amount of visited nodes associated with each of these radii, considering a constant sphere.

Figure 4.12: FER for different sphere radii in using early bias subtraction

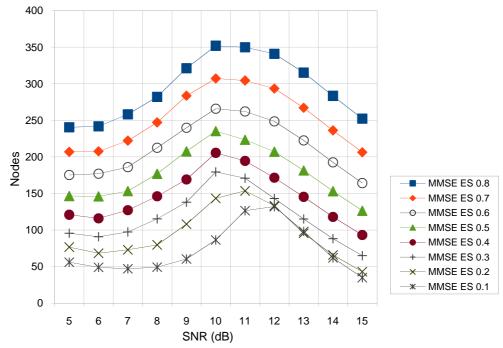

Figure 4.13: Visited nodes for different sphere radii in using early bias subtraction Table 4.11: Parameters for simulations in Figures 4.12 and 4.13

| Parameter               | Value             |  |  |  |  |

|-------------------------|-------------------|--|--|--|--|

| Number of antennas      | 4                 |  |  |  |  |

| Frame errors limit      | 100               |  |  |  |  |

| Number format           | Floating point    |  |  |  |  |

| Bias subtraction method | Early subtraction |  |  |  |  |

Figure 4.12 shows that 0.4 is the smallest radius that ensures no significant FER increase for all simulated SNRs. For higher SNRs, however, much smaller radii are acceptable. In Figure 4.13 it is visible that the reduction obtained in the average amount of visited nodes is very significant when the reduced radii are used.

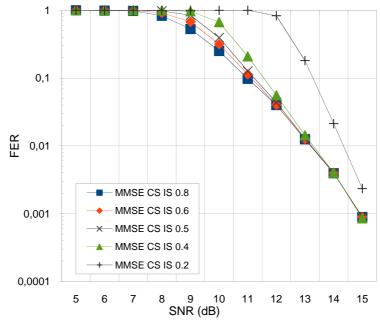

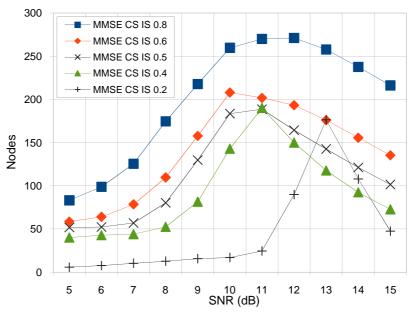

The same analysis was done for the intermediate bias subtraction.

Figure 4.14: FER for different sphere radii in using intermediate bias subtraction

Figure 4.15: Visited nodes for different sphere radii in using intermediate bias subtraction

| Parameter               | Value                    |  |  |  |  |

|-------------------------|--------------------------|--|--|--|--|

| Number of antennas      | 4                        |  |  |  |  |

| Frame errors limit      | 100                      |  |  |  |  |

| Number format           | Floating point           |  |  |  |  |

| Bias subtraction method | Intermediate subtraction |  |  |  |  |

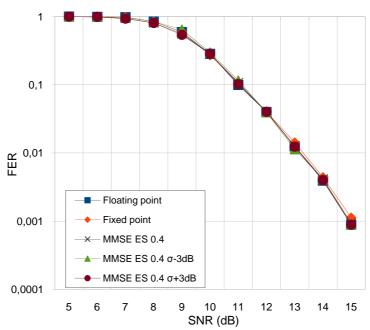

Table 4.12: Parameters for simulations in Figures 4.14 and 4.15