#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTE OF INFORMATICS COMPUTER ENGINEERING

FELIPE AUGUSTO CHIES

Validation and Evaluation of the ASAM -Automatic Architecture Synthesis and Application Mapping - Flow

> Final Report presented in partial fulfillment of the requirements for the degree of Computer Engineer.

> Prof. Dr. Luigi Carro Universidade Federal do Rio Grande do Sul Advisor

Menno Lindwer Intel Corporation Coadvisor Chies, Felipe Augusto

Validation and Evaluation of the ASAM - Automatic Architecture Synthesis and Application Mapping - Flow / Felipe Augusto Chies. – Porto Alegre: COMGRAD ECP UFRGS, 2013.

40 f.: il.

Final Report (Master) – Universidade Federal do Rio Grande do Sul. Computer Engineering, Porto Alegre, BR–Brazil, 2013. Universidade Federal do Rio Grande do Sul Advisor: Luigi Carro; Intel Corporation Coadvisor: Menno Lindwer.

1. Embedded systems. 2. Heterogeneous multi-processor system-on-chip (MPSoC). 3. Customizable ASIPs. 4. Architecture synthesis. 5. Design space exploration. I. Carro, Luigi. II. Lindwer, Menno. III. Título.

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL President: Prof. Carlos Alexandre Netto Vice President: Prof. Rui Vicente Oppermann President for Undergraduate Studies: Prof. Sérgio Roberto Kieling Franco Dean of Institute of Informatics: Prof. Luís da Cunha Lamb Coordinator of ECP: Prof. Marcelo Goetz Chief Librarian: Beatriz Regina Bastos Haro

## CONTENTS

| LIST OF ABBREVIATIONS AND ACRONYMS                                                                                                                                                                                                                                                                                                                  | 5                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                     | 7                                            |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                      | 8                                            |

| ABSTRACT                                                                                                                                                                                                                                                                                                                                            | 9                                            |

| RESUMO                                                                                                                                                                                                                                                                                                                                              | 10                                           |

| 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                      | 11                                           |

| 2 RELATED WORKS                                                                                                                                                                                                                                                                                                                                     | 12                                           |

| 3.1       Overview                                                                                                                                                                                                                                                                                                                                  | 13<br>13<br>14<br>15<br>15<br>17<br>17       |

| 4.1       Background Concepts         4.1.1       Architecture Template         4.1.2       Application Model         4.1.3       Architecture Construction         4.1.4       Configurable Library of Components         4.1       Inter Issue Slot Communication DSE         4.4       Deriving the System Level Communication from a Task-Graph | 19<br>19<br>20<br>20<br>20<br>20<br>21<br>22 |

| 5 EXPERIMENTAL RESULTS                                                                                                                                                                                                                                                                                                                              | 24                                           |

| 6 CONCLUSION AND PERSPECTIVES                                                                                                                                                                                                                                                                                                                       | 28                                           |

| REFERENCES                                                                                                                                                                                                                                                                                                                                          | 29                                           |

| APPENDIX A EXAMPLE OF USER CONSTRAINS (XML FILE)                                                                                                                                                                                                                                                                                                    | 31                                           |

| APPENDIX B EXAMPLE OF PLATFORM DESCRIPTION (XML FILE) .                                                                                                                                                                                                                                                                                             | 32                                           |

| APPENDIX C | EXAMPLE OF TASK AND SYSTEM ANALYSIS (XML FILE) | 33 |

|------------|------------------------------------------------|----|

| APPENDIX D | EXAMPLE OF DEFAULT COMPONENTS                  | 35 |

| APPENDIX E | HOST CODE EXAMPLE                              | 37 |

| APPENDIX F | ASIP CODE EXAMPLE                              | 38 |

| APPENDIX G | PROJECT DESCRIPTION <tg1></tg1>                | 40 |

# LIST OF ABBREVIATIONS AND ACRONYMS

| API    | Application Programmers Interface                                                                                                                                                                                                                                                          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARU    | Arithmetic Unit                                                                                                                                                                                                                                                                            |

| ASAM   | Automatic Architecture Synthesis and Application Mapping. EU-funded<br>project with the high-level goal of inferring suitable architectures and map<br>software onto these, given unoptimized target-unaware input applications.                                                           |

| ASIP   | Application-specific Instruction-set Processor                                                                                                                                                                                                                                             |

| Bus    | A TDM interconnect with one channel.                                                                                                                                                                                                                                                       |

| DSE    | Design space exploration                                                                                                                                                                                                                                                                   |

| EDA    | Electronic Design Automation                                                                                                                                                                                                                                                               |

| FIFO   | First-In First-Out. A queue.                                                                                                                                                                                                                                                               |

| FU     | Function Unit                                                                                                                                                                                                                                                                              |

| HiveCC | Intel-VIED's SDK for Intel-VIED-specific ASIPs.                                                                                                                                                                                                                                            |

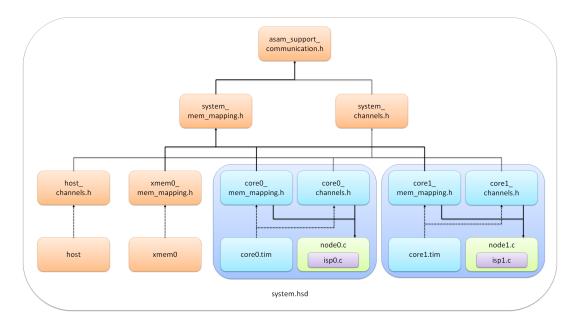

| HSD    | Hive System Description: language for describing multi-core systems                                                                                                                                                                                                                        |

| IDE    | Integrated Development Environment                                                                                                                                                                                                                                                         |

| ILP    | Instruction-Level Parallelism: refers to the kind of instruction processing<br>where a single instruction contains multiple operations. Also refers to the<br>measure of the average number of operations executed in parallel on a<br>VLIW machine, throughout (part of) and application. |

| IPC    | Inter-process communication                                                                                                                                                                                                                                                                |

| IS     | Issue Slot                                                                                                                                                                                                                                                                                 |

| MAC    | Multipy-Accumulate: the combined operation of multiplying and adding, also refers to the multiply-accumulate function unit within a processor.                                                                                                                                             |

| MCG    | Mobile and Communications Group, within Intel.                                                                                                                                                                                                                                             |

| MIMD   | Multiple Instruction Multiple Data: referring to multi-processors which<br>can execute multiple independent parallel operation streams on multiple<br>independent data streams                                                                                                             |

| MoC    | Model of computation                                                                                                                                                                                                                                                                       |

| OLP    | Operation-Level Parallelism: single operations performing multiple tasks<br>simultaneously which, on a RISC processor, would have taken multiple<br>operations                                                                                                                             |

| PC         | Program Counter                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF         | Register File                                                                                                                                                                                                                                                                                                                                                                                              |

| RSN        | Result Select Network: the HiveLogic IP module instantiated within the processor's datapath to provide a sparsely connected communications facility running from Issue slot outputs to Register file inputs                                                                                                                                                                                                |

| SDK        | Software development kit. Set of tools to support developing software.                                                                                                                                                                                                                                                                                                                                     |

| SIMD       | Single-Instruction Multiple-Data.                                                                                                                                                                                                                                                                                                                                                                          |

| SoC        | System-on-Chip                                                                                                                                                                                                                                                                                                                                                                                             |

| SR         | Status Register                                                                                                                                                                                                                                                                                                                                                                                            |

| SW         | Software                                                                                                                                                                                                                                                                                                                                                                                                   |

| System     | Top-level collection of hardware components in HSD, often roughly cor-<br>responding to the functionality of an SoC. This specifically does not refer<br>to application-level systems consisting of constellations of different pro-<br>cessing kernels, such as often associated with MatLab descriptions and<br>Kahn process networks, but rather the hardware on which such systems<br>could be mapped. |

| Sub-system | Collection of hardware components in HSD, corresponding to some in-<br>termediary hierarchy level                                                                                                                                                                                                                                                                                                          |

| TIM        | Intel-VIED's proprietary processor description language.                                                                                                                                                                                                                                                                                                                                                   |

| VIED       | Video and Imaging Engineering Department within Intel-MCG.                                                                                                                                                                                                                                                                                                                                                 |

| VLIW       | Very Long Instruction Word: generally used to refer to processors which can execute multiple independent operations in parallel.                                                                                                                                                                                                                                                                           |

| VLSI       | Very Large Scale Integration                                                                                                                                                                                                                                                                                                                                                                               |

# **LIST OF FIGURES**

| Figure 3.1: | Global objective of the ASAM Project.                               | 13 |

|-------------|---------------------------------------------------------------------|----|

| Figure 3.2: | Work Flow's extension proposed by the ASAM Project.                 | 14 |

| Figure 3.3: | Meta-flow used to evaluate and integrate the ASAM Flow              | 15 |

| Figure 3.4: | KPN generated analyzing the Hearing Aid use case.                   | 16 |

| Figure 3.5: | The ASAM Flow.                                                      | 17 |

| Figure 4.1: | The Processor Architecture Template (PAT).                          | 19 |

| Figure 4.2: | Example of clusters of issues slots interconnected.                 | 21 |

| Figure 4.3: | Deriving the system communication from a task-graph                 | 22 |

| Figure 4.4: | Template of the API proposed for a User-Oriented Multi-ASIP System. | 23 |

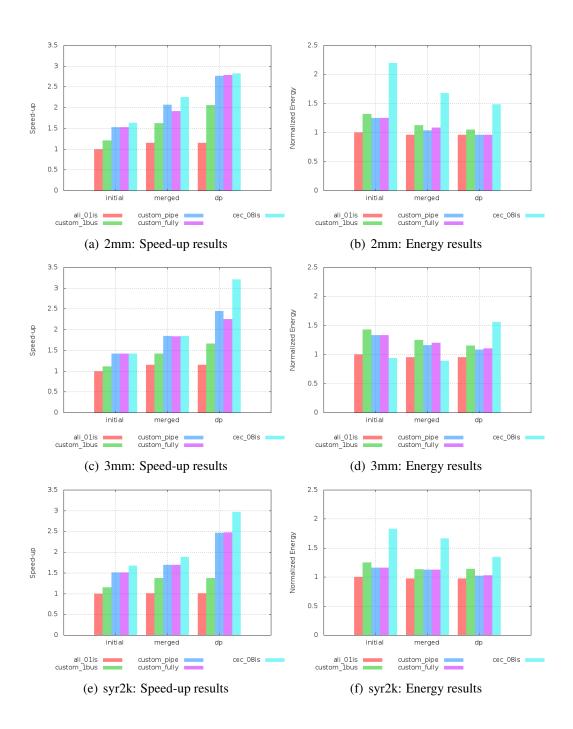

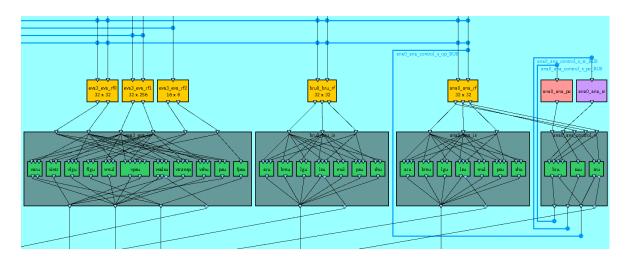

| Figure 5.1: | Code transformation results for 2mm, 3mm and syr2k                  | 26 |

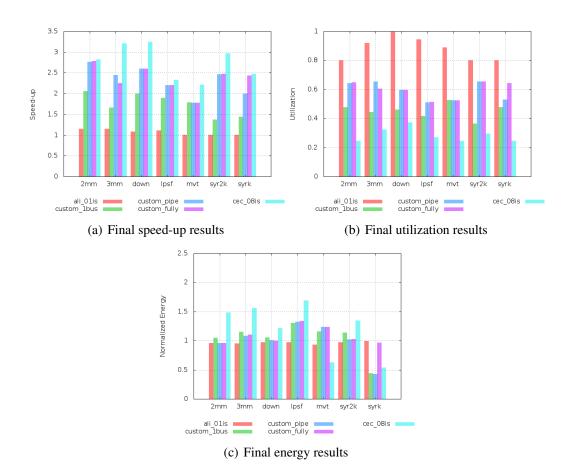

| Figure 5.2: | Final results.                                                      | 27 |

# LIST OF TABLES

| Table 5.1: | Benchmarks. |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 2 | 24 |

|------------|-------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|----|

|------------|-------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|----|

## ABSTRACT

High-quality MPSoCs can only be constructed exploiting more adequate concepts of computation, storage and communication, as well as usage of efficient design methods and electronic design automation (EDA) tools. This document discusses some subsystems of the Automatic Architecture Synthesis and Application Mapping (ASAM) flow. In addition, we propose a component based design for multi-ASIP platform and we will introduce and compare several strategies to connect different issue slots. Experimental results show that our approach give the best trade-off regarding application execution time and energy consumption between the different architectures analyzed.

**Keywords:** Embedded systems, heterogeneous multi-processor system-on-chip (MP-SoC), customizable ASIPs, architecture synthesis, design space exploration.

# Validação e Avaliaçao de uma ferramenta automática de síntese de arquitetura e mapeamento de aplicação (ASAM flow).

## RESUMO

A fim de construir MPSoCs de alta qualidade é necessário investigar e explorar conceitos mais satisfatórios de computação, armazenamento e comunicação, além de utilizar eficientes métodos de design e softwares de projeto de circuitos integrados. Este documento discute alguns subsistemas de uma ferramenta automática de síntese de arquitetura e mapeamento de aplicação (ASAM flow). Além disso, será proposta uma plataforma baseada em componentes para o design de sistemas com múltiplos ASIPs e algumas estratégias para conectar diferentes issue slots serão introduzidas e comparadas. Os resultados experimentais mostram que o método introduzido neste documento resulta nos melhores trade-offs com relação ao tempo de execução e ao consumo da aplicação entre as diferentes arquiteturas analisadas.

**Palavras-chave:** sistemas embarcados, sistema-em-um-chip com multi-processadores heterogêneos (MPSoC), ASIPs customizáveis, síntese de arquitetura, exploração espacial de designs.

### 1 INTRODUCTION

Modern embedded systems design technology is relevant for different fields of application (multimedia, telecom, medical, military, etc.). These applications require ultra high performance, but also flexibility and low Non Recurring Engineering (NRE) costs in order to be adjustable to shifts in the market.

The progress in semiconductor technologies has allowed Multiprocessor System on Chip (MPSoC) to reach the high performance needed by this kind of application. However, high-quality MPSoCs can only be constructed exploiting more adequate concepts of computation, storage and communication, as well as usage of efficient design methods and electronic design automation (EDA) tools.

The high performance is often achieved through highly specialized processors. Application specific instruction-set processors (ASIPs) are programmable, deliver high performance and they are energy efficient. Recent system-on-chip solutions ((Movidius, 2013), (Intel, 2013)) contain such components. We can improve the efficiency of the system by exploring the intrinsic parallelism of an application for instance (by effectively exploiting the target VLIW ASIP).

The focus of this document is to evaluate and validate the ASAM flow, in terms of e.g. lead time, amount of manual work, and quality of results. During the process of validation, some issues were found in the flow and the solutions implemented will be presented. In addition, a component based design for multi-ASIP platform was developed and will be introduced in this document.

This document extends the previous work that can be found in the Appendix G. This Appendix will be referred many times in this document as the project description. All the research and results presented here are related to a European project ASAM (Automatic Architecture Synthesis and Application Mapping) being currently executed in the framework of the ARTEMIS program. By the time that this document was written the project was still in progress. Thus, things could have changed and some issues introduced here could have been fixed.

This document is organized as follows. The next section introduces some related works. Section 3 discusses the ASAM flow, the integration challenges and issues found and the solutions proposed. Section 4 focuses in the component based design proposed and its relevance when generating multi-ASIP systems. Section 5 discusses the experimental results and Section 6 concludes this document and lists some perspectives.

## 2 RELATED WORKS

Many problems related to automatic ASIP design represent hot research topics. Retargetable compilers, such as Coware Processor Designer, Expression, Mescal, ASIP-Meister, Tensilica's compiler or HiveCC, are used to schedule and map a high-level application specification onto the optimized configurable ASIP platform. However, the major general challenge is the hardware and software co-design tuned for a specific application.

Many published research results (JOZWIAK, 2001), (JOZWIAK; ONG, 2008), (DENS-MORE; PASSERONE, 2006) and system design frameworks, e.g. Metropolis (Metropolis, 2013), Daedalus etc., target heterogeneous MPSoC design. Some achievements in design automation have demonstrated that it is possible to automatically generate application-specific architectures that compete with handmade solutions. Examples of these successes are High-Level Synthesis (SCHREIBER; ADITYA; MAHLKE; KATHAIL; RAU; CRONQUIST; SIVARAMAN, 2002) for ASIC design and automatic Instruction Set Extension (MURRAY; FRANKE, 2012) for ASIP configuration.

Several industrial tool-flows, e.g. (FlexASP project, 2013) and (KATHAIL; ADITYA; SCHREIBER; RAU; CRONQUIST; SIVARAMAN, 2002), are available to specify, simulate, and/or synthesize VLIW architectures. (KATHAIL; ADITYA; SCHREIBER; RAU; CRONQUIST; SIVARAMAN, 2002) can perform an automatic exploration of these architectures, but it's focused on VLIW processors with a centralized register file. Terechko et al. (TERECHKO; THENAFF; GARG; EIJNDHOVEN; CORPORAAL, 2003) defined a taxonomy for different variations of clustered VLIW processor architectures. However, until now, clustered processor architecture exploration has been performed by hand.

Beside ASAM, no flows currently exist which automate both (multi-core) system design and design of the multiple ASIPs within those systems. The existing multi-core DSE flows (such as Metropolis and Daedalus) assume a given library of processors. Moreover, in existing flows, the types of processors are not as heterogeneous as those built by ASAM. The existing flows merely differentiate between a multitude of standard RISC cores and standard DSPs. The task of specifically having to restructure the code partitions, in order to target the differences between these cores is typically also not handled by other flows.

## 3 PROPOSED CHANGES IN THE ASAM FLOW

#### 3.1 Overview

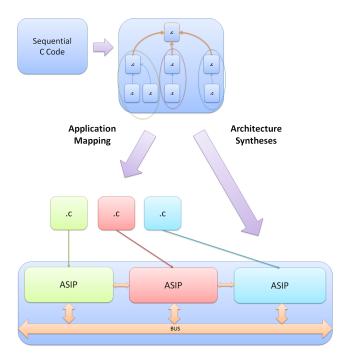

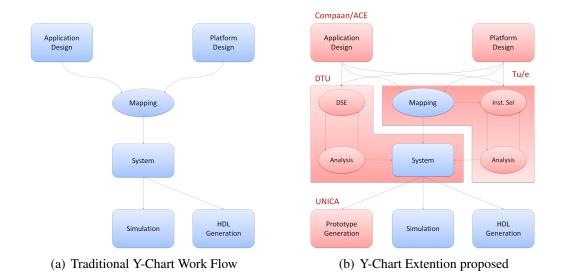

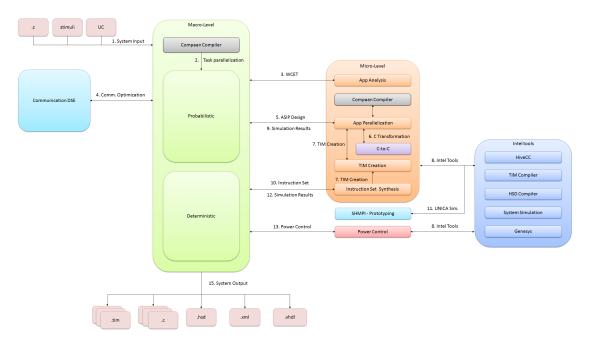

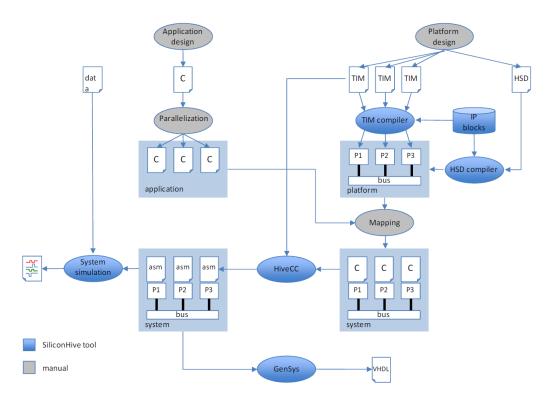

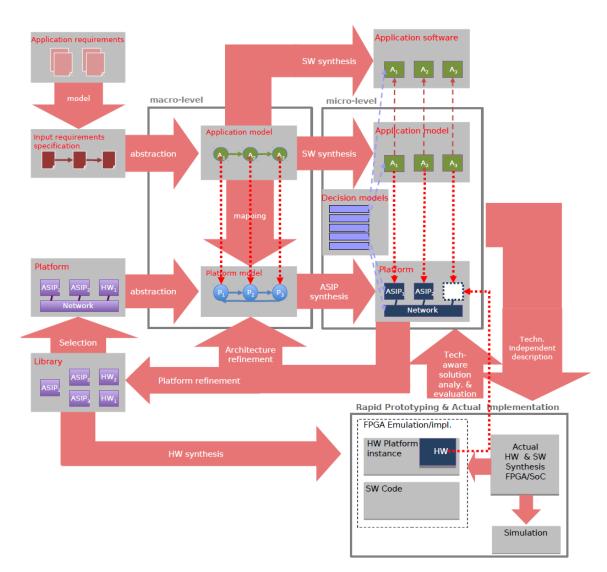

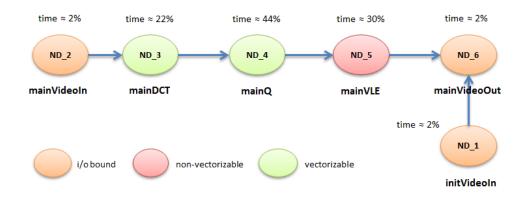

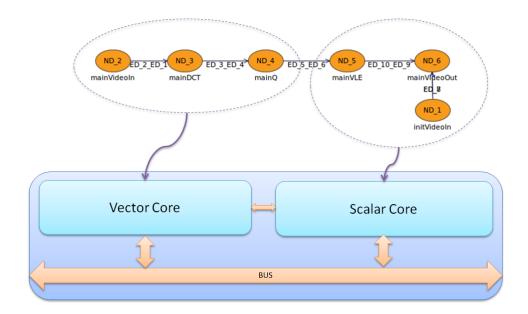

The main objective of the ASAM project is to develop a design methodology and a design flow that provides efficient application mapping and automatic architecture synthesis for multi-ASIP systems. Figure 3.1 gives an overview of the project's global objective. Briefly, given an input application (sequential C Code), the flow should propose a suitable target platform. In addition, the application's tasks should be partitioned and optimizations in communication, memory management, loop transformations and vectorization should be applied. This flow will be implemented by extending the traditional Y-Chart Work Flow (Figure 3.2). A more detailed explanation about the project can be found in this project description (Appendix G, Section 2) and in the literature ((JOZWIAK; LINDWER; CORVINO; MELONI; MICCONI; MADSEN; DIKEN; GAN-GADHARAN; JORDANS; POMATA; POP; TUVERI; RAFFO, 2012), (JOZWIAK; LINDWER, 2011), (JOZWIAK; LINDWER, 2010), (ASAM, 2013), (JOZWIAK; LINDWER; MAD-SEN, 2011)).

Figure 3.1: Global objective of the ASAM Project.

Figure 3.2: Work Flow's extension proposed by the ASAM Project.

#### **3.2 Integration Challenges**

The initial goal of this thesis project is to evaluate the ASAM Flow. However, in order to do it, the tools should be working properly and all the subsystems of the flow should be connected or, at least, they should have a standard of communication already defined in order to simulate and generate all the inputs/outputs correctly. Unfortunately, that was not the case. When this work started, most part of the tools were not delivered and the partners of the project had never tried to communicate the subsystems. In addition, the use cases chosen were not ported to be used on the flow and a lot of extra work was required.

One of the most important challenges of this kind of project is that its success heavily depends on the compatibility and coherent collaboration of all models and tools. Due to its complexity, the scope of this project covers many different research fields. The synthesis and prototyping flow involves several different kinds of models, many various tools operating on them and complex collaboration among models and tools (JOZWIAK; LINDWER; MADSEN, 2011). Keeping all this information in mind, it becomes evident that a significant effort should be made in order to integrate all the tools that compose the flow.

Another challenge usually faced in projects like this is the interaction between the different partners. Taking the ASAM project as an example, we have eight different partners (four universities and four companies) and most of them are spread around the world. This makes project meetings something difficult to happen, which can lead to a small interaction between the partners. Good project managers and leaders become very important in this case to ensure that the partners keep exchanging information and to make sure that the subsystems that need to integrate are communicating well. Wrong assumptions about what one subsystem can supply to the other can have seriously consequences on the whole project, sometimes even leading to the failure or restructuration of a whole subsystem.

Different priorities, ways of working and objectives are other points to be faced during the progress of the project, mainly between academia and companies. Universities partners for example are normally focused only in the research/novelty part of the problems. It can let the "non-research" part of the work (default libraries, use cases, global integration, templates, general documentation, interfaces, translators, among others) forgotten without implementation, creating therefore gaps in the communication and avoiding the integration of the whole system. In general, these tasks are not implemented because they are seemed as a "waste of valuable time". However, knowing that these implementations could allow a whole automated flow to work, it can only be seen as beneficial in a long-term project. On the other hand, universities tend to be more flexible than companies, being more adaptable to little changes in the initial specification of the project.

Lastly, it is important to highlight that the integration process should start as soon as possible, even though the tools are not finished. Only by integrating we can find out what is missing in the flow and what was misunderstood between the different partners. A lot of time can be saved by doing it in earlier phases of the project.

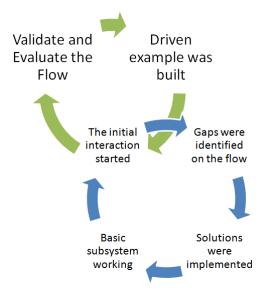

#### 3.3 Initial Integration and Evaluation

As mentioned before, some challenges were faced during the integration. In order to evaluate and integrate the flow, a work strategy was created and followed during the execution of this project. Basically, use cases and some extra examples were used with the intention of stressing the flow to find out gaps and communication problems. This strategy is illustrated on Figure 3.3.

Figure 3.3: Meta-flow used to evaluate and integrate the ASAM Flow.

#### **3.3.1** The Model of Computation Issue

The first task performed during this thesis project was to map a consumer-oriented application (in this case a Motion JPEG encoder) into a multi-ASIP system created specially and optimized for this application. Most of steps required to produce and map this system were performed by hand in order to generate a new reference to compare against the results generated automatically by the flow. This example is different from the initial use cases because we kept a track for each transformation applied on the code and on the system. Thus, we are able to analyze the result of each tool separately and not only the result of whole flow. An exhaustive description of these steps can be found on the project description (Appendix G, Section 4).

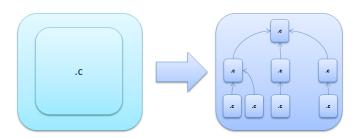

With the MJPEG example created and ready to be analyzed, we tried to run the automated ASAM flow with this example as input. By doing it, we noticed that the initial C Code of the input application needs to be changed. The reason of this requirement is that the flow needs an initial Model of Computation (MoC) to start the Design Space Exploration (DSE). The MoC chosen by the project is a Kahn Process Network (KPN). Due to its expressiveness, the KPN is hard to be inferred and it's difficult to generate an efficient implementation without some pragmas/hints embedded on the C Code. The tool used to generate the MoC is the Compaan Compiler and an example illustrating the modifications needed by the tool can be found on Appendix G, Section 4.1.2.

The ASAM project has three main use cases: an Electrocardiogram algorithm (ECG); a Digital Hearing Aid System; a MPEG4 Encoder Algorithm (further information on Appendix G, Section 3.1). These use cases were supplied by the partners of the project and they are coded in C. However, they were not compatible with the Compaan Compiler, generating thereby the first issue to be faced in order to evaluate the flow.

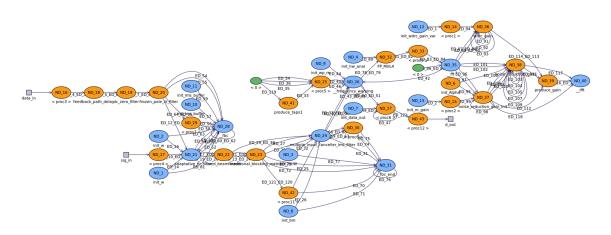

The Hearing Aid application was the first target use case to be ported. The initial code was relative small (about 750 lines of code), but much more effort than expected was required to adapt the application. Almost five working days were spent porting this use case and the final code was more than two times bigger than the original code (2000 lines of code). The final KNP generated by the tool can be found on Figure 3.4.

Figure 3.4: KPN generated analyzing the Hearing Aid use case.

A similar matter was observed with the MJPEG encoder. A simple coarse-grained KNP (only six nodes were generated from the six main functions of the application - Appendix G, Section 4.1.2) can be easily generated without many modifications on the code. However, the DSE of the flow needs a more fine-grained Model of Computation (almost a node for each loop on the code) in order to perform important analysis of the code and to infer significant code transformations. For the MJPEG encoder, a hierarchical and fine-grained KPN was generated after almost four working days. It is important to notice that these are quite small applications. More complex applications as the MPEG4 encoder would need much longer time in order to analyze the code and after to port it. For this reason, it was decided to use the MJPEG example as an alternative of the MPEG4.

In the opinion of the author of this document, the trade-off brought before concerning modifications in the input application is one of most important open discussion of this project. It needs to be carefully studied to decide how much effort should be allocated to change the code in order to generate a certain level of granularity in the Model of Computation. This granularity will have a significant impact on the quality of the final result.

#### 3.3.2 A Unified Communication Method

With the use cases ported and ready to run on the ASAM Flow a new evaluation attempt started. This time, many problems concerning the communication between different subsystems prevented the flow to work. In order to repair it, a large interaction with the different partners of the project started. After numerous meetings, a standard of communication was defined to be used for all the subsystems. It was decided to use three different XML files. The first one should specify the user constrains, the second one should be used to describe the communication between the different processors and memories on the systems. The third one is the most important and it will be used by almost all tools. It describes all the analysis performed in the application, simulations results regarding power, area and performance and the decisions taken concerning the mapping and the system generation. Examples of these three files can be found on Appendix A, B and C respectively. One important aspect of these files is that they keep track of the current status of the flow. Making use of this information, a designer controlling the flow could change some parameters of the tools helping the flow to converge to a more optimized solution.

In addition, as the different partners/tools started to interact more, concerns in the initial description of the flow were found and some modifications were needed. Figure 3.5 illustrates the updated version of the ASAM Flow. In comparison with the initial flow (introduced on the project description) we can have a much clearer idea about the different tools inside the flow and how they interact.

Figure 3.5: The ASAM Flow.

#### 3.3.3 Selecting and Porting Extra Benchmarks

With the flow redefined and with the communication problem solved, we could start a new iteration of the working meta-flow using the Hearing Aid and the MJPEG application. As it's generally expected, this first try of the flow failed and more issues appeared. Even though these use cases are not so complex, they have some complexity that can be explored in different ways by the DSE and it was quite hard to identify which part of the flow had some problem or did not perform well. Hence, some basic examples were needed in order to easily validate individual tools.

A solution proposed to this matter was the Polybench set of benchmarks (Polybench, 2013). In total, 25 benchmarks were ported to be used on the ASAM flow. These benchmarks were chosen because they are very small, they contain static control parts (that help the generation of the MoC, making it easy to port to the ASAM Flow) and they are largely used in Academia (providing us many results to compare against). Two more benchmarks were ported: a Low Pass Spatial Filter (LPSF) and a Down Sampling Filter.

By stressing these benchmarks on the flow problems were found and places with some gaps were easily identified. The solutions proposed can be found in the following section.

## 4 COMPONENT BASED DESIGN FOR MULTI-ASIP PLAT-FORM

#### 4.1 Background Concepts

#### 4.1.1 Architecture Template

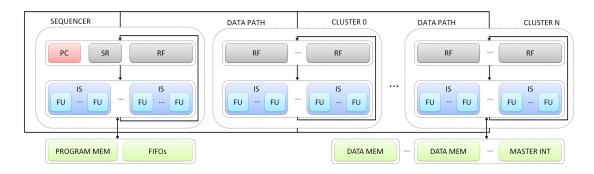

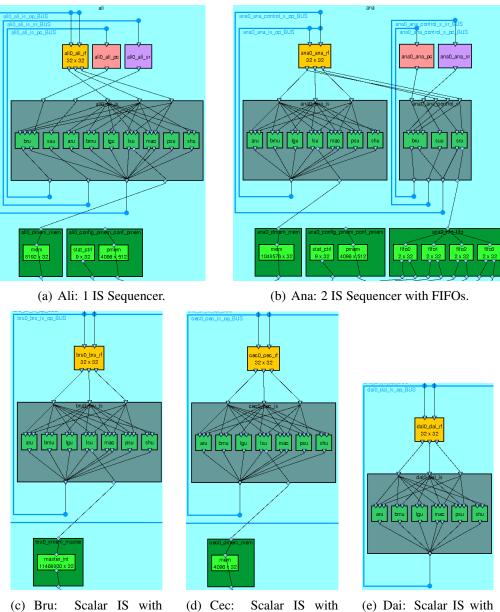

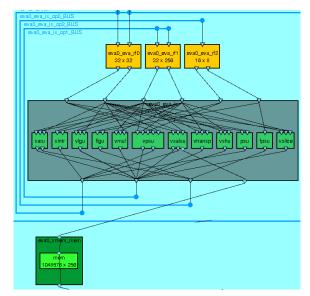

The project targets clustered VLIW ASIP machines capable of executing parallel software with a single thread of control. Figure 4.1 shows a simplified view of the architecture template.

The VLIW datapath is controlled by a sequencer that executes the program stored in the local program memory. The datapath contain Functional Units (FUs) grouped into Issue Slots (IS) that are connected via a programmable interconnect network to Register Files (RF). The sequencer is a special IS containing branch instructions, a program memory, a status register (SR), a program counter (PC) and some registers. FIFOs can be added in order to manage external communication. They can be connected to any IS, but they are usually connected to the sequencer.

FUs within the same IS share hardware, in consequence they cannot be used at the same time. In addition, FU implements operations that can require pipelining. Thus, each IS can start at most one new operation per cycle.

Almost every component of within the processor architecture template (PAT) is freely scalable. It is possible to have as many RFs, ISs, FUs, memories and master interfaces as wanted. All these components can work both with scalar and vector elements of different sizes. Therefore, both single-instruction multiple-data (SIMD) and multiple-instruction multiple-data (MIMD) can be performed. The interconnection between all components is also customizable.

Figure 4.1: The Processor Architecture Template (PAT).

#### 4.1.2 Application Model

In the Micro-Level DSE of the ASAM flow, the application is represented by a taskgraph model. This task-graph is an Array Oriented Language (Array-OL) (GLITIA; DU-MOND; BOULET, 2010). This model contains two abstraction levels: a higher level that specifies inter-task dependencies and a lower level that specifies intra-task (data-) dependencies.

#### 4.1.3 Architecture Construction

The initial prototype of the ASIP's architecture is derived from an exploration of the application model which intent to find the best combination of several possible loop-transformations (e.g. loop fusion, tiling, and vectorization). In this way, we adapt the hardware and the software architectures to the requirements of the application with satisfactory results.

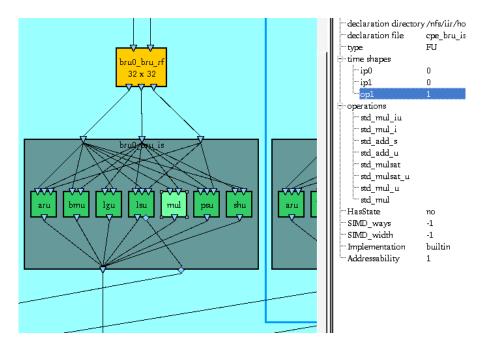

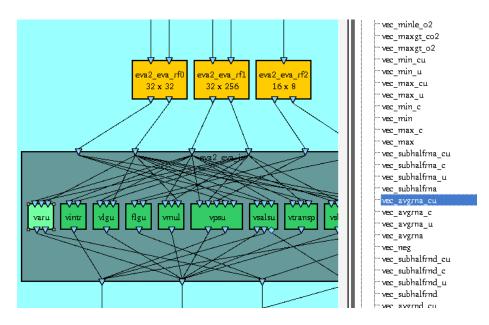

#### 4.2 Configurable Library of Components

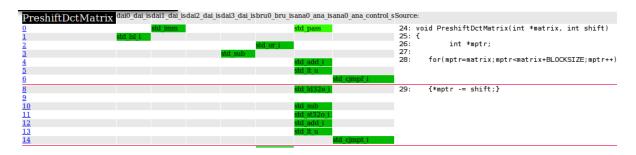

As explained before, the architecture construction is obtained from the application model. However, we can only infer the number and the kind of issue slots and memories that we need from the application model and the real architecture was not being generated. To fill this gap, a configurable library of components was created to work together with the DSE. This allowed to automatically generate the ASIP architecture. These components were developed in the TIM language VIED's proprietary processor description language.

Appendix D contains some examples of the components created to be part of a default library. They are configurable and the element size can be easily changed. By connecting these components together the ASIP can finally be created and simulated.

As the instruction-set architecture exploration is based on a shrinking method, these components have a default and extensive set of operations. This allows the exploration to investigate many different designs and to choose only the operations more relevant to the application being analyzed.

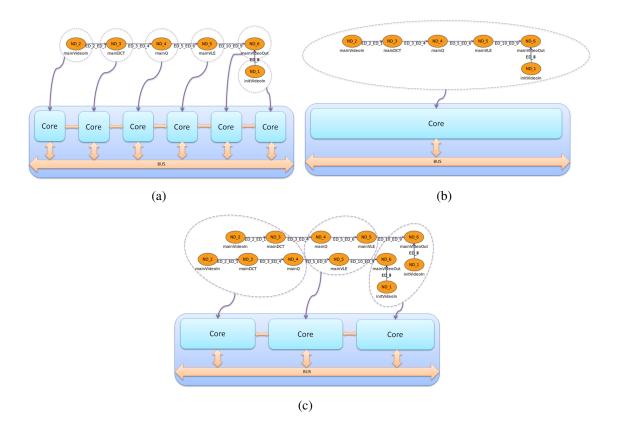

#### **4.3 Inter Issue Slot Communication DSE**

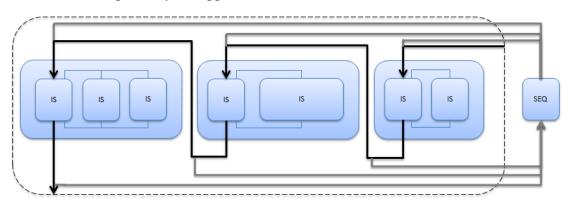

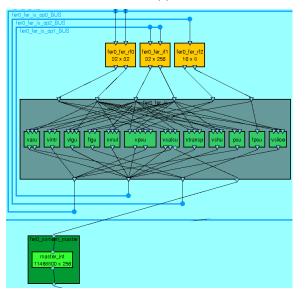

Another concern found inside the flow was the way that the different issue slots were being connected. Even though we could generate models of ASIPs and simulate their behavior in software, the implementation was not possible. It was happening because all issue slots were connected through a fully connected network. This is not feasible in practice due to the complexity of the routing process, the final area and power consumption of the circuit. In this section we will describe a solution proposed to reduce the size and the complexity of the interconnections between different issue slots.

The construction of the network starts from the hierarchical Array-OL model. Each task in the Array-OL description becomes a cluster in our model. The nested level of fusion identifies nested levels of clusters. It is important to observe that due to locality reasons, issue slots inside the same cluster tend to need a higher level of communication than issue slots of different clusters.

From the analysis of the data-flow graph, the maximum number of operations that can be executed in parallel is computed. This number defines the number of issue slots to be allocated and distributed inside the different clusters. Then, issue slots and memories are evenly distributed in the clusters.

The issue slots within a cluster are fully connected and the clusters are connected to each other in a pipelined manner. Inside a cluster only one issue slot is chosen to take care of the external communication as illustrated in Figure 4.2. The input memory is connected to the sequencer and the output memory is connected to the latest issue slots on the pipeline chain. As the sequencer is connected to the input and to the default memory (where the stack is placed) the communication with this issue slot is usually higher. For this reason, we decided to connect all clusters in the highest hierarchical level directly to the sequencer. In this way, the maximum distance between these clusters become equal to two. This reduces the overall connectivity of the VLIW, although it maintains minimum connections as required by the application.

Figure 4.2: Example of clusters of issues slots interconnected.

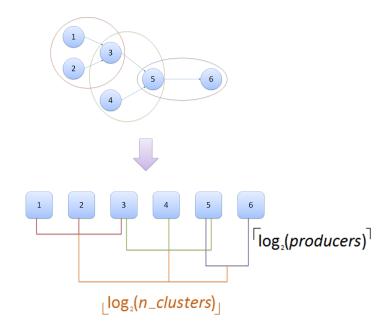

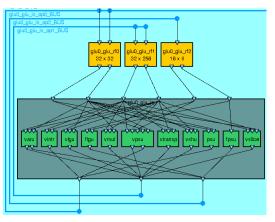

#### 4.4 Deriving the System Level Communication from a Task-Graph

The ASAM Project has already a tool to design and explore the system communication. However, during the period of this project, the Communication DSE was not integrated with the ASAM flow. A fast solution was needed in order to generate and simulate complete systems, allowing the partners to evaluate design choices.

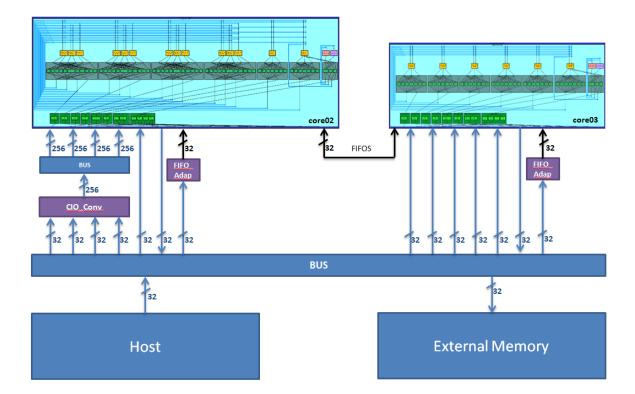

We decided then to create a hierarchical bus-based network derived from a task-graph. Figure 4.3 shows this procedure. The task-graph is generated by the Macro-level system of the ASAM Flow. Each node of this graph is a cluster of different tasks that will be mapped on the same ASIP and each edge represents a channel of communication. In order to infer the connections we will generate new clusters. The clusters' generation works as follow. First, we select a consumer from the graph and a new cluster is created. Then, all nodes that are producers for this consumer will be included inside this cluster. This procedure will be repeated until each consumer of the graph has its own cluster. The next step is to generate a multi-layer bus for each cluster connecting all nodes inside the cluster. The number of layers in the bus is equal to  $log_2(number of edges inside the application, it is important to create a communication path between all ASIPs in the system. This is ensured by creating a last multi-layer bus that connects all clusters. The number of layers in this bus is equal to <math>log_2(number of cluster)$ .

The model of communication proposed here can still be used in the future of the ASAM project. As this model showed to be efficient in the experiments performed, it can be used as an initial approach to generate first estimations.

Figure 4.3: Deriving the system communication from a task-graph.

#### 4.5 Generic API Definition for a User-Oriented Multi-ASIP System

The last gap found in the ASAM flow, but crucial for it success was that lack of some API to manage the system communication. As we aim to develop multi-ASIP systems, we need a system structure which ensures the synchronization between diverse tasks mapped on different ASIPs. In addition, it is important to have some kind of API to help to load and store data from the host processor to the system.

Based on a shared memory approach and making use of FIFOs to shake hands between the different processes, an API was developed to manage the system communication. The elements that compose this API are presented in the Figure 4.4. This API is generic, working both with scalar and vector elements. In addition, it was implemented in a way that more complex modes of operation like double-buffering are allowed.

Examples of the use of this API can be found in the Appendix E and F. The Appendix E represents the orange host square in the Figure 4.4 and it shows a host code interacting with an ASIP. It makes use of the functions *hrt\_asam\_indexed\_store\_signed\_vector* and *hrt\_asam\_indexed\_load\_signed\_vector* to load and store vectors in the local memory of the ASIP. To store scalar elements, the function *hrt\_asam\_mem\_store\_nooffset* is used.

The Appendix F is the green squares in the Figure 4.4. This is a default template that can be generated automatically from the analysis of the application. It is responsible for all the system communication.

Figure 4.4: Template of the API proposed for a User-Oriented Multi-ASIP System.

## **5 EXPERIMENTAL RESULTS**

To validate the methods briefly introduced before and test some subsystems of the ASAM flow we have selected seven of the benchmarks presented on Section 3.3.3. The applications chosen are listed in Table 5.

The only parts of the flow that we were able to test were the application analysis and the application parallelization of the Micro-Level in collaboration with Intel tools. Some steps were accomplished manually in order to supply the correct input information to these tools. However, these tools were sufficient to validate all the concepts presented before and we were capable to automatically: analyze the code, infer code transformations and generate customized systems for the application.

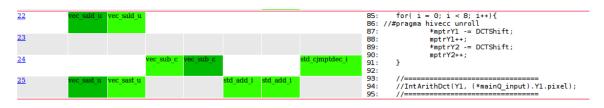

Each exploration of the application parallelization tool infers an ASIP and applies loop transformations on the input application, generating a Pareto front of solutions and selecting the best results. Taking into account that the longest exploration took eleven seconds, this exploration is very fast compared to a handmade DSE. On the other hand, at the time that this evaluation happened, this tool was able to explore only three code transformations: loop fusion, loop tiling and data partitioning.

As many different solutions were generated for each application we decided to choose the fastest one. The tool generates a graph with the transformations selected and a XML file describing the system (see 4.1.3). By combining the XML file and the configurable library of components (see 4.2) we were able to create the customized ASIP for the application. To validate the communication DSE proposed in this document we decided to generate three different customized ASIPs for each application. The first one (custom\_1bus) connects all clusters through a single bus. This configuration extremely reduces the overall connectivity. The second one (custom\_pipe) is the model proposed which connects the clusters in a pipelined way. The last one (custom\_fully) connects all clusters together with a bus for each cluster's output connected to all clusters' input. It is important to emphasize

| Name  | Description                           |

|-------|---------------------------------------|

| Lpsf  | Low pass spatial filter               |

| Down  | Down sampling                         |

| 2mm   | Two matrix multiplication             |

| 3mm   | Three matrix multiplication           |

| Mvt   | A matrix vector product and transpose |

| Syrk  | Symmetric rank-k operations           |

| Syr2k | Symmetric rank-2k operations          |

Table 5.1: Benchmarks

that the custom ASIPs are different for each application. In other words, the custom\_pipe generated for 2mm will be different from the custom\_pipe generated for 3mm.

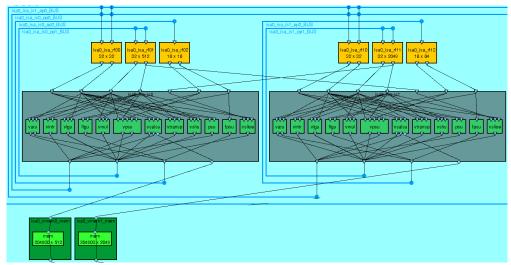

In order to evaluate the results we decided to compare our customized ASIPs against two different architectures. The first one (called ali\_01is) is a scalar processor containing only one issue slot. This architecture aims to represent the least parallel architecture possible and it tends to take many cycles to finish, but using little energy. On the other hand, the second architecture (cec\_08is) is a very large processor containing eight issue slots fully connected. We did not generate vector issue slot because the Application Parallelization tool is not able to automatically infer vectorization yet. We know that vectorization can decrease a lot the number of cycles and also reduce the power consumption. However, with these ASIPs we can still verify if the flow is implying a correct number of clusters and issue slots, taking advantage of the parallelization available in the code.

All the application versions were then compiled to all target ASIPs and then the systems were simulated to measure cycles, power and utilization. All results were normalized and the result for the initial version of the code mapped on the ali\_01 ASIP was selected as reference. The system level communication and the generic API for a user-oriented multi-ASIP system proposed in this document were used to generate and simulated the system.

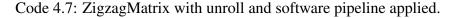

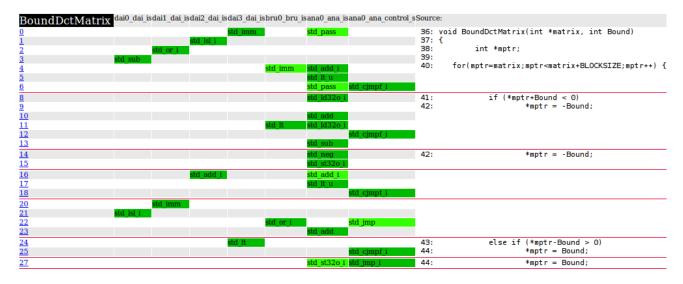

Figure 5.1 shows the speed-up and energy results for 2mm, 3mm and syr2k. In this figure "initial" means the initial code, "merged" means only fusion explored and "dp" means that fusion and data partitioning were explored. As we can observe, for all applications the transformations applied on the code speed-up the execution. In the 3mm we achieved a speed-up of almost 3.25 which is a good result for only three code transformations (without vectorization). In addition, we can observe that the number of cycles for the custom pipe and for the custom fully is very similar. Also, the pipelined way consumes less energy. This means that the pipelined connection is a good approach and a fully connected set of clusters is not needed. Another important observation is that in some cases the custom\_pipe performed better than the custom\_fully, which shouldn't happen. We trust that the explanation come from the compiler. As we were not using the compiler on the exhaustive mode (which search for the optimal schedule), we believe that the pipelined structured helps the compiler to keep some variables in the correct cluster (instead of passing to other clusters, which could happen more frequently in the fully connected case because it has less restrictions in the connectivity). The custom 1bus is always slower and uses more energy than the other customized ASIPs. This validates the inter issue slot communication approach proposed.

Comparing the customized ASIP with ali\_01is we can conclude that customized can perform much faster (at least 1.5 times) without increasing much energy (around 20% more). Moreover, in comparison with the cec\_08is it's possible to perceive that the speed-up is almost similar, but the energy consumption is much lower. Thus, it is possible to conclude that the DSE has made an acceptable design choice.

Figure 5.2 shows the final result (all transformations explored) for all the benchmarks selected. We can reach the same conclusions as before by looking to the other applications. In addition, we can observe the graph with the ASIP's utilization. As expected, the ali\_01 has the biggest utilization because it has only one IS that is almost always executing an operation. On the other hand, cec\_08 has the lowest utilization because we do not have enough parallelism to take advantage of all eight issue slots. The custom ASIPs show a tolerable utilization is some cases, but it should be improved by exploring more code transformations for instance.

Figure 5.1: Code transformation results for 2mm, 3mm and syr2k.

Figure 5.2: Final results.

### 6 CONCLUSION AND PERSPECTIVES

In this document we have discussed the ASAM flow, introduced its challenges and issues and proposed solutions to different matters. In addition, part of the flow was evaluated and validated and the experimental results revealed an important design-time speedup. Moreover, a component based design for multi-ASIP platform was proposed and validated. We have introduced and compared several strategies to connect different issue slots and we have shown that our approach give the best trade-off regarding application execution time and energy consumption.

Still, there is much work to be completed on the ASAM project. First, the trade-off involving the Model of Computation and the time spent to port the code should be further investigated and supportive methods to accelerate the porting phase should be proposed. In addition, the flow should be stressed with much more (and more complex) use cases in order to continue the integration process and to generate real consumer applications. The vectorization should be introduced and validated as soon as possible because we can only reach significant improvements on this kind of ASIPs systems through an efficient use of vectors. Finally, more code transformations should be implemented. As shown in the project description (Appendix G) there are much more code transformations that help to exploit the parallelism of the ASIPs and they are required to achieve important speed-up, targeting at least 20 times faster than the initial code as it is seen in the industry nowadays.

Future work could involve new features inside the ASAM flow. For example, fixed point conversion (numerical analysis), register size reduction (in number of bits) and custom operations could be investigated in the ASIP generation, optimizing even more the final result.

In conclusion, even though we have many things to do in order to finish the entire ASAM flow, we already have some parts of the full flow working that could help the designer, generating information about alternatives architectures and reducing the design-time. If one day we can have a complete flow working and generating real optimized consumer systems, the impact on the market can be huge and it can allow spreading embedded systems much faster and energy-efficient.

## REFERENCES

Movidius Myriad SoC. Software Programmable Media Processor, Movidius Myriad SoC, Project website. Available on: <a href="http://movidius.com/">http://movidius.com/</a>. Last access: May 2013.

Intel Mobile SoCs. **Programmable Image Signal Processor, Medfield, Clover Trail, Project website**. Available on: <a href="http://www.intel.com/>">http://www.intel.com/></a>. Last access: May 2013.

JOZWIAK, L. Quality-driven design in the system-on-a-chip era: Why and how?, Journal of Systems Architecture, vol. 47, no. 3-4, pp. 201-224, Apr. 2001.

JOZWIAK, L; ONG, S. Quality-driven model-based architecture synthesis for realtime embedded SoCs, Journal of Systems Archi-tecture, vol. 54, no. 3-4, pp. 349-368, Mar. 2008.

DENSMORE, D; PASSERONE, R. A Platform-Based Taxonomy for ESL Design, IEEE Design & Test of Computers, vol. 23, no. 5, pp. 359-374, May 2006.

UCBerkeley. **Metropolis: Design Environment for Heterogeneous Systems, Project website**. Available on: <a href="http://embedded.eecs.berkeley.edu/metropolis/platform.html">http://embedded.eecs.berkeley.edu/metropolis/platform.html</a>. Last access: May 2013.

SCHREIBER, R; ADITYA, S; MAHLKE, S; KATHAIL, V; RAU, B; CRONQUIST, D; SIVARAMAN, M. **Pico-npa: High-level synthesis of nonprogrammable hardware accelerators**, J. of VLSI Signal Proc. (2002)

MURRAY, A; FRANKE, B. Compiling for automatically generated instruction set extensions, In: proceedings of the Tenth International Symposium on Code Generation and Optimization, CGO '12 pp. 13-22. ACM, New York, NY, USA (2012).

FlexASP project. **TTA-based co-design environment, Project website**. Available on: <<u>http://tce.cs.tut.fi/></u>. Last access: May 2013.

KATHAIL, V; ADITYA, S; SCHREIBER, R; RAU, B; CRONQUIST, D; SIVARAMAN, M. **PICO: automatically designing custom computers**, Computer, vol. 35, no. 9, pp. 39-47, 2002.

TERECHKO, A; THENAFF, E; GARG, M; EIJNDHOVEN, J; CORPORAAL, H. Intercluster communication models for clustered vliw processors, in High-Performance Computer Architecture, 2003. HPCA-9 2003. Proceedings. The Ninth International Symposium on. IEEE, 2003, pp. 354-364. JOZWIAK, L; LINDWER, M; CORVINO, R; MELONI, P; MICCONI, L; MADSEN, J; DIKEN, E; GANGADHARAN, D; JORDANS, R; POMATA, S; POP, P; TUVERI, G; RAFFO, L. **ASAM: Automatic Architecture Synthesis and Application Mapping**, DSD 2012 - 15th Euromicro Conference on Digital System Design, pages 1-11, Cesme, Izmir, Turkey, 2012.

JOZWIAK, L; LINDWER, M. Issues and Challenges in Development of Massively-Parallel Heterogeneous MPSoCs Based on Adaptable ASIPs, PDP 2011 - 19th International Euromicro Conference on Parallel, Distributed and Network-Based Processing, pages 483-487, 2011.

JOZWIAK, L; LINDWER, M. Automatic Architecture Synthesis and Application Mapping for Application-specific Customizable MPSoCs, HOPES 2010 - the First International Workshop on Hands-on Platforms and Tools for Model-based Engineering of Embedded Systems, in the scope of ECMFA 2010 - the Sixth European Conference on Modelling Foundations and Applications, pages 105-110, Paris, France, 2010.

ASAM. ASAM Project website. Available on: <a href="http://www.asam-project.org">http://www.asam-project.org</a>. Last access: February 2013.

JOZWIAK, L; LINDWER, M; MADSEN, J. Model-based MPSoC Architecture Synthesis for Highly-demanding Embedded Applications, DATE 2011 Tutorial presentation.

SILICONHIVE. **Hivelogic Configurable Parallel Processing Platform**, SiliconHive, 2010.

ASAM. **Polybench: The Polyhedral Benchmark Suite, Project website**. Available on: <<u>http://www.cse.ohio-state.edu/pouchet/software/polybench/></u>. Last access: May 2013.

GLITIA, C; DUMOND, P; BOULET, P. Array-ol with delays, a domain specific specification language for multidimensional intensive signal processing, Multidimensional Syst. Signal Process., vol. 21, no. 2, pp. 105-131, Jun. 2010. [Online]. Available: http://dx.doi.org/10.1007/s11045-009-0085-4

# APPENDIX A EXAMPLE OF USER CONSTRAINS (XML FILE)

# APPENDIX B EXAMPLE OF PLATFORM DESCRIPTION (XML FILE)

```

<?xml version="1.0" encoding="utf-8" ?>

<platform id="1">

<node id="1">

<name>PU1</name>

<type>PE</type> </node>

<node id="2">

<name>PU2</name>

<type>PE</type>

</node>

<node id="3">

<name>PU3</name>

<type>PE</type>

</node>

<node id="4">

<name>PU4</name>

<type>bus</type>

<width id="1">32</width>

<frequency id="1">10</frequency>

<width id="2">16</width>

<frequency id="2">10</frequency>

</node>

<edge source="1" target="4" />

<edge source="2" target="4" />

<edge source="3" target="4" />

<edge source="4" target="1" />

<edge source="4" target="2" />

<edge source="4" target="3" />

</platform>

```

## APPENDIX C EXAMPLE OF TASK AND SYSTEM ANAL-YSIS (XML FILE)

```

<?xml version="1.0" encoding="utf-8" ?>

<solutions>

<solution id="1">

<cluster id="1:1">

<node id="1:1:1" >

<name>T1</name>

<WCET id="1">47</WCET>

<WCET id="2">77</WCET>

<WCET id="3">97</WCET>

<WCET id="4">107</WCET>

<WCET id="5">110</WCET>

<WCET id="6">135</WCET>

<priority>1</priority>

</node>

<node id="1:1:3" >

<name>T2</name>

<WCET id="1">55</WCET>

<WCET id="2">60</WCET>

<WCET id="3">90</WCET>

<WCET id="4">47</WCET>

<WCET id="5">100</WCET>

<WCET id="6">35</WCET>

<priority>3</priority>

</node>

</cluster>

<cluster id="1:2">

<node id="1:2:5" >

<name>T3</name>

<WCET id="1">60</WCET>

<WCET id="2">65</WCET>

<WCET id="3">100</WCET>

<WCET id="4">137</WCET>

<WCET id="5">150</WCET>

<WCET id="6">175</WCET>

<priority>5</priority>

</node>

</cluster>

<cluster id="1:4">

<edge id="1:4:2" source="1:1:1" target="1:1:3">

<name>MT1</name>

<data>7680</data>

</edge>

```

```

<edge id="1:4:4" source="1:1:3" target="1:2:5">

<name>MT2</name>

<data>1536</data>

</edge>

<edge id="1:4:6" source="1:1:1" target="1:2:5">

<name>MT3</name>

<data>696</data>

</edge>

</cluster>

<parametersList>

<parameters clusterId="1:1">

<config id="1" area="70" power="50" />

<config id="2" area="50" power="40" />

<config id="3" area="30" power="30" />

<config id="4" area="20" power="30" />

<config id="5" area="10" power="10" />

<config id="6" area="10" power="5" />

</parameters>

<parameters clusterId="1:2">

<config id="1" area="80" power="60" />

<config id="2" area="40" power="40" />

<config id="3" area="10" power="20" />

<config id="4" area="10" power="10" />

<config id="5" area="5" power="10" />

<config id="6" area="5" power="10" />

</parameters>

<parameters clusterId="1:4">

<config id="1" area="80" power="60"/>

<config id="2" area="90" power="40"/>

</parameters>

</parametersList>

</solution>

</solutions>

```

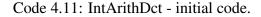

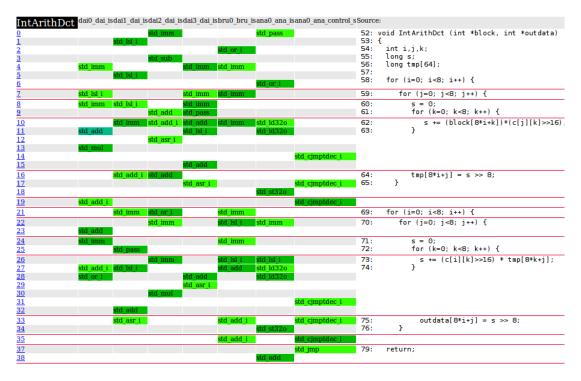

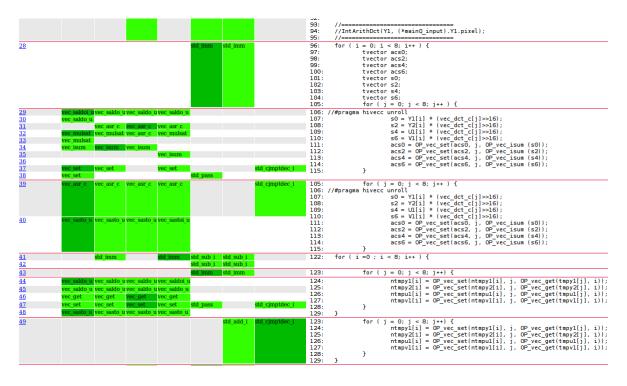

## APPENDIX D EXAMPLE OF DEFAULT COMPONENTS

(c) Bru: Scalar IS with scalar master interface.

(d) Cec: Scalar IS v scalar memory.

(e) Dai: Scalar IS with no memory.

Figure D.1: Only scalar components.

(a) Eva: Vector and scalar IS with vector memory.

(b) Fer: Vector and scalar IS with vector master interface.

(c) Giu: Vector and scalar IS with no memory.

(d) Isa: Two different vector and a scalar IS communicating through slice operations and connected to two different vector memories.

# APPENDIX E HOST CODE EXAMPLE

```

hrt_cell_load_program(CELL, "fir");

for ( i = 0; i < N_h; i++ ) {</pre>

for ( j = 0; j < n_width; j++ ) {</pre>

hrt_asam_indexed_store_signed_vector(CORE, CELL, fir, (&in_image[i][j*

CORE_NWAYS]), image_hive, (i*(n_width)+j));

}

}

for ( i = 0; i < N_h2; i++ ) {</pre>

for ( j = 0; j < n_width2; j++ ) {</pre>

hrt_asam_indexed_store_signed_vector(CORE, CELL, fir, (&in_image2[i][j*

CORE_NWAYS]), image_hive2, (i*(n_width2)+j));

}

}

hrt_asam_mem_store_nooffset( CELL, fir, height_hive, &height, sizeof(

int) );

hrt_asam_mem_store_nooffset( CELL, fir, width_hive, &n_width, sizeof(

int) );

hrt_asam_mem_store_nooffset( CELL, fir, height_hive2, &height2, sizeof(

int) );

hrt_asam_mem_store_nooffset( CELL, fir, width_hive2, &n_width2, sizeof(

int) );

hrt cell start function(CELL, fir);

hrt cell wait(CELL);

for ( i = 0; i < N_h; i++ ) {</pre>

for ( j = 0; j < n_width; j++ ) {</pre>

hrt_asam_indexed_load_signed_vector(CORE, CELL, fir, image_hive, (i*(

n_width)+j), (&out_image[i][j*CORE_NWAYS]));

}

}

for ( i = 0; i < N_h2; i++ ) {</pre>

for ( j = 0; j < n_width2; j++ ) {</pre>

hrt_asam_indexed_load_signed_vector(CORE, CELL, fir, image_hive2, (i*(

n_width2)+j), (&out_image2[i][j*CORE_NWAYS]));

}

}

```

## APPENDIX F ASIP CODE EXAMPLE

#include <hive/asam\_support\_cell.h>

#include "isp00.c"

```

SYNC_WITH(core01_IN) MEM(HIVE_MEM_core01_A)AT(HIVE_ADDR_core01_A)

___intern int A[core01_N_BUFFERS_IN][N][N];

SYNC_WITH(core01_IN) MEM(HIVE_MEM_core01_x1)AT(HIVE_ADDR_core01_x1)

___intern int x1[core01_N_BUFFERS_IN][N];

SYNC_WITH(core01_IN) MEM(HIVE_MEM_core01_x2)AT(HIVE_ADDR_core01_x2)

__intern int x2[core01_N_BUFFERS_IN][N];

SYNC_WITH(core01_IN) MEM(HIVE_MEM_core01_y_1)AT(HIVE_ADDR_core01_y_1)

__intern int y_1[core01_N_BUFFERS_IN][N];

SYNC WITH (core01 IN) MEM (HIVE MEM core01 y 2) AT (HIVE ADDR core01 y 2)

__intern int y_2[core01_N_BUFFERS_IN][N];

SYNC_WITH(core01_OUT) MEM(HIVE_MEM_core01_x1_out)AT(

HIVE_ADDR_core01_x1_out)extern int x1_out[core01_N_BUFFERS_IN][N];

SYNC_WITH(core01_OUT) MEM(HIVE_MEM_core01_x2_out)AT(

HIVE_ADDR_core01_x2_out)extern int x2_out[core01_N_BUFFERS_IN][N];

static int db_in[core01_N_CHANNELS_IN] = {0};

SYNC_WITH(core01_IN) static int db_read[core01_N_CHANNELS_IN] = {0};

SYNC_WITH(core01_OUT) static int db_out[core01_N_CHANNELS_OUT] = {0};

void ND_01() ENTRY

{

int i;

// request input

std_snd(HIVE_FCTRL_core01_host_00, HIVE_FIF0_core01_host_00, db_in[0])

SYNC(core01_IN);

modinc(db_in[0], core01_N_BUFFERS_IN) SYNC(core01_IN);

for ( i = 0; i < 8; i++ ) {</pre>

if( i > 0 ){

// output sent

std_snd(HIVE_FCTRL_core01_host_05, HIVE_FIF0_core01_host_05, db_out[0])

SYNC (core01_OUT);

}

if(i < 8-1){

// request input

```

```

std_snd(HIVE_FCTRL_core01_host_00, HIVE_FIFO_core01_host_00, db_in[0])

SYNC(core01_IN);

modinc(db_in[0], core01_N_BUFFERS_IN) SYNC(core01_IN);

// wait for input

std_rcv(HIVE_FCTRL_core01_host_00, HIVE_FIFO_core01_host_00, db_read

[0]) SYNC(core01_IN);

// request to write output

std_rcv(HIVE_FCTRL_core01_host_05, HIVE_FIFO_core01_host_05, db_out[0])

SYNC(core01_OUT);

// real function

isp_kernel_mvt(x1[db_read[0]], x2[db_read[1]], y_1[db_read[2]], y_2[

db_read[3]], A[db_read[4]], x1_out[db_out[0]], x2_out[db_out[1]]);

}

```

```

// output sent

std_snd(HIVE_FCTRL_core01_host_05, HIVE_FIF0_core01_host_05, db_out[0])

SYNC(core01_OUT);

```

}

APPENDIX G PROJECT DESCRIPTION <TG1>

## UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTE OF INFORMATICS COMPUTER ENGINEERING

FELIPE AUGUSTO CHIES

Validation and Evaluation of the ASAM -Automatic Architecture Synthesis and Application Mapping - Flow

**Project Description**

Prof. Dr. Luigi Carro Universidade Federal do Rio Grande do Sul Advisor

Menno Lindwer Intel Corporation Coadvisor

Eindhoven, February 2013

UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL President: Prof. Carlos Alexandre Netto Vice President: Prof. Rui Vicente Oppermann President for Undergraduate Studies: Prof. Valquíria Linck Bassani Dean of Institute of Informatics: Prof. Luís da Cunha Lamb Coordinator of ECP: Prof. Marcelo Goetz Chief Librarian: Beatriz Regina Bastos Haro

# CONTENTS

| LIST OF ABBREVIATIONS AND ACRONYMS                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                                      |

| LIST OF CODE                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                      |

| <b>ABSTRACT</b> 1                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                                                                      |

| <b>1 INTRODUCTION</b> 1                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                      |

| <b>2.1</b> Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                | 3<br>3<br>4                                                                            |

| <b>3.1 Description</b>                                                                                                                                                                                                                                                                                                                                                                                                                               | 7<br>7<br>8                                                                            |

| 4.1Before Mapping24.1.1Rewriting the Application24.1.2Make use of a Model of Computation24.1.3Clustering24.1.4System Selection24.2Processor Architecture Features24.2.1Operation-level Pipelining24.2.2Multi-RISC Operations24.2.3Instruction-level Parallelism24.2.4Vector-, Data- or SIMD-level Parallelism24.2.5Task-, Thread- or MIMD-level Parallelism24.3.1Vectorization24.3.2Compiler Pragmas24.3.3Task- and Loop-level Code Transformations2 | 20<br>20<br>21<br>23<br>25<br>25<br>26<br>26<br>28<br>28<br>29<br>29<br>29<br>29<br>36 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4                                                                                      |

| <b>REFERENCES</b>                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                                                     |

| APPENDIX A | CORES                             | 47 |

|------------|-----------------------------------|----|

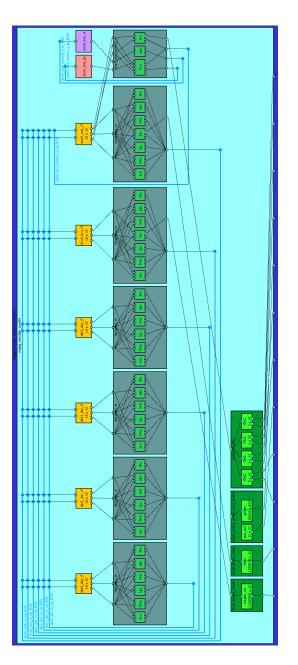

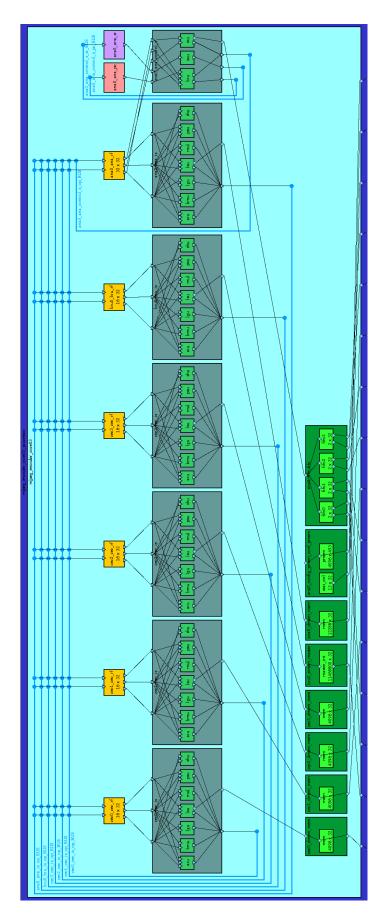

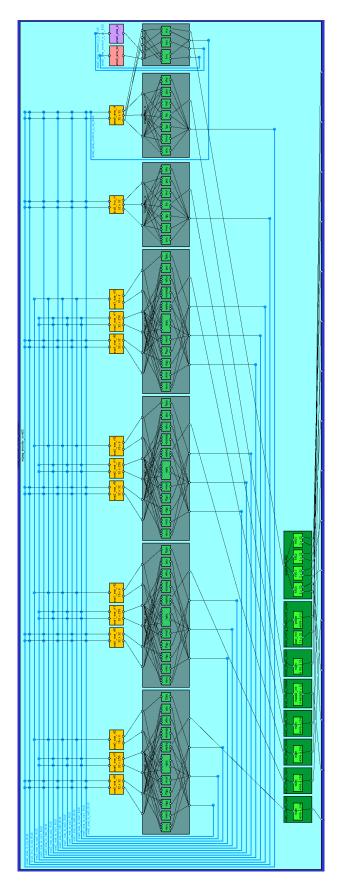

| APPENDIX B | SYSTEMS                           | 50 |

| APPENDIX C | METRICS                           | 51 |

| APPENDIX D | OPERATIONAL TARGETS (O)           | 54 |

| APPENDIX E | FUNCTIONAL REQUIREMENTS (F)       | 55 |

| APPENDIX F | DETAILED TECHNICAL OBJECTIVES (T) | 56 |

| APPENDIX G | VERIFICATION REQUIREMENTS (V)     | 58 |

| APPENDIX H | SYSTEM REQUIREMENT                | 59 |

# LIST OF ABBREVIATIONS AND ACRONYMS

| Americal National Standards Institute version of the 'C' programming language.                                                                                                                       |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Application Programmers Interface                                                                                                                                                                    |  |  |

| Arithmetic Unit                                                                                                                                                                                      |  |  |

| Application-specific Instruction-set Processor                                                                                                                                                       |  |  |

| Programming language, based on the 'C' language. SystemC is built on top of C++.                                                                                                                     |  |  |

| Intel's proprietary MMIO interface protocol                                                                                                                                                          |  |  |